# LUIS CÂNDIDO TOMASELLI

# CONTROLE DE UM PRÉ-REGULADOR COM ALTO FATOR DE POTÊNCIA UTILIZANDO O CONTROLADOR DSP TMS320F243

FLORIANÓPOLIS 2001

# UNIVERSIDADE FEDERAL DE SANTA CATARINA CURSO DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

CONTROLE DE UM

PRÉ-REGULADOR

COM ALTO

FATOR DE POTÊNCIA

UTILIZANDO O

CONTROLADOR DSP TMS320F243

Dissertação submetida à

Universidade Federal de Santa Catarina

como parte dos requisitos para a

obtenção do grau de Mestre em Engenharia Elétrica.

LUIS CÂNDIDO TOMASELLI

Florianópolis, Fevereiro de 2001.

# CONTROLE DE UM PRÉ-REGULADOR COM ALTO FATOR DE POTÊNCIA UTILIZANDO O CONTROLADOR DSP TMS320F243

#### LUIS CÂNDIDO TOMASELLI

Esta Dissertação foi julgada adequada para obtenção do Título de Mestre em Engenharia Elétrica, na área de concentração de Eletrônica de Potência, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina.

Professor Hari Bruno Mohr, Dr. Orientador

Professor Aguinaldo Silveira e Silva, Ph. D.

Coordenador do Programa de Pós-Graduação em Engenharia Elétrica

Banca Examinadora:

Professor Hari Bruno Mohr, Dr.

Presidente da Banca

Professor Ivo Barbi, Dr. Ing.

Rexandre Ferrari de Souza, Dr.

Professor Enio Valmor Kassick, Dr.

"Realmente, só pelo fato de ser consciente das causas que inspiram minhas ações, estas causas já são objetos transcendentes para minha consciência; elas estão fora. Em vão tentaria apreendê-las. Escapo delas pela minha própria existência. Estou condenado a existir para sempre além da minha essência, além das causas e motivos dos meus atos. Estou condenado a ser livre. Isso quer dizer que nenhum limite para minha liberdade pode ser estabelecido exceto a própria liberdade, ou, se você preferir; que nós não somos livres para deixar de ser livres."

Jean-Paul Sartre, O Ser e o Nada (1943), Quarta parte

## Agradecimentos

Por muitas vezes caminhamos, por razões diferentes, em busca de escopos comuns. Não há nada que apraze mais nossa opropriedade do que a satisfação das metas que traçamos um dia.

Hoje as lembranças representam momentos de alegría e a existência destas, propicia a possibilidade de um futuro. As muitas pessoas, que compõe a minha trajetória, dispenso as minhas atenções e reverências em agradecimento a tudo o que me ensinaram.

Gostaria de agradecer a todos os membros que compõe o corpo técnico e administrativo do Instituto de Eletrônica de Potência (INEP) e em especial ao meu orientador, o Prof. Hari Bruno Mohr, a CAPES pela bolsa concedida, a Texas Instrument pela doação da placa de desenvolvimento e aos professores Daniel Pagano, Júlio Elias, Enio, Arnaldo, João, Denizar, Alexandre e Ivo pelos conhecimentos transmitidos durante o período de créditos.

Dedico, também, agradecimentos ao meu colega e amigo Samir que foi uma fonte de incentivos constantes mesmo nos momentos em que os revezes se sobressaiam em relação aos sucessos.

Aos meus conspícuos amigos Sérgio, Luciano, Djonny, Milton, Paulo, José, Kefas, Romeu, César David, Marcos Muricame, Valcir e Yales agradecimentos pela convivência durante este pequeno intervalo o qual estivemos nesta jornada.

Minha admiração aos meus pais e irmãos por sua inefável paciência em lidar com uma pessoa tão teimosa quanto eu.

A todos aqueles aos quais não mencionei, não por falta de merecimento mas, por minha inépcia em fazê-lo em tão pouco espaço e com tão poucas palavras.

Resumo da Dissertação apresentada à UFSC como parte dos requisitos necessários para a obtenção do grau de Mestre em Engenharia Elétrica.

# CONTROLE DE UM PRÉ-REGULADOR COM ALTO FATOR DE POTÊNCIA UTILIZANDO O CONTROLADOR DSP TMS320F243

#### Luis Cândido Tomaselli

Fevereiro de 2001.

Orientador: Professor Hari Bruno Mohr, Dr. Área de Concentração: Eletrônica de Potência.

Palavras-chave: Controlador DSP, pré-regulador, alto fator de potência, conversor Boost.

Número de páginas: 95

RESUMO: Este trabalho trata de um estudo da aplicação de um controlador DSP, em eletrônica de potência, na implementação do controle digital de um conversor Boost operando como pré-regulador com alto fator de potência. Parte-se de um estudo sobre as principais características, necessárias ao projeto, do controlador DSP. Prossegue-se através do projeto do conversor Boost e dos controladores das malhas de controle da tensão e da corrente. Os resultados de simulação são apresentados e em uma última etapa são mostrados os resultados experimentais de um protótipo com potência de 500W, tensão de saída de 400V e frequência de comutação de 50kHz.

Abstract of Dissertation presented to UFSC as a partial fulfillment of the requirements for the degree of Master in Electrical Engineering.

### A HIGH POWER FACTOR PRE-REGULATOR CONTROL USING THE DSP CONTROLER TMS320F243

#### Luis Cândido Tomaselli

February of 2001.

Advisor: Professor Hari Bruno Mohr, Dr. Área of Concentration: Power Electronics.

Keywords: DSP Controler, pre-regulator, high power factor, Boost converter.

Number of pages: 95

ABSTRACT: This work deals with a study of a Boost converter operating as a high power factor pre-regulator using the DSP controller TMS320F243 from Texas Instruments. The study begins with a description of the controller and its peripheral devices that were used. After this, it is shown the design of the controllers of the voltage control loop and the current control loop. The results obtained by simulation and by experimentation are presented for a prototype implementation with output voltage of 400V, output power of 500W and switching frequency of 50kHz.

# SUMÁRIO

| RE  | SUMO .       |        |                                                     | vi  |

|-----|--------------|--------|-----------------------------------------------------|-----|

| AB  | STRAC        | Γ      |                                                     | vii |

| SIN | <b>IBOLO</b> | GIA    |                                                     | x   |

| INT | rodu         | ÇÃO GE | ERAL                                                | 1   |

| CA  | PÍTULO       | 1      |                                                     |     |

| 0 ( | CONTRO       | DLADO: | R DSP (DIGITAL SIGNAL PROCESSOR) TMS320F243         | 3   |

|     | 1.1          | INTR   | ODUÇÃO                                              | 3   |

|     | 1.2          | PROC   | ESSADOR DIGITAL DE SINAIS – DSP                     | 3   |

|     | 1.3          | FORM   | NATOS NUMÉRICOS EM UM PROCESSADOR DSP               | 6   |

|     |              | 1.3.1  | Ponto fixo                                          | 9   |

|     |              | 1.3.2  | Ponto flutuante                                     | 14  |

| ,   | 1.4          | A FAI  | MÍLIA TMS320                                        | 15  |

|     |              | 1.4.1  | TMS320F243                                          | 16  |

|     | •            |        | 1.4.1.1 A arquitetura interna                       | 18  |

|     |              |        | 1.4.1.2 Interrupções                                | 19  |

| ,   | •            |        | 1.4.1.3 Gerenciador de eventos                      | 20  |

|     |              |        | 1.4.1.4 Conversor analógico digital pseudo-dual     | 24  |

|     | 1.5          | CONC   | CLUSÃO                                              | 26  |

| CA  | PÍTULO       | 2      |                                                     |     |

| PR  | OJETO        | DO CO  | NTROLADOR DIGITAL PARA O CONVERSOR BOOST            | •   |

| PR  | É-REGU       | LADO   | 3                                                   | 27  |

|     | 2.1          | INTR   | ODUÇÃO                                              | 27  |

|     | 2.2          | DESC   | RIÇÃO DO MÉTODO DE CONTROLE UTILIZADO               | 27  |

|     | 2.3          | PROJ   | ETO DO ESTÁGIO DE POTÊNCIA DO CONVERSOR             | 30  |

|     | 2.4          | PROJ   | ETO DO CONTROLE DIGITAL DO CONVERSOR                | 35  |

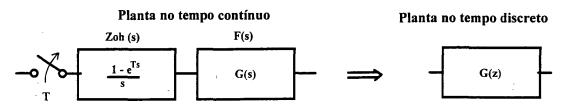

|     |              | 2.4.1  | Obtenção das funções de transferência discretizadas | 38  |

|     |              | 2.4.2  | Projeto dos filtros de anti-aliasing                | 42  |

|     |              | 2.4.3  | Projeto do controlador da malha de corrente         | 43  |

|     |              | 2.4.4  | Projeto do controlador da malha de tensão           | 48  |

|     |              |        |                                                     |     |

|          | 2.4.5   | Cálculo da malha de feedforward            | 51   |

|----------|---------|--------------------------------------------|------|

|          | 2.4.6   | Obtenção da equação à diferenças           | 52   |

|          | 2.4.7   | Exemplo de projeto dos controladores       |      |

| 2.5      | CON     | CLUSÃO                                     | 59   |

| CAPÍTULO | 0 3     |                                            |      |

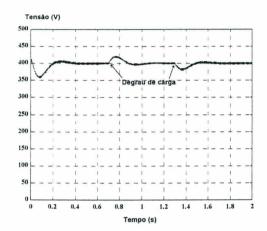

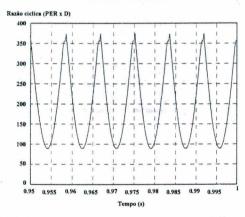

| RESULTA  | DOS DE  | SIMULAÇÃO                                  | 61   |

| 3.1      | INTR    | ODUÇÃO                                     | 61   |

| 3.2      | RESU    | JLTADOS DE SIMULAÇÃO UTILIZANDO-SE AS FUNC | ÇÕES |

| DE T     | ΓRANSF  | ERÊNCIA                                    | 61   |

| 3.3      | RESU    | JLTADOS DE SIMULAÇÃO USANDO A MODELA       | GEM  |

| POR      | EQUAÇ   | ÇÕES DE ESTADO DO CONVERSOR BOOST          | 67   |

| 3.4      | CON     | CLUSÃO                                     | 78   |

| CAPÍTULO |         |                                            |      |

| IMPLEME  | NTAÇÃ   | O DO PROTÓTIPO                             | 79   |

| 4.1      |         | ODUÇÃO                                     |      |

| 4.2      |         | OGRAMA                                     |      |

| 4.3      |         | IRCUITOS DE INTERFACE                      |      |

| 4.4      |         | JLTADOS EXPERIMENTAIS                      |      |

| 4.5      |         | CLUSÃO                                     |      |

| CONCLUS  |         | RAL                                        |      |

| REFERÊN  | CIAS BI | IBLIOGRÁFICAS                              | 93   |

## **SIMBOLOGIA**

## 1. Símbolos adotados nos equacionamentos.

| Símbolo        | Significado                                                                       | Unidade         |

|----------------|-----------------------------------------------------------------------------------|-----------------|

| η              | rendimento                                                                        | %               |

| $\tau_1$       | frequência de corte do filtro                                                     | Rad/s           |

| ωz             | frequência do zero do compensador                                                 | Rad/s           |

| Ae             | área da perna central                                                             | cm <sup>2</sup> |

| Aw             | área da janela                                                                    | cm <sup>2</sup> |

| В              | offset                                                                            |                 |

| $C_0$          | capacitância de saída                                                             | F               |

| Ca             | capacitor do filtro de anti-aliasing                                              | F               |

| $C_s$          | capacitância do <i>snubber</i>                                                    | · F             |

| D'med          | razão cíclica complementar média                                                  |                 |

| $D_{min}$      | razão cíclica mínima                                                              |                 |

| E<br>F         | potência do radix                                                                 |                 |

| F              | inclinação fracional                                                              |                 |

| $\mathbf{f_a}$ | frequência de amostragem                                                          | Hz              |

| fc             | frequência de cruzamento                                                          | Hz              |

| FEi            | fator de escala da malha de corrente                                              |                 |

| FEv            | fator de escala da malha de tensão                                                |                 |

| $F_{feed}$     | fator de correção feedforward                                                     |                 |

| $f_r$          | freqüência da rede                                                                | Hz              |

| $\mathbf{f_s}$ | freqüência de comutação                                                           | Hz              |

| Ganho          | ganho do amplificador de corrente                                                 |                 |

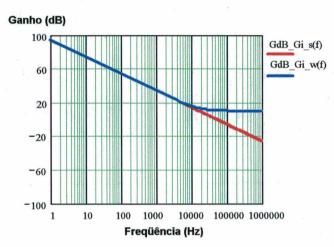

| Gi(s)          | função de transferência da corrente do indutor pela razão cíclica no domínio de s |                 |

| Gi(w)          | função de transferência da corrente do indutor pela razão cíclica no domínio de w |                 |

| Gi(z)          | função de transferência da corrente do indutor pela razão cíclica no domínio de z |                 |

| Gim(s)         | função de transferência da corrente do indutor pela razão cíclica modificada no   |                 |

|                | domínio de s                                                                      |                 |

| Gim(w)         | função de transferência da corrente do indutor pela razão cíclica modificada no   |                 |

|                | domínio de w                                                                      |                 |

| Gim(z)         | função de transferência da corrente do indutor pela razão cíclica modificada no   |                 |

|                | domínio de z                                                                      |                 |

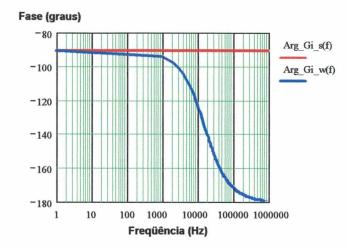

| Gv(s)          | função de transferência da tensão pela corrente do indutor domínio de s           |                 |

| Gv(w)          | função de transferência da tensão pela corrente do indutor domínio de w           |                 |

| Gv(z)          | função de transferência da tensão pela corrente do indutor domínio de z           |                 |

| Hv.            | função de transferência de malha fechada da malha de corrente                     |                 |

| Id             | corrente média no diodo de saída                                                  | Α               |

| $I_D$          | corrente de dreno                                                                 | Α               |

| Idr            | corrente média nos diodos retificadores                                           | Α               |

| $I_{FAV}$      | corrente média no diodo                                                           | Α               |

| Iin            | corrente de entrada                                                               | Α               |

| $IL_{in}$      | corrente do indutor de entrada                                                    | Α               |

| Iр             | corrente de pico                                                                  | Α               |

| $I_{REFp}$     | corrente de referência de pico da tabela                                          |                 |

| Is             | corrente eficaz no interruptor                                                    | Α               |

| $I_{sn}$       | corrente de descarga do capacitor de snubber                                      | Α               |

| Kpi            | ganho do controlador da malha de corrente                                         |                 |

| Kp <sub>v</sub>          | ganho do controlador da malha de tensão               |                    |

|--------------------------|-------------------------------------------------------|--------------------|

| kv                       | ganho do divisor resistivo                            |                    |

| lg                       | comprimento do entreferro                             | mm                 |

| Lin                      | indutância boost                                      | Н                  |

| M                        | mantissa                                              |                    |

| MF                       | margem de fase                                        | 0                  |

| n                        | posição do ponto do radix                             |                    |

| N                        | número de espiras                                     |                    |

| $N_d$                    | número decimal que se deseja converter                |                    |

| $P_0$                    | potência de saída                                     | W                  |

| $P_{com}$                | perdas por comutação                                  | W                  |

| P <sub>cond</sub>        | perdas por condução                                   | W                  |

| PER                      | valor do registrador de período PWM                   |                    |

| PrSH                     | potência da resistência shunt                         | W                  |

| $P_s$                    | potência dissipada pelo snubber                       | W                  |

| Q                        | número inteiro equivalente que codifica V             |                    |

| q(t)                     | função de chaveamento                                 |                    |

| R <sub>eha</sub>         | resistência térmica dissipador-ambiente               | <sup>o</sup> C/W   |

| R <sub>0ja</sub>         | resistência térmica junção-ambiente                   | °C/W               |

| R <sub>0jc</sub>         | resistência térmica junção-cápsula                    | °C/W               |

| Ra                       | resistor do filtro de <i>anti-aliasing</i>            | Ω                  |

|                          | resistência em condução do MOSFET                     |                    |

| R <sub>DSON</sub><br>RSH | resistência shunt                                     | Ω                  |

|                          |                                                       | Ω                  |

| Rsn                      | resistência do <i>snubber</i>                         | Ω                  |

| S                        | inclinação                                            | 2                  |

| Scu                      | área de cobre necessário para o condutor              | cm <sup>2</sup>    |

| Ta                       | período de amostragem                                 | ${}^{ m s}_{ m C}$ |

| $T_{ca}$                 | temperatura da cápsula                                |                    |

| $T_{CLK}$                | valor do período de clock                             | S                  |

| td <sub>off</sub>        | tempo de atraso no bloqueio do MOSFET                 | S                  |

| tdon                     | tempo de atraso na entrada em condução do MOSFET      | S                  |

| $t_f$                    | tempo de descida no bloqueio do MOSFET                | °C                 |

| $T_{j}$                  | temperatura da junção                                 |                    |

| $T_{PWM}$                | valor do período de comutação                         | S                  |

| t <sub>r</sub>           | tempo de subida na entrada em condução do MOSFET      | S                  |

| $T_{rr}$                 | tempo de recuperação reversa                          | S                  |

| V                        | valor real equivalente                                | 17                 |

| $V_0$                    | tensão de saída                                       | V                  |

| vc(t)                    | tensão de saída em função do tempo                    | V                  |

| Vd <sub>p</sub>          | tensão reversa máxima sobre o diodo boost             | V                  |

| Vdr <sub>p</sub>         | tensão reversa máxima sobre os diodos retificadores   | V                  |

| V <sub>DSS</sub>         | tensão dreno source                                   | V                  |

| $V_{\rm F}$              | queda de tensão direta do diodo                       | V                  |

| Vin <sub>RMS</sub>       | tensão eficaz de entrada                              | V                  |

| Vmed <sub>atual</sub>    | valor médio atual                                     |                    |

| Vmed <sub>norm</sub>     | valor médio calculado para a tensão mínima de entrada | τ,                 |

| V <sub>REFHI</sub>       | tensão de referência alto do conversor A/D            | V                  |

| V <sub>REFLO</sub>       | tensão de referência baixa do conversor A/D           | V                  |

| $V_{RRM}$                | tensão reversa máxima no diodo                        | V                  |

| Vs <sub>p</sub>          | tensão máxima sobre o interruptor                     | V                  |

## 2. Sub-índices utilizados.

| Sub-índice | Significado                                                              |

|------------|--------------------------------------------------------------------------|

| Δ          | variação de uma grandeza em torno de um valor                            |

| aux        | valor relativo ao enrolamento auxiliar do transformador de ferro-silício |

| ef         | valor eficaz da grandeza                                                 |

| M          | valor relativo ao interruptor principal                                  |

| max        | valor máximo da grandeza                                                 |

| med        | valor médio da grandeza                                                  |

| min        | valor mínimo da grandeza                                                 |

| pk         | valor de pico da grandeza                                                |

## 3. Símbolos para referenciar elementos de circuitos.

| Símbolo | Significado     |  |

|---------|-----------------|--|

|         | Capacitor       |  |

| D       | Diodo           |  |

| L       | Indutor         |  |

| M       | Interruptor     |  |

| Q       | Transistor      |  |

| R       | Resistor        |  |

| TX      | Transformador   |  |

| V       | Fonte de tensão |  |

## 4. Símbolos de unidades de grandezas físicas.

| Sub-índice | Significado |                                       |

|------------|-------------|---------------------------------------|

| Ω          | Ohm         |                                       |

| Α          | Ampère      |                                       |

| dB         | Decibel     |                                       |

| F          | Farad       | · · · · · · · · · · · · · · · · · · · |

| Н          | Henry       | ·                                     |

| Hz         | Hertz       |                                       |

| m          | Metro       |                                       |

| rad        | Radiano     |                                       |

| S          | Segundo     |                                       |

| T          | Tesla       |                                       |

| V          | Volt        |                                       |

| W          | Watt        |                                       |

## 4. Acrônimos e abreviaturas.

|                 | Significado                                                 |

|-----------------|-------------------------------------------------------------|

| ACTR            | Full Compare Action Control Register                        |

| ADC             | Analog-Digital Converter                                    |

| <b>ADCFIFOx</b> | ADC Data Register $(x = 1 e 2)$                             |

| ADCTRLx         | ADC Control Register $(x = 1 e 2)$                          |

| ADCx            | Analog-Digital Input $(x = 0, 1, 2, 3, 4, 5, 6 e 7)$        |

| ANSI            | American National Standards Institute                       |

| CAN             | Control Area Network                                        |

| CAPES           | Coordenação de Aperfeiçoamento de Pessoal de Nível Superior |

| CC-CC           | Corrente contínua – corrente contínua                       |

| CI              | Circuito integrado                                          |

| CMPRx           | Compare Register $(x = 1, 2 e 3)$                           |

| COMCON          | Compare Control Register                                    |

| CPU             | Central Processor Unit                                      |

|                 |                                                             |

| DAC             | Digital-Analog Converter                                    |

| DARAM           | Dual Access Random Access Memory                            |

| DC              | Direct Current                                              |

| DSP             | Digital Signal Processor                                    |

| DSP             | Digital Signal Processing                                   |

| EEPROM          | Electrically Erasable Programable Read Only Memory          |

| EV              | Event Manager                                               |

| EVIFRx          | Event Manager Interrupt Flag Register $(x = A, B \in C)$    |

| EVIMRx          | Event Manager Interrupt Mask Register $(x = A, B e C)$      |

| FF'T            | Fast Fourier Transform                                      |

| FTLA            | Função de transferência de laço aberto                      |

| FTMF            | Função de transferência de malha fechada                    |

| GISR            | General Interrupt Service Routine                           |

| GP              | General Purpose                                             |

| GPIO            | General Purpose Input/Output                                |

| GPTCON          | General Purpose Timer Control Register                      |

| IEEE            | Institute of Electrical and Electronics Engineers           |

| IFR             | Interrupt Flag Register                                     |

| IMR             | Interrupt Mascarable Register                               |

| INEP            | Instituto de Eletrônica de Potência                         |

| ISR             | Interrupt Service Routine                                   |

| LSB             | Least Significant Bit                                       |

| MOSFET          | Metal-oxide-semiconductor field-effect-transistor           |

|                 |                                                             |

| MSB             | Most Significant Bit                                        |

| NMI             | Non Mascarable Interrupt                                    |

| PAB             | Program Address Bus                                         |

| PI              | Proporcional integral                                       |

| PIACK           | Peripherical Interrupt Acknowledge                          |

| PIC             | Peripheral interface controller                             |

| PID             | Proporcional integral derivativo                            |

| PIE             | Peripherical Interface Expansion                            |

| PIVR            | Peripherical Interrupt Vector Register                      |

| PLL             | Phase Locked Loop                                           |

| PWM             | Pulse width modulation                                      |

| SCI             | Serial Comunication Interface                               |

| SPI             | Serial Peripheral Interface                                 |

| TxCMP           | General Purpose Timer Compare/PWM Output $(x = 1 e 2)$      |

| TxCMPR          | General Purpose Compare Register $(x = 1 e 2)$              |

| TxCNT           | General Purpose Counter Register ( $x = 1 e 2$ )            |

| TxCON | General Purpose Control Register $(x = 1 e 2)$ |

|-------|------------------------------------------------|

| TxPR  | General Purpose Period Register $(x = 1 e 2)$  |

| FFT   | Fast Fourier Transform                         |

| FIR   | Finite Impulse Response                        |

| UFSC  | Universidade Federal de Santa Catarina         |

## INTRODUÇÃO GERAL

A eletrônica vem se desenvolvendo rapidamente e com isto, propiciando uma verdadeira reestruturação dos conceitos pertinentes à ciência. É inegável que todas as áreas, que geram conhecimento, possuem em algum grau a presença ou influência dos recursos disponíveis por intermédio da eletrônica.

E a eletrônica de potência pode ser vista como uma área de estudos abrangente e que também se faz presente em diversas instâncias dentro deste cenário. Assim como as revoluções desta, de um certo modo, acabam interferindo nas outras tecnologias, mudanças em outras áreas também acabam interferindo nesta. Dentro deste quadro surge a eletrônica digital como uma ferramenta, muito poderosa, disponível para quem estuda e trabalha com eletrônica de potência.

O controle digital, embora seja uma ciência muito bem fundamentada desde a metade do século, vem a cada dia assumindo um papel cada vez mais importante dentro da eletrônica de potência. Por intermédio dos processadores DSPs, hoje, pode-se implementar em produtos comerciais diversas formas de controle antes somente presentes em laboratórios de alta tecnologia ou em ambientes de simulação.

O estudo, que será apresentado, utiliza-se de um controlador DSP (TMS320F243) para implementar digitalmente o controle de um conversor pré-regulador Boost.

Não é abordado neste trabalho aspectos relativos a viabilidade econômica do projeto, ou seja, não é feito um estudo para verificar onde o controle digital passa a ser mais atrativo em relação ao controlador analógico.

No capítulo 1 será mostrado uma breve descrição do componente, procurando-se detalhar, principalmente, a questão de representação numérica de uma grandeza, tanto no formato de ponto fixo quanto no formato de ponto flutuante, e também quanto aos periféricos utilizados.

No capítulo 2 apresenta-se, com detalhes, todo o projeto do conversor. É abordado desde o estágio de potência até o cálculo das leis de controle a serem implementadas, digitalmente.

O capítulo 3 ilustra todo o procedimento de simulação, para investigação e

comprovação da funcionalidade das leis de controle, utilizado durante o desenvolvimento do trabalho.

Finalmente no capítulo 4 apresentam-se todos os resultados obtidos experimentalmente e irá observar-se a conformidade ou não destes com relação às normas que vigoram atualmente e com os dados encontrados por simulação.

## 1 O controlador DSP (Digital Signal Processor) TMS320F243

#### 1.1 Introdução

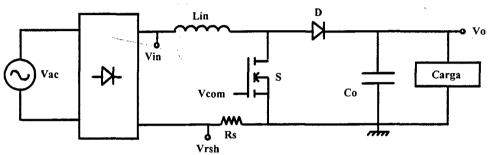

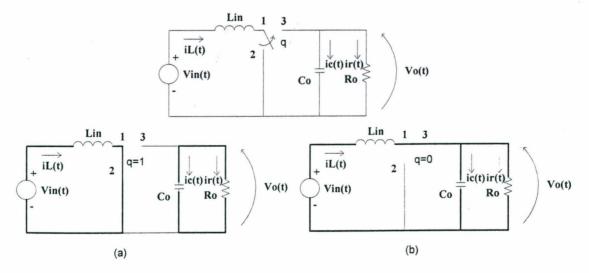

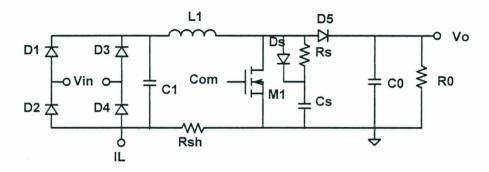

Estuda-se e apresenta-se um pré-regulador com alto fator de potência controlado por um processador digital de sinais (DSP). A topologia escolhida para desenvolver o trabalho é o conversor Boost (Fig. 1.1). Uma estrutura que, em termos de pesquisa, está consolidada e é amplamente utilizada para este fim [1] a [8].

Fig. 1.1 - Conversor Boost operando como pré-regulador.

Não é objetivo apresentar um estudo do funcionamento do conversor, que pode ser encontrado em literaturas específicas [1] a [8], mas sim de como efetuar um projeto do controle digital e implementá-lo a partir de um controlador digital.

Como início é apresentado uma síntese que retrata um pouco os DSPs. Procura-se descrever um DSP, como se faz a representação numérica e as diferenças entre os formatos adotados e por último uma visão genérica do controlador TMS320F243 e dos periféricos, a ele associados, usados para implementar o controle do conversor Boost.

### 1.2 Processador Digital de Sinais – DSP

Um DSP é, basicamente, um tipo de microprocessador otimizado para efetuar processamento matemático enquanto os demais processadores são otimizados para manipulação e gerenciamento de dados. Esta característica o faz apto a trabalhar com aplicações que não toleram atrasos de transporte significativos entre a aquisição de um dado digital, efetuação dos cálculos necessários e devolução da resposta digital.

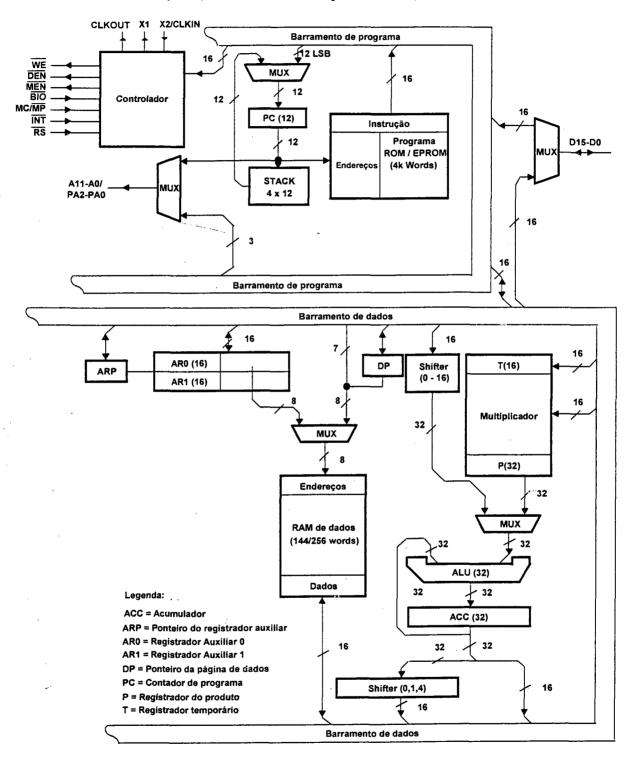

A Fig. 1.2 mostra uma arquitetura típica de um DSP básico de formato de ponto fixo. Por esta, pode-se observar algumas das características dos núcleos DSP tais como:

barramentos múltiplos, arquitetura de 16 bits, registradores de 32 bits e implementação por hardware de várias funções (deslocadores, multiplicadores...).

Fig. 1.2 - Arquitetura do núcleo DSP da família TMS320.

Os processadores usados em computadores são otimizados de modo a gerenciar e trabalhar com bancos de dados além de efetuar operações relacionais em detrimento das operações matemáticas. Isto por que a maior parte das tarefas a serem executadas são de

processamento off-line.

Segundo Smith [9], no processamento off-line o sinal de entrada inteiro reside no computador no mesmo tempo. Como exemplos de processamento off-line têm-se as imagens médicas, como as tomografias computadorizadas e exames de ressonância magnética. O conjunto de dados é adquirido enquanto o paciente está dentro da máquina, mas a reconstrução da imagem pode ser atrasada no tempo sem impor restrições ao desempenho do processamento. O ponto chave é que toda a informação está disponível simultaneamente para o processamento pelo programa.

Alternativamente, ainda sob a visão de Smith [9], no processamento em tempo real, o sinal de saída é produzido ao mesmo tempo que o sinal de entrada é adquirido. Por exemplo, isto é necessário na comunicação por telefone, aparelhos auditivos e radares. Estas aplicações devem ter a informação imediatamente disponível, embora possa haver um pequeno atraso (devido ao processamento requerido). Neste instante, um atraso de 10 ms em um telefone não pode ser detectado pelo locutor ou pelo ouvinte. Do mesmo modo, não faz diferença se um sinal de radar é atrasado por uns poucos segundos antes de ser mostrado para o operador.

Deste modo criou-se diferentes necessidades que dificultaram a fabricação de um processador que tratasse eficientemente os dois tipos de processamento. Assim, no início, o processador ou era otimizado para gerenciamento de dados e ou era otimizado para processamento matemático (devido as dificuldades e custos envolvidos para se obter um componente otimizado para ambos). Esta filosofia começou a mudar com a criação das redes de comunicação (tal como a INTERNET), nas quais tem-se a necessidade de processamento em tempo real fazendo que em um futuro próximo seja possível, em um mesmo componente, ter-se um bom desempenho tanto no gerenciamento de dados quanto no processamento matemático.

O fato do DSP estar otimizado para processamento matemático não o impede de efetuar tarefas de gerenciamento, o mesmo valendo para os demais processadores que podem efetuar processamento matemático. Apenas que, o desempenho será mais pobre quando comparado com um processador otimizado àquela aplicação.

Entretanto, um sinal digital é uma seqüência de uns e zeros que pode ser processada matematicamente pelo processador. Os DSPs podem manusear com grandes velocidades os sinais digitais, porém, necessitam de *interfaces* com o mundo real.

Deste modo sempre se faz necessário a inclusão da eletrônica analógica em conjunto com estes dispositivos. Por exemplo, sinais de intensidade luminosa, pressão sonora, velocidade, amplitudes de sinais periódicos, tão comuns no mundo como percebemos não são representados diretamente por sinais digitais. É necessário a conversão destes por intermédio de um conversor analógico-digital para que o processador possa trabalhar esta informação.

Do mesmo modo, para que possamos compreender os resultados do processamento, é necessário converter estes por intermédio de conversores digital-analógicos. São alguns exemplos de aplicações: comunicações sem fio, ampliação da capacidade de transmissão de dados por fios, aplicações INTERNET, áudio, vídeo, controle de robôs, acionamentos, etc.

Neste ponto pode caber a pergunta: por que tratarmos os sinais como digitais, se não são desta natureza? Diversos são os motivos que levam um projetista a escolher uma tecnologia em detrimento a outra. Mas podemos partir de um princípio que a eletrônica digital permite uma maior capacidade de adaptação (haja visto que muitas das modificações podem ser feitas via *software*) e uma maior possibilidade de implementação de técnicas e leis de controle antes presentes somente em laboratórios de pesquisa.

#### 1.3 Formatos numéricos em um processador DSP

O formato numérico de um processador está ligado a forma como são armazenados e manipulados os dados em sua arquitetura interna. Os dados podem ser trabalhados tanto no formato de **ponto fixo** quanto no formato de **ponto flutuante**. Deste modo os DSPs são divididos em duas grandes categorias, definidas pelo modo de como é tratado o formato numérico.

A representação de ponto fixo é caracterizada pelo ponto *radix* (binário) e pelo comprimento da palavra (16 *bits*, 32 *bits...*). O ponto *radix* indica o modo de como a palavra binária é escalonada. Os números de ponto fixo podem, ainda, serem subdivididos em:

- Representação com sinal e representação sem sinal;

- Representação por números inteiros e representação fracionária.

A principal diferença entre os números do formato de ponto fixo é o seu ponto radix. Por intermédio deste é que se faz o escalonamento da representação numérica. Ele equivale a uma constante (sempre uma potência de dois) que multiplica o valor numérico da palavra.

Na representação de números inteiro sem sinal, o valor armazenado em um processador de 16 *bits* pode tomar qualquer valor entre 0 e 65535. Similarmente, a representação de números inteiros com sinal utiliza o complemento de dois para poder incluir a escala de números negativos, de –32768 a 32767, neste caso o *bit* mais significativo (MSB) é usado para representar o sinal. Com notação fracional sem sinal e *radix* 15, os 65535 níveis são divididos uniformemente entre 0 e 1. E por último, a notação fracional com sinal e *radix* 15 permite a representação de números negativos, igualmente espaçados entre –1 e 1.

Os dados, do tipo ponto flutuante, são caracterizados por um campo para a mantissa (ou fração), um campo para o expoente e um *bit* de sinal. A principal norma que define estes formatos é a IEEE 754.

Os DSPs de ponto flutuante, tipicamente, usam um mínimo de 32 bits para armazenar cada valor. Isto resulta em um número maior de bits para representação do que no ponto fixo,  $2^{32} = 4.294.968.296$ , para ser exato. Um ponto importante a ser ressaltado sobre a notação de ponto flutuante é que os números representados não são uniformemente espaçados. No formato mais comum (ANSI/IEEE Std. 754-1985), o maior e o menor número são  $\pm 3.4 \times 10^{38}$  e  $\pm 1.2 \times 10^{-38}$ , respectivamente.

Aqui cabe uma ressalva. O fato do processador trabalhar com um tipo específico de dado (ponto fixo ou ponto flutuante) não o impede de trabalhar com o outro tipo de dado. Os DSPs de ponto fixo podem manusear dados de ponto flutuante, somente que, isto deve ser feito por *software* e não mais por *hardware* (como nos DSPs de ponto flutuante) o que acaba onerando a programação e o tempo de execução.

Já nos processadores de ponto flutuante o *hardware* está adaptado para trabalhar com os dois formatos, porém, necessitam de um conjunto de instruções maior do que nos processadores de ponto fixo. Isto se faz necessário devido à necessidade de se usar contadores, laços e os próprios sinais provenientes dos ADC que trabalham com números no formato de ponto fixo tornando necessária instruções que também manipulem este tipo

de dados.

A vantagem do tratamento do dado como ponto flutuante é que este possui uma melhor precisão e uma escala dinâmica maior do que o equivalente em ponto fixo, além de não haver uma real necessidade de se preocupar com fenômenos associados ao formato de ponto fixo, tais como, *underflow*, *overflow* e erros de arredondamento.

A principal vantagem do formato de ponto fixo está no custo. Pelo *hardware* ser mais "simples", seu custo, usualmente, é bem menor do que o de um processador de ponto flutuante.

A diferença chave entre os processadores de ponto fixo e de ponto flutuante está ligado ao desempenho de ambos em relação a uma característica: relação sinal-ruído. A representação por palavras binárias só é possível para um determinado conjunto de valores. Se o número não coincidir com um destes valores este será arredondado, inserindo um ruído denominado de **ruído de quantização**.

No formato de ponto flutuante, o espaço existente entre dois números adjacentes é muito menor do que aquele que há no formato de ponto fixo, ou seja, adiciona-se um ruído de quantização muito maior nos processadores de ponto fixo.

Para melhorar o desempenho quanto a relação sinal-ruído, os processadores de ponto fixo geralmente trabalham com acumuladores de precisão estendida (2 a 3 vezes o comprimento da palavra de dados) para que não haja perda da relação sinal-ruído. Esta escala estendida, virtualmente, elimina ruído de arredondamento enquanto a acumulação está em progresso. O único erro de arredondamento que ocorre é quando este valor é armazenado em uma memória de 16 bits.

Por ter menor ruído de quantização, sistemas de ponto flutuante também são mais fáceis de serem projetados. Muitas das técnicas DSP (processamento de sinais digitais) são baseadas na repetição de multiplicações e adições. Em ponto fixo, a possibilidade de *overflow/underflow* precisa ser considerada em cada operação. Deve-se conhecer a amplitude dos números, como os erros de quantização são acumulados e que escalonamento é necessário. Em comparação, estas necessidades não surgem em ponto flutuante (com raras exceções).

Neste ponto é necessário abordar uma questão: qual formato numérico trabalhar? Segundo Smith [9], há alguns pontos para se considerar:

- 1. Verificar quantos bits são usados no ADC ou DAC. Em muitas aplicações, 12-14 bits por amostra é o ponto de cruzamento entre o formato de ponto fixo e de ponto flutuante. Por exemplo, sinais de televisão e de vídeo tipicamente usam um ADC e ou DAC de 8 bits e a precisão de ponto fixo é aceitável. Em contrapartida nas aplicações de áudio profissional podem ser requeridas amostras de 20 ou 24 bits, e quase certamente necessita-se de ponto flutuante para poder manusear a larga escala dinâmica.

- 2. Verificar a complexidade do algoritmo a ser implementado. Se é relativamente simples, pode-se trabalhar no formato de ponto fixo; se é muito complicado pode-se utilizar formato de ponto flutuante. Por exemplo, um filtro FIR e outras operações no domínio do tempo somente requerem umas poucas dezenas de linhas de código, inclinando-se para lógica de ponto fixo. Em contraste, os algoritmos no domínio da freqüência, como um analisador de espectro e a convolução FFT, são muito detalhados e podem ser muitos difíceis de serem escritos em lógica de ponto fixo. O tempo de desenvolvimento pode ser reduzido utilizando-se a lógica de ponto flutuante.

- 3. Verificar a implicação de custo. Quando escolhe-se o formato de ponto fixo, o custo do produto irá ser reduzido mas o custo de desenvolvimento cresce em comparação ao de formato de ponto flutuante. De modo contrário, o sistema de ponto flutuante terá um ciclo de desenvolvimento mais barato, mas um produto final mais caro.

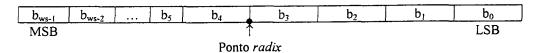

#### 1.3.1 Ponto fixo

Uma representação comum para os números binários de ponto fixo é dada na Fig. 1.3. O formato é caracterizado pelo comprimento da palavra (número de bits) e pelo ponto radix.

Fig. 1.3 - Representação de um número no formato de ponto fixo.

onde:

b<sub>i</sub> = dígitos binários (bits).

- ws = tamanho da palavra em bits.

- MSB = bit mais significativo é o bit mais a esquerda, representado pela locação b<sub>ws-1</sub>.

- LSB = bit menos significativo é o bit mais a direita, representado pela locação b<sub>0</sub>.

- ponto radix (binário) é mostrado quatro posições da direita para esquerda.

O ponto *radix* pode ser interpretado como sendo a forma com que o dado será escalonado, ou seja, pode ser entendido como um fator de escala, que é sempre uma potência de dois, multiplicando o dado para melhor adequá-lo a representação adotada. O ponto *radix* é geralmente usado na programação, pois os circuitos lógicos do processador realizam todas as funções matemáticas (soma, subtração, multiplicação...) como se o número tivesse um ponto *radix* constante (a direita do LSB).

Um esquema que pode ser utilizado para efetuar a conversão é o modelo de *slope/bias*. *Slope* significa que o dado será multiplicado por uma constante (potência de dois) que modificará a inclinação de modo a ocupar mais convenientemente a escala numérica do padrão de *bits* adotado. *Bias* representa um *offset* do dado. É efetuado quando se deseja cobrir números que estão fora do padrão adotado. Esse esquema é matematicamente representado pela Eq. 1.1.

$$V \approx \widetilde{V} = S \times Q + B \tag{1.1}$$

onde:

- V é um valor real.

- $\widetilde{V}$  é um valor aproximado.

- Q é um número inteiro que codifica V.

- $S = F \times 2^E$  é a inclinação (slope).

- B é o offset (bias).

A inclinação é dividida em duas partes:

- $2^E$  especifica o ponto *radix*. E é o expoente da potência de dois.

- F é a inclinação fracional. É normalizado tal que  $1 \le F \le 2$ .

Tanto S quanto B são constantes e não representam diretamente o hardware do processador. Trabalha-se somente com o valor quantizado Q. São usados somente para

interpretar os valores do "mundo real" na linguagem de ponto fixo da máquina.

Neste trabalho, utilizar-se-á somente o escalonamento do ponto *radix*. Deste modo:

$$B = 0 ag{1.2}$$

$$F = 1 \tag{1.3}$$

Assim:

$$V \approx \widetilde{V} = 2^E \times Q \tag{1.4}$$

Ou seja, o escalonamento de um número do "mundo real" é definido somente pela inclinação ou melhor, pelo ponto *radix*.

A representação de formato de ponto fixo com *radix* 0 é usada para armazenar números inteiros, positivos e negativos: ...-3, -2, -1, 0, 1, 2, 3.... Como exemplo, pode-se analisar o caso de um processador de 16 *bits*. No caso mais simples, existem  $2^{16} = 65536$  possibilidades de representação, que são equivalentes aos números 0 à 65535. Denominase formato de números inteiros sem sinal. A conversão entre o modelo de *bits* e o equivalente decimal é apenas uma conversão de base (decimal para binária). A desvantagem é que números negativos não podem ser representados.

Um dos modos de representar os números negativos é por intermédio de um offset binário, que é similar ao formato de números inteiros sem sinal, exceto que os valores decimais são deslocados para permitir valores negativos. Deste modo, uma representação de 16 bits pode usar um offset de 32767 resultando em uma escala de -32767 a 32768. Offset binário não é um formato padronizado e pode-se encontrar qualquer valor de offset em uso, como 32768, por exemplo. É mais usado na conversão ADC ou DAC.

Outro método para representação de números negativos é o método de **sinal e amplitude**. O *bit* mais a esquerda (MSB) é chamado de *bit* de sinal, sendo zero quando o número for positivo e um para números negativos. Isto resulta em um padrão perdido, haja visto que possuí dois zeros, o zero positivo (0000h) e o zero negativo (1000h). Este esquema de codificação resulta em números de 16 *bits* com uma escala de –32767 até 32767.

Embora sejam simples, estas representações são de difícil implementação em hardware. O formato mais comum adotado para representação de números negativos é o complemento de dois. Este método facilita o projeto do hardware do processador que é

um circuito eletrônico que modela as funções matemáticas necessárias como por exemplo, tendo um dado A e outro B como entradas constrói-se um circuito lógico que resulta na sua saída C, tal que:

$$A + B = C \tag{1.5}$$

O **complemento de dois** é o padrão utilizado para representar os números negativos nos computadores. Para entendê-lo, toma-se o número inteiro decimal 0 (0000b). Contando-se progressivamente, o número decimal é simplesmente o equivalente binário (0 = 0000b, 1 = 0001b, 2 = 0010b...). Retornando ao número 0 (0000b) e agora subtraindo, o equipamento digital automaticamente conta no complemento de dois (0 = 0000b, -1 = 1111b, -2=1110,...).

Usando 16 *bits*, o complemento de dois pode representar números de -32768 à 32767. O *bit* mais significativo é zero se o número é positivo ou um se o número é negativo. Consequentemente o *bit* mais significativo é chamado de *bit* de sinal, assim como na representação de sinal e amplitude.

Um ponto em questão no momento é como efetivamente usar o que até então foi explanado para representação numérica em um processador, tanto de números fracionais, como inteiros, positivos e ou negativos. Inicialmente, números fracionais são representados nos DSPs em um formato de ponto fixo na forma de complemento de dois. A TI™ (Texas Instrument) adota a simbologia denominada de formato Q, a qual será usada daqui por diante por ter-se trabalhado com um processador fabricado por esta empresa.

No formato Qn, o n significa o número de bits a direita do ponto binário (radix). Assim, uma palavra de 16-bits tem um bit de sinal, 15 - n bits inteiros e n bits fracionais. O número binário 1100000000000001b pode ser interpretado, por exemplo, como segue:

Q0:

$$1100000000000001b = -2^{15} + 2^{14} + 2^{0} = -16383$$

Q14:

$$11.000000000000001b = -2^1 + 2^0 + 2^{-14} = -0,9999389648438$$

Q15:

$$1.1000000000000001b = -2^0 + 2^{-1} + 2^{-15} = -0,4999694824219$$

discretos, definidos por intervalos regulares, o que condiciona o arredondamento quando um número não se enquadra a um destes estados.

Baseado na tabela 1, pode-se escolher o formato Qn para representar o número decimal. O número deve estar contido dentro da escala do formato adotado. Para realizar a conversão de um valor fracional decimal positivo para o formato Qn escolhido pode-se utilizar a seguinte fórmula:

$$Q_n = (N_d \times 2^n)_d \tag{1.6}$$

onde:

$Q_n = número no formato Qn;$

$N_d$  = número decimal que se deseja converter;

n = formato do número representado (posição do ponto radix).

Tabela 1 – Escala do formato Qn para uma palavra de 16 bits com sinal.

| n(Qn) | Valor mínimo | Valor máximo   |

|-------|--------------|----------------|

| 0     | -32768       | 32767          |

| 1     | -16384       | 16383,5        |

| 2     | - 8192       | 8191,75        |

| 3     | -4096        | 4095,875       |

| 4     | -2048        | 2047,9375      |

| 5     | -1024        | 1023,84375     |

| 6     | -512         | 511,984375     |

| 7     | -256         | 255,9296875    |

| 8     | -128         | 127,87109375   |

| 9     | -64          | 63,998046875   |

| 10    | -32          | 31,9990234375  |

| 11    | -16          | 15,99951171875 |

| 12    | -8           | 7,999755859375 |

| 13    | -4           | 3,999877929687 |

| 14    | -2           | 1,999938964843 |

| 15    | -1           | 0,999969482421 |

O resultado ainda está no formato decimal, não sendo necessário convertê-lo aos formatos hexadecimal e ou binário, pois o *Assembler* o faz na compilação do programa. Do mesmo modo, para representar números fracionais negativos, pode-se usar a seguinte fórmula:

$$Q_n = ((2^{16} - N_d x 2^n) + 1)_d \tag{1.7}$$

Alternativamente, para se fazer a conversão de uma palavra binária para o seu equivalente no "mundo real" pode-se usar a Eq. 1.8 para o caso de um valor de ponto fixo

sem consideração de sinal e a Eq. 1.9 para um valor considerando o sinal. Deve-se notar que é usado o sistema de representação com *slope/bias*.

$$\widetilde{V} = S \cdot \left[ \sum_{i=0}^{w_{S}-1} b_i \cdot 2^i \right] + B \tag{1.8}$$

$$\widetilde{V} = S \cdot \left[ -b_{ws-1} \cdot 2^{ws-1} + \sum_{i=0}^{ws-2} b_i \cdot 2^i \right] + B$$

(1.9)

V = é um valor aproximado.

$S = F \times 2^{E}$  é a inclinação (slope).

$B = \acute{e} \circ offset (bias).$

ws = é o comprimento da palavra.

bi = é o bit em questão da palavra.

#### 1.3.2 Ponto Flutuante

A representação de ponto fixo é limitada quando se trata de representar uma escala com grandes variações e nas quais é necessário representar números muito pequenos e extremamente grandes. Isto pode ser contornado usando a notação científica, podendo relocar, dinamicamente, o ponto *radix* à posição mais conveniente, de modo a melhor representar o número, a medida que as operações são efetuadas.

Este é um sistema mais complicado do que o esquema usado na representação de ponto fixo. A idéia básica é a mesma usada na notação científica, onde uma **mantissa** é multiplicada por 10 elevado a algum **expoente**. Por exemplo, 5,4321 x 10<sup>6</sup>, 5,4321 é a mantissa e 6 é o expoente. Notar que os números representados na notação científica são normalizados até que haja somente um único dígito não nulo à esquerda da vírgula. Isto é obtido ajustando o expoente adequadamente.

A representação de ponto flutuante é similar a notação científica, exceto que é apresentada na base 2, ao invés da base 10. A forma de representar é dada pela Eq. 1.10.

$$\widetilde{V} = \pm f \times 2^{\pm e} \tag{1.10}$$

Embora haja diversos formatos similares em uso, o mais comum é ANSI/IEEE Std. 754-1985. Este padrão define o formato de números de 32 bits chamados de precisão

simples, assim como os números de 64 bits, chamados de dupla precisão. Os 32 bits usados na precisão simples são divididos em três grupos separados: bits 0 até 22 formam a mantissa, bits 23 até 30 formam o expoente, e o bit 31 é o bit de sinal. Estes bits formam o número no formato de ponto flutuante, v, dado pela seguinte relação:

$$v = (-1)^S x M x 2^{E - 127}$$

(1.11)

O termo (-1)<sup>S</sup>, simplesmente significa o *bit* de sinal, S é zero para números positivos e um para números negativos. A variável, E, é um número entre 0 e 255 representando os oito *bits* do expoente. Subtraindo 127 deste número, permite que o expoente varie de -127 à 128. Em outras palavras o expoente é armazenado com um *offset binário* de 127. A mantissa, M, é formada de 23 *bits* como uma fração binária.

Usando este esquema, o maior e o menor número representáveis são, respectivamente:  $\pm$  6,8 x  $10^{38}$  e  $\pm$  5.9 x  $10^{-39}$ . O padrão IEEE reduz esta escala para permitir que determinados padrões obtenham significados especiais. Em particular o maior número e o menor número permitidos pelo padrão são:  $\pm$  3,4 x  $10^{38}$  e  $\pm$  1,2 x  $10^{-39}$ , respectivamente. Os padrões não usados permitem três casos especiais de classes de números:

- (1)  $\pm 0$  é definido como todos os *bits* da mantissa e do expoente sendo zeros.

- (2) ±∞ é definido como todos os *bits* da mantissa sendo zeros e todos os *bits* de expoente sendo uns.

- (3) Um grupo de números muito pequenos não normalizados entre ± 1,2 x 10<sup>-38</sup> e ± 1,4 x 10<sup>-45</sup>. Estes são números de menor precisão obtidos pela remoção da restrição de que o primeiro dígito da mantissa seja um. Além destas três classes especiais, há o modelo de *bits* que não é dado nenhum significado, comumente referidos como NANs (*not a number*).

O padrão IEEE para dupla precisão simplesmente adiciona mais *bits*, tanto para a mantissa quanto para o expoente. Dos 64 *bits* usados para armazenar o número com dupla precisão, os *bits* de 0 à 51 são a mantissa, os *bits* de 52 até 62 são o expoente e o *bit* 63 e o *bit* de sinal. Como antes, a mantissa está entre 1 e 2. O expoente de 11 *bits* forma um número entre 0 e 2047, com um *offset* de 1023, permitindo expoentes de -1023 à 1024. O maior número representável e o menor número representável são:  $\pm 1.8 \times 10^{308}$  e  $\pm 2.2 \times 10^{-308}$ , respectivamente.

#### 1.4 A família TMS320

O primeiro processador desta família foi fabricado em 1982, quando a Texas Instrument lançou no mercado o TMS32010, o primeiro DSP de ponto fixo da família TMS320. Consiste de **processadores** de sinais digitais (DSPs) de ponto fixo, ponto flutuante e multiprocessamento e de **controladores** DSP.

Atualmente a família TMS320 é constituída pelas seguintes gerações: 'C1x,'C2x, 'C24x, 'C5x, 'C54x e 'C6x, para DSPs de ponto fixo; 'C3x e 'C4x, para DSPs de ponto flutuante, e 'C8x para multiprocessadores DSP. Existem três plataformas principais e estas são:

- 1. Plataforma 'C2000;

- 2. Plataforma 'C5000 e

- 3. Plataforma 'C6000.

Componentes dentro de uma mesma plataforma da família TMS320 compartilham o mesmo núcleo DSP, mas diferentes configurações de memória interna e periféricos.

Cada plataforma apresenta características otimizadas a um determinado grupo de aplicações. Deste modo, por exemplo, a plataforma 'C2000 é mais apropriada à aplicações de sistemas de controle em geral. A plataforma 'C5000 é otimizada para produtos portáteis e de baixo consumo. A plataforma 'C6000 é otimizada para um alto desempenho de processamento para aplicações que exijam uma alta capacidade de processamento, como áudio, por exemplo.

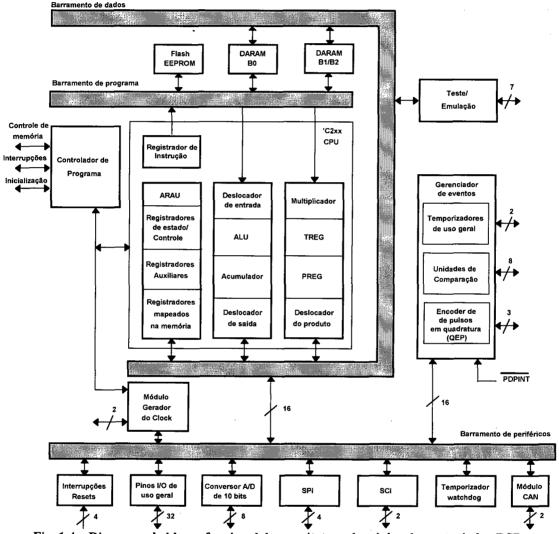

#### 1.4.1 TMS320F243

É um controlador DSP de ponto fixo de 16 bits que pertence a plataforma 'C2000. Tanto o núcleo quanto os periféricos são otimizados para serem utilizados em projetos de controle de motores e de movimentos. As principais características deste componente são:

- Interface para memória externa;

- Módulo gerenciador de eventos;

- ❖ Oito canais de modulação de largura de pulso

#### (PWM)/comparador;

- Dois temporizadores de uso geral de 16 bits com quatro modos de operação;

- Três unidades de comparação completa com tempo morto;

- Três unidades de captura (duas com possibilidade de *interface* com um *encoder* de pulso em quadratura);

Fig. 1.4 – Diagrama de blocos funcional da arquitetura do núcleo do controlador DSP.

- Um conversor analógico digital de 10 bits (ADC) com uma entrada multiplexada de oito canais;

- Um módulo de controlador de rede local CAN (Controler Area Network);

- 26 pinos individualmente programados de uso genérico I/O (GPIO);

- Pulsos de *clock* do sistema baseados em um módulo PLL;

- Módulo temporizador watchdog;

- Módulo de interface de comunicação serial (SCI);

- Módulo de interface periférico serial (SPI);

- Cinco interrupções externas (power drive protection, reset, NMI e duas interrupções mascaráveis);

- Três modos de baixo consumo;

- Memória:

- ❖ 544 palavras de 16 bits de memória RAM de dados/programa interna de acesso duplo (DARAM);

- ❖ 8k de palavras de 16 bits de memória FLASH EEPROM

- ❖ 224k de palavras de 16 bits de memória total.

### 1.4.1.1 Arquitetura interna

É baseada no modelo *Harward* modificado, que suporta barramentos separados para o programa e para os dados. Um terceiro (entrada/saída), é também disponível e acessível através de um barramento de *interface* externa. Por suportar uma grande quantidade de periféricos, é usado um barramento para estes. Isto permite que haja acesso simultâneo de dados e instruções de programa. Por exemplo, enquanto um dado é multiplicado, um produto prévio pode ser adicionado ao acumulador, e ao mesmo tempo, um novo endereço pode ser gerado. Devido a este paralelismo, o componente suporta uma série de instruções aritméticas, lógicas e manipulação de *bits*, que podem ser efetuados em um único ciclo de *clock*. Possui ainda mecanismos de gerenciamento de interrupções, repetição de operações e chamada de funções/subrotinas.

O bloco funcional é apresentado na Fig. 1.4 e dá uma boa descrição do componente. É composto de três blocos principais: núcleo DSP, memória interna e periféricos. Em adição a estas, há diversos sistemas e características distribuídas. A isto incluem-se: registradores mapeados na memória, reinicializações, interrupções,

entradas/saídas digitais, geração de pulso de clock e modo de operação de baixo consumo.

#### 1.4.1.2 Interrupções

Interrupções são geradas por componentes que precisam enviar ou buscar alguma informação do núcleo DSP como, por exemplo, conversores A/D e outros processadores digitais de sinal. Quando ocorre o reconhecimento da interrupção, suspende-se a execução do código específico e executa-se uma seqüência de instruções ligadas ao evento que gerou a interrupção.

O processador digital de sinais TMS320F243 contém muitas interrupções de periféricos internos, cada uma capaz de gerar múltiplas interrupções em resposta a cada evento. A CPU suporta uma interrupção não mascarada (não pode ser desabilitada) e seis interrupções mascaradas e não manipula diretamente as requisições de interrupção. Devido a isto utiliza-se um controlador de interrupções centralizado para arbitrar sobre elas, denominado Expansão de Controle de Periféricos (PIE – *Peripherical Interface Expansion*).

A PIE gerencia todas as requisições de interrupção dos periféricos. É conectado entre os periféricos, a CPU e os barramentos de endereços e informações. Contém três registradores:

- PIRQ Peripherical Interrupt Request Detecta e grava qualquer requisição de interrupção dos periféricos.

- PIVR Peripherical Interrupt Vector Register Contém o vetor de interrupção da requisição mais recente e que foi reconhecida.

- PIACK Peripherical Interrupt Acknowledge Envia o reconhecimento da interrupção para os periféricos.

O nível de prioridade da interrupção é programado em alguns casos. As interrupções do ADC, SCI, SPI, CAN e as interrupções externas podem ser configuradas para serem de alta prioridade e ou de baixa prioridade para o controlador PIE. Em cada periférico, um *bit* de indicação de interrupção e um *bit* de habilitação (máscara) irão causar uma requisição de interrupção no módulo PIE. Esta requisição simplesmente reflete o estado do periférico. A requisição pode ser apagada reconhecendo-a e ou pelo programa

(escrevendo 1 no indicador correspondente no periférico). Se nenhuma requisição de interrupção, não reconhecida pela CPU, de mesma prioridade foi previamente transmitida, um sinal de interrupção é gerado e transmitido a CPU quando a PIRQ estiver ativa. A interrupção requerida, irá ativar o *bit* correspondente no registro de indicadores de interrupção (IFR). Se a interrupção da CPU estiver habilitada por um *bit* apropriado no registrador de máscara de interrupção (IMR) e se o *bit* INTM estiver em zero a CPU reconhecerá a interrupção.

Depois de aceita a requisição, a CPU envia ao módulo PIE um sinal de reconhecimento de interrupção e um valor no barramento de endereços de programa (PAB), que corresponde ao nível de interrupção que está sendo respondida. O PIE decodifica este valor e reconhece qual requisição de interrupção foi reconhecida, enviando ao periférico um sinal de reconhecimento de interrupção (PIACK). Este sinal será usado pelo periférico para limpar o indicador de interrupção.

Quando uma interrupção é reconhecida, o controlador PIE carrega o vetor de interrupção de periféricos dentro do registrador do vetor de interrupção de periféricos (PIVR) com o valor armazenado na tabela. Então, a rotina de interrupção de serviço genérica (GISR) salva os conteúdos necessários e lê o valor do PIVR. Em seguida executa um salto para um local da memória apropriado que contém a rotina de interrupção de serviço específica, usando o vetor como base para localizar o endereço.

As referências [13] e [14] fazem uma abordagem sobre como tratar as interrupções. As interrupções não usadas devem prover um salto para uma rotina fantasma, pois caso haja algum imprevisto, não se perde o controle do processo.

#### 1.4.1.3 Gerenciador de eventos

Há dois temporizadores de uso genérico no gerenciador de eventos do 'F243. Estes podem ser usados como base de tempo independentes em aplicações como:

- Geração do período de amostragem em um sistema de controle.

- Propiciar uma base de tempo para processamento de sinal do sensor decodificador em quadratura em um sistema de controle de um motor.

- Fornecer uma base de tempo para os comparadores de ação completa e circuitos

PWM associados para gerar saídas PWM em um sistema de controle de um motor.

• Servir como base de tempo para monitorar o intervalo entre dois eventos externos ao processador por intermédio do circuito de captura.

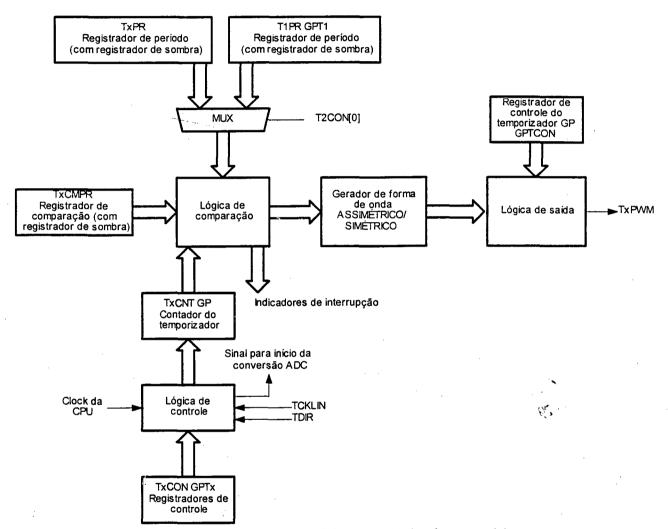

Na Fig. 1.5 tem-se o diagrama de blocos funcional de um temporizador de uso genérico, que resumidamente contém:

Fig. 1.5 - Diagrama de blocos funcional do temporizador de uso genérico.

- Um registrador que armazena o valor de contagem (UP/DOWN), TxCNT (x = 1,2). Armazena o valor corrente da contagem e incrementam ou decrementam a cada *clock* de acordo com o modo de contagem selecionado.

- Um registrador de comparação, TxCMPR (x = 1,2), duplicado o que permite que a recarga seja programada por diferentes eventos.

- Um registrador de período, TxPR (x = 1,2), duplicado.

- Um registrador de controle individual, TxCON (x = 1,2).

- Divisor do número de *clock*s programável para pulsos gerados internamente e ou externamente.

- Lógica de controle de interrupção.

- Um pino de saída do comparador, TxCMP (x=1,2).

- Lógica de saída programável.

Um registrador de controle genérico (GPTCON) especifica a ação a ser tomada pelos temporizadores nos diferentes eventos de temporização e indica a direção de contagem dos temporizadores:

São quatro, os modos de funcionamento dos temporizadores:

- Modo de contagem pára/mantém.

- Modo de contagem contínua crescente.

- Modo de contagem contínua crescente/decrescente.

- Modo de contagem direcional crescente/decrescente.

Cada temporizador pode ser programado para, independentemente, fornecer uma saída PWM. Para se criar uma saída PWM (assimétrica ou simétrica) deve-se parametrizar os seguintes registradores:

- TxPR em acordo com a frequência da portadora (frequência PWM).

- TxCON para especificar o modo de contagem e a fonte de clock e o início da operação.

- TxCMPR com o valor da razão cíclica calculado em tempo real.

Além destes existem outros registradores que devem ser configurados para se obter a característica desejada do GP (temporizador de uso genérico), sendo eles o GPTCON, EVIFRA, EVIFRB, EVIFRC, EVIMRA, EVIMRB e EVIMRC. Estes são registradores de controle das interrupções e de controle de funções comuns aos dois temporizadores (GPTCON).

A unidade de comparação é composta de seis comparadores que podem ser configurados para gerarem três saídas PWM (assimétricas ou simétricas) com

complemento, que podem ser usadas para acionamento de motores. A base de tempo para está unidade só pode ser obtida do temporizador um. O gerenciador de eventos ainda possui:

- Três registradores de comparação, duplicados, CMPRx (x = 1, 2 e 3).

- Um registrador de controle de comparação (COMCON).

- Um registrador de controle de ação (ACTR), duplicado.

- Seis pinos de saída PWM.

- Lógica de controle e interrupção.

A operação pode ser descrita da seguinte forma: o valor do contador do temporizador um é continuamente comparado com o valor do registrador de comparação. Quando os dois valores se igualam, uma transição ocorre nas duas saídas da unidade de comparação de acordo com a configuração dos *bits* do registrador de controle de ação (ACTR). Os *bits* no ACTR podem individualmente especificar cada saída para comutar ativo baixo ou ativo alto (se não, forçado baixo ou forçado alto) quanto este evento ocorrer. O indicador associado com a unidade de comparação é posto em nível alto se a comparação estiver habilitada. Uma PIRQ é gerada se a interrupção não estiver mascarada. As saídas das unidades de comparação estão sujeitas à modificações pela lógica de saída, unidades de tempo morto e a lógica de vetor de espaço PWM. A seqüência de configuração dos registradores é:

#### $T1PR \Rightarrow ACTR \Rightarrow CMPRx \Rightarrow COMCON \Rightarrow T1CON$

Existem, ainda, unidades auxiliares que tornam possível gerar saídas PWM com tempo morto e por vetores de espaço. Resumidamente pode-se listar a capacidade, como um todo, do gerenciador de eventos:

- Cinco saídas PWM independentes, três associadas as geradas pelos comparadores de ação completa; as outras duas são geradas pelos comparadores dos temporizadores GP, mais três saídas dependentes das três unidades de comparação completa.

- Tempo morto programável para os pares das saídas PWM associadas com as unidades de comparação.

- Duração mínima de tempo morto de um pulso de clock.

- Mínima largura de pulso e incremento/decremento desta de um pulso de *clock*.

- Máxima resolução PWM de 16-bits.

- Mudança da frequência da portadora no funcionamento assim como da largura de pulso.

- Interrupção de proteção do circuito de potência gerada externamente.

- Geração programável de formas de onda PWM simétrica, assimétrica e vetor de espaço.

- Não há interferência da CPU na recarga dos registradores de período e comparação.

Maiores informações sobre o gerenciador de eventos podem ser encontradas na bibliografia [11 à 24] e com o fabricante do componente.

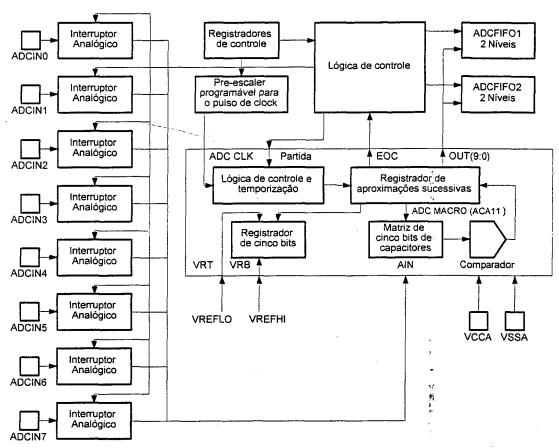

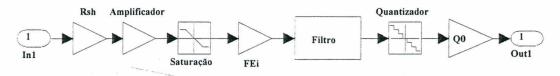

## 1.4.1.4 Conversor analógico digital pseudo-dual

O método usado para efetuar a conversão A/D é o de aproximações sucessivas. Utiliza-se um capacitor para fazer a amostragem e retenção do sinal. Diferente do F240, o F243 possui somente um conversor A/D e um único circuito de amostra e retenção. Este periférico funciona como se tivesse dois conversores, ADC1 e ADC2, mas como dito possui apenas um. Esta medida é tomada para garantir o mínimo de modificações em relação aos controladores com dois conversores A/D. Deste modo o 'F/C243 apresenta os mesmos registradores (ADCNTRL1 e ADCNTRL2, ADCFIFO1 e ADCFIFO2...) o que faz com que a programação deste periférico equivale a do 'F/C240 e permite a conversão (quase simultânea) de dois sinais analógicos. O tempo mínimo de conversão é de 850 ns a uma frequência de 20 MHz. Tensões de referência externas e internas podem ser usadas. Possui oito entradas analógicas multiplexadas. Também permite a divisão dos pulsos de *clock* e gera interrupções (com prioridade programada) quando termina a conversão de um sinal. Pode operar em conversão contínua ou conversão simples. Possui precisão de 10 *bits*.

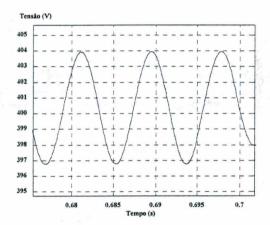

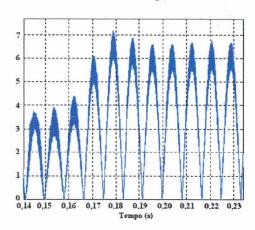

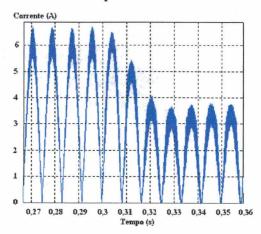

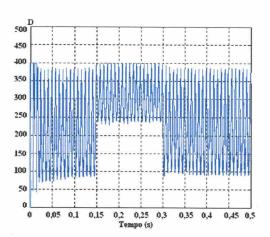

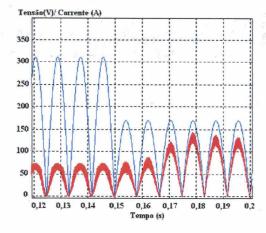

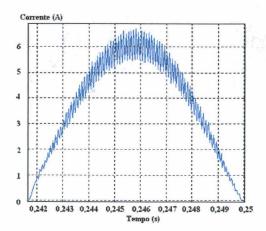

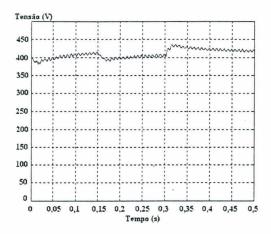

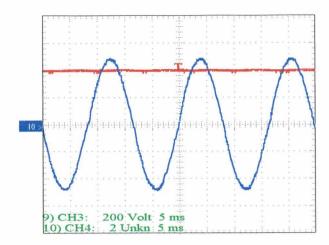

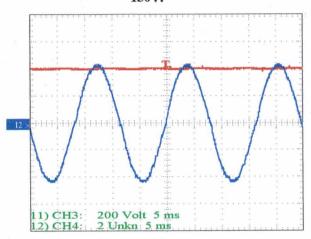

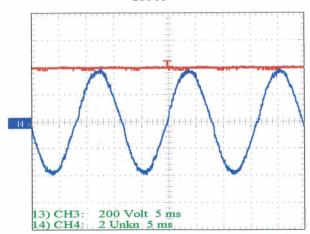

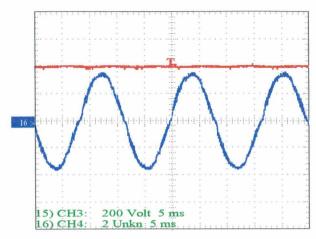

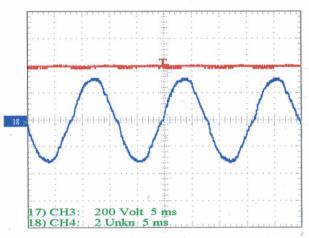

A Fig. 1.6 apresenta o diagrama de blocos funcional do conversor analógico digital. Foi elaborado um programa que realiza uma conversão a cada 20 µs a partir de uma base de tempo proveniente do temporizador 2. Ao se completar a conversão gera-se uma

interrupção que armazena o valor lido na memória de dados do controlador DSP.

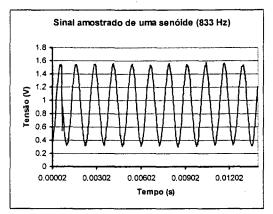

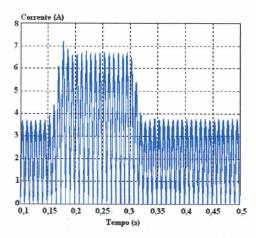

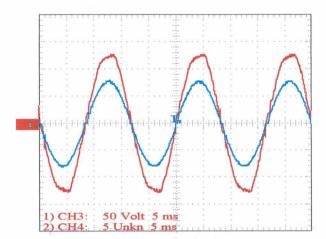

Foram efetuadas aquisições de sinais utilizando a rotina elaborada. Na Fig. 1.7 apresenta-se a aquisição de um sinal cuja forma de onda é senoidal e a frequência deste é de 833 Hz. A presença do nível DC se faz necessária pois a escala de conversão do AD é de 0 à 5V.

Fig. 1.6 - Diagrama de blocos funcional do pseudo-dual ADC.

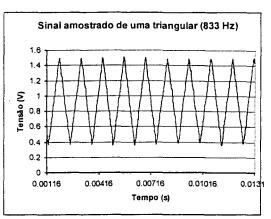

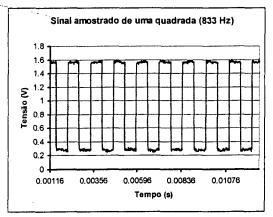

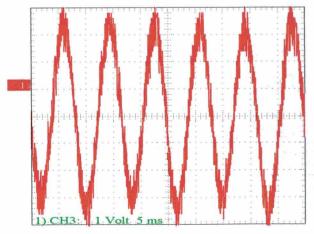

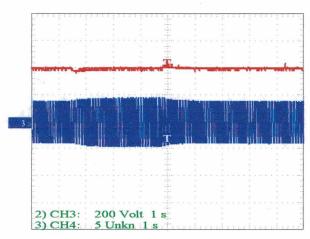

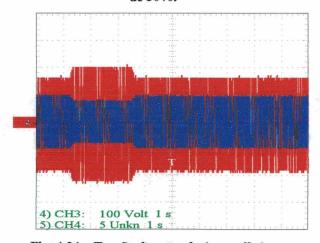

Do mesmo modo foram feitas aquisições para formas de onda triangular (Fig. 1.8) e quadrada (Fig. 1.9). As freqüências destas também foram de 833 Hz. As aquisições destas formas de onda foram efetuadas sem a inserção de um filtro e um *buffer* na entrada.

Fig. 1.7 – Aquisição de uma forma de onda senoidal de freqüência de 833Hz com freqüência de amostragem de 50KHz.

Fig. 1.8 – Aquisição de uma forma de onda triangular de freqüência de 833Hz com freqüência de amostragem de 50KHz.

Fig. 1.9 - Aquisição de uma forma de onda quadrada de frequência de 833Hz com frequência de amostragem de 50KHz.

#### 1.5 Conclusão

Este capítulo teve o escopo de ilustrar alguns pontos importantes a respeito do controlador DSP utilizado no projeto. Foi apresentado o controlador e discutido com uma determinada profundidade as principais partes, utilizadas (o EV e o AD) no trabalho desenvolvido.

Teve a finalidade, também, de mostrar como é feito o tratamento numérico dentro do controlador. Fez-se um estudo em cima dos formatos numéricos disponíveis. Dentro do projeto, como um todo, é essencial saber como se representa os ganhos calculados dentro da lógica do controlador.

Dependendo da escolha do *radix* a dinâmica do sistema pode se alterar significativamente, o que implica na necessidade da compreensão completa do sistema de representação numérica.

# 2. Projeto do Controlador Digital para o Conversor Boost Préregulador

## 2.1 Introdução

Tanto o método de projeto do conversor pré-regulador Boost quanto do controle por valores médios já são de domínio das comunidades científica e industrial e estão amplamente estudadas e apresentadas em diversas publicações [1] a [8].

O que se faz, neste trabalho, é apenas reaplicar as conclusões obtidas de um compêndio das proposições encontradas de modo a projetar um controlador digital. As regras que irão reger o projeto do controlador digital serão as mesmas que são usadas no projeto do compensador analógico. É importante ter-se em mente que, embora o tratamento matemático seja diferente, a filosofia aplicada é a mesma.

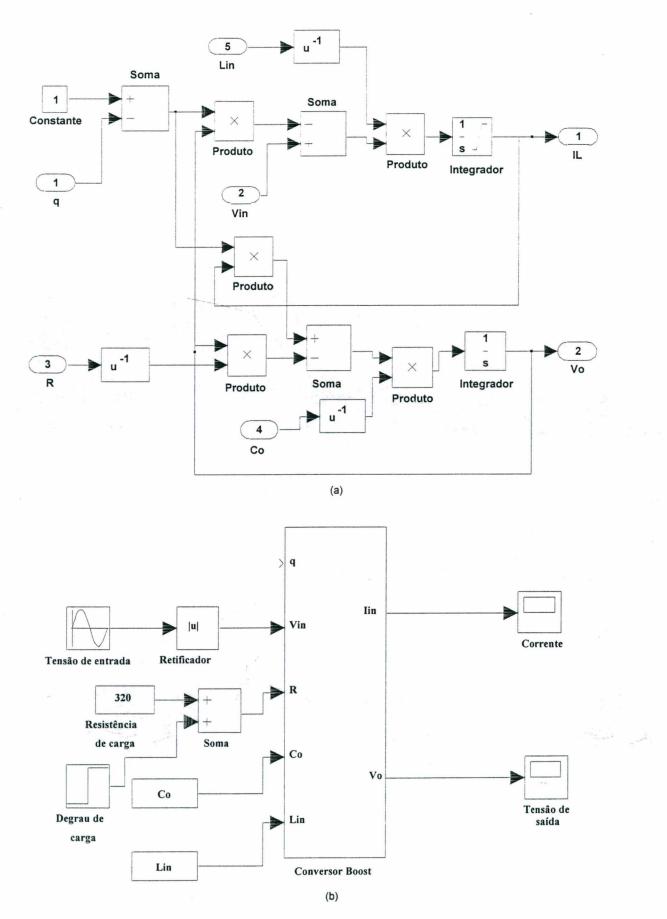

## 2.2 Descrição do método de controle utilizado

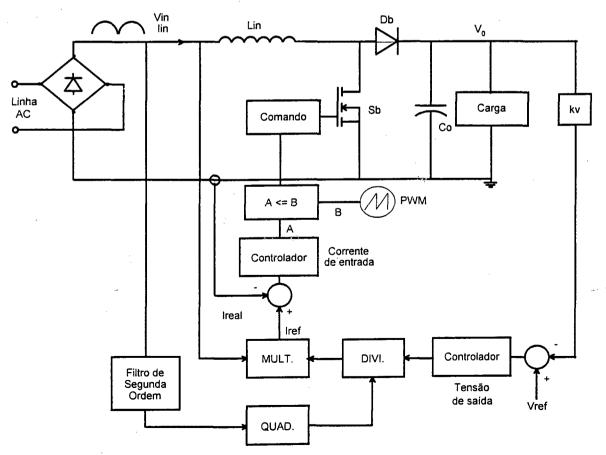

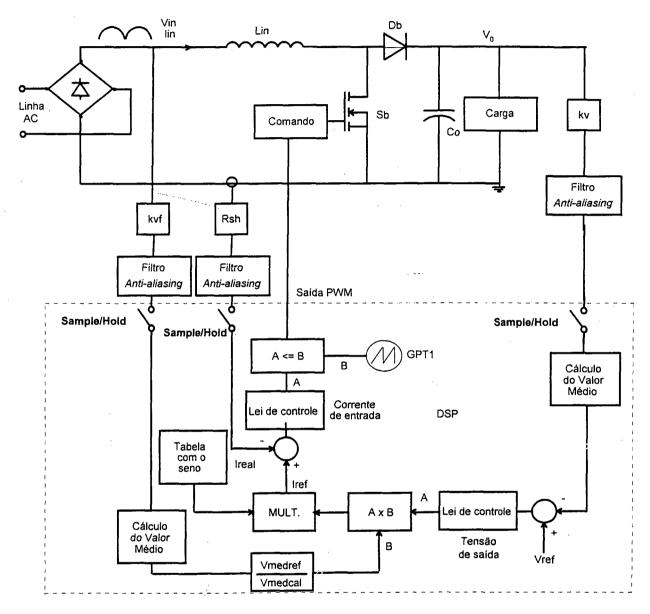

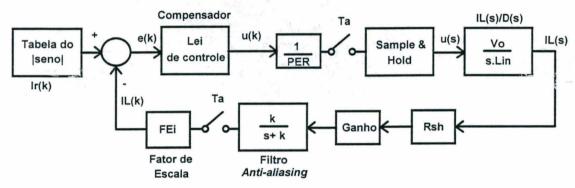

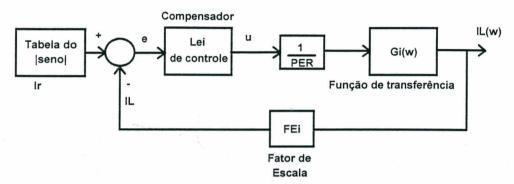

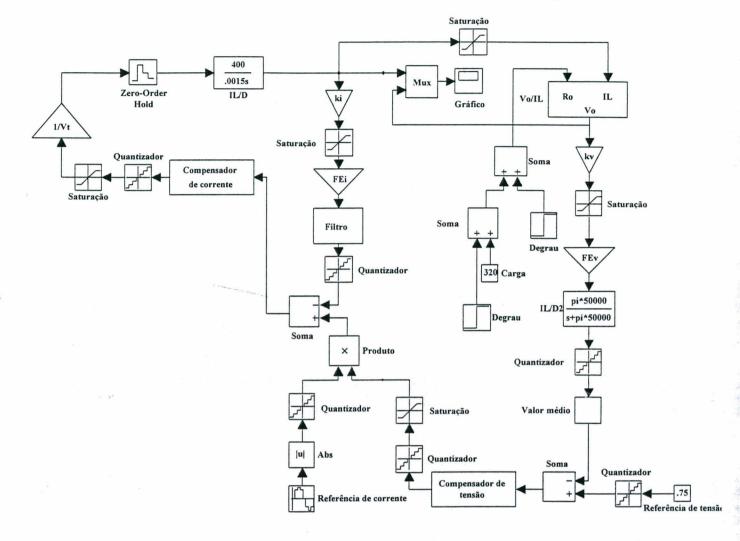

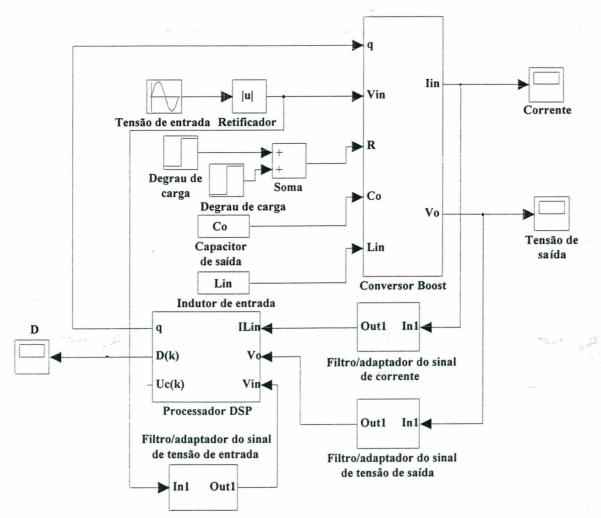

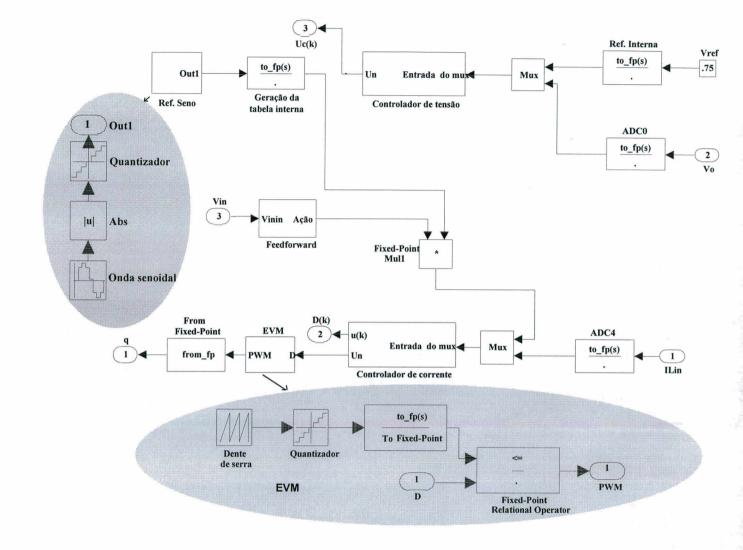

Fig. 2.1 - Diagrama de blocos do controle de um pré-regulador com alto fator de potência.

A Fig. 2.1 mostra o diagrama de blocos funcional do método de controle por valores médios de corrente (utilizado pelo controlador UC3854 da Unitrode [30]) em um conversor Boost. Esta é apenas uma representação ilustrativa, uma visão mais completa pode ser obtida dos dados fornecidos, em notas de aplicação, pelo fabricante.

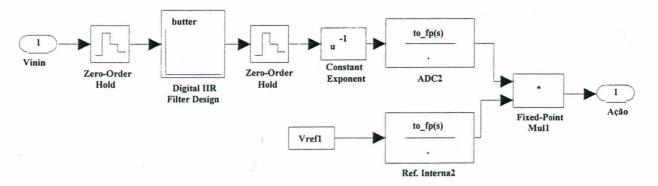

Nota-se a existência de duas malhas de controle, um laço interno de controle da corrente de entrada e um laço externo de controle da tensão de saída. O laço de corrente é programado para seguir a referência da tensão retificada. Esta referência tem sua amplitude modulada por dois sinais sendo, um proveniente do compensador de tensão e o outro da malha de controle feedforward. A tensão de saída é controlada alterando-se o valor da amplitude da corrente de entrada. Um multiplicador analógico cria a corrente de referência multiplicando a tensão de referência retificada pela ação de controle do controlador de tensão e dividindo pela ação do feedforward ao quadrado (o sinal feedforward é proveniente de um filtro de segunda ordem). Deste modo a corrente de entrada é programada para ter o formato da tensão de entrada retificada e uma amplitude que controla a tensão média de saída. O fator de divisão (feedforward) serve para corrigir as variações da tensão na carga devido aos distúrbios ou variações da tensão de entrada. Seu valor é elevado ao quadrado para tornar a referência da forma de onda inversamente proporcional à tensão de entrada - se fosse somente a tensão média (proveniente do filtro de entrada), sem elevar-se ao quadrado, o único resultado seria tornar a referência da forma de onda independente da tensão de entrada, ou seja, com amplitude constante, sem a ação de correção feedforward.

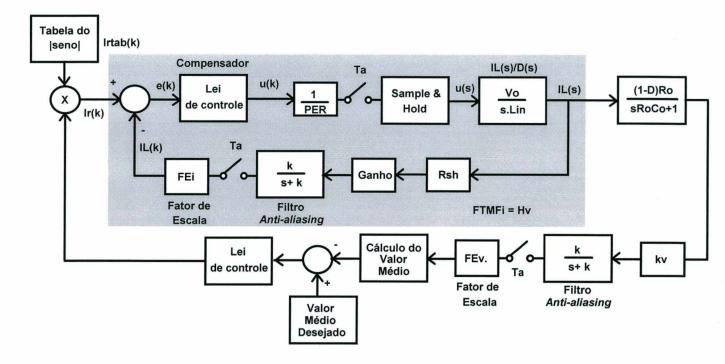

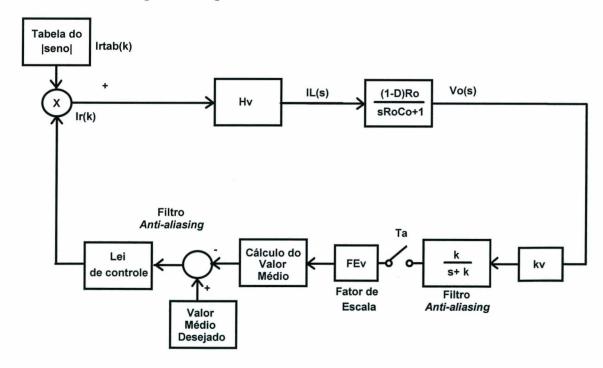

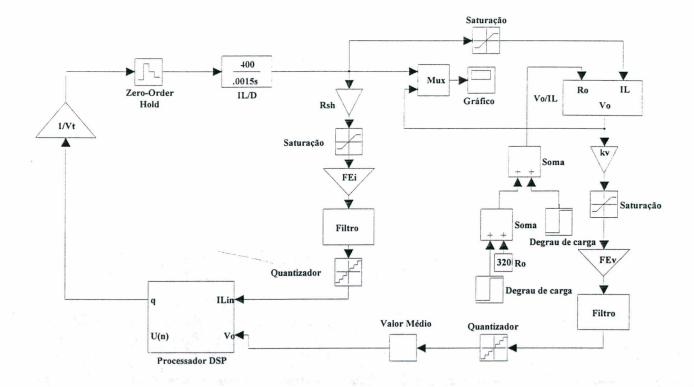

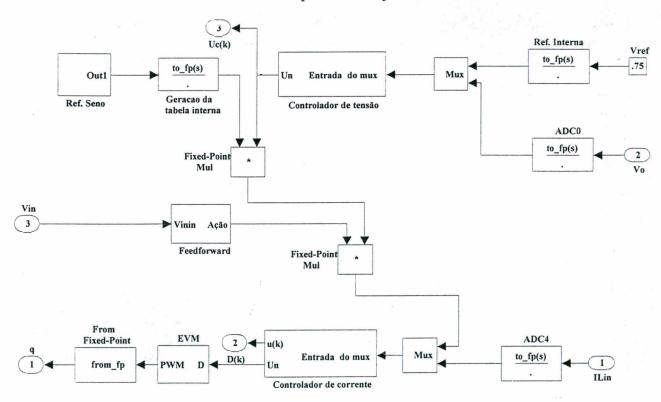

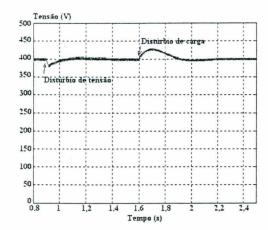

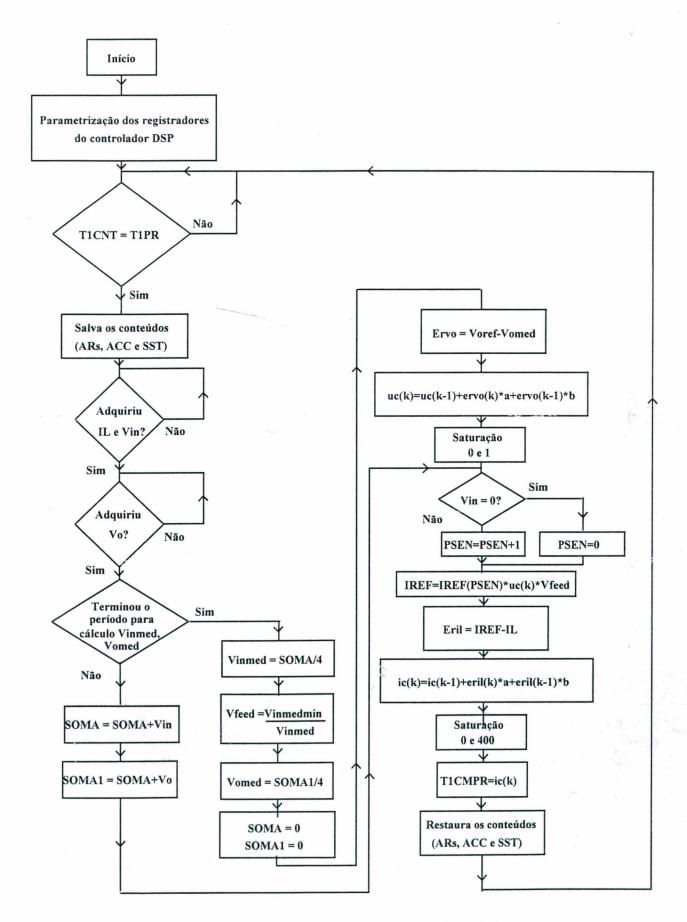

A partir do esquema acima descrito concebeu-se a forma de como controlar o conversor Boost, operando como pré-regulador, digitalmente. Mas devido às facilidades que o sistema de controle digital proporciona, fez-se algumas modificações neste esquema. Estas alterações são apresentadas na Fig. 2.2.

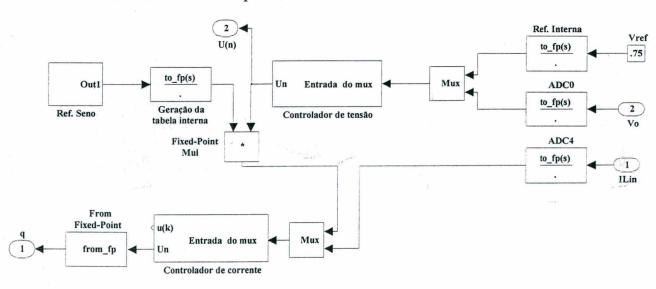

A primeira destas modificações está relacionado com a referência da forma de onda da corrente de entrada. Diferente do controlador contínuo, base para este projeto, preferiu-se impor a forma de onda a partir de uma tabela de pontos na memória de programa do controlador DSP. Deste modo há uma referência que é independente da tensão de entrada e é rigidamente uma senóide (existe uma pequena distorção, devido à natureza desta senóide, pois ela é discreta).

No controlador convencional utiliza-se a forma de onda da tensão da rede, que pode apresentar uma distorção em seu formato estendida à corrente de entrada, empobrecendo o

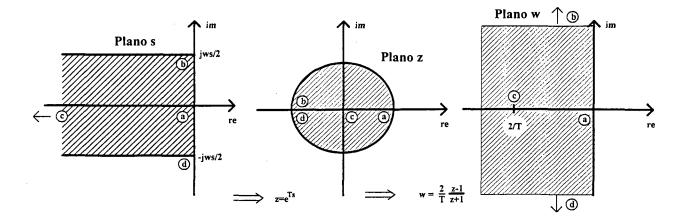

fator de potência. Outro ponto é que, usando como referência a tensão da rede, é necessário calcular o quadrado do valor médio da tensão de entrada para calcular a ação feedforward, o que implica em um aumento da complexidade do programa.

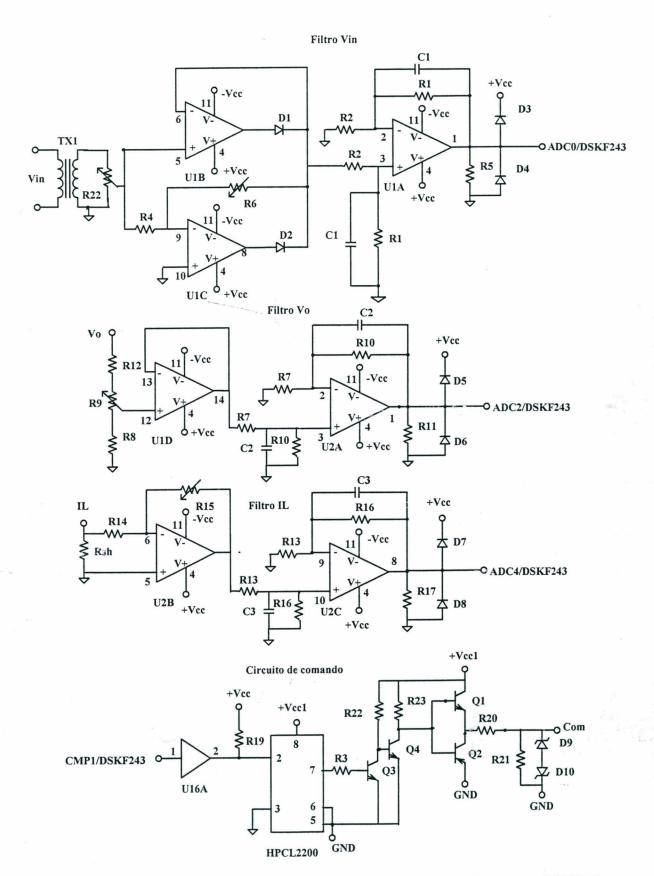

Fig. 2.2 – Diagrama em blocos funcional do controle implementado com controlador DSP em um conversor pré-regulador.

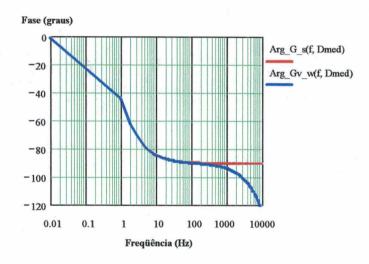

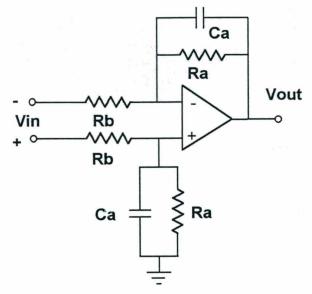

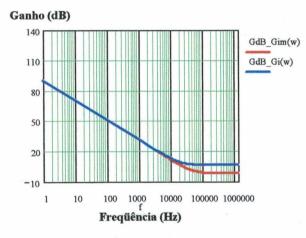

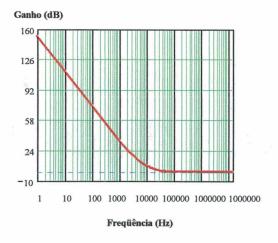

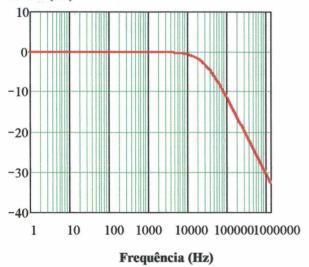

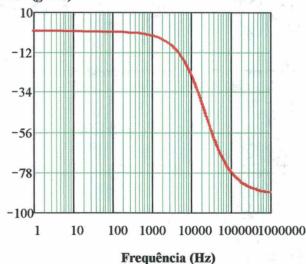

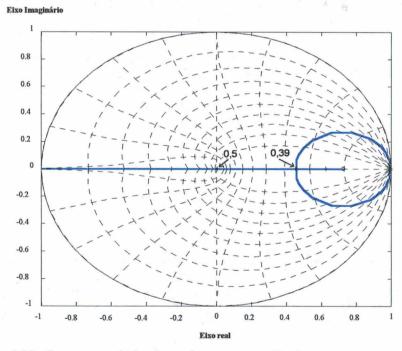

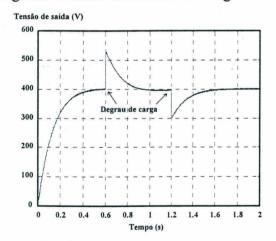

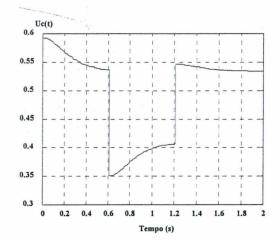

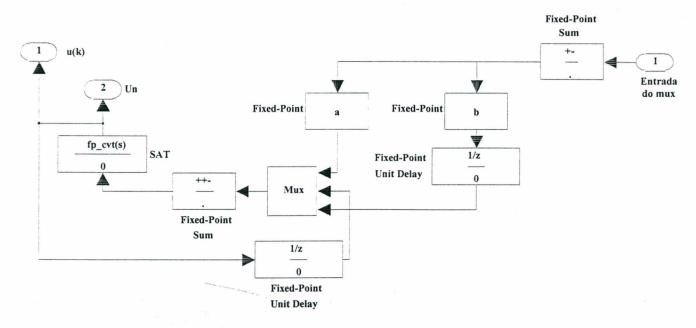

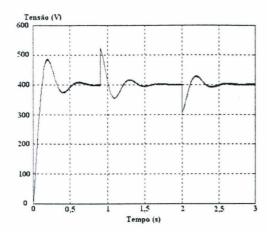

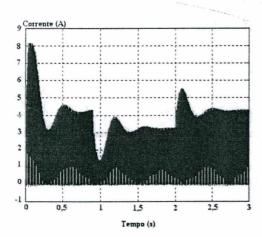

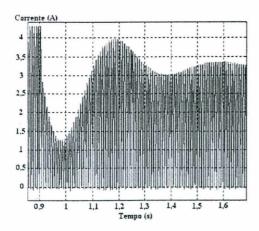

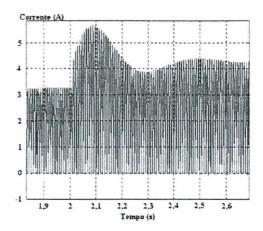

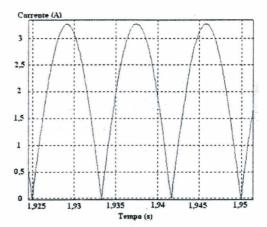

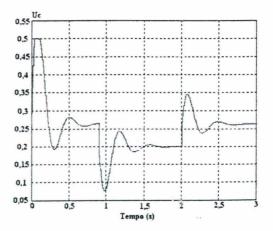

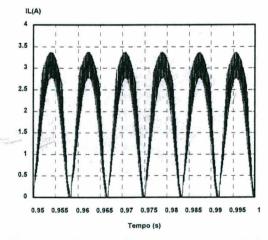

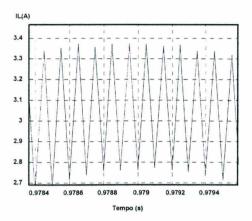

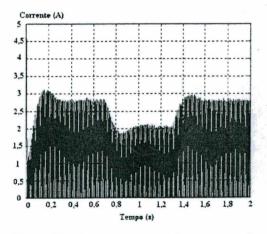

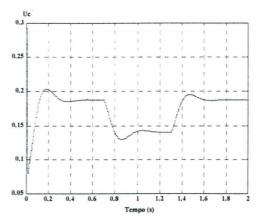

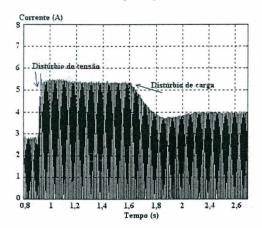

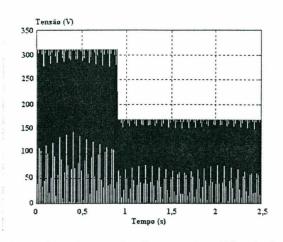

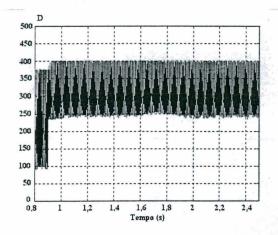

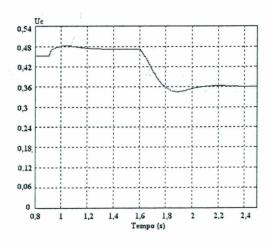

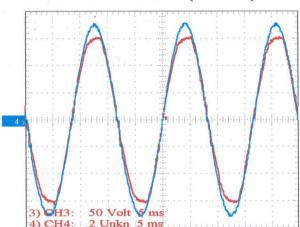

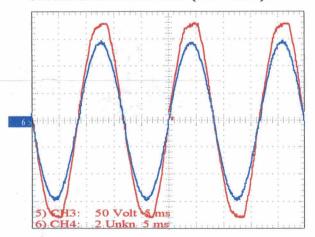

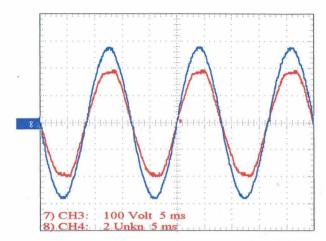

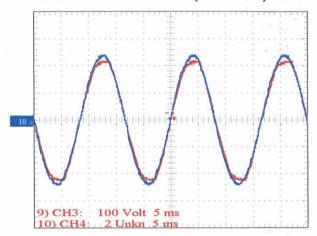

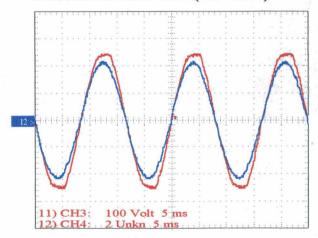

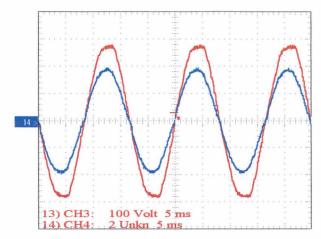

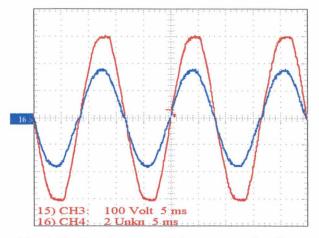

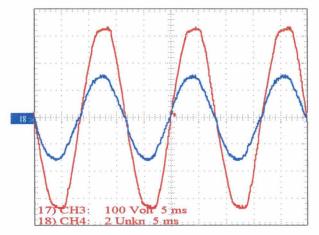

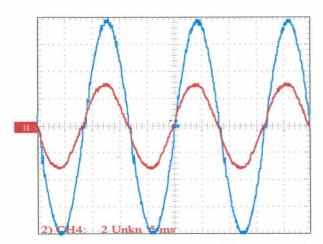

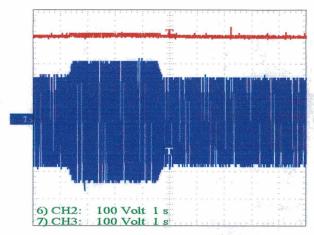

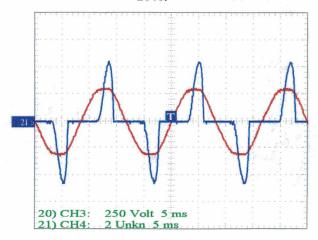

Para calcular-se a ação de controle *feedfoward* fez-se o cálculo do valor médio da tensão de entrada retificada. No controlador contínuo é feito do mesmo modo, porém, por um filtro de segunda ordem e que sempre possui uma ondulação. Esta ondulação se reflete no formato da corrente de entrada aumentando a distorção harmônica de corrente. Utilizando-se o valor médio calculado e atualizando a cada semi-ciclo (durante o cruzamento por zero) esta influência reduz-se.