## UNIVERSIDADE FEDERAL DE SANTA CATARINA CAMPUS FLORIANÓPOLIS, CENTRO TECNOLÓGICO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Cleisson Fernandes da Silva

Acelerador para a Convolução de Redes Neurais Binárias visando Computação de Borda

| Cleisson Ferr | nandes da Silva                                                                                                                                         |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                                                                                                                                         |

|               |                                                                                                                                                         |

|               | s Neurais Binárias visando Computação<br>Borda                                                                                                          |

|               |                                                                                                                                                         |

|               | Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do título de mestre |

|               | em Engenharia Elétrica.<br>Orientador: Prof. Eduardo Augusto Bezerra, Dr.                                                                               |

|               |                                                                                                                                                         |

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Silva, Cleisson Fernandes da Acelerador para a convolução de redes neurais binárias visando computação de borda / Cleisson Fernandes da Silva ; orientador, Eduardo Augusto Bezerra, 2022.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2022.

Inclui referências.

84 p.

1. Engenharia Elétrica. 2. Acelerador de domínio específico. 3. FPGA. 4. Rede neural binária. 5. Computação de borda. I. Bezerra, Eduardo Augusto. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

#### Cleisson Fernandes da Silva

# Acelerador para a Convolução de Redes Neurais Binárias visando Computação de Borda

O presente trabalho em nível de mestrado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. Anderson Wedderhoff Spengler, Dr. UFSC

Prof Laio Oriel Seman, Dr. UNIVALI

Prof. Renan Augusto Starke, Dr. IFSC

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de mestre em Engenharia Elétrica.

Prof. Telles Brunelli Lazzarin, Dr. Coordenação do Programa de Pós-Graduação

Prof. Eduardo Augusto Bezerra, Dr. Orientador

Florianópolis, 2022.

#### **RESUMO**

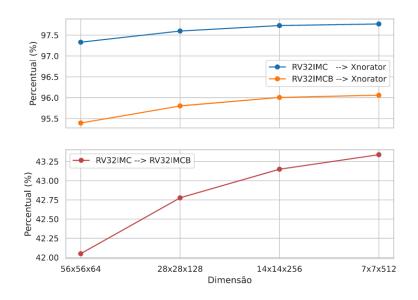

Com o crescimento exponencial de dados gerados por dispositivos IoT, o meio de comunicação está se tornando um gargalo para a computação em nuvem. Paradigmas como a computação de borda estão sendo cada vez de mais interesse por suas vantagens, tais como redução da latência de comunicação, uso mais eficiente da rede e o menor gasto energético. Ao transferir parte ou toda a computação para os dispositivos de borda é possível reduzir a quantidade de informações enviadas para a nuvem. Entre as aplicações que manipulam uma quantidade considerável de dados, pode-se destacar o processamento de vídeos e imagens. Através de algoritmos como as redes neurais é possível extrair propriedades e características úteis destes dados brutos. Dentro destes algoritmos, as redes neurais binárias têm atraído bastante interesse ultimamente devido às suas vantagens como a redução da complexidade computacional e de requisitos de memória. Além disso, em sistemas embarcados como encontrados nos dispositivos de borda, o uso de aceleradores de domínio específico para realizar uma determinada tarefa tem se mostrado altamente eficiente. Este trabalho apresenta o estudo, projeto e desenvolvimento de um acelerador de domínio específico para realizar o algoritmo de convolução binária presente nestas redes, visando a sua utilização nos sistemas embarcados dos satélites desenvolvidos no SpaceLab (UFSC). Através do uso de técnicas como especialização de dados e paralelismo de operações é possível obter ganho de desempenho significativo na execução do algoritmo em comparação com a sua execução em um núcleo de processamento. Os dados obtidos em simulação mostram que o acelerador executa em até 97,77% menos ciclos do que a execução utilizando apenas um núcleo RISC-V simples e em 96,06% menos ciclos do que um núcleo RISC-V com extensão de manipulação de bits. Além disso, a síntese para FPGA demonstra baixa utilização de recursos lógicos, permitindo sua utilização em dispositivos de baixa densidade disponíveis comercialmente.

**Palavras-chave**: Acelerador de Domínio Específico. FPGA. Rede Neural Binária. Computação de Borda.

#### **ABSTRACT**

With the exponential growth of data generated by IoT devices, communication medium is becoming a bottleneck for cloud computing. Paradigms such as edge computing are getting more and more interest for its advantages, such as reduced communication latency, more efficient use of the network, and lower energy consumption. By offloading some or all of the computation to the edge devices, it is possible to reduce the amount of information sent to the cloud. Among the applications that handle a considerable amount of data, one can highlight video and image processing. Through algorithms such as neural networks it is possible to extract useful properties and characteristics from this raw data Within these algorithms, binary neural networks have attracted a lot of interest lately due to their advantages such as the reduction of computational complexity and memory requirements. Furthermore, in embedded systems as found in edge devices, the use of domain-specific accelerators to perform a certain task has been shown to be highly efficient. This work presents the study, design and development of a domain-specific accelerator to perform the binary convolution algorithm found in these networks, with the goal of using it in the embedded systems of the satellites developed at SpaceLab. Through the use of techniques such as data specialization and operation parallelism, it is possible to obtain significant performance gains in the execution of the algorithm compared to its execution in a processing core. The data obtained in simulation shows that the accelerator runs in up to 97.77% less cycles than the execution using only a simple RISC-V core and in 96.06% less cycles than a RISC-V core with bit manipulation extension. In addition, FPGA synthesis demonstrates low utilization of logic resources, allowing its use in the lowest density devices commercially available.

**Keywords**: Domain Specific Accelerator. FPGA. Binary Neural Network. Edge Computing.

## **LISTA DE FIGURAS**

| Figura 1 – Modelo computacional de um neurônio artificial                          | 17 |

|------------------------------------------------------------------------------------|----|

| Figura 2 – Estrutura de uma rede neural artificial                                 | 18 |

| Figura 3 - Comparação entre os processos de treinamento e inferência de uma        |    |

| rede neural profunda                                                               | 19 |

| Figura 4 – Exemplos de mapas de atributos em diferentes camadas convolucio-        |    |

| nais de um modelo de CNN                                                           | 20 |

| Figura 5 - Erro <i>top</i> -5 no conjunto de dados ImageNet ao longo dos anos      | 22 |

| Figura 6 - Bloco residual                                                          | 23 |

| Figura 7 – Equivalência do produto escalar com as operações de multiplicação       |    |

| e acumulação (em cima) com as operações XNOR e popcount (em                        |    |

| baixo)                                                                             | 26 |

| Figura 8 - Comparação de uma rede neural com valores reais e uma Rede              |    |

| Neural Binária                                                                     | 26 |

| Figura 9 – Acurácia <i>top</i> -5 de modelos BNNs nos últimos anos para o conjunto |    |

| de dados ImageNet                                                                  | 28 |

| Figura 10 – Comparação do custo energético de instruções para um processador       |    |

| RISC com o custo de operações aritméticas                                          | 29 |

| Figura 11 – Comparação da especialização de um acelerador de domínio espe-         |    |

| cífico                                                                             | 31 |

| Figura 12 – Acelerador fortemente acoplado                                         | 33 |

| Figura 13 – Acelerador fracamente acoplado                                         | 34 |

| Figura 14 – Comparação entre os tipos de aceleradores para DNN                     | 36 |

| Figura 15 – Topologia da rede <i>QuickNet</i>                                      | 41 |

| Figura 16 – Influência da inserção de conexões residuais em uma rede binária.      | 42 |

| Figura 17 – Área de atuação do acelerador implementado                             | 42 |

| Figura 18 – Esquema de <i>padding</i> proposto por Guo <i>et al.</i> (2018)        | 44 |

| Figura 19 – Organização dos mapas de atributos binarizados na memória              | 46 |

| Figura 20 – Organização dos pesos binarizados na memória                           | 46 |

| Figura 21 – Comparação entra a organização dos atributos de entrada e saída        |    |

| em um mesmo endereço de memória                                                    | 47 |

| Figura 22 – Parâmetros para a convolução 3D                                        | 47 |

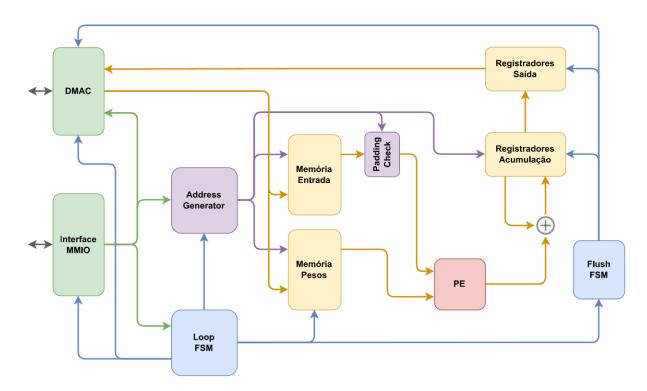

| Figura 23 – Diagrama de blocos da arquitetura interna do acelerador                | 49 |

| Figura 24 – Diagrama de sequência para a utilização do acelerador                  | 50 |

| Figura 25 – Diagrama de estados do componente Loop FSM                             | 52 |

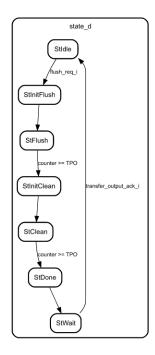

| Figura 26 – Diagrama de estados do componente Flush FSM                            | 53 |

| Figura 27 – Paralelismo de computação e comunicação                                | 54 |

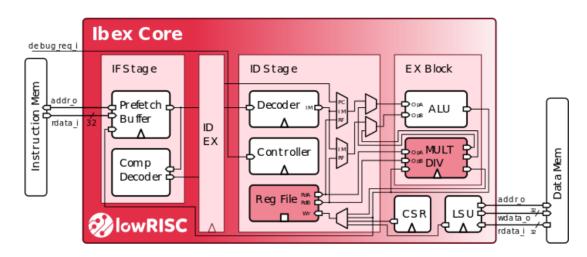

| Figura 28 – Diagrama de conexão com o acelerador                                   | 55 |

| Figura 29 – Diagrama de blocos do núcleo Ibex                                   | 56 |

|---------------------------------------------------------------------------------|----|

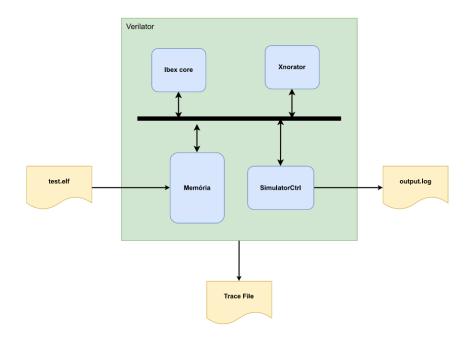

| Figura 30 – Esquema de simulação utilizando o Verilator                         | 57 |

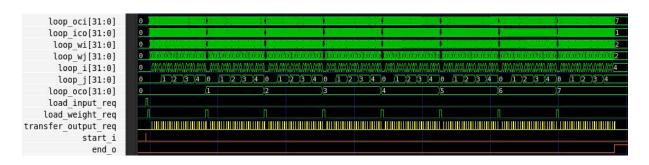

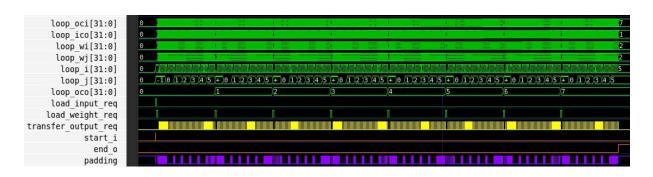

| Figura 31 – Formas de onda do laço de convolução completo                       | 58 |

| Figura 32 – Formas de onda do laço externo de canal da saída.                   | 58 |

| Figura 33 – Formas de onda do laço de coluna da saída.                          | 58 |

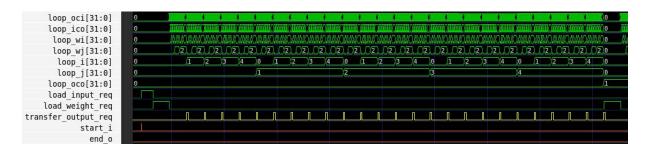

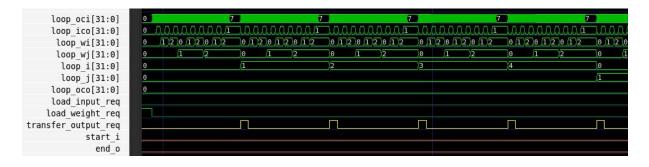

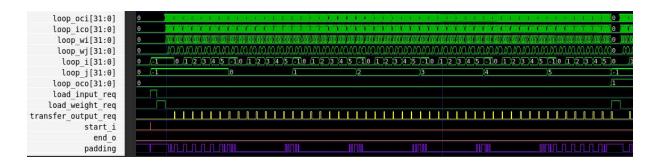

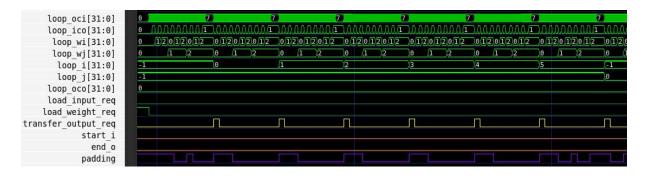

| Figura 34 – Formas de onda do laço de convolução completo com <i>padding</i>    | 59 |

| Figura 35 – Formas de onda do laço externo de canal da saída com <i>padding</i> | 59 |

| Figura 36 – Formas de onda do laço de coluna da saída com <i>padding</i>        | 59 |

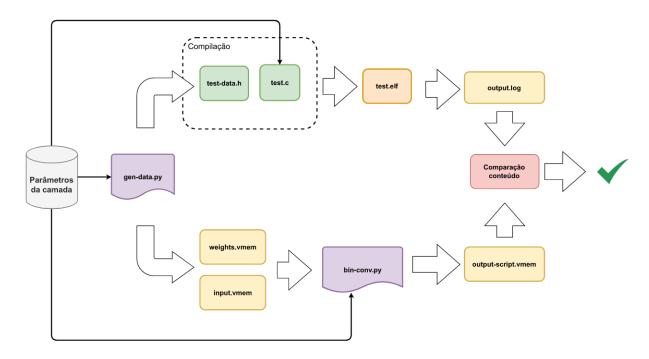

| Figura 37 – Esquema utilizado para testes.                                      | 60 |

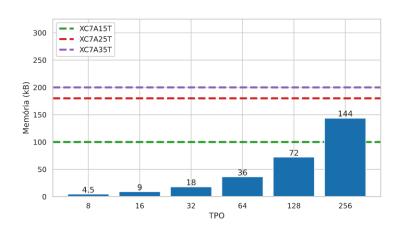

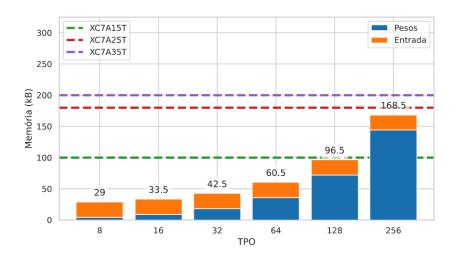

| Figura 38 – Memória necessária para armazenar os valores de pesos para dife-    |    |

| rentes parâmetros TPO                                                           | 62 |

| Figura 39 – Memória necessária para armazenar os valores dos mapas de atri-     |    |

| butos de entrada e pesos para diferentes parâmetros TPO                         | 63 |

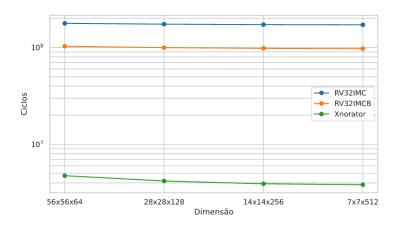

| Figura 40 – Comparação entre os ciclos de execução do algoritmo de convolução   |    |

| binária para as diferentes configurações                                        | 64 |

| Figura 41 – Comparação entre as reduções percentuais do número de ciclos        |    |

| entre as configurações de teste.                                                | 66 |

|                                                                                 |    |

## **LISTA DE QUADROS**

| Quadro 1 – Pseudocódigo de um algoritmo de convolução simples            | 48 |

|--------------------------------------------------------------------------|----|

| Quadro 2 - Pseudocódigo do algoritmo utilizado para a convolução binária | 48 |

| Quadro 3 – Algoritmo para operação de <i>popcount</i>                    | 63 |

## LISTA DE TABELAS

| Tabela 1 – Comparação entre trabalhos relacionados                             | 39 |

|--------------------------------------------------------------------------------|----|

| Tabela 2 – Memória utilizada em camadas selecionadas da rede <i>QuickNet</i>   | 43 |

| Tabela 3 – Memória disponível em dispositivos FPGAs da família Artix7 da em-   |    |

| presa Xilinx.                                                                  | 43 |

| Tabela 4 - Comparação da quantidade de elementos adicionados ao se realizar    |    |

| o padding.                                                                     | 45 |

| Tabela 5 – Endereços dos registradores da interface MMIO                       | 50 |

| Tabela 6 - Ciclos de execução do algoritmo de convolução binária para as dife- |    |

| rentes configurações de teste.                                                 | 64 |

| Tabela 7 - Redução percentual do número de ciclos necessários para executar    |    |

| o algoritmo de convolução binária no acelerador em comparação                  |    |

| com as configurações de RISCV                                                  | 65 |

| Tabela 8 - Redução percentual do número de ciclos necessários para execu-      |    |

| tar o algoritmo de convolução binária no núcleo com extensão de                |    |

| manipulação bits em comparação com o núcleo simples                            | 65 |

| Tabela 9 - Utilização de recursos do acelerador sintetizado para FPGA          | 66 |

| Tabela 10 – Utilização de recursos para diferentes TPOs                        | 67 |

| Tabela 11 – Comparação da implementação em FPGA do acelerador desenvol-        |    |

| vido com trabalhos relacionados                                                | 67 |

#### LISTA DE ABREVIATURAS E SIGLAS

ASIC Circuito Integrado de Aplicação Específica (Application Specific In-

tegrated Circuit)

BNN Rede Neural Binária (*Binary Neural Network*)

BRAM Block RAM

CNN Rede Neural Convolucional (*Convolutional Neural Network*)

CPU Unidade Central de Processamento (*Central Processing Unit*)

DNN Rede Neural Profunda (*Deep Neural Network*)

FPGA Arranjo de Porta Programável em Campo (Field Programmable Gate

Array)

GPU Unidade de Processamento Gráfico (*Graphics Processing Unit*)

IoT Internet das Coisas (Internet of Things)

ISA Conjunto de Instruções (*Instruction Set Archtecture*)

LoRa Long Range

LUT Look-Up Table

# SUMÁRIO

| 1     | INTRODUÇAO                         | 13 |

|-------|------------------------------------|----|

| 1.1   | OBJETIVOS                          | 16 |

| 2     | FUNDAMENTAÇÃO TEÓRICA              | 17 |

| 2.1   | REDES NEURAIS                      | 17 |

| 2.1.1 | Redes Neurais Artificiais          | 17 |

| 2.1.2 | Redes Neurais Convolucionais       | 19 |

| 2.1.3 | Otimizações                        | 22 |

| 2.1.4 | Redes Neurais Binárias             | 24 |

| 2.1.5 | Recursos Arquiteturais             | 27 |

| 2.2   | ACELERADORES DE DOMÍNIO ESPECÍFICO | 29 |

| 2.2.1 | Contextualização e Definição       | 29 |

| 2.2.2 | Modelos de Aceleradores            | 32 |

| 2.2.3 | Aceleradores de DNN                | 34 |

| 2.3   | PLATAFORMAS E COMPONENTES          | 35 |

| 2.3.1 | <b>FPGA</b>                        | 35 |

| 2.3.2 | RISC-V                             | 36 |

| 3     | TRABALHOS RELACIONADOS             | 38 |

| 4     | PROJETO E IMPLEMENTAÇÃO            | 40 |

| 4.1   | ANÁLISE BNNS                       | 40 |

| 4.1.1 | Topologia                          | 40 |

| 4.1.2 | Memória                            | 41 |

| 4.1.3 | Padding                            | 43 |

| 4.2   | ORGANIZAÇÃO DOS DADOS              | 45 |

| 4.3   | ALGORITMO DE CONVOLUÇÃO BINÁRIA    | 46 |

| 4.4   | MICROARQUITETURA                   | 48 |

| 4.4.1 | Visão Geral                        | 48 |

| 4.4.2 | Interface MMIO                     | 49 |

| 4.4.3 | DMAC                               | 51 |

| 4.4.4 | Memória Local                      | 51 |

| 4.4.5 | PE                                 | 52 |

| 4.4.6 | Loop FSM e Address Generator       | 52 |

| 4.4.7 | Banco de Registradores e Flush FSM | 53 |

| 4.4.8 | Padding Check                      | 53 |

| 5     | TESTES E RESULTADOS                | 55 |

| 5.1   | SIMULAÇÃO                          | 55 |

| 5.2   | VALIDAÇÃO                          | 59 |

| 5.3   | MÉTRICAS                           | 61 |

| SÍNTESE                      | 65      |

|------------------------------|---------|

| CONSIDERAÇÕES FINAIS         | 67      |

| CONCLUSÃO                    | 69      |

| Referências                  | 71      |

| ANEXO A – SCRIPT BIN-CONV.PY | 80      |

| ANEXO B - SCRIPT GEN-DATA.PY | 83      |

|                              | SÍNTESE |

## 1 INTRODUÇÃO

Nos últimos anos, houve um grande crescimento dos dados gerados por dispositivos de Internet das Coisas (IoT, *Internet of Things*). Esses dispositivos, também chamados de dispositivos de borda, são caracterizados por recursos computacionais e energéticos limitados. Essa limitação foi reduzida fazendo com que estes dispositivos transfiram o processamento necessário a ser realizado com os dados para a nuvem. Embora a velocidade de processamento de dados dos dispositivos da nuvem tenha aumentado, a largura de banda das redes que transportam dados para a nuvem não aumentou consideravelmente. Assim, com dispositivos de borda gerando cada vez mais dados, a rede está se tornando o gargalo da computação em nuvem (PREMSANKAR; DI FRANCESCO; TALEB, 2018).

Portanto, devido ao crescimento exponencial de dispositivos loT que se conectam à Internet para receber informações da nuvem ou entregar dados de volta à nuvem, surgiu o conceito de computação de borda (SHI; DUSTDAR, 2016). A computação de borda é um novo paradigma de computação em que os dados são processados no local onde os mesmos são produzidos. Este modelo de computação traz diversas vantagens como por exemplo:

- Latência reduzida: Estes sistemas podem ser colocados mais próximos dos usuários e serviços finais. Desse modo, isso naturalmente evita os atrasos de propagação de rede. Além disso, algumas aplicações possuem requisitos rigorosos de latência e desempenho em tempo real. Aplicações criadas em torno da experiência do usuário e aplicações de segurança automotiva são exemplos onde a latência não pode ser tolerada, portanto, os dados devem ser processados no próprio dispositivo (SORO, 2021);

- Consumo de Rede: Certos ambientes têm largura de banda limitada e a computação de borda pode atender melhor esse problema por meio de técnicas de filtragem, armazenamento em cache, extração de atributos e compactação de dados para maximizar com eficiência a largura de banda disponível (LEA, 2020); Ou seja, se os dispositivos puderem executar mais processamento nos dados brutos localmente (no próprio hardware local), menos dados brutos deverão ser transmitidos (PARKS, 2018);

- Gasto energético: Existem casos em que o gasto energético para mandar os dados e receber uma resposta seria maior do que processar os dados no próprio local;

- Segurança e Privacidade: Algumas situações devem proteger ou até mesmo remover certos dados antes que saiam do dispositivo de borda.

As áreas de aprendizado profundo e redes neurais, que demonstraram um grande desenvolvimento na última década, podem contribuir drasticamente para o

processamento de dados na borda (LI; OTA; DONG, 2018). Um algoritmo de rede neural pode extrair propriedades e características úteis dos dados brutos. Além disso, a Rede Neural Convolucional (CNN, *Convolutional Neural Network*), que é um tipo específico de rede neural, forneceu uma melhoria dramática de desempenho nos campos de processamento de imagem e visão computacional.

Observa-se em aplicações que é desejável utilizar a visão computacional para extrair as informações significativas de um vídeo diretamente no sensor de imagem e não na nuvem, para reduzir o custo de comunicação, dado que os vídeos envolvem uma grande quantidade de dados. Sendo assim, uma destas aplicações e motivação deste trabalho é a sua utilização nos sistemas embarcados dos satélites pesquisados e desenvolvidos no SpaceLab (Universidade Federal de Santa Catarina). Além das limitações de energia e tamanho, estes sistemas possuem limitações na comunicação ao se utilizar protocolos de comunicação loT, tais como o LoRa.

Além desta aplicação, foi identificado na literatura outros casos de uso como veículos autônomos, navegação por drones e robótica, onde o processamento local é desejado, pois a latência e o risco de segurança de depender da nuvem são muito altos (SZE *et al.*, 2017a).

A implantação da inteligência artificial nos dispositivos de borda pode ajudar a obter dados mais significativos mais rapidamente, o que não apenas traz as vantagens mencionadas anteriormente como economia dos custos de comunicação e redução do atraso de resposta como também expande muito os cenários de aplicações de inteligência artificial (WANG *et al.*, 2020). Esses dispositivos não possuem inteligência para processar os dados de entrada e tomar decisões, em vez disso, dependem do usuário ou de outras entidades de processamento, como a nuvem, para tomar a decisão e controlá-los remotamente. Sendo assim, a inclusão dos algoritmos de inteligência artificial nestes dispositivos de borda podem permitir a emergência de dispositivos inteligentes que são capazes de processar os dados detectados, avaliar a situação e agir de forma independente (SAMIE; BAUER; HENKEL, 2019).

Portanto, um dos problemas atuais é como adicionar estas redes neurais complexas nestes dispositivos de borda sem reduzir o desempenho. As CNNs de última geração normalmente têm milhões de parâmetros e uma única tarefa de inferência pode invocar bilhões de operações aritméticas e acessos à memória. Os dispositivos onde esses algoritmos serão executados são geralmente constituídos por sistemas embarcados compostos por microcontroladores. Além disso, são normalmente alimentados por bateria e, como consequência, precisam funcionar em uma faixa de baixa potência.

Para contornar esse problema, deu-se início ao desenvolvimento de uma nova geração de redes neurais, mais compactas em tamanho e que focam na eficiência além da acurácia do modelo. Diversos trabalhos foram desenvolvidos do lado do al-

goritmo onde surgiram otimizações como remover pesos da rede neural para diminuir o número de operações (WEN *et al.*, 2016) ou diminuir a representação dos pesos e ativações para um valor de *bits* menor e assim utilizar menos recursos computacionais do *hardware* (HUBARA *et al.*, 2016).

Uma dessas otimizações que recebeu atenção ultimamente é a Rede Neural Binária (BNN, *Binary Neural Network*) (COURBARIAUX *et al.*, 2016), um tipo de rede neural convolucional onde os valores de ambos os pesos e ativações são limitados para apenas os valores +1 e -1. Além de um uso de memória reduzido, essas redes trazem uma grande vantagem na sua execução devido à simplificação das operações ao se utilizar apenas dois valores. As operações de multiplicação e acumulação, onde há o maior gasto computacional das CNNs, podem ser substituídas por operações de XNOR e *popcount* que são muito mais eficientes de serem executadas (RASTEGARI *et al.*, 2016). Inicialmente esse tipo de rede sofria de baixa acurácia devido à quantização massiva imposta na rede neural. No entanto, nos últimos anos, as pesquisas neste tipo de rede mostraram um grande avanço na sua acurácia ao se utilizar técnicas como topologias de rede neural customizadas e estratégias para o treinamento (YUAN; AGAIAN, 2021). Deste modo, as BNNs estão cada vez diminuindo a diferença de acurácia que existe entre elas e os modelos de rede neural que utilizam precisão total.

Além de otimizar o modelo de rede neural, transferir a sua execução para um acelerador de *hardware* dedicado surgiu como uma solução amplamente adotada para melhorar o tempo de execução e a eficiência energética. Isso vai ao encontro com a tendência atual de utilizar aceleradores de domínio específico para executar determinadas tarefas com mais eficiência. Essa tendência se deve ao fato de a lei de Moore (MOORE *et al.*, 1965) ter chegado ao fim (THEIS; WONG, 2017) e há uma busca por novas arquiteturas e tecnologias para continuar escalando desempenho e eficiência.

Diversos aceleradores para BNNs foram propostos como, por exemplo, FINN (UMUROGLU *et al.*, 2017), FP-BNN (LIANG, Shuang *et al.*, 2018) e XNE (CONTI; SCHIAVONE; BENINI, 2018). No entanto, grande parte destes aceleradores foram projetados para modelos de BNNs pequenos onde a imagem de entrada é muito reduzida para se utilizar em aplicações de visão computacional reais ou utilizam topologias de redes já obsoletas que não refletem o estado da arte. Além disso, como apontado por Bannink *et al.* (2021), muitos estudos de BNNs focam em desempenho teórico e muitas vezes carecem de dados empíricos.

Sendo assim, este trabalho foi realizado a fim de possibilitar o uso de redes neurais binárias do estado da arte no contexto de computação de borda através do uso de um acelerador de domínio específico para executar a operação de convolução binária e suprir as limitações impostas neste ambiente.

#### 1.1 OBJETIVOS

Este trabalho apresenta como objetivo geral a pesquisa e desenvolvimento de um acelerador de domínio específico para a execução de Redes Neurais Binárias em dispositivos de computação de borda e análise de suas métricas relacionadas ao desempenho. Para realização do objetivo geral proposto, tem-se como objetivos específicos os seguintes tópicos:

- Realizar uma análise bibliográfica e do estado da arte.

- Elaborar uma microarquitetura para o acelerador.

- Implementar a microarquitetura proposta utilizando uma linguagem de descrição de *hardware*.

- Verificar, com base em síntese e simulações, o desempenho de execução do acelerador implementado.

- · Avaliar os resultados obtidos.

## 2 FUNDAMENTAÇÃO TEÓRICA

Neste capítulo são apresentados os conceitos base para o entendimento e desenvolvimento do trabalho. O capítulo está dividido em três seções. A Seção 2.1 compreende os conhecimentos pertinentes à área de redes neurais. A Seção 2.2 discorre sobre os aceleradores de domínio específico, a motivação de seu uso, suas arquiteturas e os aspectos relacionados ao seu uso no campo de redes neurais. A Seção 2.3 detalha os componentes utilizados para a concepção do trabalho.

#### 2.1 REDES NEURAIS

#### 2.1.1 Redes Neurais Artificiais

As Redes Neurais Artificiais são um conjunto de algoritmos pertencentes à área de Aprendizado de Máquinas, inspirados no cérebro humano, que são projetados para reconhecer padrões (AGGARWAL *et al.*, 2018). Estas redes são constituídas por unidades computacionais chamadas de neurônio artificial ou simplesmente unidade. O modelo matemático que descreve um neurônio artificial é ilustrado na Figura 1. Segundo Khan *et al.* (2018), este neurônio recebe um conjunto de dados de entrada que são ponderados por um conjunto de pesos, além de um valor de *bias*. Todos esses valores são somados e no valor resultante é aplicado uma função não linear (chamada de função de ativação) para calcular o valor de saída dessa unidade. Após isso, o valor de saída, também chamado de ativação, pode ser utilizado como entrada para outras unidades.

$y = \sigma(\mathbf{W}\mathbf{x} + b)$   $x_1$   $x_2$   $w_2$   $\sum(.)$   $x_n$   $w_n$   $w_n$   $w_n$   $\mathbf{y}$   $\mathbf{x}$   $\mathbf{Activation}$   $\mathbf{Function}$   $\mathbf{y}$   $\mathbf{Activation}$   $\mathbf{Function}$   $\mathbf{Supple }$   $\mathbf{y}$   $\mathbf{y$

Figura 1 – Modelo computacional de um neurônio artificial

Fonte - Khan et al. (2018).

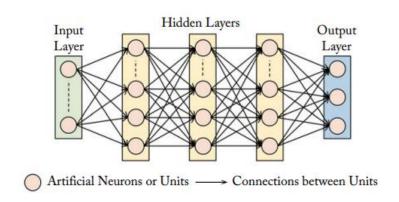

Desse modo, como ilustrado na Figura 2, uma rede neural artificial consiste em unidades computacionais interconectadas agrupadas em camadas, sendo: uma

camada de entrada para receber os dados a serem processados, uma camada de saída que fornece os resultados da tarefa da rede e um conjunto de camadas internas chamadas de camadas ocultas (VÉSTIAS *et al.*, 2020). Segundo Goodfellow, Bengio e Courville (2016), uma rede neural com mais de três camadas ocultas é designada Rede Neural Profunda (DNN, *Deep Neural Network*) para enfatizar o alto número de camadas.

Figura 2 – Estrutura de uma rede neural artificial

Fonte - Khan et al. (2018).

Atualmente as DNNs são utilizadas em diversos setores para uma ampla gama de tarefas que vão desde a previsão de dados à tarefas mais complexas como a classificação de imagens, reconhecimento de voz, robótica, etc. (SZE *et al.*, 2017a).

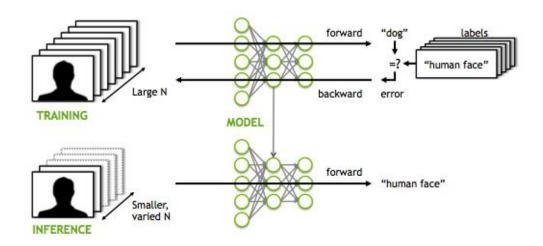

De acordo com Véstias *et al.* (2020), um modelo de rede neural é primeiro treinado para resolver um problema específico e, em seguida, usado para classificar novas amostras em um processo conhecido como inferência. O treinamento da rede determina sua acurácia. Este treinamento pode ser supervisionado ou não supervisionado. No treinamento supervisionado, o modelo aprende com os dados rotulados manualmente e os pesos são ajustados para que a saída da rede para uma entrada específica corresponda à resposta correta. Já o treinamento não supervisionado não requer dados rotulados. Em vez disso, o modelo extrai padrões da entrada por si só. Para as aplicações de visão computacional o treinamento mais utilizado é o supervisionado.

A Figura 3 ilustra as duas fases do processo de aprendizado profundo, treinamento e inferência. A fase de treinamento possui duas etapas: propagação direta e retropropagação. Na propagação direta, o dado de entrada é carregado na camada inicial e é propagado até que uma saída seja produzida. A saída é então comparada com o valor de saída esperado usando uma função de custo e o desempenho é avaliado. O mesmo processo é repetido por retropropagação, onde os dados são realimentados na camada inicial com o objetivo de reduzir a função custo alterando os pesos. Dessa forma, até que os pesos ótimos sejam calculados, o treinamento continua e o modelo

está pronto para inferência ou teste. Na fase de inferência há apenas propagação direta dos dados e a saída produzida é o resultado final da previsão (MUCHANDI, 2020).

Figura 3 – Comparação entre os processos de treinamento e inferência de uma rede neural profunda

Fonte - MITXPC (2022).

Existem diversos tipos de redes neurais e cada uma tem sua configuração e sua utilização. A maneira como os neurônios são organizados em uma camada e como eles estão conectados à camada sucessora definem o que é chamado arquitetura ou topologia da rede neural. Alguns exemplos são a rede neural *feed-forward*, rede neural recorrente (RNNs), rede neural convolucional (CNN), etc. Para este trabalho, a arquitetura de rede de interesse é a CNN devido a sua aplicação na visão computacional.

#### 2.1.2 Redes Neurais Convolucionais

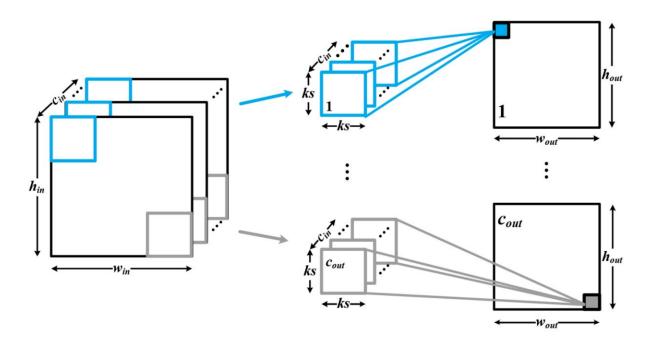

Com o rápido desenvolvimento da tecnologia de aprendizado profundo, a Rede Neural Convolucional (CNN, *Convolutional Neural Network*) tornou-se um dos métodos mais populares em reconhecimento de padrões e visão computacional (PATEL *et al.*, 2015). A CNN é um tipo de DNN que adiciona a operação de convolução em sua arquitetura. Essa operação pode ser vista como uma versão estendida de multiplicações de matrizes, que adiciona as propriedades de conectividade local e invariância de translação. Comparado com multiplicações de matrizes, em convoluções, cada elemento de entrada é substituído por um mapa de atributos e cada elemento de peso é substituído por um *kernel* convolucional (ou filtro). Então, o cálculo é baseado em janelas deslizantes (CHEN, Y. *et al.*, 2020).

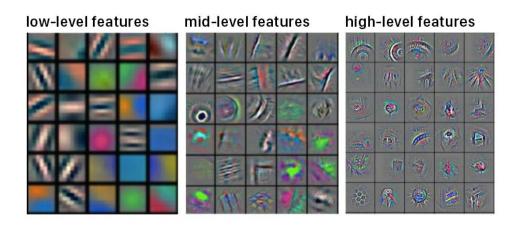

Para as aplicações de visão computacional, as CNNs são compostas de múltiplas camadas convolucionais e, com cada camada, uma abstração em alto nível dos dados de entrada (chamado mapa de atributos ou *feature map*), é extraído para preservar informações essenciais, porém únicas. Como apontado por Sze *et al.* (2017b), a saída das primeiras camadas convolucionais podem ser interpretadas como representando a presença de diferentes atributos de baixo nível na imagem, como linhas e bordas. Nas camadas subsequentes, esses atributos são então combinados em uma medida da provável presença de atributos de alto nível, por exemplo, as linhas são combinadas em formas. E, finalmente, com todas essas informações, a rede fornece uma probabilidade de que esses atributos de alto nível compõem um objeto ou cenário em particular. A Figura 4 ilustra como estes mapas de atributos podem se apresentar em diferentes camadas de um modelo CNN.

Figura 4 – Exemplos de mapas de atributos em diferentes camadas convolucionais de um modelo de CNN

Fonte - Bebes (2017).

De acordo com Goodfellow, Bengio e Courville (2016), para uma imagem 2D *I* como entrada e um kernel 2D *K*, a convolução discreta é dada pela Equação (1)

$$S[i,j] = (K * I)[i,j] = \sum_{m} \sum_{n} I[i-m,j-n]K[m,n]$$

(1)

Além da camada convolucional, as CNNs são compostas por outras camadas que realizam operações nos mapas de atributos como, por exemplo:

• Camada de Pooling: Introduz invariância translacional no mapa de atributos substituindo os valores de ativações em uma janela por um valor representativo. O método de escolha deste valor pode ser por meio de uma média entre todos os valores dessa janela (average-pooling) ou a ativação com o maior valor da mesma (max-pooling) (GOODFELLOW; BENGIO; COUR-VILLE, 2016). O tamanho desta janela é o mesmo do tamanho do filtro de pooling e esse filtro desloca por uma certa distância (chamada de stride) para percorrer todo o mapa de atributos. Além disso, esta camada é normalmente adicionada ao longo das sucessivas camadas convolucionais e

também é empregada para reduzir progressivamente o tamanho espacial da representação, reduzindo assim a quantidade de parâmetros e computação na rede. (SHAWAHNA; SAIT; EL-MALEH, 2018);

• Camada de Batch Normalization (IOFFE; SZEGEDY, 2015): Esta operação desloca e dimensiona a distribuição de entrada para ter média zero e variância unitária. Normalmente é utilizada para reduzir o tempo de treinamento e melhorar a capacidade de generalização da rede (LIANG, Songhong et al., 2020). Esta operação é dada pela Equação (2), onde x e y são entrada e saída, respectivamente, μ e σ são estatísticas coletadas sobre o conjunto de treinamento, γ e β são parâmetros treinados, e ε para evitar problemas de arredondamento. Durante a inferência, todos os parâmetros são fixos, portanto, é preciso apenas aplicar Equação (2) a cada ativação do respectivo mapa de atributos. Cada mapa de atributos requer seu próprio conjunto de parâmetros de batch normalization;

$$y = \frac{x - \mu}{\sqrt{\sigma^2 + \varepsilon}} \cdot \gamma + \beta \tag{2}$$

• Camada Densa: Geralmente vem no final da rede onde o mapa de atributos da camada anterior é achatado em um vetor. A partir disso, todas as ativações desse vetor são conectadas à próxima camada ou à camada de saída que é o vetor de predição, onde seu tamanho é o número de classes e os valores suas probabilidades. As camadas densas desempenham o papel da tarefa de classificação, enquanto que as camadas anteriores atuam na extração de atributos.

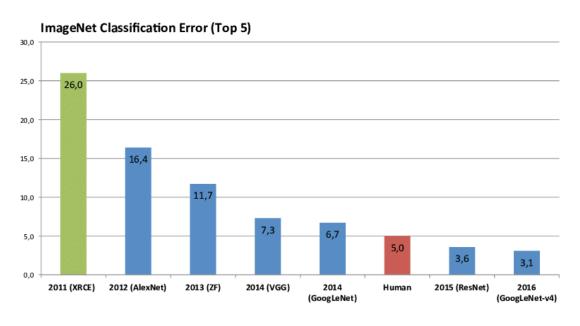

Embora as CNNs sejam conhecidas pelos pesquisadores há décadas (LECUN et al., 1989), elas foram popularizadas após demonstrarem alta acurácia no desafio de reconhecimento ImageNet de 2012 (RUSSAKOVSKY et al., 2015). ImageNet é um conjunto de dados amplamente utilizado para avaliar o desempenho de algoritmos de detecção de objetos e classificação de imagens que consiste em milhões de imagens diferentes distribuídas em dezenas de milhares de classes de objetos (RUSSAKOVSKY et al., 2015). Além disso, para comparar o desempenho dos algoritmos de classificação, costuma-se utilizar as métricas top-1 e top-5, onde top-1 indica que a resposta do modelo (a com maior probabilidade) é exatamente a resposta esperada e o top-5 indica que a resposta esperada está entre as 5 respostas de maior probabilidade geradas pelo modelo.

A Figura 5 apresenta a evolução do desempenho dos modelos CNNs ao longo do tempo. Os vencedores do ano 2011 e anteriores utilizavam uma abordagem de visão computacional com métodos tradicionais, onde a funcionalidade de detecção era realizada através de atributos inseridos manualmente. Em 2012 houve o grande avanço através do modelo AlexNet (KRIZHEVSKY; SUTSKEVER; HINTON, G. E., 2012) em

que os atributos eram aprendidos através do aprendizado profundo. Nos anos seguintes, todos os vencedores estavam usando o aprendizado profundo para continuar melhorando significativamente o estado da arte. Entre estes estão os modelos ZF (ZEILER; FERGUS, 2014), VGG (SIMONYAN; ZISSERMAN, 2014) e GoogleLeNet (também chamado de InceptionV1) (SZEGEDY *et al.*, 2015) Em 2015, o modelo ResNet (HE *et al.*, 2016) conseguiu superar o desempenho considerado de nível humano no conjunto de dados ImageNet (RUSSAKOVSKY *et al.*, 2015). Subsequentemente, as CNNs tornaram-se o estado da arte para tarefas de classificação, detecção e localização de imagens. A pesquisa em CNNs e outras áreas de aprendizado profundo continua em ritmo acelerado, com centenas de novos artigos publicados a cada ano apresentando novos modelos e técnicas.

Figura 5 – Erro *top*-5 no conjunto de dados ImageNet ao longo dos anos.

Fonte – Poel (2020).

O modelo ResNet adiciona em sua topologia os blocos residuais, ilustrado na Figura 6. Este bloco consiste em adicionar uma conexão de atalho (também chamada de conexão residual) em que após passar por uma ou mais camada convolucional, o resultado de saída é somado elemento a elemento com os valores anteriores ao bloco. Esta estratégia permitiu treinar redes extremamente profundas, com mais de 150 camadas.

#### 2.1.3 Otimizações

Os modelos CNNs são computacionalmente caros e intensivos no uso de memória, dificultando assim seu uso no contexto de dispositivos com recursos escassos, como aqueles empregados na computação de borda. Portanto, muito esforço tem sido

$\mathcal{F}(\mathbf{x}) \qquad \begin{array}{c} \mathbf{x} \\ \text{weight layer} \\ \text{weight layer} \end{array} \qquad \mathbf{x} \\ \text{identity} \\ \mathcal{F}(\mathbf{x}) + \mathbf{x} \qquad \begin{array}{c} \mathbf{x} \\ \text{identity} \end{array}$

Figura 6 – Bloco residual.

Fonte – He et al. (2016).

dedicado à definição de técnicas para compressão e aceleração de modelos CNNs sem afetar significativamente a acurácia dos mesmos (RUSSO *et al.*, 2021). Em geral, essas técnicas podem ser classificadas nas seguintes categorias principais:

- Pruning: também chamada de poda, essas técnicas são baseadas na suposição de que muitos parâmetros em DNNs são desnecessários ou sem importância, sendo assim, os métodos de pruning são usados para remover estes parâmetros. Após uma fase de treinamento inicial, conexões sem importância são removidas, levando a uma rede esparsa. O impacto no desempenho quando estas técnicas são usadas está relacionado ao menor número de cálculos devido ao fato de vários parâmetros terem sido suprimidos. No entanto, como a rede podada é esparsa, o acesso irregular induzido à memória afeta negativamente a aceleração prática em plataformas de hardware. Na verdade, em alguns casos, o ganho de desempenho sobre a rede original não podada é muito limitada ou negativa, mesmo que a esparsidade da rede seja alta, maior que 95% (WEN et al., 2016). Outro problema com as técnicas de poda é que elas exigem um retreinamento que, em alguns casos, pode exigir mais tempo do que o próprio treinamento. Por exemplo, em Han et al. (2015) é relatado que o AlexNet original levou 75 horas para treinar na GPU NVIDIA Titan X. Após a poda, toda a rede é treinada novamente com 1/100 da taxa de aprendizado inicial da rede original, exigindo 173 horas para retreinar a rede podada (RUSSO et al., 2021);

- Quantização: A quantização reduz a largura de bits dos dados que fluem através do modelo de rede neural. Deste modo, portanto, é possível diminuir o tamanho do modelo para economizar memória e reduzir os requisitos de largura de banda para as memórias externa e interna. Além disso, este método resulta em circuitos aritméticos menos complexos, pois precisam

trabalhar em operandos com menor número de *bits*, resultando em uma redução do números de componentes lógicos necessários para cada unidade de operação de multiplicação e acumulação (MAC) além da quantidade de roteamento (DENG, L. *et al.*, 2020);

- Decomposição matricial: Operações com matrizes é a computação básica de uma rede neural (DENG, L. et al., 2020). Portanto, métodos de fatoração são usados para aproximar a matriz de pesos de uma camada DNN com a multiplicação de duas ou múltiplas matrizes com um menor posto (SAINATH et al., 2013). Este método pode ser aplicado tanto em camadas convolucionais quanto em camadas densas, mas seu uso prático não é tão fácil, pois envolve extensas operações de decomposição que são computacionalmente caras. Outra questão da fatoração é que ela requer um extenso retreinamento do modelo para alcançar a convergência quando comparado ao modelo original (RUSSO et al., 2021);

- Destilação de conhecimento: Neste método é realizado o processo de tranferir o conhecimento de uma rede maior e mais complexa para um modelo menor, de modo que o modelo menor tenta imitar a função aprendida pelo modelo complexo (HINTON, G.; VINYALS; DEAN, Jeff et al., 2015). Uma das desvantagens desta técnica é que ela só pode ser aplicada a tarefas que possuam função perda softmax (DENG, L. et al., 2020).

#### 2.1.4 Redes Neurais Binárias

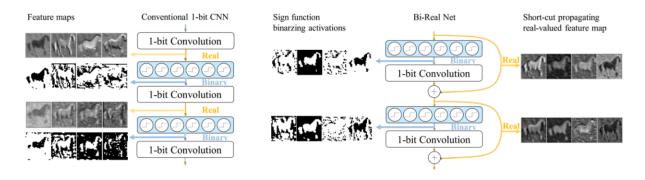

A quantização é conhecida por ser uma das formas mais eficazes de reduzir a complexidade de inferência de rede neural, que consiste em reduzir a precisão do formato de dados utilizado para representar os pesos do modelo e as entradas/saídas das camadas (HUBARA et al., 2017). A forma mais comum de quantização é utilizar inteiros de 8 bits para pesos e ativações, proporcionando redução de complexidade considerável com pouca queda de precisão em relação aos modelos de ponto flutuante (JACOB et al., 2018). No entanto, o consumo de memória e o número total de operações para a inferência de modelos quantizados em 8 bits ainda são excessivos para dispositivos de computação de borda (DAGHERO et al., 2021). Para alcançar uma redução ainda maior da complexidade, Courbariaux et al. (2016) foram os primeiros a apresentar o conceito de Redes Neurais Binárias.

As Redes Neurais Binárias (COURBARIAUX *et al.*, 2016) podem ser consideradas como uma versão de rede convolucional com quantização extrema, onde a precisão tanto dos pesos quanto das ativações são reduzidas para 1 bit e assim restringindo os valores possíveis para +1 e -1. O processo de compactar valores codificados em 32 *bits* para 1 *bit* é chamado de binarização e é obtido simplesmente com a função

sign(·), apresentada na Equação (3). A binarização de pesos e ativações afeta significativamente o uso de memória do modelo, reduzindo-a em 32x em relação a uma implementação de ponto flutuante de precisão simples (RASTEGARI *et al.*, 2016).

$$y = sign(x) = \begin{cases} +1 & \text{se } x \ge 0, \\ -1 & \text{caso contrário} \end{cases}$$

(3)

A função  $sign(\cdot)$  possui derivada igual a 0 em quase todos os lugares, o que torna impossível calcular o gradiente utilizando a regra da cadeia na fase de treinamento. A fim de contornar este problema, uma prática amplamente aceita é usar uma função diferente durante a retropropagação que é diferenciável, mas muito parecida com a ativação binária (RAJ; NAYAK; KALYANI, 2020). A função mais utilizada é o *Straight-Through Estimator* (BENGIO; LÉONARD; COURVILLE, 2013), em que permite que apenas valores retropropagados em um determinado intervalo passem.

Segundo Yuan e Agaian (2021), o objetivo da binarização é de não apenas poder economizar no armazenamento de um modelo DNN, mas também reduzir os custos da computação de matrizes na sua inferência. Sendo assim, a operação de convolução pode ser aproximada pela binarização das matrizes dos operandos, como mostrado na Equação (4).

$$\mathbf{I} * \mathbf{W} \approx sign(\mathbf{I}) \circledast sign(\mathbf{W}) \tag{4}$$

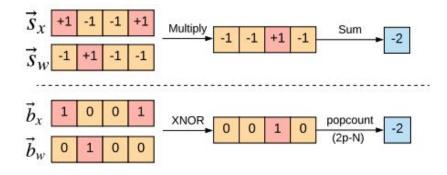

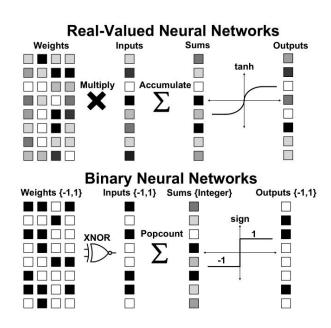

Como os valores após a binarização são +1 ou -1, a convolução denotada pelo símbolo ⊛ pode ser reduzida a operações *bit* a *bit*. Isto é, se os valores binários obtidos dessas operações forem codificados com +1 como um *bit* de valor um e -1 como um *bit* de valor zero, uma operação de multiplicação é equivalente a uma operação lógica XNOR nos valores binários. A soma das operações XNOR também pode ser calculada através de um simples *popcount*, que é a contagem do número de *bits* definido como valor 1. Esta equivalência entre as operações é ilustrada na Figura 7 e uma comparação visual entre as operações realizadas em uma rede neural com valores reais e uma rede neural binária é apresentada na Figura 8.

Devido a transformação dos valores {-1,+1} para {0,1}, o resultado final do produto escalar entre dois vetores binários de pesos (w) e entradas (x) é obtido com a Equação (5), onde ⊙ é a operação de XNOR e N é o tamanho do vetor.

$$y = 2 \cdot popcount(w \odot x) - N \tag{5}$$

Desta forma, a binarização reduz os requisitos de armazenamento e largura de banda de memória e elimina completamente as operações de multiplicação e acumulação (MAC) presentes nas camadas de computação da rede neural por operações binárias que podem ser executadas com muita eficiência em um hardware dedicado, como um FPGA.

Figura 7 – Equivalência do produto escalar com as operações de multiplicação e acumulação (em cima) com as operações XNOR e popcount (em baixo)

Fonte – Ghasemzadeh, Samragh e Koushanfar (2018).

Figura 8 – Comparação de uma rede neural com valores reais e uma Rede Neural Binária

Fonte - Knag et al. (2020).

Apesar dos benefícios atraentes, é consideravelmente difícil treinar e otimizar redes fortemente quantizadas como as redes binárias para se obter um alto desempenho (ZHANG, Y.; ZHANG, Z.; LEW, 2021). As BNNs pioneiras costumavam sofrer de uma diferença de acurácia no *top-1* do dataset *ImageNet* de mais de 20% em comparação com suas contrapartes de ponto flutuante (COURBARIAUX *et al.*, 2016). Apenas recentemente as BNNs se tornaram comparáveis em qualidade aos modelos populares como por exemplo o *ResNet* (HE *et al.*, 2016). Segundo Liu *et al.* (2021), um dos motivos para essa dificuldade é que as BNNs tendem a ter uma função perda

muito caótica e descontínua que torna sua otimização desafiadora. Além disso, há uma perda severa de informações devido à binarização dos parâmetros. Para que a binarização funcione, é preciso mudar muitas coisas em comparação com as práticas padrões de DNNs. Segundo Yuan e Agaian (2021), para reduzir essa diferença de acurácia em comparação com as CNNs de precisão total, uma variedade de novas soluções de otimização foram propostas nos últimos anos que incluem:

- Minimizar o erro de quantização.

- Melhorar a função perda.

- Melhor aproximação do gradiente.

- Novas estruturas de topologias de redes.

- Estratégias e truques para o treinamento.

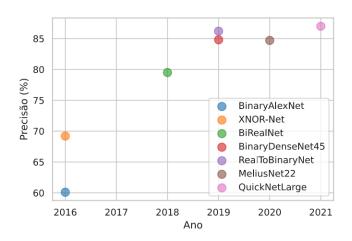

Como mostrado na Figura 9, os modelos BNNs estão atingindo uma acurácia melhor a cada ano. No entanto, como notado por Bannink *et al.* (2021), embora as BNNs tenham o potencial de tornar as aplicações de aprendizado profundo radicalmente mais eficientes, na prática as redes que utilizam ponto flutuante ou com quantização de 8 *bits* ainda dominam os modelos de DNN em produção. Segundo Yuan e Agaian (2021), um dos motivos é que os principais *frameworks* para a implementação de modelos DNNs como o Tensorflow (ABADI *et al.*, 2016) e o Pytorch (PASZKE *et al.*, 2019) ainda não possuem suporte nativo para este tipo de rede. No entanto, na literatura, foram publicados diversos *frameworks* para a utilização de BNNs como BMXNet (YANG *et al.*, 2017), FINN (BLOTT *et al.*, 2018), Riptide (FROMM *et al.*, 2020) e Larq (BANNINK *et al.*, 2021). Larq<sup>1</sup> é um framework *open source* considerado o estado da arte para a implementação, treinamento, conversão e inferência de BNNs.

Além das vantagens de reduções do tamanho de armazenamento e da computação, as BNNs são mais eficientes em termos de energia pois a redução da complexidade do *hardware* resulta em menos componentes lógicos além de uma área de *chip* menor. Outro ponto é que as BNNs podem ser consideradas mais confiáveis, pois demonstraram ter maior robustez contra ataques adversariais do que as DNNs normais (GALLOWAY; TAYLOR; MOUSSA, 2017). Em vista disso, portanto, as BNNs são promissoras para uma implementação eficiente e precisa para a computação de borda.

#### 2.1.5 Recursos Arquiteturais

A Unidade de Processamento Gráfico (GPU, *Graphics Processing Unit*) é a plataforma mais amplamente utilizada para implementar CNNs, pois oferece o melhor desempenho em termos de rendimento computacional puro. No entanto, GPUs possuem um gasto energético elevado e existem outras plataformas que oferecem um

https://github.com/larg/larg

Figura 9 – Acurácia *top*-5 de modelos BNNs nos últimos anos para o conjunto de dados ImageNet.

Fonte - Autor.

gasto energético menor, como o Circuito Integrado de Aplicação Específica (ASIC, Application Specific Integrated Circuit) ou Arranjo de Porta Programável em Campo (FPGA, Field Programmable Gate Array). Com um projeto de hardware orientado para rede neural, estas plataformas podem implementar um alto paralelismo e fazer uso das propriedades de computação da rede neural para remover lógica adicional resultando em um processamento com um menor gasto energético. Como multiplicações e convoluções de matrizes dominam mais de 90% das operações de uma CNN, estes são os principais alvos dos projetos de aceleradores para CNN (CHEN, Y. et al., 2020).

O ASIC fornece o melhor desempenho por valores de energia, pois pode ser estritamente adaptado para uma determinada aplicação. No entanto, ele não tem a flexibilidade de plataformas de computação de uso geral, como a Unidade Central de Processamento (CPU, *Central Processing Unit*) e GPU, e, portanto, não conseguem se adaptar a algoritmos de aprendizado profundo que mudam rapidamente.

Enquanto a implementação de um acelerador ASIC supera os aceleradores FPGAs em desempenho, o acelerador em FPGA oferece maior flexibilidade, limites de desenvolvimento mais baixos e menos ciclos de desenvolvimento. Além disso, é possível desenvolver um projeto para FPGA e posteriormente convertê-lo para ASIC (ON SEMICONDUCTOR, 2021). Portanto, o FPGA é a plataforma mais utilizada para desenvolvimento e testes de aceleradores de CNN.

## 2.2 ACELERADORES DE DOMÍNIO ESPECÍFICO

### 2.2.1 Contextualização e Definição

A maior parte da computação hoje em dia é realizada programando-se para processadores de propósito geral, ou CPUs. Segundo William J. Dally, Turakhia e Han (2020), o grande atrativo das CPUs se deve ao fato de que são fáceis de programar além de que existe uma ampla base de códigos para elas. No entanto, segundo Qadeer *et al.* (2015) os processadores podem ser considerados como uma máquina ineficiente.

A baixa eficiência dos processadores de uso geral é explicada na Figura 10, que compara o gasto energético de várias operações aritméticas com o gasto energético total de uma instrução para um processador RISC extremamente simples. A dissipação de energia das operações aritméticas que realizam o trabalho útil em uma computação permanece muito menor do que a energia desperdiçada nos *overheads* de instrução, como busca de instruções, decodificação, gerenciamento de *pipeline*, sequenciamento de programas, etc. (QADEER *et al.*, 2015). Dado esse *overhead*, pequenas mudanças nos núcleos existentes podem nos trazer melhorias de até 10%, mas se quisermos melhorias de maior ordem de grandeza ao mesmo tempo em que oferecemos programabilidade, precisamos aumentar o número de operações aritméticas por instrução de um para centenas (HENNESSY; PATTERSON, 2017).

Figura 10 – Comparação do custo energético de instruções para um processador RISC com o custo de operações aritméticas.

| RISC instruction  | Overhead | ALU | 125 pJ     |

|-------------------|----------|-----|------------|

| Load/Store D-\$   | Overhead | ALU | 150 pJ     |

| SP floating point |          | +   | 15–20 pJ   |

| 32-bit addition   |          | +   | 7 pJ       |

| 8-bit addition    |          | +   | 0.2-0.5 pJ |

Fonte – Qadeer et al. (2015).

Outro ponto importante é que a lei de Moore (MOORE *et al.*, 1965), que dita que o número de transistores de um *chip* de silício dobra a cada 2 anos, chegou ao fim (THEIS; WONG, 2017). Como consequência, será necessário mais especialização do processador para obter melhorias de desempenho. Além disso, aplicações emergentes, como inteligência artificial, estão exigindo desempenho computacional pesado que não pode ser atendido por arquiteturas convencionais. Segundo Urquhart (2021), para uma tarefa fixa ou uma gama limitada de tarefas, o dimensionamento de energia funciona

melhor do que para uma ampla gama de tarefas. Em vista destes problemas, para continuar escalando desempenho e eficiência devemos procurar arquiteturas alternativas, como os aceleradores de domínio específico (DALLY, William J.; TURAKHIA; HAN, 2020).

Um acelerador de domínio específico é um processador ou conjunto de processadores que são otimizados para realizar tarefas específicas. Eles são adaptados para atender às necessidades dos algoritmos exigidos para seu domínio. Por exemplo, no processamento de áudio, um processador pode ter um conjunto de instruções para implementar de forma otimizada algoritmos para cancelamento de eco. Em outro exemplo, um acelerador de DNN pode ter a operação de multiplicação e acumulação em um conjunto de elementos simultaneamente a fim de realizar operações de matriz com eficiência (URQUHART, 2021). Segundo Shepard (2021), inicialmente, os aceleradores de domínio específico foram desenvolvidos para reduzir o tempo de execução de tarefas particularmente intensivas em computação e, mais recentemente, os aceleradores estão sendo adotados para reduzir o consumo de energia necessário para executar determinadas tarefas. Além disso, o autor destaca que, mesmo que o consumo de energia de pico do acelerador seja maior que o consumo de energia de pico consumido por um processador de uso geral, o tempo de execução da tarefa é reduzido em uma quantidade tão grande que a energia total necessária para concluí-la é menor. Aceleradores foram projetados para aplicações em diferentes domínios, como processamento de imagens e aplicações de visão embarcada (SUN et al., 2018), criptografia (WU; WEAVER; AUSTIN, 2001), aprendizagem profunda (CHEN, Y.-H. et al., 2016), processamento de grafos (HAM et al., 2016), banco de dados (WU et al., 2014), etc. Como ilustrado na Figura 11, os aceleradores podem variar consideravelmente em sua especialização. Enquanto alguns aceleradores podem ser similares ou derivados de um núcleo de processador embarcado, outros podem ter uma programação limitada e parecer mais perto de um hardware com lógica fixa. Aceleradores mais especializados serão mais eficientes em termos de área de silício e consumo de energia. De acordo com Yu-Ting Chen et al. (2013), arquiteturas com aceleradores podem trazer uma eficiência energética de 10 a 100 vezes ao transferir a computação de um CPU de uso geral para aceleradores de domínio específico.

Segundo William J. Dally, Turakhia e Han (2020), os aceleradores de domínio específico exploram quatro técnicas diferentes para ganhos de desempenho e eficiência energética, são estes:

Especialização de dados: Operações especializadas em tipos de dados específicos de um determinado domínio podem fazer em um ciclo o que poderia levar dezenas de ciclos em uma unidade de computação convencional.

O laço interno de execução do algoritmo de muitas aplicações exigentes realizam de dezenas a centenas de operações aritméticas e lógicas utilizando

Figura 11 – Comparação da especialização de um acelerador de domínio específico

Fonte - CODASIP (2022)

apenas referências de memória local. Em muitos casos, a lógica especializada pode executar todo o laço interno em um único ciclo com uma pequena quantidade de área e potência.

- Paralelismo: Altos graus de paralelismo, frequentemente explorados em diversos níveis, proporcionando ganhos em desempenho. Para serem eficazes, as unidades paralelas devem explorar a localidade e fazer poucas referências de memória global ou seu desempenho será limitado à memória.

- Memória local e otimizada: Ao armazenar as principais estruturas de dados em várias pequenas memórias locais, uma largura de banda de memória muito alta pode ser alcançada com baixo custo e baixo consumo energético. Os padrões de acesso à memória global podem ser otimizados para alcançar a maior largura de banda de memória possível. Além disso, as principais estruturas de dados utilizadas na aplicação podem ser compactadas para multiplicar a largura de banda. Os acessos à memória podem ser balanceados em todos os canais de memória e cuidadosamente programados para maximizar a sua utilização.

- Redução de overhead: A especialização de hardware elimina ou reduz o overhead de interpretação do programa. De acordo com William J Dally et al. (2008), em um processador com execução "em ordem"gasta mais de 90% de sua energia em overheads como busca de instrução, decodificação de instrução, controle, etc.

William J. Dally, Turakhia e Han (2020) pontuam que para obter uma aceleração elevada e ganhos de eficiência de um *hardware* especializado geralmente é necessário a modificação do algoritmo subjacente. Os autores explicam que, como os algoritmos existentes são altamente ajustados para processadores convencionais de uso geral, eles raramente são a abordagem ideal para uma solução especializada. Em vez disso, o algoritmo e o *hardware* devem ser projetados em conjunto para otimizar simultane-

amente o desempenho e a eficiência, preservando ou aprimorando a acurácia. Para elucidar este ponto, William J. Dally, Turakhia e Han (2020) se referem ao trabalho de Han, Mao e William J Dally (2015) que mostrou como as redes neurais podem utilizar da otimização de *pruning* para serem compactadas até 30 vezes. Eles concluem que o *overhead* de se utilizar métodos esparsos como o *pruning* em *hardware* convencional tornava estes algoritmos desinteressantes, exceto pela compactação de memória. No entanto, o projeto em conjunto de um *hardware* para a aceleração das operações esparsas permite que esses algoritmos também sejam usados para reduzir a computação.

Segundo Patterson e Hennessy (2020), assim como o campo da computação mudou o uso de processadores com um único núcleo para processadores com diversos núcleos na última década devido à necessidade de escalar o desempenho, os projetistas de sistemas computacionais de agora estão trabalhando em aceleradores de domínio específico. Segundo os autores, o novo normal será que um computador consistirá em processadores padrões de uso geral para executar os programas convencionais e maiores, como sistemas operacionais, juntamente com processadores e aceleradores de domínio específico que executam apenas uma pequena gama de tarefas, mas que as executam extremamente bem. Desta forma, os autores preveem que os computadores serão muito mais heterogêneos do que os *chips* com processador multinúcleos do passado.

#### 2.2.2 Modelos de Aceleradores

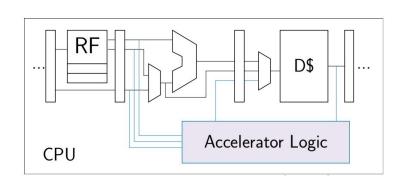

A escolha do tipo de integração com o processador tem um efeito fundamental nas considerações do projeto do acelerador e vice-versa. Os aceleradores são amplamente diferenciados em fortemente acoplados (do inglês *tightly-coupled*) e fracamente acoplados (do inglês *loosely-coupled*) com base em sua integração com o processador (MUCHANDI, 2020).

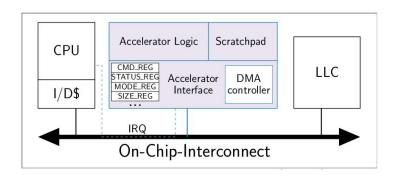

A Figura 12 apresenta um modelo de acelerador fortemente acoplado. Este modelo de acelerador consiste em uma ou mais unidades funcionais de *hardware* especializadas projetadas para acelerar partes críticas de uma aplicação; por exemplo, o *loop* interno para um determinado algoritmo ou uma sequência de funções trigonométricas. Este tipo de acelerador está localizado dentro ou muito próximo do núcleo de processamento e portanto são incluídos no datapath da CPU como coprocessador. Desta maneira, para acessá-los é necessário expandir o Conjunto de Instruções (ISA, *Instruction Set Archtecture*) para incluir instruções especiais para gerenciar sua operação. Além disso, este modelo compartilha com o núcleo de processamento os recursos chaves como banco de registradores, *cache* de dados, etc. e, portanto, paralisa a execução do pipeline até que o acelerador complete a sua execução. A vantagem deste modelo é que possui um *overhead* de chamada nula. No entanto, eles podem

complicar ainda mais o projeto da CPU e impor desafios de sincronização para atender as restrições de frequência de clock que são definidas para a CPU. Além disso, eles possuem portabilidade limitada entre diferentes projetos de sistemas, pois é muitas vezes necessário adaptar a interface do acelerador com a CPU (COTA *et al.*, 2015).

Figura 12 – Acelerador fortemente acoplado

Fonte - Cota et al. (2015).

A Figura 13 apresenta um modelo de acelerador fracamente acoplado. Neste modelo, o acelerador é localizado fora do núcleo da CPU e interage com a mesma através do barramento de interconexão do *chip*. Estar fora do núcleo oferece ao acelerador com esse modelo um orçamento de área maior do que os aceleradores fortemente acoplados, pois neste caso ele não degrada o desempenho do *pipeline* do processador ou o tempo de acesso à *cache*. Isso permite blocos lógicos maiores e com caminhos de dados mais complexos que podem implementar e acelerar uma determinada aplicação por completo, como, por exemplo, uma transformada rápida de Fourier ou um algoritmo de codificação de imagem completo. Além disso, estar fora do núcleo da CPU permite implementar memórias locais privadas, também conhecidas como *scratchpads* (BANAKAR *et al.*, 2002), que armazenam os dados de entrada a serem processados, resultados temporários e os dados de saída a serem escritos de volta na memória (COTA *et al.*, 2015).

Enquanto que os aceleradores fortemente acoplados são restritos no pipeline de uma CPU e, portanto, experimentam benefícios limitados de uma personalização completa, os aceleradores fracamente acoplados ignoram completamente os *overheads* de CPU (instruções, *caches*, etc.) e podem ser otimizados com uma maior liberdade (CHEN, Y.-T. *et al.*, 2013). Cota *et al.* (2015) analisaram os efeitos dos *overhead* de comunicação interna do chip e chamadas do acelerador em diferentes projetos de aceleradores com base no acoplamento com o processador e na comunicação com a memória. Os autores apresentaram uma comparação quantitativa entre projetos de aceleradores de alto desempenho para tarefas como Transformada Rápida de Fourier, encriptação AES, etc. aplicados em diversos modelos de acoplamento como forte-

Figura 13 – Acelerador fracamente acoplado

Fonte – Cota *et al.* (2015).

mente acoplado com uma CPU, fracamente acoplado com DMA para a cache de último nível e fracamente acoplado com DMA para a memória DRAM. Por fim, os autores concluíram que para cargas de trabalho com tamanhos de dados não triviais a melhor configuração é de aceleradores fracamente acoplados com blocos de memória privados personalizados para a determinada tarefa.

#### 2.2.3 Aceleradores de DNN

Além das melhorias de algoritmos das redes neurais e otimizações como especificados na Seção 2.1.3, o desempenho de execução dessas redes depende muito da capacidade de computação do *hardware*. Como mencionado na Seção 2.1.5, os processadores de uso geral, como GPUs, atuam como o pilar da era do aprendizado profundo, especialmente no lado da nuvem. No entanto, para a computação de borda, a disponibilidade de recursos e energia geralmente é muito limitada de modo que minimizar a latência, energia e área tornou-se uma preocupação de *design* inevitável. Isso motiva o estudo de aceleradores especializados desenvolvidos para o domínio das redes neurais. Ao sacrificar a flexibilidade até certo ponto, esses aceleradores se concentram em padrões específicos das redes neurais para obter um desempenho satisfatório por meio da otimização da arquitetura de processamento, hierarquia de memória e mapeamento de fluxo de dados (DENG, L. *et al.*, 2020).

Como ilustrado na Figura 14, os aceleradores de DNNs podem ser divididos fundamentalmente em duas categorias baseado na forma em como executam a rede neural: aceleradores de streaming e aceleradores de camadas. Uma comparação entre estas duas arquiteturas é explicado a seguir:

Aceleradores de streaming: Aceleradores com essa arquitetura são customizados para uma topologia de rede neural específica onde é instanciado uma unidade de computação para cada camada (KROES et al., 2020). Como é implementado um hardware otimizado para cada camada, esse tipo de arquitetura geralmente oferece uma latência melhor, no entanto, requerem mais recursos do que os aceleradores de camadas. Além disso, apenas suportam a topologia de rede neural previamente definida antes da implementação. Portanto, se uma rede é otimizada e implementada para uma aplicação específica, ela precisa ser alterada estruturalmente e reprojetada para então ser utilizada em outras aplicações (CHO *et al.*, 2021). Como notado por Kroes *et al.* (2020), é um grande desafio alcançar alta acurácia com este tipo de arquitetura pois os modelos de redes convolucionais do estado da arte aumentam significativamente a quantidade de unidades computacionais necessárias para implementar a topologia da rede inteira, como também necessitam de um tamanho de memória interna maior para armazenar os pesos.

• Aceleradores de camadas: Aceleradores de camadas são projetados para manipular uma determinada camada por vez da topologia de rede neural. Além disso, como um acelerador com este tipo de arquitetura precisa ser capaz de lidar com vários tipos de camadas diferentes (diferentes tamanhos de mapas de atributos, diferentes números filtros, etc), a maioria destes aceleradores são projetados com arquiteturas reconfiguráveis que podem lidar com várias topologias diferentes de redes. Portanto, como apontado por Cho et al. (2021), este tipo de arquitetura pode ser mais adequado para aplicações com recursos limitados como na computação.

#### 2.3 PLATAFORMAS E COMPONENTES

Esta seção apresenta conceitos adicionais que compõem o trabalho.

#### 2.3.1 FPGA

Os FPGAs são dispositivos programáveis que fornecem uma plataforma flexível para implementar funcionalidades de *hardware* personalizadas a um baixo custo de desenvolvimento. Eles consistem principalmente de um conjunto de células lógicas programáveis, chamadas de blocos lógicos configuráveis (CLBs), uma rede de interconexão programável e um conjunto de células programáveis de entrada e saída ao redor do dispositivo (VILLASENOR; MANGIONE-SMITH, 1997). Além disso, eles têm um rico conjunto de componentes incorporados, como blocos de processamento de sinal digital (DSP) que são usados para executar operações aritméticas intensivas, como multiplicar e acumular, *Block RAMs (BRAMs)*, *Look-Up Tables (LUTs)*, *Flip-Flops* (FFs), unidade de gerenciamento de clock e outros.

Em um FPGA, a porta lógica XNOR pode ser implementada como uma LUT. A LUT é um dos principais recursos em um FPGA moderno e, através dessas LUTs,

heterogeneously sized; tailored to compute requirements layer L layer 1 laver 2 on-chip compute compute array compute array array weights weights weights carry intermediate activations via on-chip channels off-chip External memory or images peripheral devices classifications (a) Acelerador de streaming dataflow on-chip compute array for multiple layers on-chip feedback path off-chip main memory weights classifications intermediate activations (b) Acelerador de camadas

Figura 14 – Comparação entre os tipos de aceleradores para DNN

Fonte - Blott et al. (2018).

mesmo dispositivos FPGA pequenos podem realizar até trilhões de operações XNOR em um segundo. Além disso, em comparação com CNNs de ponto flutuante ou quantizadas, os pesos binários em BNNs gastam menos espaço de memória para armazenálos. Isso significa que estes pesos podem ser armazenados na memória interna destes dispositivos, a BRAM, onde é alcançado uma velocidade de acesso muito mais alta, bem como menor consumo de energia.

Sendo assim, FPGAs são adequados para BNNs, pois seus cálculos dominantes são operações lógicas *bit* a *bit* e seus requisitos de memória são bastante reduzidos.

# 2.3.2 RISC-V

O RISC-V (WATERMAN *et al.*, 2014) é uma arquitetura que começou a ser desenvolvida pela Universidade de Berkeley em 2010. Atualmente, o RISC-V é um ISA

modular, ampliável através de extensões, aberta e *royalty-free*. Sua especificação está inteiramente disponível e seu objetivo principal é servir de base para que empresas, instituições, ou qualquer outra entidade possa desenvolver não somente periféricos compatíveis mas também seus próprios núcleos, SoCs e aceleradores.

Por ser projetado de forma modular, o RISC-V permite que grupos de instruções sejam utilizados conforme necessário. Isto resulta em uma implementação que utiliza exatamente o que a aplicação precisa, sem a necessidade de desperdiçar área e energia que não seriam utilizadas. Além disso, possui um grupo especial de instruções em que desenvolvedores podem adicionar qualquer instrução necessária para a aplicação que desejam acelerar, sem quebrar a compatibilidade de software.

## **3 TRABALHOS RELACIONADOS**

A partir de uma pesquisa exploratória, foram levantados diversos trabalhos que desenvolveram uma arquitetura para realizar a aceleração de BNNs. Com a taxonomia apresentada na Seção 2.2.3 foi possível filtrar ainda mais os trabalhos de interesse.

Os primeiros aceleradores de BNNs geralmente possuíam a arquitetura de streaming e eram validados com topologias de redes consideradas pequenas, onde a resolução da imagem de entrada é, como por exemplo, 32x32 pixels. Isso se deve ao fato de que este é o método que possui menos overhead e menor latência. No entanto, esta arquitetura limita o uso de aplicações, pois o tamanho da topologia de rede suportada também é limitada.

O acelerador de *streaming* FINN (UMUROGLU *et al.*, 2017) apresentou um resultado para topologia AlexNet, mas, como previsto, é necessário utilizar FPGA de alto desempenho com grande quantidade de componentes lógicos e memória, inviabilizando seu uso na computação de borda.

O acelerador LP-BNN (GENG *et al.*, 2019) aprimora a arquitetura de FINN para dar suporte às camadas residuais presentes na rede ResNet e propõe uma técnica de balanceamento de carga de trabalho entre o paralelismo das camadas para alcançar a máxima utilização de *hardware*. Porém, mesmo com as otimizações, os autores reportam o uso de 509K LUTs de um Xilinx Kintex KCU1500 portanto, o uso de recursos do FPGA ainda é exorbitante e inviável na computação de borda. Sendo assim, limitou-se a análise para arquiteturas de aceleradores de camadas.

FBNA (GUO *et al.*, 2018) foi a primeira arquitetura de acelerador de rede neural totalmente binarizada. Este acelerador utiliza memórias locais para o armazenamento dos mapas de atributos de entrada, pesos e mapas de atributos de saída. Assim, é realizada a busca dos dados de entrada e pesos, realizada as operações em seu *datapath* e o resultado da acumulação escrito na memória local de saída. Os autores avaliam o acelerador para as topologias beseadas em CIFAR10 e SVHN, que possuem dimensões de entrada 32x32.

Shuang Liang *et al.* (2018) apresentaram o acelerador FP-BNN, onde foi reportado resultado para um modelo de rede mais complexa, a AlexNet. Os dados de entrada são carregados da memória externa para uma memória interna e então é realizado as operações utilizandos vários *datapaths* para o processamento de dados em paralelo. Apesar do ganho de desempenho pela paralelização, a quantidade de recursos utilizados ainda é muito alta para a implementação na computação de borda visto que, para o modelo AlexNet, o acelerador requer mais de 230K ALMs de um FPGA Altera Stratix-V.

Conti, Schiavone e Benini (2018) divulgaram o acelerador XNE. Este é um acelerador configurável em que os autores validaram em um sistema baseado em micro-

controlador. Sua arquitetura é composta por um controlador que pode ser configurado através do mapeamento de memória utilizando protocolo AMBA APB. Além disso, Em vez de depender de um processador externo para calcular os deslocamentos para acesso à memória e iterações da execução do laço interno, os autores incluíram um processador de microcódigo que utiliza uma pequena ISA personalizada e suas instruções são carregadas através do mapeamento de memória. Este trabalho demonstrou o suporte a cenários de trabalho complicados e para aplicações práticas, no entanto, apenas avaliado para dispositivo ASIC.

Cho *et al.* (2021) estendem o trabalho de Conti, Schiavone e Benini (2018) e modificam o agendamento de dados das primeiras camadas para extrair um maior paralelismo. Desse modo, os autores alcançaram uma taxa de transferência e eficiência energética maior. Além disso, os autores reportaram a implementação em FPGA Xilinx onde é utilizado apenas 4,8K LUTs.

A Tabela 1 sintetiza as informações levantadas destes aceleradores selecionados. Em relação às topologias de redes utilizadas, percebe-se que os aceleradores são predominantemente avaliados utilizando modelos de BNNs que não refletem o estado da arte. Como mencionado anteriormente, as BNNs recentes utilizam técnicas que permitem alcançar uma acurária maior. Sendo assim, este trabalho visa utilizar conceitos destas arquiteturas e modificá-los para sua utilização com topologias de BNN modernas em FPGA.

| Tabela 1 | <ul> <li>Comparação</li> </ul> | entre trabalnos | relacionados. |

|----------|--------------------------------|-----------------|---------------|

|----------|--------------------------------|-----------------|---------------|

| Trabalho                                    | Camadas       | Topologias              | Plataforma |

|---------------------------------------------|---------------|-------------------------|------------|

| FBNA (GUO <i>et al.</i> , 2018)             | BC, BN, P, FC | CIFAR10, SVHN           | FPGA       |

| FP-BNN (LIANG, Shuang <i>et al.</i> , 2018) | BC, BN, P, FC | MNIST, CIFAR10, AlexNet | FPGA       |

| XNE (CONTI; SCHIAVONE; BENINI, 2018)        | BC, BN, FC    | VGG, ResNet             | ASIC       |

| Cho <i>et al.</i> (2021)                    | BC, BN, P, FC | CIFAR10, VGG            | FPGA       |

BC=Convolução Binária, BN=*Batch Normalization*, P=*Pooling*, FC=Camada Densa (*Fully Connected*)

Fonte – Autor.

# 4 PROJETO E IMPLEMENTAÇÃO

A metodologia empregada consistiu primeiramente em realizar uma análise nas topologias de BNNs do estado da arte e levantar especificações que delimitam a arquitetura e funcionamento do acelerador projetado. Após essa investigação, são definidos conceitos importantes como a organização dos dados e o algoritmo para convolução binária. Por fim, é apresentado a microarquitetura proposta e seus componentes.

## 4.1 ANÁLISE BNNS

# 4.1.1 Topologia

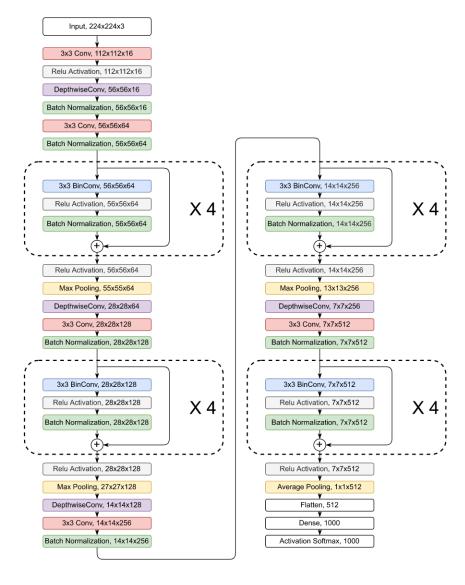

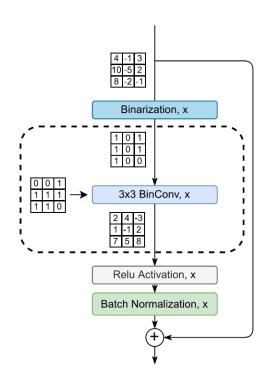

A topologia da BNN a ser executada influencia diretamente no projeto do acelerador. Certos parâmetros da rede podem inviabilizar algumas soluções enquanto pode permitir outras soluções mais otimizadas. Em vista disso, como uma das motivações é executar BNNs do estado da arte, inicialmente, foram analisadas as topologias das seguintes BNNs: *QuickNet* (BANNINK *et al.*, 2021) e *BinaryResNetE18* (BETHGE *et al.*, 2019). A Figura 15 apresenta topologia da rede *QuickNet*. Devido à semelhança estre estas duas redes, apenas uma delas (a rede *Quicknet*) será detalhada e utilizada como base para a implementação deste trabalho. A área delimitada pela linha tracejada indica que a sequência de componentes no seu interior se repete pela quantidade de vezes indicada no lado direito. Para a operação de convolução binária (denominada "BinConv"), é implicitamente realizada a operação de binarização dos dados seguindo a Equação (3).

A partir da análise realizada foram levantados os seguintes pontos:

- É utilizado exclusivamente um filtro de convolução com a dimensão 3x3;

- O bloco residual é predominantemente utilizado para as camadas que utilizam convolução binária;

- É empregado o padding em todas as convoluções binárias.

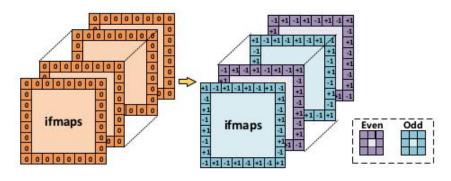

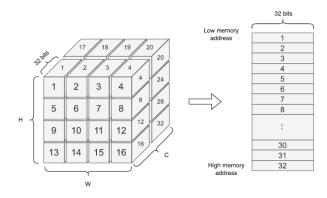

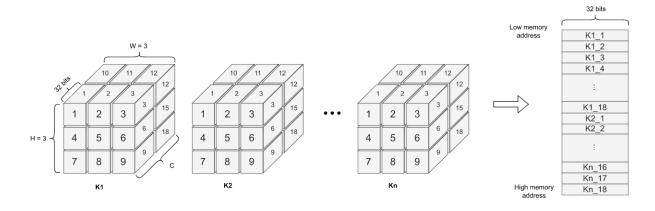

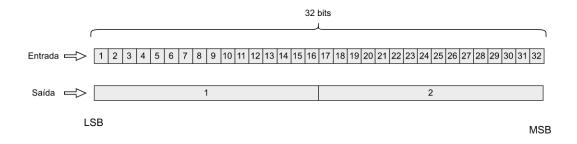

Segundo Liu *et al.* (2018), o bloco residual aumenta a capacidade de representação da rede binária e a ajuda a atingir uma acurácia maior. Como exemplificado pela Figura 16, as conexões residuais permitem a propagação de atributos para as camadas mais profundas da rede e assim, reduzindo o erro decorrente pela binarização.