# UNIVERSIDADE FEDERAL DE SANTA CATARINA INFORMÁTICA E ESTATÍSTICA

Gabriel Arthur Gerber Andrade

### EXPLOITING CANONICAL DEPENDENCE CHAINS AND ADDRESS BIASING CONSTRAINTS TO IMPROVE RANDOM TEST GENERATION FOR SHARED-MEMORY VERIFICATION

Florianópolis

2017

#### Gabriel Arthur Gerber Andrade

### EXPLOITING CANONICAL DEPENDENCE CHAINS AND ADDRESS BIASING CONSTRAINTS TO IMPROVE RANDOM TEST GENERATION FOR SHARED-MEMORY VERIFICATION

Dissertação submetida ao Programa de Pós-Graduação em Ciência da Computação para a obtenção do Grau de Mestre em Ciência da Computação. Universidade Federal de Santa Catarina Orientador: Prof. Luiz Cláudio Villar dos Santos, Dr.

Florianópolis

2017

## Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Andrade, Gabriel Arthur Gerber

Exploiting canonical dependence chains and address biasing constraints to improve random test generation for shared-memory verification / Gabriel Arthur Gerber Andrade; orientador, Luiz Cláudio Villar dos Santos - Florianópolis, SC, 2017.

109 p.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Ciência da Computação.

Inclui referências

1. Ciência da Computação. 2. Verificação de projeto. 3. Memória compartilhada. 4. Coerência de memória. 5. Consistência de memória. I. Villar dos Santos, Luiz Cláudio. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Ciência da Computação. III. Título.

#### Gabriel Arthur Gerber Andrade

### EXPLOITING CANONICAL DEPENDENCE CHAINS AND ADDRESS BIASING CONSTRAINTS TO IMPROVE RANDOM TEST GENERATION FOR SHARED-MEMORY VERIFICATION

Esta Dissertação foi julgada aprovada para a obtenção do Título de "Mestre em Ciência da Computação", e aprovada em sua forma final pelo Programa de Pós-Graduação em Ciência da Computação.

| Florianópolis, 17 de Fevereiro de 2017.                                                           |         |

|---------------------------------------------------------------------------------------------------|---------|

|                                                                                                   |         |

| Prof <sup>a</sup> . Carina Friedrich Dorneles, Dr. <sup>a</sup><br>Coordenadora do Programa       |         |

| anca Examinadora:                                                                                 | Banca I |

|                                                                                                   |         |

| Prof. Luiz Cláudio Villar dos Santos, Dr.<br>Universidade Federal de Santa Catarina<br>Orientador |         |

|                                                                                                   |         |

| Prof. Rômulo Silva de Oliveira, Dr.<br>Universidade Federal de Santa Catarina                     |         |

| Prof. Djones Vinicius Lettnin, Dr. Universidade Federal de Santa Catarina                         |         |

| Prof. Laércio Lima Pilla, Dr. Universidade Federal de Santa Catarina                              |         |

#### ACKNOWLEDGEMENTS

Many thanks go to my advisor for his guidance, support, and confidence. His pragmatism has been crucial to finish this work in just two years. During this time, he has shown me how "less is more".

I have been fortunate to be among great friends and colleagues. Particularly, I would like to thank the following people for providing the experimental infrastructure for my research: Eberle Andrey Rambo, Leandro da Silva Freitas, Olav Philipp Henschel, and Marleson Graf.

I would like to thank the members of the Examination Committee for their contributions to improve this work.

I would like to thank my parents, my relatives, and my friends. They were instrumental in supporting me. And, particularly, without these same people I would not be who I am today.

I would like to express my gratitude to the financial support of the Brazilian Research Agency CAPES (within the DS Program).

"Vamos em frente que atrás vem gente" — A frase preferida de meus avôs.

Adolfo Gerdelmann Andrade e Guido Gerber  $(in\ memoriam).$

#### RESUMO ESTENDIDO

#### Introdução

A verificação funcional do projeto de um sistema com multiprocessamento em *chip* (CMP) vem se tornando cada vez mais desafiadora por causa da crescente complexidade para suportar a abstração de memória compartilhada coerente, a qual provavelmente manterá seu papel crucial para multiprocessamento em *chip*, mesmo na escala de centenas de processadores. A verificação funcional baseia-se principalmente na geração de programas de teste aleatórios.

#### Trabalhos Correlatos e Gerador Proposto

Embora frameworks de verificação funcional que se baseiam na solução de problemas de satisfação de restrições possuam a vantagem de oferecer uma abordagem unificada para gerar estímulos aleatórios capazes de verificar todo o sistema, eles não são projetados para explorar não-determinismo, que é um importante mecanismo para expôr erros de memória compartilhada.

Esta dissertação reporta novas técnicas que se baseiam em lições aprendidas de ambos—os frameworks de verificação de propósitos gerais e as abordagens especializadas em verificar o modelo de memória. Elas exploram restrições sobre endereços e cadeias canônicas de dependência para melhorar a geração de testes aleatórios enquanto mantêm o papel crucial do não-determismo como um mecanismo-chave para a exposição de erros.

### Geração de Sequências

Ao invés de selecionar instruções aleatoriamente, como faz uma técnica convencional, o gerador proposto seleciona instruções de acordo com cadeias de dependências pré-definidas que são comprovadamente significativas para preservar o modelo de memória sob verificação. Esta dissertação explora cadeias canônicas, definidas por Gharachorloo, para evitar a indução de instruções que, sendo desnecessárias para preservar o modelo de memória sob verificação, resultem na geração de testes ineficazes.

### Assinalamento de Endereços

Em vez de selecionar aleatoriamente padrões binários para servir de endereços efetivos de memória, como faz um gerador convencional, o gerador proposto aceita restrições à formação desses endereços de forma a forçar o alinhamento de objetos em memória, evitar falso comparti-

lhamento entre variáveis e especificar o grau de competição de endereços por uma mesma linha de cache.

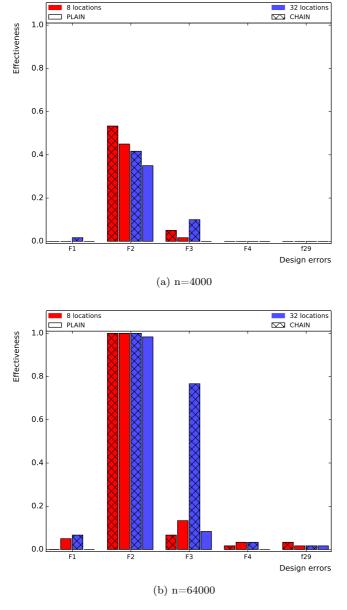

#### Avaliação Experimental

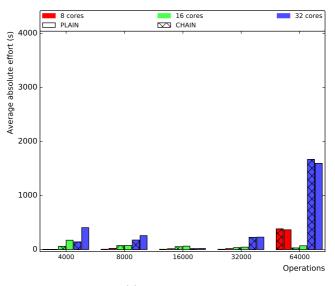

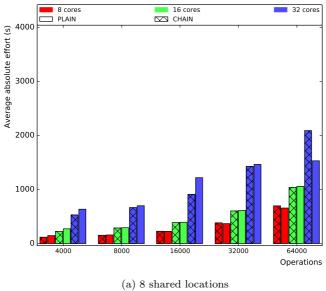

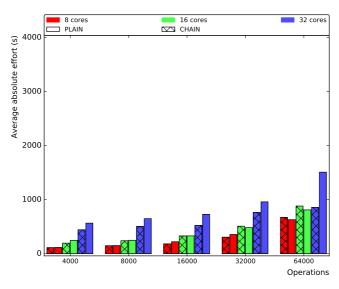

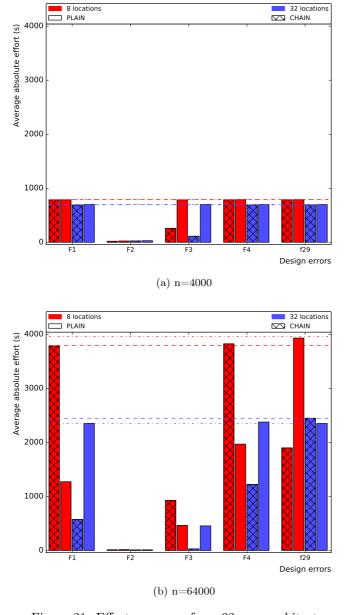

Um novo gerador, construído com as técnicas propostas, foi comparado com um gerador convencional de testes aleatórios. Ambos foram avaliados em arquiteturas de 8, 16, e 32 núcleos, ao sintetizar 1200 programas de testes distintos para verificar 5 projetos derivados, cada um contendo um diferente tipo de erro (6000 casos de uso por arquitetura). Os testes sintetizados exploraram uma ampla variedade de parâmetros de geração (5 tamanhos de programas, 4 quantidades de posições compartilhadas de memória, 4 mixes de instruções, e 15 sementes aleatórias). Os resultados experimentais mostram que, em comparação com um convencional, o novo gerador tende a expor erros para um maior número de configurações dos parâmetros: ele aumentou em 38% o potencial de expor erros de projeto. Pela análise dos resultados da verificação sobre todo o espectro de parâmetros, descobriu-se que os geradores requerem um número bastante distinto de posições de memória para alcançar sua melhor exposição. Os geradores foram comparados quando cada um explorou a quantidade de posições de memória correspondente à sua melhor exposição. Nestas condições, quando destinados a projetos com 32 núcleos através da exploração de todo o espectro de tamanhos de testes, o novo gerador expôs um tipo de erro tão frequentemente quanto a técnica convencional, dois tipos com 11% mais frequência, um tipo duas vezes, e um tipo 4 vezes mais frequentemente. Com os testes mais longos (64000 operações) ambos os geradores foram capazes de expor todos os tipos de erros, mas o novo gerador precisou de 1,5 a 15 vezes menor esforço para expor cada erro, exceto por um (para o qual uma degradação de 19% foi observada).

### Conclusões e Perspectivas

Com base na avaliação realizada, conclui-se que, quando se escolhe um número suficientemente grande de variáveis compartilhadas como parâmetro, o gerador proposto requer programas de teste mais curtos para expor erros de projeto e, portanto, resulta em menor esforço, quando comparado a um gerador convencional.

Palavras-chave: Verificação de projeto. Memória compartilhada. Coerência de memória. Consistência de memória.

#### ABSTRACT

Albeit general functional processor verification frameworks relying on the solution of constraint satisfaction problems have the advantage of offering a unified approach for generating random stimuli to verify the whole system, they are not designed to exploit non-determinism, which is an important mechanism to expose shared-memory errors. This dissertation reports new techniques that build upon the lessons learned from both—the general verification frameworks and the approaches specifically targeting memory-model verification. They exploit address biasing constraints and canonical dependence chains to improve random test generation while keeping the crucial role of non-determinism as a key mechanism to error exposure. A new generator, built with the proposed techniques, was compared to a conventional random test generator. Both were evaluated for 8, 16, and 32-core architectures, when synthesizing 1200 distinct test programs for verifying 5 derivative designs containing each a different type of error (6000 use cases per architecture). The synthesized tests explored a wide variety of generation parameters (5 program sizes, 4 shared-location counts, 4 instruction mixes, and 15 random seeds). The experimental results show that, as compared to a conventional one, the new generator tends to expose errors for a larger number of parameter settings: it increased by 38% the potential for exposing design errors. By analyzing the verification outcomes over the full parameter ranges, we found out that the generators require quite distinct numbers of shared locations to reach best exposure. We compared them when each generator exploited the location count leading to its best exposure. In such conditions, when targeting 32-core designs by exploring the whole range of test lengths, the new generator exposed one type of error as often as the conventional technique, two types 11% more often, one type twice as often, and one type 4 times as often. With the longest tests (64000 operations) both generators were able to expose all types of errors, but the new generator required from 1.5 to 15 times less effort to expose each error, except for one (for which a degradation of 19% was observed).

**Keywords:** Design verification. Shared memory. Memory coherence. Memory consistency.

### LIST OF FIGURES

| Figure 1  | Structure of the proposed generator                               | 35 |

|-----------|-------------------------------------------------------------------|----|

| Figure 2  | An example of how to enforce a significant ordering               | 41 |

| Figure 3  | Algorithm Sequence-Generator                                      | 44 |

| Figure 4  | Routine chain                                                     | 45 |

| Figure 5  | Auxiliary routines of the generator                               | 46 |

| Figure 6  | The interpretation of a competition pattern $\ldots \ldots$       | 49 |

| Figure 7  | Enumeration of all CPs for $s = 4 \dots$                          | 50 |

| Figure 8  | CPs induced by $cbc = (3, 4)$ for $s = 8 \dots$                   | 51 |

| Figure 9  | Relation between address fields and biasing constraints           | 52 |

| Figure 10 | $\label{pattern} \mbox{Routine select-competition-pattern}$       | 55 |

| Figure 11 | Algorithm Address-Assigner                                        | 57 |

| Figure 12 | Algorithm Instruction-Synthesizer                                 | 60 |

| Figure 13 | The relation between effectiveness, runtime and effort $\!\ldots$ | 66 |

| Figure 14 | Exposure as a function of test length                             | 70 |

| Figure 15 | A breakdown for error exposure capability (p=32)                  | 71 |

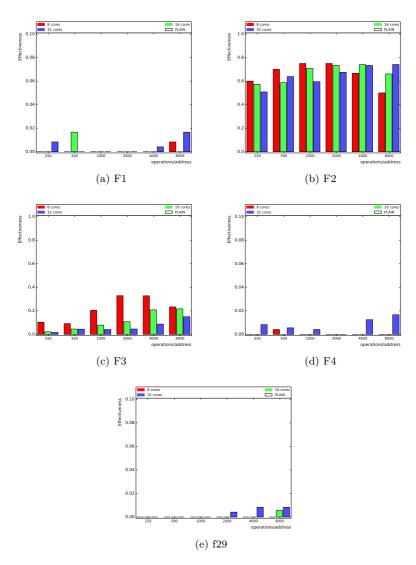

| Figure 16 | Exposure per error for a 32-core architecture                     | 73 |

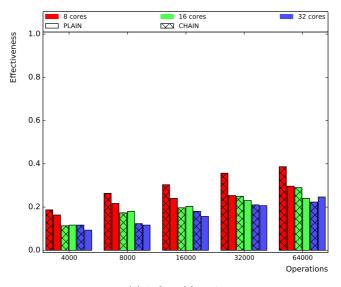

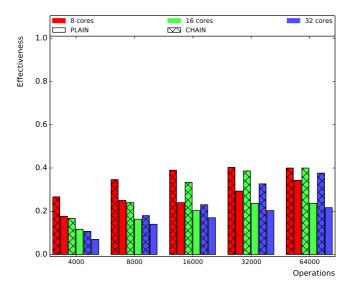

| Figure 17 | Effectiveness as a function of test length                        | 75 |

| Figure 18 | Effectiveness per error for a 32-core architecture                | 76 |

| Figure 19 | Effort as a function of test length (joint exposure)              | 79 |

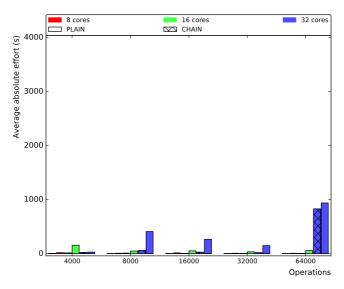

| Figure 20 | Effort as a function of test length (overall exposure)            | 80 |

| Figure 21 | Effort per error for a 32-core architecture                       | 82 |

| Figure 22 | Candidate chains to expose an error                               | 89 |

| Figure 23 | Sharing-level distributions for errors                            | 98 |

### LIST OF TABLES

| Table 1  | Description of classes of artificial design errors            | 62  |

|----------|---------------------------------------------------------------|-----|

| Table 2  | Target mixes                                                  | 63  |

| Table 3  | Percentage of scenarios with potential for error exposure     | 68  |

| Table 4  | Improvement in effectiveness under joint exposure             | 74  |

| Table 5  | Improvement in effort under joint exposure                    | 78  |

| Table 6  | Improvement in useful effort under best exposure              | 83  |

| Table 7  | Improvement in overall effort under best exposure             | 84  |

| Table 8  | Test length required for full exposure in 32-core designs .   | 84  |

| Table 9  | Percentage of scenarios with potential for exposure (s=8)1 $$ | .03 |

| Table 10 | Percentage of scenarios with potential for exposure (s=32)1   | .03 |

| Table 11 | Improvement in effectiveness under joint exposure (s=8) $1$   | .04 |

| Table 12 | Improvement in effectiveness under joint exposure (s=32)1 $$  | .04 |

|          |                                                               |     |

### LIST OF ABBREVIATIONS AND ACRONYMS

| FSM   | Finite State Machine              | 28 |

|-------|-----------------------------------|----|

| CMP   | Chip Multiprocessing              | 31 |

| ARM   | Advanced RISC Machine             | 38 |

| RISC  | Reduced Instruction Set Computing | 38 |

| CPU   | Central Processing Unit           | 61 |

| SPARC | Scalable Processor Architecture   | 61 |

| MESI  | Modified Exclusive Shared Invalid | 61 |

| LRU   | Least Recently Used               | 61 |

### LIST OF SYMBOLS

| Test genera             | ation parameters                                             |    |

|-------------------------|--------------------------------------------------------------|----|

| p                       | Number of processors                                         | 35 |

| n                       | Number of memory operations                                  | 35 |

| s                       | Number of shared locations                                   |    |

| M                       | Target mix of canonical dependence chains                    | 35 |

| seed                    | Random seed                                                  | 35 |

| Memory op               | perations                                                    |    |

| L                       | A Load operation                                             | 37 |

| S                       | A Store operation                                            | 37 |

| $I_j$                   | A load or store instruction                                  | 37 |

| MB                      | A memory barrier                                             | 37 |

| O                       | Set of memory operations issued by all processors            | 37 |

| $\mathcal{O}^i$         | Set of memory operations issued by some processor $i$        | 37 |

| $\mathcal{O}_a^i$       | Subset of memory operations to the same location $a$         | 37 |

| $(O_j)_a^i$             | An operation $O_i$ issued by processor $i$ to location $a$ . | 37 |

| $Val_a^0$               | Initial value stored at location $a 	ext{ } 	ext{.} 	ext{.}$ | 37 |

| $Val[(O_j)_a^i]$        | Value written or returned by some operation                  | 37 |

| Relations a             | nd dependence chains                                         |    |

| $\prec_{po}$            | Program order                                                | 37 |

| $\leq$                  | Execution order                                              | 37 |

| $\prec_{spo}$           | Significant program order                                    | 36 |

| $\leq_{co}$             | Conflict order                                               | 39 |

| $\prec$                 | Precedence relation                                          | 39 |

| ${A \prec B \prec}_*$   | Zero or more occurrences of a pattern                        | 39 |

| $\{A \prec B \prec\}_+$ | One or more occurrences of a pattern                         | 39 |

| $\mathcal{C}_{\kappa}$  | Set of chains from category $\kappa$ in a given test program | 40 |

| C                       | Set of all chains                                            | 40 |

| length(c)                      | Number of operations in chain $c$                                 | 40 |

|--------------------------------|-------------------------------------------------------------------|----|

| $length^i(c)$                  | Number of operations in chain $c$ is<br>sued by processor $i$     | 40 |

| $T^i$                          | Thread assigned to processor $i$                                  | 42 |

| $T^i[x]$                       | Content of the $x$ -th slot of thread $T^i$                       | 43 |

| $av^i$                         | Number of available slots in thread $T^i$                         | 43 |

| $M[\kappa]$                    | Target proportion of chains specified for category $\kappa$ .     | 43 |

| $C[\kappa]$                    | Fraction of all slots available for category $\kappa$             | 43 |

| Val[a]                         | Last value written to location $a$                                | 43 |

| $\lambda_{min}(\kappa)$        | Length feasibility of minimal chain from category $\kappa.$       | 43 |

| $\beta_{min}(\kappa)$          | Breadth feasibility of minimal chain from category $\kappa$       | 43 |

| $\phi_{min}(\kappa)$           | Feasibility of minimal chain from category $\kappa$               | 43 |

| X                              | Set of slots from thread $T^i$ filled with operations             | 43 |

| $X_{x>m}$                      | Subset of X with slots x such that $x > m \dots$                  | 43 |

| $max_a^i$                      | Last slot of thread $T^i$ referencing location $a 	cdots$         | 43 |

|                                |                                                                   |    |

| Locations,                     | addresses, and bit fields                                         |    |

|                                |                                                                   |    |

| A                              | Set of shared locations                                           | 35 |

| $a_i$                          | A shared location in A                                            | 35 |

| E                              | Set of effective addresses                                        | 35 |

| $e_i$                          | An effective address in $E$                                       | 35 |

| abc                            | Alignment biasing constraint                                      | 35 |

| sbc                            | Sharing biasing constraint                                        | 35 |

| cbc                            | Competition biasing constraint                                    | 35 |

| $\kappa$                       | Number of addresses mapping to distinct cache rows                | 35 |

| $\chi$                         | Maximum degree of competition for a same cache row                | 35 |

| C                              | Relation "locations competing for a cache row"                    | 49 |

| CP                             | Undirected graph representing a competition pattern               | 49 |

| $A_x$                          | $x$ -th component of a partition of $A$ induced by $C \dots$      | 50 |

| N                              | Number of bits in an effective address                            | 51 |

| T                              | Number of bits in the tag field                                   | 51 |

| I                              | Number of bits in the index field                                 | 51 |

| O                              | Number of bits in the block offset field                          | 51 |

| $\alpha$                       | Mapping from locations to effective addresses                     | 52 |

| $\mathcal{CP}_{\kappa,\chi,s}$ | Set of $CP$ s induced by $cbc = (\kappa, \chi)$ for $s$ locations | 52 |

| $e.\mathcal{T}$                      | Tag field of address $e$                                             | 52 |

|--------------------------------------|----------------------------------------------------------------------|----|

| $e.\mathcal{I}$                      | Index of address $e$                                                 | 52 |

| $e.\mathcal{O}$                      | Block offset of address $e$                                          | 52 |

| f                                    | Inducer for a competition pattern                                    | 53 |

| c                                    | Cardinality of a connected component in a $CP$                       | 53 |

| $CP_f$                               | Competition pattern built from inducer $f$                           | 53 |

| $f^*$                                | Inducer for the primal competition pattern                           | 54 |

| $\sigma$                             | Current number of locations                                          | 54 |

| ${\cal E}$                           | Available address space at a given iteration                         | 55 |

| i                                    | Index $i$ of some effective address                                  | 55 |

| $\mathcal{E}_i$                      | Set of available addresses induced by index $i \dots index i \dots$  | 55 |

| t                                    | A tag $t$ of some effective address                                  | 55 |

| $\mathcal{E}_{i,t}$                  | Set of addresses induced by index $i$ and tag $t$                    | 55 |

| $\mathcal{E}_i^	au$                  | Address subspace with same index $\boldsymbol{i}$ and different tags | 56 |

| $\mathcal{I}(A_x, sbc, \mathcal{E})$ | Set of candidate indices                                             | 56 |

|                                      |                                                                      |    |

| Metrics                              |                                                                      |    |

| (p, n, s)                            | A verification scenario                                              | 65 |

| T                                    | Collection of tests induced by a verification scenario               | 66 |

| $t_i$                                | Measured runtime for test $T_i$                                      | 66 |

| $\varepsilon$                        | Effectiveness of a verification scenario                             | 66 |

| $\hat{t}$                            | Average test runtime of a verification scenario                      | 66 |

| $EF_G$                               | Verification effort to expose error with generator $G$ .             | 66 |

### **SUMMARY**

| 1 INTRODUCTION                                     |

|----------------------------------------------------|

| 2 RELATED WORK AND PROPOSED GENERATOR              |

| 2.1 POST-SILICON CHECKERS                          |

| 2.2 PRE-SILICON CHECKERS                           |

| 2.3 RANDOM TEST GENERATION                         |

| 2.4 TEST-DIRECTED GENERATION                       |

| 2.5 AN OVERVIEW OF THE PROPOSED GENERATOR          |

| 3 SEQUENCE GENERATION                              |

| 3.1 NOTATION                                       |

| 3.2 KEY IDEAS                                      |

| 3.3 MAIN NOTIONS                                   |

| 3.4 CHAIN CATEGORIES                               |

| 3.5 PROBLEM FORMULATION                            |

| 3.6 AN EXAMPLE                                     |

| 3.7 PSEUDOCODE                                     |

| 4 ADDRESS ASSIGNMENT                               |

| 4.1 KEY IDEAS AND MAIN NOTIONS                     |

| 4.1.1 Selection of a competition pattern           |

| 4.1.2 Enforcement of biasing constraints           |

| 4.2 PROBLEM FORMULATION                            |

| 4.3 SOLVER ALGORITHM                               |

| 5 INSTRUCTION SYNTHESIS                            |

| 5.1 PROBLEM FORMULATION                            |

| 5.2 SOLVER ALGORITHM                               |

| 6 EXPERIMENTAL EVALUATION                          |

| 6.1 EXPERIMENTAL SET UP                            |

| 6.2 METRICS                                        |

| 6.2.1 Error exposure correlation                   |

| 6.2.2 Effectiveness                                |

| <b>6.2.3</b> Verification effort                   |

| 6.3 IMPACT OF THE PROPOSED SEQUENCE GENERATION     |

| 6.3.1 Impact of parameter choice on error exposure |

| 6.3.2 Impact on effectiveness                      |

| 6.3.3 Impact on effort                             |

| 7 CONCLUSIONS AND PERSPECTIVES                     |

| 7.1 CONCLUDING REMARKS                             |

| 7.2 DISCUSSION                                     |

| 7.3 FUTURE WORK                                   | 90  |

|---------------------------------------------------|-----|

| 7.3.1 Conceptual generalizations                  | 90  |

| 7.3.2 Technical extension                         | 91  |

| 7.3.3 Extra experimentation                       | 92  |

| APPENDIX A - Design error characterization        | 97  |

| APPENDIX B - Comparison of the generators in sup- |     |

| plementary scenarios                              | 103 |

| References                                        | 105 |

#### 1 INTRODUCTION

Design verification has been challenged by the growing hardware complexity to support the *coherent* shared-memory abstraction, which is expected to keep its crucial role in Chip Multiprocessing (MARTIN; HILL; SORIN, 2012) even in the scale of hundreds of cores (DEVADAS, 2013), because general-purpose parallel programming requires implicit management of cache coherence. Besides, since memory operations might be allowed to execute out of program order, a *memory model* is provided as part of the programmer's view for reasoning about the ordering of memory operations across the multiple threads of a parallel program. It specifies *consistency* rules defining not only the degree of program order relaxation, but also the extent of store atomicity (ADVE; GHARACHORLOO, 1996). Due to the dominance of synchronized programs, consistency rules end up hidden from the ordinary programmer (HENNESSY; PATTERSON, 2011). Thus, weak memory models allow for higher performance without compromising programability.

As a result from such trends, two main difficulties challenge shared-memory verification: 1) the growing complexity due to cache coherence (the number of reachable states grows exponentially with core up-scaling); 2) the higher complexity due to memory consistency (weaker models lead to larger numbers of allowed behaviors).

Functional processor verification largely relies on random test program generation. For instance, the literature reports verification frameworks that cast test generation into a constraint satisfaction problem (LEWIN et al., 1995; BIN et al., 2002; ADIR; SHUREK, 2002; ADIR et al., 2004; NAVEH et al., 2007). Albeit such frameworks provide general, unified mechanisms to synthesize test programs that exercise the whole system, including the *shared memory subsystem*, they are not designed to exploit non-determinism, which is an important mechanism to expose shared-memory errors (HANGAL et al., 2004; ELVER; NAGARAJAN, 2016).

This explains the existence of verification approaches specifically targeting the shared memory. Formal methods (e.g. (CHATTERJEE; SIVARAJ; GOPALAKRISHNAN, 2002)) rely on model checking to prove coherence and consistency properties, but cannot handle the memory system in full detail. Simulation-based verification relies on the execution of test programs on a design representation of the memory system implementation (SHACHAM et al., 2008; FREITAS; RAMBO; SANTOS, 2013). Hybrid methods (e.g. (ABTS; SCOTT; LILJA, 2003)) combine

formal and simulation-based approaches. The literature reports two complementary simulation-based approaches, as follows.

Protocol-based verification has the advantage of relying on a precise coverage metric. Since the finite state machine (FSM) of each cache controller is known for a given coherence protocol, it is possible to build the product FSM, which specifies all reachable states and transitions. Therefore, it is possible to track which states and transitions were covered by a test suite or to guide test program generation towards higher coverage. On the one hand, it allows a trade-off between coverage and test length by means of adaptive test generation (e.g. (WAGNER; BERTACCO, 2008)). On the other hand, test generation may exploit the decomposition of the state space into simpler structures to make full coverage viable (e.g. (QIN; MISHRA, 2012)). The main disadvantages of protocol-based verification are: it is not directly reusable across derivate designs with distinct protocols and it requires either the validation of the memory system in isolation or the use of an abstraction of the other parts of the full-system functional design (ELVER; NAGARAJAN, 2016).

Memory-model verification has the advantage of checking the expected behavior for the whole shared-memory system (since it captures coherence requirements and consistency rules). Its main disadvantage is the lack of a precise metric for coverage (since the memory model relies on an axiomatic specification of order relations, it cannot directly rely on a native FSM model, as a coherence protocol does). The fact of not being tied to a specific protocol, however, leads to its main advantage: its direct reusability across derivative designs. On the one hand, it allows adaptive test-directed generation by selecting memory operations contributing to increase the non-determinism of a test (e.g. (ELVER; NAGARAJAN, 2016)). On the other hand, it allows the reuse of techniques originally developed for post-silicon checkers (e.g. (HANGAL et al., 2004)), which are based on constrained random test generation.

This dissertation reports new techniques for random test generation that build upon the lessons learned from both approaches — the general verification frameworks based on constraint satisfaction (LEWIN et al., 1995; BIN et al., 2002; ADIR et al., 2004; NAVEH et al., 2007) and the methods specifically targeting memory-model checking (HANGAL et al., 2004; MANOVIT; HANGAL, 2006; SHACHAM et al., 2008; HU et al., 2012), as follows:

- Graph-based random address assignment: From the former, it borrows the notion of address biasing constraints (ADIR et al., 2004), which are important mechanisms to induce interesting behaviors such as cache eviction. The dissertation proposes a new graph-based mechanism to exploit them when specifically targeting memory-model verification.

- Chain-based random sequence generation: From the latter, it preserves the exploitation of non-determinism, because aggressive data races tend to expose multiprocessor bugs faster (MANOVIT; HANGAL, 2006), as has been observed in both industrial (HANGAL et al., 2004) and academic (SHACHAM et al., 2008) environments. Typically, a test program generator offers control parameters such as frequency of instruction types, number of memory operations, and number of shared locations. Besides, a generator generally allows users to specify desirable sequences of memory operations to exercise known corner cases (HANGAL et al., 2004). Instead of simply allowing the ad hoc specification of desirable sequences, the dissertation proposes a novel mechanism that builds upon a formal specification (GHARACHORLOO, 1995) to automatically select the proper sequences (ANDRADE; GRAF; SANTOS, 2016).

Instead of directly solving a unified constraint satisfaction problem for the whole system, we deliberately reduce the scope of verification to the shared-memory subsystem and we decompose it into two main subproblems: constrained random sequence generation and constrained random address assignment. Such decomposition was induced by two properties of canonical dependence chains (GHARACHORLOO, 1995): their ability to rule out orderings not required to preserve the semantics of a memory model and their independence from the actual effective addresses assigned to the memory locations that are shared by the operations of a chain. That decomposition allows the exploitation of significant operation orderings as constraints (so as to avoid the generation of sequences unable to expose errors) and the exploitation of distinct address patterns for a given collection of sequences (so as to allow control on cache eviction as another key mechanism to error exposure). The reduction in scope and the decomposition fostered the design of specific algorithms to solve the subproblems instead of relying on generic solvers.

The remainder of this dissertation is organized as follows. The next chapter summarizes related work and informally presents the decomposition of the target problem by showing an overview of the interacting engines solving distinct subproblems and the generation flow underlying the proposed technique. Chapters 3, 4, and 5 formalize the target subproblems and describe the algorithms solving them. Chapter 6 compares a new generator (built with the proposed techniques) with a typical random generator in terms of their potential to error exposure, their effectiveness in exposing errors, and their impact on verification effort. Chapter 7 draws the main conclusions and discusses current limitations and future work.

A significant part of the text of this dissertation reflects the contents of other documents written in co-authorship: a published paper (ANDRADE; GRAF; SANTOS, 2016) and an article in preparation for submission, which were the result of strongly collaborative research. The author acknowledges the contributions of the co-authors of those documents for the joint research effort and points out his exclusive contributions to that collaborative effort, which are the object of this dissertation: the development of the algorithms solving Problems 1, 2, and 3; their implementation, and their experimental validation and evaluation.

#### 2 RELATED WORK AND PROPOSED GENERATOR.

This chapter briefly reviews related works on checkers and test generators for shared-memory verification so as to propose, in face of them, a new generator.

#### 2.1 POST-SILICON CHECKERS

Memory-model checkers changed the approach to the problem of memory verification in Chip Multiprocessing (CMP) systems. Instead of directly dealing with the implementation, they exploit a pre-existing programmer's view abstraction, the memory model, for reducing the coupling between verification and implementation details. The seminal paper by Hangal, Vahia, and Manovit (HANGAL et al., 2004) inspired many post-silicon checkers (e.g. (MANOVIT; HANGAL, 2006; ROY et al., 2006; CHEN et al., 2009; HU et al., 2012)), which elaborated on their original idea. This allowed for more reusable checkers and extended post-silicon testing (the backbone of processor design validation efforts) beyond race-free self-checking tests and towards more effective pseudorandom tests with intensive data races. Despite suggestions (HANGAL et al., 2004; HU et al., 2012) that post-silicon approaches could be efficiently reused as pre-silicon checkers, they only hold for best effort versions of post-silicon checkers, but not for the complete versions providing verification guarantees for each test (MANOVIT; HANGAL, 2006; HU et al., 2012). In the latter case, post-silicon checkers exhibit poor scalability with the number of cores, which tends to severely limit their use at design time.

Most post-silicon checkers are postmortem engines, i.e. they require all traces to be available before starting their verification. Most of them rely on directed acyclic graphs to model order relations inferred from traces and, consequently, they prove memory incorrectness by counterexample. However, albeit the detection of a cycle is proof of incorrectness, the non-detection of any cycle is not proof of correctness, because some order relation might not have been inferred by the traces.

#### 2.2 PRE-SILICON CHECKERS

A single pre-silicon *postmortem* checker is reported in the literature (RAMBO; HENSCHEL; SANTOS, 2012). To rule out false negatives, it exploits the extra observability of a design representation by oversampling memory events from two sequences per processor so as to infer order relations with extended bipartite graph matching.

Two classes of pre-silicon runtime checkers are reported in the literature. The use of a relaxed scoreboard was proposed for fast runtime checking (SHACHAM et al., 2008). As opposed to a conventional scoreboard, which admits a single event per entry, the relaxed scoreboard keeps multiple expected events per entry when a single memory event cannot be identified. It employs an update rule that stores a new event after each write operation and dynamically removes events that become invalid after each read operation. Since it never reconsiders a previous decision, the technique admittedly may raise false negatives for a given test program. In contrast, a recent work (FREITAS; RAMBO; SANTOS, 2013) proposes the use of multiple verification engines (one per core) and a single global checker to build an axiom-based on-the-fly checker. An error is raised as soon as it is found either by a local engine or by the global checker. The checker offers proven guarantees for a given test program (neither false positives nor false negatives if an error is exposed by the program).

#### 2.3 RANDOM TEST GENERATION

Industrial environments have been relying on random stimuli generators for the functional verification of processors since the mid-1980 (AHARON et al., 1991). In the next decade, IBM developed the first model-based pseudorandom test generator. In the early 2000's, test generators have relied on more powerful engines, which translate the test generation problem into a constraint satisfaction problem and use a solver customized for pseudorandom test generation. Such approaches have the advantage of offering a unified framework for generating stimuli to verify the whole system (processor, memory, and interconnect). The downside of such unifying approach is that it makes it more difficult to exploit non-determinism (which is an important mechanism to expose shared-memory errors). Although a recent paper (ADIR et al., 2014) shows an extension to handle non-determinism within such verification methodology, it admittedly does not address the memory

subsystem (but only the verification of the instruction set support for transactional memory).

On the other hand, it has been observed in both academic and industrial environments that non-determinism is an important key to shared-memory verification: programs with intensive data races expose bugs faster (HANGAL et al., 2004). As opposed to general, unifying verification methodologies, this observation has fostered specific pseudorandom test generation techniques targeting the memory subsystem.

Random tests targeting memory-model checking have been used by post-silicon checkers (HANGAL et al., 2004; ROY et al., 2006; MAN-OVIT; HANGAL, 2006; HU et al., 2012) in industrial environments and by pre-silicon checkers (SHACHAM et al., 2008; FREITAS; RAMBO; SANTOS, 2013) in academic environments. Most works focus on describing the analysis algorithms, albeit a brief description of the generation parameters is sometimes reported (HANGAL et al., 2004) or can be inferred (SHACHAM et al., 2008). Except for two works (RAMBO; HENSCHEL; SANTOS, 2011; ANDRADE; GRAF; SANTOS, 2016), no pseudocode for a typical generator could be found. Common parameters are the frequency of instruction types (HANGAL et al., 2004; MANOVIT; HANGAL, 2006; HU et al., 2012), the number of shared locations (HANGAL et al., 2004; MANOVIT; HANGAL, 2006; SHACHAM et al., 2008), and even desirable sequences to induce known corner cases. Instead of simply allowing the ad hoc specification of desirable sequences, a recent work (AN-DRADE; GRAF; SANTOS, 2016) builds upon a formal specificion (GHAR-ACHORLOO, 1995) to automatically select the proper sequences.

#### 2.4 TEST-DIRECTED GENERATION

Since the hardware's throughput is orders of magnitude higher than a simulator's, pre-silicon verification can neither afford long tests nor large test suites to achieve coverage goals, as opposed to post-silicon testing. That is why test-directed generation has been advocated (WAGNER; BERTACCO, 2008) (QIN; MISHRA, 2012) (ELVER; NAGARAJAN, 2016) to bridge the coverage gap that would be induced by the random generation of shorter tests and smaller test suites when targeting protocol-based and memory model verification.

In face of core up-scaling, one of the keys to scalability is the decomposition of the state space. In MCjammer (WAGNER; BERTACCO, 2008), each core is assigned an agent, which sees the coherence protocol in terms of a dichotomic FSM (comprising only the states of the local

node and the state of the environment). Cooperating agents formulate their coverage goals in terms of the dichotomic FSM, not the product FSM. Another technique (QIN; MISHRA, 2012) decomposes the state space into simpler structures such as hypercubes and cliques, which can be traversed (in an Euler tour) to avoid visiting the same transitions many times. It may allow full coverage with tests 50% shorter than a breadth-first traversal.

To maximize coverage without increasing test length, adaptive test generation is preconized. For instance, based on the coverage goals attained by the tests already generated, a MCjammer's agent makes a probabilistic decision to either pursue its own goal, or to generate a stream of instructions to allow another agent to achieve its goal, or to execute a random stream of memory accesses (WAGNER; BERTACCO, 2008). In McVerSi (ELVER; NAGARAJAN, 2016), a genetic programming approach is used to progressively improve the quality of the test suite. It relies on a crossover function that prioritizes memory operations contributing to non-determinism, thereby increasing the probability of uncovering coherence and consistency errors.

Albeit adaptive test-directed generation may lead to high coverage for both protocol-based and memory model verification, it has to rely on some basic random generation engine to expose new frontiers for improvement. Therefore, random test generation can be exploited as a standalone approach or as part of an adaptive test-directed generation framework.

As shown in an early work (ANDRADE; GRAF; SANTOS, 2016), there is unexploited room for improvement by creating a technique lying in between random and directed test generation. This dissertation generalizes such early work, as shown in the next section.

#### 2.5 AN OVERVIEW OF THE PROPOSED GENERATOR

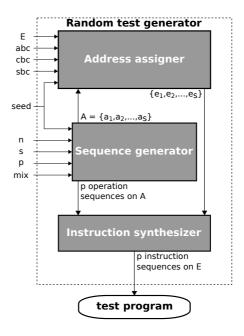

As shown in Figure 1, the proposed generator consists of three interacting engines: a sequence generator, an address assigner, and an instruction synthesizer.

Given the number of processors (p) of the architecture, the target numbers of memory operations (n) and shared locations (s) for the test program, a target mix of canonical dependence chains, and a random seed, the *sequence generator* builds p random sequences containing each n/p operations with references to locations in the set  $A = \{a_1, a_2, \dots, a_8\}$ . To build the sequences, the generator exploits

Figure 1: Structure of the proposed generator

dependence chains so as to increase the probability of error exposure (ANDRADE; GRAF; SANTOS, 2016) by relying on canonical chains that provenly preserve the semantics of the original memory model (GHAR-ACHORLOO, 1995). Given the set of effective addresses (E) defined by the address space of a given architecture, the address assigner maps locations  $a_1, a_2, \dots, a_s$  to effective addresses  $e_1, e_2, \dots, e_s$ . The mapping relies on three types of biasing constraints to enforce desirable properties for the effective addresses to be assigned:

- Alignment biasing constraint (abc): a natural number specifying that the address is aligned to  $2^{abc}$  bytes.

- Sharing biasing constraint (sbc): a Boolean value enforcing true sharing or not.

- Competition biasing constraint (cbc): a pair  $(\kappa, \chi)$ , with  $\kappa, \chi \in \{1, 2, \dots, s\}$ , indicating the number of addresses mapping to distinct cache rows and the maximum degree of competition for a same cache row (as will be explained later).

The instruction synthesizer converts p sequences of memory operations referencing locations into p sequences of memory instructions referencing effective addresses. Besides, it also defines the values to be written by store instructions.

The next three chapters formalize the problems addressed by each engine and propose algorithms to solve them.

## 3 SEQUENCE GENERATION

This chapter describes how canonical dependence chains are exploited when generating sequences of operations. First, it illustrates the key ideas and formalizes the notions required to formulate the target problem. Then it explains how the generator works by means of an example. Finally, it describes the algorithm proposed to solve the constrained random sequence generation problem.

#### 3.1 NOTATION

We rely on the following notation.  $\mathcal{O}$  is the set of memory operations issued by all processors.  $\mathcal{O}^i \subset \mathcal{O}$  denotes the operations induced by the instructions issued by some processor i. We let p denote the total number of processors. Therefore,  $\mathcal{O} = \cup_{i=1}^p \mathcal{O}^i$ . A is the set of all locations referenced by operations in  $\mathcal{O}$ .  $\mathcal{O}_a^i \subset \mathcal{O}^i$  denotes the subset of operations to the same location  $a \in A$ . To specify that an operation  $O_j$  is issued by a processor i and makes a reference to a location  $a \in A$ , we write  $(O_j)_a^i$ . We replace O by L or S to specify that the operation is either a load or a store. In shorthand notation, we may drop one of the subscripts or the superscript when irrelevant. Besides, we let  $Val_a^0$  denote the initial value stored at location a before any processor ever writes to it. Finally, let  $Val[(O_j)_a^i]$  be the value written or returned by some operation issued by processor i.

Given two (load or store) instructions, say  $I_j$  and  $I_m$ , if  $I_j$  precedes  $I_m$  in some thread, their respective memory operations are in program order, written  $O_j \prec_{po} O_m$ . Therefore,  $\prec_{po}$  is a partial order on the set of all memory operations and a total order on the set of operations of a given thread.

A test program may induce many executions with distinct outcomes. An execution induces a memory behavior. Every valid behavior of a memory system must satisfy a partial order  $\leq$  on the set of memory operations.

From the program order  $\prec_{po}$ , a memory model specifies the allowed execution orders by means of a partial order  $\leq$ , which is formally defined by axioms. Examples of such axioms can be found in the literature for distinct models (MANOVIT; HANGAL, 2006) (FREITAS; RAMBO; SANTOS, 2013) (ROY et al., 2006).

For convenience, but without loss of generality, we selected as

target the memory model adopted in the Alpha architecture (GHAR-ACHORLOO, 1995), whose weak enforcement of program order leads to a larger number of valid states as compared to less relaxed models such as the Total Store Ordering model (GHARACHORLOO, 1995) for instance. Besides, the target model closely ressembles the popular Weak Ordering model adopted in ARMv7.

For simplicity, we avoid an axiomatic description of the target memory model, since it is not required for understanding the proposed technique. Essentially, the adopted target model allows loads and stores to different locations to complete out of program order unless there is a memory barrier between them (GHARACHORLOO, 1995). Such an informal description of the memory model is sufficient for the formulation of dependence chains, which are addressed in the next section.

### 3.2 KEY IDEAS

We were aware that Gharachorloo had formalized aggressive specifications that provenly preserve the semantics of memory models (GHARACHORLOO, 1995). His conditions aimed to enable the *design* of an aggressive implementation that provides higher performance than the original model but leads to the same results. We realized that we could exploit those conditions for a different use: the constrained pseudorandom generation of test programs for *verification*.

Our insight was the following. A test program should avoid inducing operation orderings that are unnecessary for maintaining the semantics of the memory model under verification, since it will not expose errors. Therefore, to rule out the generation of ineffective test programs, we should induce only *significant operation orderings*. It turns out that, among the various conditions of an aggressive specification, Gharachorloo specifies the actual significant orderings in the form of uniprocessor and multiprocessor dependence chains.

Instead of randomly selecting instructions as typical generators do, we select instructions according to predefined dependence chains that are provenly significant for keeping memory model semantics. Since the ordering between some of the elements of a chain depends on their execution order, despite using proper verification patterns, the generated test program may not always induce a given chain at runtime. When this happens, some ineffective orderings may remain in the test, as if they were induced by a conventional generator.

## 3.3 MAIN NOTIONS

**Definition 1** Let  $O_j \in \mathcal{O}_a^i$  and  $O_m \in \mathcal{O}_b^i$ . Let MB be a memory barrier, i.e. a mechanism to restore program order between load and store operations whose order is relaxed by the memory model<sup>1</sup>. We say that two operations are in significant program order, written  $O_j \prec_{spo} O_m$ , iff one of the following holds:  $(O_j)_a \prec_{po} (O_m)_{b=a}$  or  $(O_j)_a \prec_{po} MB \prec_{po} (O_m)_{b\neq a}$ .

**Definition 2** We say that two operations are in conflict order, written  $O_j \leq_{co} O_m$ , iff  $(O_j)_a^i \leq (O_m)_a^k$  and at least one of them is a store.

**Definition 3** We say that two operations are in significant conflict order, written  $O_j \leq_{sco} O_m$ , iff  $(L_j)_a^i \leq (S_m)_a^k \vee (S_j)_a^i \leq (L_m)_a^k \vee (S_j)_a^i \leq (S_m)_a^k \vee (L_j)_a^i \leq S_a^x \leq (L_m)_a^k$ .

**Definition 4** A chain is a sequence  $X \prec A \prec \cdots \prec B \prec Y$ , where the endpoints X and Y are memory operations, but  $A, \cdots, B$  may represent either memory operations or memory barriers. The precedence relation  $\prec$  between two successive elements denotes one of the relations  $\prec_{po}$ ,  $\prec_{spo}$ ,  $\leq$ ,  $\leq_{co}$ , or  $\leq_{sco}$ . For convenience, let  $\{A \prec B \prec\}_*$  denote zero or more occurrences of this pattern in the chain. Similarly, let  $\{A \prec B \prec\}_+$  denote one or more occurrences of the pattern.

The above formalized notions allows us to formulate the chains to be used by our generator.

## 3.4 CHAIN CATEGORIES

A dependence chain is one that may induce data dependency through memory, either within the scope of the same thread (uniprocessor chain) or across threads allocated in distinct processors (multiprocessor chain). Gharachorloo (GHARACHORLOO, 1995) has defined a single category of significant uniprocessor dependence chain and three

<sup>&</sup>lt;sup>1</sup>In the Alpha processor, there are two flavors of instructions providing memory barriers: MB (which may intervene between arbitrary memory instructions) and WMB (which may intervene between store instructions). In the latter case, an extra clause would be required in Definition 1:  $(O_j)_a \prec_{po} WMB \prec_{po} (O_m)_{b\neq a}$  and  $O_j$  and  $O_m$  are stores. We prefer to omit such technicality to keep the definition independent from the choice of instruction-set architecture.

categories of multiprocessor dependence chains. Each category of significant chain is defined below. To simplify the notation, the defining patterns use L, S, O to denote types of memory operations (respectively, load, store, any). We implicitly assume that distinct operation instances of each type will be used for actually building the chain.

**Category 0:**  $O_a^i \prec_{po} \{O_a^i \prec_{po} O_a^i \prec_{po}\}_* O_a^i$ , where two successive elements cannot be of load type.

Category 1:  $S_a^i \leq L_a^j \prec_{po} L_a^j$  or  $S_a^i \leq L_a^j \prec_{po} S_a^j$ , where  $i, j \in \{1, \cdots, p\}$  and  $i \neq j$ .

**Category 2:**  $O_a^i \prec_{spo} \{O_b^i \leq_{sco} O_b^j \prec_{spo}\}_+ O_a^j$ , where  $i, j \in \{1, \dots, p\}, i \neq j$  and b is arbitrary.

**Category 3:**  $S_a^i \leq_{sco} L_a^j \prec_{spo} \{O_b^j \leq_{sco} O_b^k \prec_{spo}\}_+ L_a^k$ , where  $i, j, k \in \{1, \dots, p\}, i \neq j, j \neq k$  and b is arbitrary.

## 3.5 PROBLEM FORMULATION

Our generator accepts four main parameters: the total number of memory operations in the test program (n), the total number of processors (p), the number of distinct shared locations (s), and the target mix of patterns (M). The mix specifies the target fraction of chains from each category. Let  $\mathcal{C}_{\kappa}$  denote the set of chains from category  $\kappa$  in a given test program and let  $\mathcal{C} = \bigcup_{\kappa=0}^{3} \mathcal{C}_{\kappa}$  be the set of all chains. Let length(c) be the number of operations in chain c and let length(c) be the amount of them that are issued by processor i. The addressed target problem can be formulated as follows:

**Problem 1** Given n, p, s, M, find a set of chains C subject to the following constraints:

- $\sum_{c \in \mathcal{C}} length(c) = n$ ,

- $\sum_{c \in \mathcal{C}} length^i(c) = n/p \text{ for all } i \in \{1, \dots, p\},$

- $a \in \{a_1, a_2, \dots, a_s\}$  for each memory operation  $O_a$  in C,

- $|\mathcal{C}_{\kappa}|/|\mathcal{C}| = M[\kappa]$  for each  $\kappa = 0, 1, 2, 3$ .

The first constraint specifies that all memory operations are part of a chain; the second, that all threads have the same number of memory operations; the third, that all operations must use one of the shared locations; the forth, that the obtained proportions should reach the target mix.

### 3.6 AN EXAMPLE

The proposed generator assumes that a single thread is assigned to each processor and all threads have the same number of slots for memory operations. For simplicity, the same latency is assumed for all memory operations. Therefore, successive slots from distinct processors are likely to reflect execution order as far as that hypothesis holds (this simplifies the generation process, but it does not preclude further elaborations from enforcing the execution order of operations belonging to distinct threads).

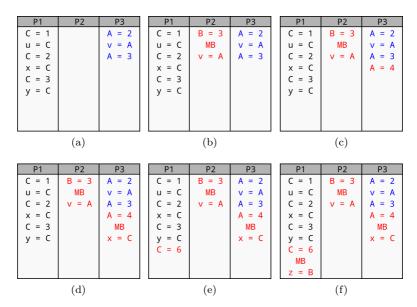

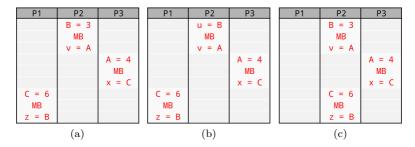

The example in Figure 2 shows how the proposed generator inserts a chain from category 2 in a test program under construction. Uppercase identifiers denote variables in memory; lowercase identifiers, variables in registers. Memory barriers are labeled as MB. Suppose that two chains from category 0 (uniprocessor dependence chain) were previously created (Figure 2a), one in processor P1 (black), another in processor P3 (blue).

Figure 2: An example of how to enforce a significant ordering

Suppose that category 2 was randomly selected as a chain target. The generator first tries to build a minimal chain from the selected category, but might randomly decide to extend it as far as it does not violate any constraints. To build the minimal chain, the generator randomly selects a processor (say P2) and adds two memory operations with an intervening memory barrier to the first free slots of the respective thread (Figure 2b). The memory operation types are randomly selected (in Figure 2b, the first one turned out to be a store; the second, a load). Then a new processor is randomly selected (say P3) for the next operations of that chain. To comply with category 2 specifications, the first of them must conflict with the previous operation already in the chain and, thus, neither its type nor its location can be randomly selected (in Figure 2c, it must be a store to location A).

At this stage, the generator randomly decides whether the chain will be kept minimal or be extended (in the former case, the next memory operation becomes an endpoint and must conflict with the chain's starting point). Assume that the generator decided for extension. In this case, the location of the next operation is randomly selected (say C), because that operation is not intended anymore as an endpoint (Figure 2d).

To accomplish the extension, a processor is randomly selected (say P1) and an operation conflicting with the previous one in the chain is inserted (Figure 2e). Again, the generator must decide whether the chain should be further extended or not. Suppose that, this time, the random decision is for no further extension. As a result, the last operation, being an endpoint, cannot be randomly selected, since it must conflict with the chain's starting point (in Figure 2f, that endpoint must be a load from location B).

The memory operations in red represent the resulting chain. The significant conflict ordered required for actually forming that chain in runtime will only take place if the order implied by the slots turns out to be the actual execution order. In spite of that, the example shows that, instead of allowing fully random generation of operation sequences, the proposed technique constrains the sequences to comply, as much as possible, with significant orderings.

#### 3.7 PSEUDOCODE

Let us formalize a few notions on which our algorithms rely. Let  $T^i$  denote the thread assigned to processor i. Each thread consists of

n/p slots. We write  $T^i[x]$  to denote the content of the x-th slot of a thread. All slots are empty before generation is launched. During generation, operations are assigned to empty slots in each thread. Our algorithms track the *number of available slots* in thread  $T^i$ , which is denoted as  $av^i$ . Operations can be selected from three different types: load (L), store (S) or memory barrier (MB). To cope with the target proportion of chains specified for some category  $\kappa$ , i.e.  $M[\kappa]$ , our algorithm tracks the fraction of all slots available for that category, which is denoted as  $C[\kappa]$ . Finally, our algorithm tracks the last value written by a store to a given location a, which is denoted as Val[a].

**Definition 5** The length of a minimal chain from category  $\kappa$  is feasible, written  $\lambda_{min}(\kappa)$ , iff one of the following holds:

- $\kappa = 0 \wedge C[\kappa] \ge 1$

- $\kappa = 1 \wedge C[\kappa] \geq 3$

- $\kappa = 2 \wedge C[\kappa] \ge 4$

- $\bullet \ \kappa = 3 \wedge C[\kappa] \geq 5$

**Definition 6** Let  $i, j, k \in \{1, 2, \dots, p\}$  with  $i \neq j, j \neq k, i \neq k$ . Given a category  $\kappa$ , the breadth required for a minimal chain is feasible, written  $\beta_{min}(\kappa)$ , iff one of the following holds:

- $\kappa = 0 \wedge av^i \geq 1$  for some i

- $\kappa = 1 \wedge av^i \geq 1 \wedge av^j \geq 2$  for some i, j

- $\kappa = 2 \wedge av^i \geq 3 \wedge av^j \geq 3$  for some i, j

- $\kappa = 3 \wedge av^i \ge 1 \wedge av^j \ge 3 \wedge av^k \ge 3$  for some i, j, k

**Definition 7** We say that a minimal chain from category  $\kappa$  is feasible, written  $\phi_{min}(\kappa)$ , iff  $\lambda_{min}(\kappa) \wedge \beta_{min}(\kappa)$ , i.e. when both its length and breadth are feasible.

**Definition 8** Let  $X = \{x \in \mathcal{Z}_+ \mid n/p - av^i\}$  be the set of slots from thread  $T^i$  which are filled with operations and let  $X_{x>m} = \{x \in X \mid x > m\}$ . The last slot of a thread  $T^i$  containing a reference to location a is:

$$max_a^i = \begin{cases} 0 & \text{if } X = \emptyset \lor \forall x \in X \ (T^i[x] = O_{b \neq a}) \\ m & \text{if } T^i[m] = O_a \land \forall x \in X_{x > m} \ (T^i[x] = O_{b \neq a}) \end{cases}$$

Figure 3 describes the top-level routine of the proposed generator. That routine reserves n/p slots for the operations in each thread (line 4) and evaluates the overall number of slots available for operations belonging to chains of each category (line 6). Then the routine performs chain generation (lines 7-14). Chain generation builds as many chains as feasible by ramdomly selecting a category and a location for the conflicting endpoints of each chain. The building of a chain starts only if a minimal chain from the selected category is feasible (line 9), otherwise that category is excluded from the set of available ones (line 13).

```

1: \mathcal{A} \leftarrow \{a_1, a_2, \cdots, a_s\}

2: \mathcal{K} \leftarrow \{0, 1, 2, 3\}

3: for i \leftarrow 1, 2, \cdots, p do

av^i \leftarrow n/p

4:

5: for \kappa \leftarrow 0, 1, 2, 3 do

C[\kappa] \leftarrow n \times M[\kappa]

7: repeat

\kappa \leftarrow \text{random } \mathcal{K}

8:

9:

if \phi_{min}(\kappa) then

a \leftarrow \text{random } \mathcal{A}

10:

11:

chain (\kappa, a)

12:

else

13:

\mathcal{K} \leftarrow \mathcal{K} - \{\kappa\}

14: until \mathcal{K} = \emptyset

```

Figure 3: Algorithm Sequence-Generator (p, n, s, M)

Figures 4 and 5 describe the routines employed by the proposed generator. The pseudocode assumes that K, A, C,  $T^i$  and  $av^i$  all have global scope for those routines.

Figure 4 describes the routine that builds a chain from category  $\kappa$  whose endpoints are conflicting operations at location a. Essentially, the routine randomly selects locations, operations, processors, and lengths, unless otherwise constrained by the rules of formation of a given category. For categories 2 and 3, the routine starts building a minimal chain from the target category (lines 19-28 and 36-46), but before closing its construction, it decides whether a longer chain (from the same category) should be derived or not from the chain under construction (lines 29 and 47). If so, the chain is extended (lines 31 and 49); otherwise, the minimal chain is concluded (lines 32-34 and 50-51). Note that the precondition  $\phi_{min}(\kappa)$  ensures that the sets in lines 2, 12, 13, 19, 20, 36, 37, and 38 are all non-empty. Three auxiliary routines are invoked: insert (for adding an operation to a chain), extend (for extending a minimal chain from categories 2 and 3), and sco (for imple-

```

1: if \kappa = 0 then

i \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \geq 1\}

\lambda \leftarrow \text{random } \{1, 2, \cdots, av^i\}

3:

4:

while \lambda \geq 1 \wedge av \geq 1 \wedge C[\kappa] \geq 1 do

if max_a^i \neq 0 and T[max_a^i] is L then

5:

6:

7:

else

8:

op \leftarrow \text{random } \{L, S\}

9:

\operatorname{insert}(\kappa, op_a^i)

10:

\lambda \leftarrow \lambda - 1

11: if \kappa = 1 then

12:

j \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \ge 2\}

13:

i \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \ge 1 \land x \ne j\}

14:

\operatorname{insert}(\kappa, S_a^i)

\operatorname{insert}(\kappa, L_a^{\jmath})

15:

16:

op \leftarrow \text{random } \{L, S\}

17:

\operatorname{insert}(\kappa, op_a^j)

18: if \kappa = 2 then

i \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \geq 3\}

19:

j \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \ge 3 \land x \ne i\}

20:

21:

op \leftarrow \text{random } \{L, S\}

22:

\operatorname{insert}(\kappa, op_a^i)

23:

\operatorname{insert}(\kappa, MB^i)

b \leftarrow \text{random } \mathcal{A} - \{a\}

24:

25:

op \leftarrow \text{random } \{L, S\}

26:

\operatorname{insert}(\kappa, op_h^i)

27:

op \leftarrow sco(\kappa, op, b, i)

28:

\operatorname{insert}(\kappa, op_h^{\jmath})

29:

\lambda \leftarrow \text{random } \{0, 3, 6, \cdots, C[\kappa]\}

30:

if \lambda \neq 0 then

31:

j \leftarrow \operatorname{extend}(\kappa, a, j, \lambda)

32:

\operatorname{insert}(\kappa, MB^j)

33:

op \leftarrow \text{random } \{L, S\}

34:

\operatorname{insert}(\kappa, op_a^j)

35: if \kappa = 3 then

36:

j \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \geq 3\}

37:

i \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \ge 3 \land x \ne j\}

38:

h \leftarrow \text{random } \{x \in \{1, 2, \cdots, p\} \mid av^x \ge 1 \land x \ne j \land x \ne i\}

39:

\operatorname{insert}(\kappa, S_a^h)

40:

\operatorname{insert}(\kappa, L_a^i)

41:

\operatorname{insert}(\kappa, MB^i)

42:

b \leftarrow \text{random } \mathcal{A} - \{a\}

43:

op \leftarrow \text{random } \{L, S\}

44:

\operatorname{insert}(\kappa, op_h^i)

45:

op \leftarrow sco(\kappa, op, b, i)

46:

\operatorname{insert}(\kappa, op_h^{\jmath})

47:

\lambda \leftarrow \text{random } \{0, 3, 6, \cdots, C[\kappa]\}

48:

if \lambda \neq 0 then

49:

j \leftarrow \operatorname{extend}(\kappa, a, j, \lambda)

50:

\operatorname{insert}(\kappa, MB^j)

\operatorname{insert}(\kappa, L_a^j)

51:

```

Figure 4: Routine chain  $(\kappa, a)$

menting the fourth clause of Definition 3). Those routines are described in Figures 5a, 5b, and 5c, respectively.

```

1: T^i[n/p - av^i + 1] \leftarrow op

2: av^i \leftarrow av^i - 1

3: C[\kappa] \leftarrow C[\kappa] - 1

(a) insert(\kappa, op^i)

1: while \lambda \geq 3 \wedge av^j \geq 2 \wedge c[\kappa] \geq 3 do

P \leftarrow \{x \in \{1, 2, \cdots, p\} \mid av^x \ge 3 \land x \ne j\}

if P \neq \emptyset then

3:

4:

return j

5:

else

6:

\operatorname{insert}(\kappa, MB^{j})

7:

c \leftarrow \text{random } \mathcal{A} - \{a\}

op \leftarrow \text{random } \{L, S\}

8:

\operatorname{insert}(\kappa, op_c^j)

9:

m \leftarrow \text{random } P

10:

op \leftarrow sco(\kappa, op, c, j)

11:

12:

\operatorname{insert}(\kappa, op_c^m)

13:

i \leftarrow m

\lambda \leftarrow \lambda - 3

14:

15: return j

(b) extend(\kappa, a, j, \lambda)

1: if op = L \wedge av^i < 1 then

O \leftarrow S

3: else

O \leftarrow \text{random } \{L, S\}

5: if op = O = L then

\operatorname{insert}(\kappa, S_{k}^{i})

7: return O

(c) sco(\kappa, op, b, i)

```

Figure 5: Auxiliary routines of the generator

The asymptotic time complexity of the sequence generation algorithm depends on how the computations required by Definitions 7 and 8 are implemented. Note that their propositions must be updated each time an operation is inserted in some slot. We assume an optimal implementation for those computations: they can be initialized, updated, and evaluated in times O(p), O(1), and O(1), respectively. Let us first analyze the complexity of the algorithms in Figures 4 and 5. Since any random selection takes O(1) and the routine insert (Figure 5a) also takes O(1), the routine sco (Figure 5c) takes O(1). The complexities of the routines extend (Figure 5b) and chain (Figure 4) are

dominated by the computation of the subset of processors required to accommodate a given chain category (line 2 in routine extend; lines 2, 12, 13, 19, 20, 36, 37, and 38 in routine *chain*). Such computation takes O(p). Therefore, the computation performed by the loops in the routines extend and chain take, respectively,  $O(p) \times O(n_i) = O(p n_i)$ and  $O(p n_i) + O(p) = O(p n_i)$ , where  $n_i$  denotes the number of operations generated by the *i*-th invocation of routine *chain*. Now, let us analyze the complexity of the top-level routine (Figure 3). Initialization (lines 1-6) takes O(s+p). To analyze the main loop (lines 7-14), note that the random selection (line 8), the evaluation of the proposition (line 9), and the removal of a category (line 13) all take O(1). Therefore, the loop computation is dominated by the routine *chain*, which is  $O(p n_i)$ . Let I be the number of iterations of that loop. The computation of the loop takes  $\sum_{i=1}^{I} O(p \ n_i)$ . Since in the end of the loop, the number of operations is bounded (at most n), the loop takes O(p n). Thus, the overall worst-case running time complexity of the sequence generation algorithm is O(s+p) + O(p n), i.e. O(p n + s).

It should be noted that the worst-case complexity of a conventional sequence generator is O(p+n).

## 4 ADDRESS ASSIGNMENT

This chapter describes how biasing constraints are exploited when converting locations into effective addresses. First, it illustrates the key ideas and formalizes the notions required to formulate the target problem. Finally, it describes the algorithm proposed to solve the constrained random address assignment problem.

## 4.1 KEY IDEAS AND MAIN NOTIONS

## 4.1.1 Selection of a competition pattern

Let a cache row means either a cache block in a directed-mapped cache or a set in a set-associative cache. The main idea behind address assignment is the competition biasing constraint (cbc). For a given cbc, there are different ways in which addresses compete for the same cache row and they can be seen as patterns which can be cast into a graph representation, as follows:

**Definition 9** A competition pattern is an undirected graph CP = (A, C) where each vertex  $a_i \in A$  represents a location and each edge  $(a_i, a_j) \in C$  represents the fact that  $a_i$  and  $a_j$  compete with each other for the same cache row.

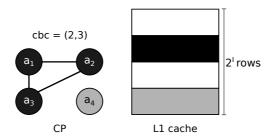

Figure 6 illustrates that notion for a verification scenario with four locations and a cache with  $2^{I}$  rows.

Figure 6: The interpretation of a competition pattern

For the sake of address assignment, a pattern should be randomly selected from a uniform distribution over all competition patterns in-

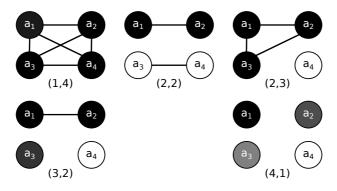

duced by a given cbc. Figure 7 enumerates all competition patterns induced for s=4. Since relation C ("compete for a cache row") is reflexive, symmetric, and transitive, C is an equivalent relation and, therefore, it induces a partition  $\{A_x\}$  of the set A such that each equivalent class  $A_x$  is represented by a strongly connected component. Besides, C is such that every strongly connected component turns out to be a clique. As a result, CP is a trivial form of a perfect graph and can, therefore, be characterized by two numbers: its clique cover number  $\kappa$  and its chromatic number  $\chi$ . Therefore, we can define a cbc as a pair  $(\kappa, \chi)$  with  $\kappa, \chi \in \{1, 2, \dots, s\}$ .

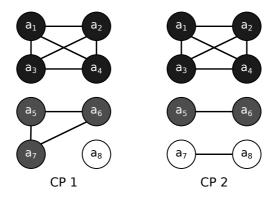

Figure 7: Enumeration of all CPs for s = 4

It should be noted that, for the cbcs (2, 2), (2, 3), and (3, 2), there are isomorphic graphs which represent the same pattern. Such graphs correspond to distinct labelings of the vertices and are not shown in Figure 7. The adoption of a single pattern to represent all isomorphic graphs does not limit the verification space because a labeling is the result of a late phase of address assignment: the constrained random choice of effective addresses. (We show a preview of the actual labeling here for illustrative convenience only). However, a same cbc may induce a collection of non-isomorphic competition patterns. For instance, Figure 8 shows that, for s = 8, there are exactly two CPs induced by cbc = (3,4). Thus, to avoid limiting the verification space, the address assigner must be able to randomly select among them with probability 1/2. Finally, notice that not all pairs of  $(\kappa, \chi)$  represent feasible constraints. Fortunately, due to the simple topology, the collection of all feasible pairs for a given s can be easily precomputed with grounds on graph theory.

Figure 8: CPs induced by cbc = (3, 4) for s = 8

Note that cbc constraints can be exploited for inducing cache evictions. Given an n-way cache, a block is evicted iff n+1 successive addresses compete for the same row; therefore,  $\chi \geq n+1$  is a necessary condition for cache eviction. Besides,  $\kappa$  defines the number of distinct cache rows to be accessed by the test program.

For simplicity, when we refer to a *component* from now on, we mean a strongly connected component of a competition pattern.

# 4.1.2 Enforcement of biasing constraints

Given an abc, an sbc, and a competition pattern randomly selected from a cbc, they are enforced when assigning binary patterns to distinct address fields. Assume that an N-bit effective address consists of three fields: a block *offset* field with O bits (meaning that  $2^O$  is the number of bytes in a cache block), an index field with I bits (meaning that the cache has  $2^I$  rows), and a tag field with T = N - O - I bits.

Figure 9 shows an example of how the effective addresses are enforced to comply with biasing constraints. The example corresponds to abc = 2 (word alignment), sbc = true (true sharing), and assumes the pattern illustrated in Figure 6, which was induced by cbc = (2,3). To enforce such competition pattern, the same binary pattern must be assigned to the index field for vertices from the same clique (as indicated in black) and distinct binary patterns must be assigned to that field for vertices from different cliques (as indicated in gray). To enforce true sharing, distinct binary patterns must be assigned to the

tag field for vertices from the same clique (as depicted in blue, red, and yellow), because this ensures that they will not lie in the same block (since their memory block addresses are different). Finally, to enforce word alignment, the two least significant bits from the offset field are set to zero. (Note that fields in white remain unconstrained).

|                | T bits   | l bits | O bits |

|----------------|----------|--------|--------|

| $e_1$          |          |        | /0,0/  |

| $e_2$          |          |        | /0,0   |

| e <sub>3</sub> |          |        | /0,0/  |

| $e_4$          |          |        | /0,0)  |

| ļ              | <u> </u> | N bits |        |

Figure 9: Relation between address fields and biasing constraints

### 4.2 PROBLEM FORMULATION

The general address assignment problem can be formulated as follows. Let E be the effective address space. Given an abc, an sbc, a feasible cbc, and a set of locations  $A = \{a_1, a_2, \cdots, a_s\}$ , find a mapping  $\alpha : A \mapsto E$  such that all biasing constraints are satisfied.

This dissertation targets an instance of that problem, where competition patterns and binary patterns are randomly selected under uniform distributions. To formulate the target instance, we rely on the notions defined in the previous section, which can be encapsulated with the following notation.

Let  $\mathcal{CP}_{\kappa,\chi,s}$  denote the collection of competition patterns induced by a given  $cbc = (\kappa,\chi)$  and by a given number of shared addresses s. Let random  $\mathcal{CP}_{\kappa,\chi,s}$  denote the random selection of a pattern from that collection.

Given a pre-selected pattern CP = (A, C), let the collection  $\{A_x\}$  denote the partition of the set A induced by its (strongly connected) components. Given an N-bit effective address, say e, let  $e.\mathcal{O}$ ,  $e.\mathcal{I}$ , and  $e.\mathcal{T}$  denote, respectively, its offset, index, and tag fields with O, I, and T = N - O - I bits. Finally, let random  $[0, 2^F - 1]$  denote the random selection of a binary pattern representing a number in the range  $[0, 2^F - 1]$  for an address field with F bits.

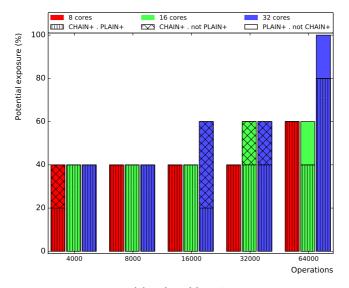

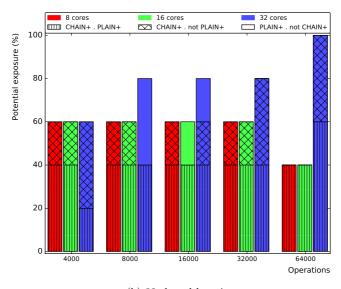

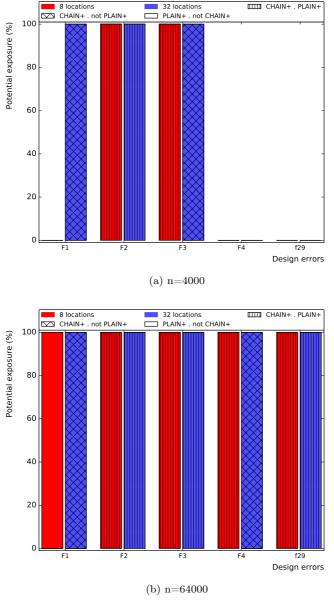

The proposed technique solves the following random address assignment problem instance: