## UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA DE AUTOMAÇÃO E SISTEMAS

Vinícius dos Santos Livramento

## TIMING OPTIMIZATION DURING THE PHYSICAL SYNTHESIS OF CELL-BASED VLSI CIRCUITS

Florianópolis

2016

#### Vinícius dos Santos Livramento

## TIMING OPTIMIZATION DURING THE PHYSICAL SYNTHESIS OF CELL-BASED VLSI CIRCUITS

Tese de doutorado submetida ao Programa de Pós-Graduação em Engenharia de Automação e Sistemas para obtenção do Grau de Doutor em Engenharia de Automação e Sistemas. Orientador: Prof. Luiz Cláudio Villar dos Santos, Dr. – INE/UFSC Coorientador: Prof. José Luís Almada

Güntzel, Dr. – INE/UFSC

Florianópolis

### Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Livramento, Vinícius

Timing Optimization During the Physical Synthesis of Cell-Based VLSI Circuits / Vinícius Livramento; orientador, Luiz Cláudio Villar dos Santos; coorientador, José Luís Almada Güntzel. - Florianópolis, SC, 2016. 192 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia de Automação e Sistemas.

Inclui referências

1. Engenharia de Automação e Sistemas. 2. Automação de Projeto Eletrônico. 3. Síntese Física. 4. Minimização de violações de timing. 5. Relaxação Lagrangeana. I. Villar dos Santos, Luiz Cláudio. II. Almada Güntzel, José Luís. III. Universidade Federal de Santa Catarina. Programa de Pôs Graduação em Engenharia de Automação e Sistemas. IV. Título.

#### Vinícius dos Santos Livramento

## TIMING OPTIMIZATION DURING THE PHYSICAL SYNTHESIS OF CELL-BASED VLSI CIRCUITS

Esta Tese foi julgada aprovada para a obtenção do Título de Doutor em Engenharia de automação e Sistemas, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia de Automação e Sistemas.

| Florianópolis, 02 de Dezembro 2016.                                                  |

|--------------------------------------------------------------------------------------|

| Prof. Daniel Ferreira Coutinho, Dr. – DAS/UFSC Coordenador                           |

| Prof. Luiz Cláudio Villar dos Santos, Dr. – INE/UFSC Orientador                      |

| Prof. José Luís Almada Güntzel, Dr. – INE/UFSC<br>Coorientador<br>Banca Examinadora: |

| Prof. Luiz Cláudio Villar dos Santos, Dr. – INE/UFSC Presidente                      |

| Prof. Fernando Gehm Moraes, Dr. – PUC/RS                                             |

| Prof. Sérgio Bampi, Dr. – Instituto de Informática/UFRGS                             |

| Prof. Eduardo Camponogara, Dr. – DAS/UFSC                                            |

| Gustavo Reis Wilke, Dr. – Synopsys, Inc.                                             |

| Prof. Márcio Bastos Castro, Dr. – INE/UFSC                                           |

#### **AGRADECIMENTOS**

Aos meus pais, Mário e Cristina, pelo amor, carinho e dedicação que nunca faltaram. Também aos meus irmãos, Natália e Vitor, pelo apoio e compreensão. Ao meu orientador, Luiz Cláudio Villar dos Santos, pela excelente orientação e rigor exigido, os quais foram fundamentais para o sucesso desta tese de doutorado. Ao meu coorientador, José Luís Almada Güntzel, que me acompanha desde o período do mestrado, sempre com muita dedicação e confiança. Aos membros da banca, pelo tempo dedicado para uma revisão rigorosa e pelas sugestões que contribuiram com esta tese. Aos colegas do ECL que de alguma forma participaram deste trabalho. Em particular, aos colegas Chrystian Guth e Renan Netto por todo suporte técnico prestado, essencial para o sucesso deste trabalho. À Capes, pelo custeio parcial da execução deste trabalho e pelo custeio do doutorado sanduíche na cidade de Austin, EUA (Processo número: 99999.0062302015-06).

#### RESUMO

A evolução da tecnologia CMOS viabilizou a fabricação de circuitos integrados contendo bilhões de transistores em uma única pastilha de silício, dando origem ao jargão Very-Large-Scale Integration (VLSI). A frequência-alvo de operação de um circuito VLSI afeta o seu desempenho e induz restrições de timing que devem ser manipuladas pelas ferramentas de síntese. Durante a síntese física de circuitos VLSI, diversas técnicas de otimização são usadas para iterativamente reduzir o número de violações de timing até que a frequência-alvo de operação seja atingida. O aumento dramático do atraso das interconexões devido à evolução tecnológica representa um dos maiores desafios para o fluxo de timina closure de circuitos VLSI contemporâneos. Nesse cenário, técnicas de síntese de interconexão eficientes têm um papel fundamental. Por este motivo, esta tese aborda dois problemas de otimização de timing para uma síntese eficiente das interconexões de um circuito VLSI: Incremental Timing-Driven Placement (ITDP) e Incremental Timing-Driven Layer Assignment (ITLA). Para resolver o problema de ITDP, esta tese propõe uma nova formulação utilizando Relaxação Lagrangeana que tem por objetivo a minimização simultânea das violações de timing para restrições do tipo setup e hold. Este trabalho também propõe uma técnica que utiliza multiplicadores de Lagrange como pesos para as interconexões, os quais são atualizados dinamicamente através dos resultados de uma ferramenta de análise de timing. Tal técnica realoca as células do circuito por meio de uma nova busca discreta que adota a distância Euclidiana como vizinhanca. Para resolver o **problema de ITLA**, esta tese propõe uma abordagem em fluxo em redes que otimiza simultaneamente segmentos críticos e não-críticos, e explora algumas condições de fluxo para extrair as informações de timing para cada segmento individualmente, permitindo assim o uso de uma ferramenta de timing externa. A validação experimental, utilizando benchmarks derivados de circuitos industriais, demonstra a eficiência das técnicas propostas quando comparadas com trabalhos estado da arte.

**Palavras-chave:** Síntese Física, Timing Closure, Incremental Timing-Driven Placement, Incremental Timing-Driven Layer Assignment, Relaxação Lagrangeana, Fluxo em Redes.

#### ABSTRACT

The evolution of CMOS technology made possible integrated circuits with billions of transistors assembled into a single silicon chip, giving rise to the jargon Very-Large-Scale Integration (VLSI). The required clock frequency affects the performance of a VLSI circuit and induces timing constraints that must be properly handled by synthesis tools. During the physical synthesis of VLSI circuits, several optimization techniques are used to iteratively reduce the number of timing violations until the target clock frequency is met. The dramatic increase of interconnect delay under technology scaling represents one of the major challenges for the timing closure of modern VLSI circuits. In this scenario, effective interconnect synthesis techniques play a major role. That is why this thesis targets two timing optimization problems for effective interconnect synthesis: Incremental Timing-Driven Placement (ITDP) and Incremental Timing-Driven Layer Assignment (ITLA). For solving the **ITDP problem**, this thesis proposes a new Lagrangian Relaxation formulation that minimizes timing violations for both setup and hold timing constraints. This work also proposes a netbased technique that uses Lagrange multipliers as net-weights, which are dynamically updated using an accurate timing analyzer. The netbased technique makes use of a novel discrete search to relocate cells by employing the Euclidean distance to define a proper neighborhood. For solving the ITLA problem, this thesis proposes a network flow approach that handles simultaneously critical and non-critical segments, and exploits a few flow conservation conditions to extract timing information for each net segment individually, thereby enabling the use of an external timing engine. The experimental validation using benchmark suites derived from industrial circuits demonstrates the effectiveness of the proposed techniques when compared with state-of-the-art works. **Keywords:** Physical Synthesis, Timing Closure, Incremental Timing-Driven Placement, Incremental Timing-Driven Layer Assignment, Lagrangian Relaxation, Network Flow.

#### LIST OF FIGURES

| Figure 1  | Example of an SoC: Samsung Exynos 5 Dual                        | 30  |

|-----------|-----------------------------------------------------------------|-----|

| Figure 2  | Market share and projected growth in IC sales. $\ldots \ldots$  | 31  |

| Figure 3  | Major steps of hardware design flow                             | 33  |

| Figure 4  | Gate and interconnect delay versus technology scaling.          | 34  |

| Figure 5  | Impact of placement                                             | 37  |

| Figure 6  | Impact of routing                                               | 38  |

| Figure 7  | Timing closure during physical synthesis                        | 39  |

| Figure 8  | Basic idea of incremental timing-driven placement               | 43  |

| Figure 9  | Basic idea of incremental timing-driven layer assignment.       | 44  |

| Figure 10 | Layout examples with different electrical characteristics. $$   | 48  |

| Figure 11 | Circuit boundaries and grids                                    | 49  |

| Figure 12 | Examples of standard cell alignment and legalization            | 49  |

| Figure 13 | Different net models that can be used during placement.         | 51  |

| Figure 14 | Example of how to compute circuit cell density. $\ldots \ldots$ | 52  |

| Figure 15 | Review of setup timing constraint (late scenario)               | 54  |

| Figure 16 | Review of hold timing constraint (early scenario)               | 54  |

| Figure 17 | Circuit example with timing analysis notation                   | 56  |

| Figure 18 | Small example of static timing analysis                         | 58  |

| Figure 19 | Electrical characterization of a cell                           | 59  |

| Figure 20 | Electrical characterization of an interconnection               | 62  |

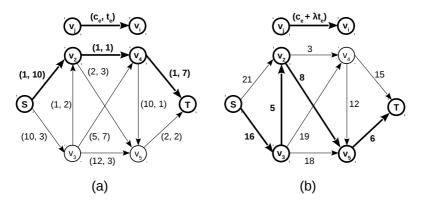

| Figure 21 | Example of application of Lagrangian Relaxation                 | 66  |

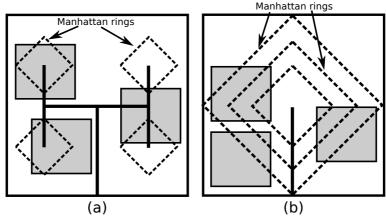

| Figure 22 | Manhattan rings overlapping with macro blocks                   | 73  |

| Figure 23 | Examples of bounding boxes to guide register placement. $$      | 75  |

| Figure 24 | Overview of Lagrangian Relaxation                               | 81  |

| Figure 25 | Flow conservation conditions for net-weights                    | 83  |

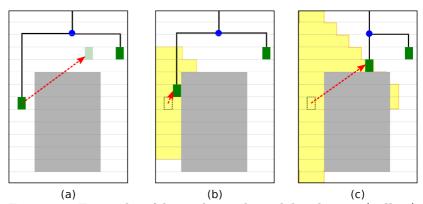

| Figure 26 | Example of how the reshaped legal area works                    | 85  |

| Figure 27 | Example of how the incremental legalization works               | 86  |

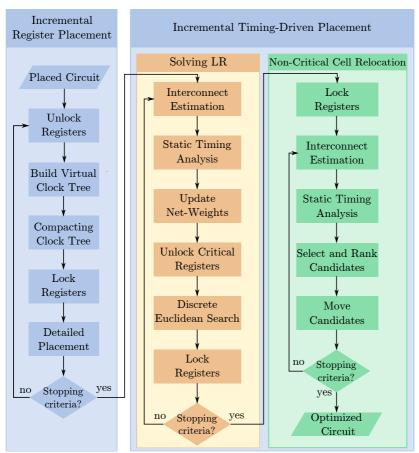

| Figure 28 | Overview of the proposed approach                               | 88  |

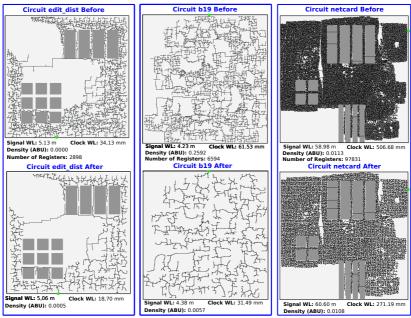

| Figure 29 | Comparison between different contraction forces                 | 90  |

| Figure 30 | How the Discrete Euclidean Search works                         | 95  |

| Figure 31 | Limitation of the Discrete Euclidean Search                     | 100 |

| Figure 32 | How the Non-Critical Cell Relocation works                      | 102 |

| Figure 33         | ICCAD 2015 ITDP Contest's clock distribution 105                  |

|-------------------|-------------------------------------------------------------------|

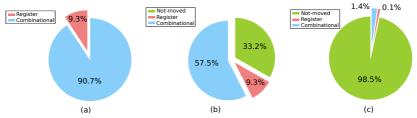

| 0                 | Statistics on all ICCAD 2015 ITDP Contest's Circuits 110          |

| Figure 35         | Snapshots of the clock routing for ICCAD 2015 circuits.112        |

| Figure 36         | 3D global routing grid example                                    |

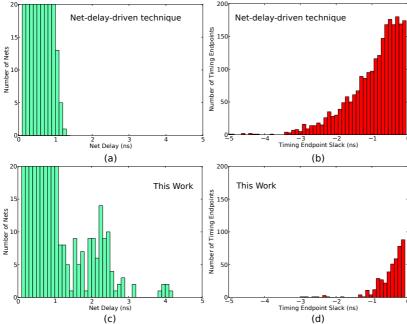

| Figure 37         | Impact of net delay on timing violations119                       |

| $Figure\ 38$      | Net delay and slack histograms                                    |

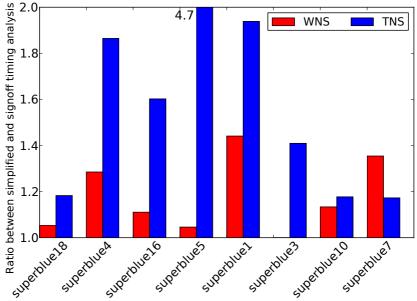

| ${\bf Figure}~39$ | Mismatch between simplified and signoff timing engine. $121$      |

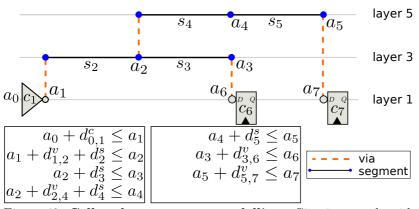

| Figure $40$       | Cell and net segment modelling126                                 |

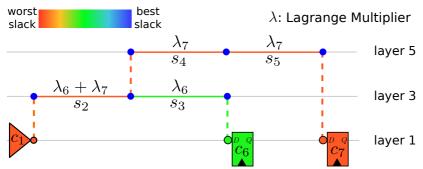

| $Figure\ 41$      | Obtaining net segment LMs from sink pin LMs 130                   |

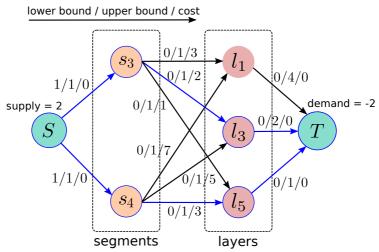

| Figure $42$       | A min-cost network flow example for layer assignment. $\! . 131$  |

| Figure $43$       | Overview of the proposed layer assignment framework $134$         |

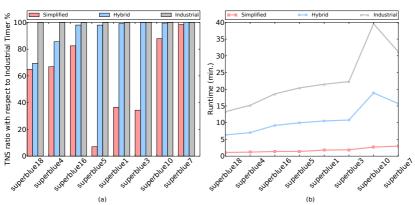

| $Figure\ 44$      | Impact of the timing engine accuracy                              |

| Figure $45$       | Impact of a hybrid timer                                          |

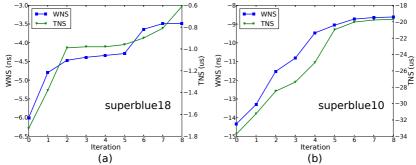

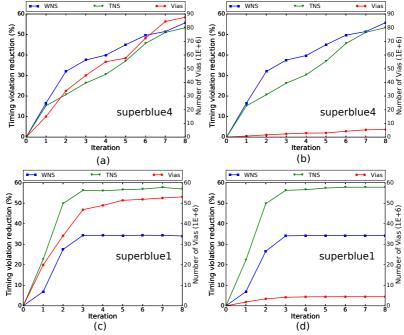

| $Figure\ 46$      | Algorithm convergence                                             |

| $Figure\ 47$      | Impact of the pruning strategy147                                 |

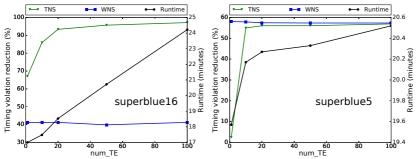

| Figure 48         | Algorithm tradeoff between number of TEs and runtime. $148$       |

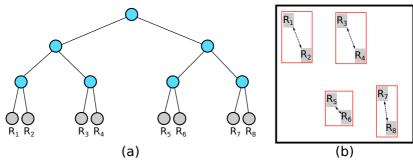

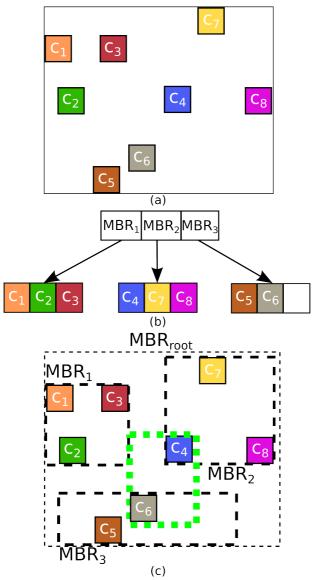

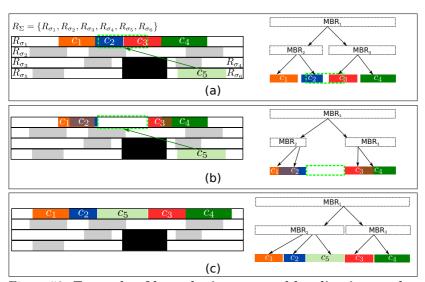

| $Figure\ 49$      | Example of how an R-tree works170                                 |

| Figure $50$       | Example of how the incremental legalization works $172$           |

| $Figure\ 51$      | Statistics on all ICCAD 2014 ITDP Contest's Circuits. $.182$      |

| $Figure\ 52$      | Snapshots of the clock routing for ICCAD 2014 circuits.<br>185 $$ |

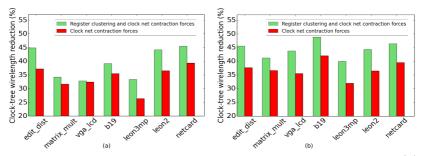

| $Figure\ 53$      | Clock-tree wirelength reduction                                   |

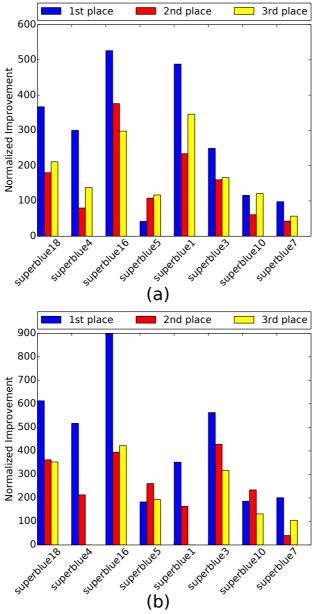

| $Figure\ 54$      | Normalized improvements for the contest top-3 teams.<br>. $192$   |

|                   |                                                                   |

#### LIST OF TABLES

#### LIST OF ALGORITHMS

| 1      | INCREMENTAL_REGISTER_PLACEMENT      | 91  |

|--------|-------------------------------------|-----|

| 2      | INCREMENTAL_TIMING-DRIVEN_PLACEMENT | 93  |

| 3      | SOLVE_LR                            | 96  |

| 4      | DISCRETE_EUCLIDEAN_SEARCH           | 98  |

| 5      | NON-CRITICAL_CELL_RELOCATION        | 103 |

| 6<br>7 | SOLVE_LDP                           |     |

| 8      | INCREMENTAL LEGALIZATION            | 173 |

#### ACRONYMS

**ASIC** Application-Specific Integrated Circuit

CAD Computed-Aided Design

CMOS Complementary Metal-Oxide Semiconductor

**DAG** Directed Acyclic Graph

**EDA** Electronic Design Automation

ESL Electronic System Level

HDL Hardware Description Language

${\bf HPWL} \qquad \qquad {\it Half-Perimeter\ Wirelength}$

IP Intellectual Property

IRP Incremental Register Placement

ITDP Incremental Timing-Driven Placement

ITLA Incremental Timing-Driven Layer Assignment

$\begin{array}{lll} \textbf{LCB} & \textit{Local Clock Buffer} \\ \textbf{LP} & \textit{Linear Programming} \\ \textbf{LR} & \textit{Lagrangian Relaxation} \\ \textbf{NLDM} & \textit{Non-Linear Delay Model} \\ \textbf{RC} & \textit{Resistance Capacitance} \\ \textbf{RTL} & \textit{Register Transfer Level} \end{array}$

SoC System-on-Chip

STA Static Timing Analysis

TDP Timing-Driven Placement

TNS Total Negative Slack

VLSI Very-Large-Scale Integration

WNS Worst Negative Slack

#### LIST OF SYMBOLS

$\mathcal{C}$ : Set of standard cells  $\mathcal{P}$ : Set of fixed elements such as I/O pads and macro blocks V: Set of Vertices, where  $V = \mathcal{C} \cup \mathcal{P}$   $\mathcal{N}$ : Set of hyperedges, i.e. nets  $\mathcal{S}$ : Set of net segments  $\mathcal{L}$ : Set of metal layers  $c_j$ : Standard cell  $c_j$  belonging to the set  $\mathcal{C}$   $s_j$ : Net segment  $s_j$  belonging to the set  $\mathcal{S}$   $s_j$ : Horizontal coordinate of cell  $s_j$   $s_j$ : Vertical coordinate of cell  $s_j$

$h_j$ : Height of cell  $c_j$   $w_i$ : Width of cell  $c_j$

$\mathcal{I}_j$ : Fanin set of integers to identify vertices connected to the input of  $v_j$   $\mathcal{O}_j$ : Fanout set of integers to identify vertices connected to the output of  $v_j$   $\mathcal{TS}$ : Set of integers to identify vertices that produce a timing startpoint  $\mathcal{TE}$ : Set of integers to identify vertices that consume a timing endpoint

P: Clock period to achieve a frequency  $\frac{1}{P}Hz$   $a_j^L$  or  $a_j$ : Late arrival time at a given timing point j  $a_j^E$ : Early arrival time at a given timing point j  $r_j^L$  or  $r_j$ : Late required time at a given timing point j  $r_j^E$ : Early required time at a given timing point j  $slk_j^L$  or  $slk_j$ : Late slack at a given timing point j  $slk_j^E$ : Early slack at a given timing point j

$\delta_{i,j}^L$  or  $\delta_{i,j}^c$ : Late arc delay of a cell from an input i to the output of cell  $c_j$   $\delta_{i,j}^E$ : Early arc delay of a cell from an input i to the output of cell  $c_j$   $\sigma_{i,j}^L$  or  $\sigma_{i,j}$ : Late arc slew of a cell from an input i to the output of cell  $c_j$   $\sigma_{i,j}^E$ : Early arc slew of a cell from an input i to the output of cell  $c_j$   $\sigma_j^E$ : Worst arc slew of cell  $c_j$   $\sigma_j^E$ : Best arc slew of cell  $c_j$   $\sigma_j^S$ : Slew of a net segment  $s_j$   $\tau_{i,j}$ : Elmore delay for the wire connecting  $c_i$  and  $c_j$   $d_{i,j}^L$ : Sum of late arc delay  $\delta_{i,j}^L$  and Elmore delay  $\tau_{i,j}$

$d_{i,j}^{E}$ : Sum of early arc delay  $\delta_{i,j}^{E}$  and Elmore delay  $\tau_{i,j}$

$R_i^s(q)$ : Resistance of segment  $s_j$  at layer  $l_q$

$R^{v}(q)$ : Resistance of via between two consecutive layers  $l_q$  and  $l_{q+1}$

$C_i^s(q)$ : Capacitance of segment  $s_j$  at layer  $l_q$

$C^{v}(q)$ : Capacitance of via between two consecutive layers  $l_q$  and  $l_{q+1}$

$C_j^{down}$ : Downstream capacitance of a cell, a net segment, or a via

$C_i^{in}$ : Input capacitance of  $c_i$

$\delta_i^s(q)$ : Delay of a net segment  $s_j$  assigned to a layer  $l_q$

$\delta^v(q)$  : Delay of via between two consecutive layers  $l_q$  and  $l_{q+1}$

$\delta_{i,j}^v(p,q)$ : Delay of via connecting the net segments  $s_i$  and  $s_j$  at layers  $l_p$  and  $l_q$

$\lambda_{i,j}^L$ : Late net-weight from the output of  $c_i$  to the output of  $c_j$

$\lambda_{i,j}^{E}$ : Early net-weight from the output of  $c_i$  to the output of  $c_j$

$\lambda_{i,j}^c$ : Lagrange multiplier associated with a timing arc i,j of a cell  $c_j$

$\lambda_i^s$ : Lagrange multiplier associated with a net segment  $s_j$

$\alpha_{j,q}$ : Binary decision variable equals 1 if segment  $s_j$  is assigned to layer  $l_q$

#### CONTENTS

| 1 INTRODUCTION                                                 |

|----------------------------------------------------------------|

| 1.1 REQUIREMENTS AND CHALLENGES OF MODERN VLSI                 |

| CIRCUITS                                                       |

| 1.2 DESIGN FLOW OF CELL-BASED VLSI CIRCUITS 31                 |

| 1.3 PHYSICAL SYNTHESIS 34                                      |

| 1.3.1 Main Steps                                               |

| 1.3.2 The Impact of Placement on Timing 36                     |

| 1.3.3 The Impact of Routing on Timing 37                       |

| <b>1.3.4 Timing Closure</b>                                    |

| 1.3.5 Challenges for Contemporary Physical Synthesis 41        |

| 1.3.6 Problems Tackled in the Thesis                           |

| 1.4 SCIENTIFIC CONTRIBUTIONS                                   |

| 1.5 PUBLICATIONS, AWARD, AND DISTINCTION 45                    |

| 1.6 REPRODUCIBILITY                                            |

| 1.7 ORGANIZATION OF THIS THESIS 46                             |

| 2 FUNDAMENTAL CONCEPTS 47                                      |

| 2.1 PLACEMENT GOALS AND CONSTRAINTS 47                         |

| <b>2.1.1</b> Cell-Based Design                                 |

| 2.1.2 Abstract Design Representation 50                        |

| <b>2.1.3</b> Wirelength Estimation                             |

| <b>2.1.4</b> Cell Density Control                              |

| 2.2 TIMING MODELING AND CONSTRAINTS 53                         |

| 2.2.1 Setup and Hold Timing Constraints                        |

| 2.2.2 Timing Analysis and Metrics 55                           |

| 2.2.3 Cell and Interconnection Modeling 57                     |

| 2.2.3.1 Cell Modeling and Concepts 59                          |

| 2.2.3.2 Interconnection Modeling and Concepts 61               |

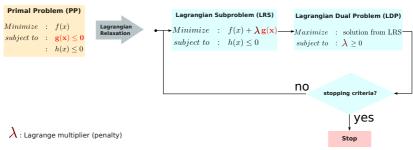

| 2.3 REVIEW OF LAGRANGIAN RELAXATION 64                         |

| 3 INCREMENTAL TIMING-DRIVEN PLACEMENT . 69                     |

| 3.1 RELATED WORKS 70                                           |

| 3.1.1 Works on Incremental Timing-Driven Placement 70          |

| 3.1.2 Works on Incremental Register Placement 73               |

| 3.1.3 The Hurdles Blocking a Proper Coupling 75                |

| 3.2 PROPOSED PROBLEM FORMULATION 76                            |

| 3.2.1 Tailoring Problem Instances for an Efficient Coupling 77 |

| 3.2.1.1 Choice of Constraints                                  |

| 3.2.1.2 Choice of Objective Functions                          |

| 3.2.2 Casting ITDP into an LR Formulation                                           | 80 |

|-------------------------------------------------------------------------------------|----|

| 3.3 PROPOSED TECHNIQUES                                                             | 85 |

| 3.3.1 Handling of Legalization During Incremental Place-                            |    |

| ment                                                                                | 85 |

| <b>3.3.2</b> The Proposed Flow                                                      | 87 |

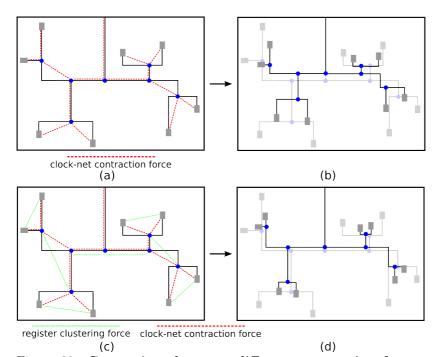

| ${\bf 3.3.3}\ Incremental\ Register\ Placement$                                     | 89 |

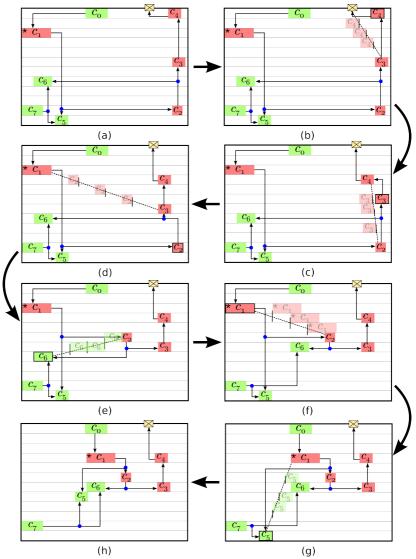

| ${\bf 3.3.4~Incremental~Timing\text{-}Driven~Placement} \ \ldots \ \ldots$          | 93 |

| 3.3.4.1~ Solving the Proposed LR Formulation                                        |    |

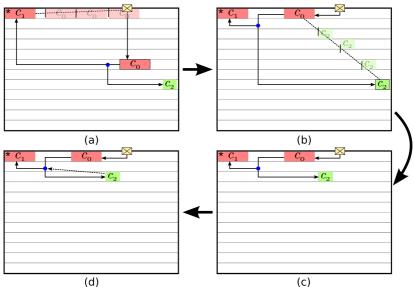

| $3.3.4.2 \ \ {\rm Non\mbox{-}Critical\ Cell\ Relocation} \ \dots \dots \dots \dots$ |    |

| 3.4 EXPERIMENTAL VALIDATION                                                         |    |

| 3.4.1 Experimental Infrastructure                                                   |    |

| $3.4.2$ The Impact of the Proposed Technique $\ldots\ldots\ldots$                   |    |

| 3.4.3 Further Evidences of Clock-Tree Compactness $\ldots\ldots$                    |    |

| 3.5 CONCLUSIONS                                                                     |    |

| 4 INCREMENTAL TIMING-DRIVEN LAYER ASSIGN-                                           |    |

| MENT                                                                                |    |

| 4.1 RELATED WORK                                                                    |    |

| 4.2 PROBLEM DEFINITION                                                              |    |

| 4.2.1 Routing Grid Modeling                                                         |    |

| 4.2.2 Timing Modeling                                                               |    |

| 4.2.3 The Target Problem                                                            |    |

| 4.3 PROPOSED PROBLEM FORMULATION                                                    |    |

| 4.3.1 Proposed Binary Integer Programming Formulation                               |    |

| 4.3.2 Proposed Lagrangian Relaxation Formulation                                    |    |

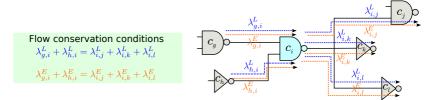

| 4.3.3 Obtaining Lagrange Multipliers for Net Segments                               |    |

| 4.4 PROPOSED TECHNIQUE                                                              |    |

| 4.4.1 Min-Cost Network Flow Model                                                   |    |

| 4.4.2 Cost Linearization                                                            |    |

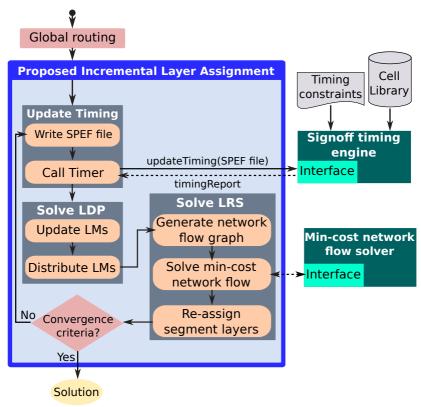

| 4.4.3 Proposed Framework                                                            |    |

| <b>4.4.4 Network Flow Graph Generation</b>                                          |    |

|                                                                                     |    |

| 4.5.1 Infrastructure                                                                |    |

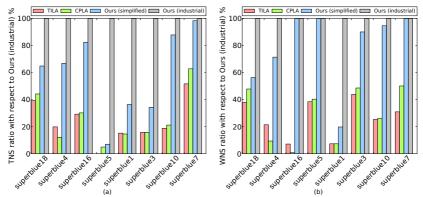

| 4.5.3 Comparison under an industrial Timer                                          |    |

| 4.5.4 Impact of the Timing Engine Accuracy                                          |    |

| 4.5.5 Impact of the Timing Engine Accuracy                                          |    |

| 4.5.6 Impact of Algorithmic Decisions                                               |    |

| 4.6 CONCLUSIONS                                                                     |    |

| 5 OVERALL CONCLUSIONS AND PERSPECTIVES.                                             |    |

| 5.1 CONCLUSIONS                                                                     |    |

| 5.2 FUTURE DIRECTIONS                                                               |    |

| Bibliography                                        | 155  |

|-----------------------------------------------------|------|

| APPENDIX A - The Incremental Legalization Technique | e169 |

| APPENDIX B - Results Under the ICCAD 2014 Con-      |      |

| test Infrastructure                                 | 177  |

| APPENDIX C - Results of the Proposed Technique Sub- |      |

| mitted to the ICCAD 2015 Contest                    | 189  |

#### 1 INTRODUCTION

This chapter first summarizes the overall hardware design flow when targeting cell-based VLSI designs (e.g. Systems-on-Chip, Application-Specific Integrated Circuits). Then it focuses on the physical synthesis phase and points out the challenging timing optimization problems tackled in the thesis. The chapter ends with a discussion of the scientific contributions.

#### 1.1 REQUIREMENTS AND CHALLENGES OF MODERN VLSI CIR-CUITS

The astonishing evolution of CMOS technology made possible integrated circuits with hundreds of millions of transistors (or even billions) assembled into a single silicon chip, giving rise to the jargon Very-Large-Scale Integration (VLSI) (KAHNG et al., 2011). VLSI systems span a wide range of classes of integrated circuits such as high-end microprocessors, Field-Programmable Gate Arrays (FPGAs), Application-Specific Integrated Circuits (ASICs), and Systems-on-Chip (SoCs) (PAPA, 2010). The design of a VLSI circuit is a highly complex process that can be carried out by two main circuit-design styles adopted in the industry: full-custom and semi-custom. Full-custom is a labor-intensive methodology where the component layouts are handcrafted and placed almost anywhere in the layout surface to obtain a very compact chip with optimized electrical properties (SAIT; YOUSSEF, 1999; KAHNG et al., 2011). This design style targets the specific class of circuits where the design cost can be amortized over high-volume production such as high-end microprocessors and FPGAs. Semi-custom (or Cell-Based) is a highly-automated design methodology that relies on predesigned elements to reduce the design complexity and hence, the overall cost and time-to-market. This design style targets a different market segment that includes ASICs and SoCs. Although cell-based circuits are slower and consume more power than full-custom circuits, this gap has been decreasing over the last years thanks to the constant research and innovation in the area (CHINNERY, 2013).

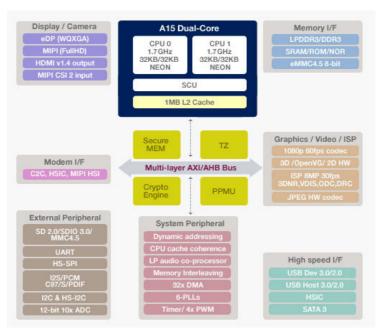

SoCs are very complex heterogeneous systems that are composed of one or more CPUs, hardware accelerators, memory subsystem (with one or more levels of cache), interconnect fabric, and non-volatile memory to store the embedded software (MARTIN; CHANG, 2003). Figure

Figure 1: Example of an SoC: Samsung Exynos 5 Dual. A couple of smartphones that use this SoC are Google Nexus 10 and Samsung Galaxy Tab II. Obtained from (SAMSUNG, 2016).

1 shows the block diagram of a contemporary SoC that uses a pair of ARM Cortex-A15 CPUs.

Nowadays, SoCs represent the main drivers for cell-based design methodologies as they are responsible for fueling the consumer electronics market, especially in the segment of smartphones, tablets, and other portable devices like digital cameras and gaming consoles (ITRS, 2015). Figure 2 brings the IC market share and growth forecast from 2013 to 2018 for different classes of products. Observe that products using SoCs account for a large portion of the market (e.g. cellphones, tablets, game consoles). Also notice that, although the growth forecast for smartphones and tablets is smaller than other segments (e.g. Internet of Things) they will keep growing and will represent an important share of the IC market. The very short product life cycle of consumer electronics and the growing demand for functionality and high-performance create the need for continued research for new algorithms and methodologies.

The consumer electronics market has been pushing SoC power and performance requirements and represents a challenge for the indus-

#### IC End-Use Markets (\$B) and Growth Rates 30% Cellphones Standard PCs \$70.7 \$59.1 25% Share of 2014 IC Sales (Est) 20% 15% Automotive **Tablets** \$21.7 Servers Wireless 10% \$17.6 **Digital TVs** Networks \$14.0 Internet \$14.1 \$9.4 of Things 5% Game Consoles \$4.5 \$3.3 Set-Top Boxes \$5.5 Medical \$4.5 0% -1% 1% 3% 7% 9% 11% 13% 15% 17% 19% 5% 23%

# Figure 2: Market share of 2014 IC sales (y-axis) and projected growth in IC sales from 2013 to 2018 (x-axis). Cellphones continue to be the largest drivers of IC sales, accounting for 25% of the total, while standard PCs represent 21%. Other produts following cellbased methodology like tablets and game consoles also account for an important market share and will continue growing. Obtained from (IN-SIGHTS, 2014).

2013-2018

Source: IC Insights

try: the execution of computationally-intensive applications using the least amount of energy (to maximize battery life) and the compliance with a power limit (to enable power dissipation from a compact device) (CHAN et al., 2014).

The **required clock frequency** affects the performance of a VLSI circuit and induces timing constraints that must be properly handled by synthesis tools. This thesis focuses on techniques for **timing closure of cell-based VLSI circuits**, i.e. techniques able to iteratively reduce the number of timing violations until the synthesis of the synchronous digital system reaches the specified target frequency.

#### 1.2 DESIGN FLOW OF CELL-BASED VLSI CIRCUITS

The design of VLSI circuits is a very complex task that demands the use of sophisticated tools and methodologies that are referred to as Electronic Design Automation (EDA) (PAPA, 2010; KAHNG et al., 2011). To cope with the design complexity and to reduce the design time, the vast majority of hardware design flows use libraries of predesigned components (the so-called standard cells) and intellectual property (IP) blocks. A standard cell library contains the physical layout of primitive building blocks with different functionalities (e.g., logic gates, adders, registers), which are provided by foundries or vendors (CHINNERY; KEUTZER, 2002). For each standard cell, the library provides the geometric information (e.g., layout, width, height) and the electrical characteristics (delay, power, etc) that are required for successful hardware synthesis.

The first step of an SoC design flow defines the system specification and performs the hardware/software partitioning at Electronic System Level (ESL). From the system specification, ESL tools help define the **hardware specification** and the requirements such as performance, power, and area, as well as the basic architecture, including memories and IP blocks, which represent the starting point for the hardware design flow (MARTIN; BAILEY; PIZIALI, 2010).

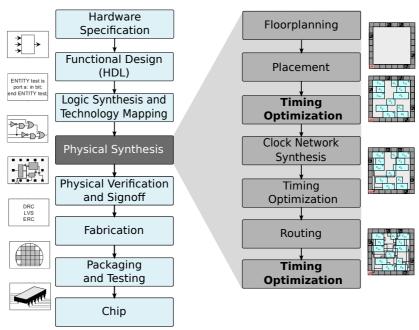

Figure 3 illustrates a simplified top-down hardware design flow<sup>1</sup>. It starts at a high abstraction level, defining the hardware specifications and general architecture, and it ends at a low abstraction level, where the chip layout geometry is determined for fabrication (COUSSY; MORAWIEC, 2010). EDA tools are adopted in almost every step of the design flow. The **functional design** step describes the functionality and timing behavior at register transfer level (RTL) using hardware description languages (HDL) such as VHDL and Verilog. The logic synthesis and technology mapping step is an automated process that converts the described hardware into boolean expressions and maps them into a set of standard cells from a library. Then physical synthesis (also known as physical design) instantiates the layout of standard cells (their geometric representations), assigns their spatial locations, and creates the connections between them. Physical verification checks the electrical and logic functionality of the physical layout while signoff validates the circuit timing and fixes some minor errors. In the **fabrication** step, the layout is sent to a foundry to be manufactured. Finally, a packaging and testing step prepares the fabricated circuit for actual use.

In earlier technology generations (say, above 180 nm), the delays of logic gates were a determinant factor of circuit timing, whereas resistance and capacitance of interconnections (wires) were proportionally less significant and could be disregarded. In such scenario, logic synthesis was able to provide accurate timing estimates (ALPERT et al.,

<sup>&</sup>lt;sup>1</sup>Although the hardware design flow is iterative, this is not captured in the figure for simplicity. Besides, a few steps are merged while others are omitted for clarity.

Figure 3: Major steps of hardware design flow. The right-hand side illustrates the main physical synthesis steps. Adapted from (KAHNG et al., 2011).

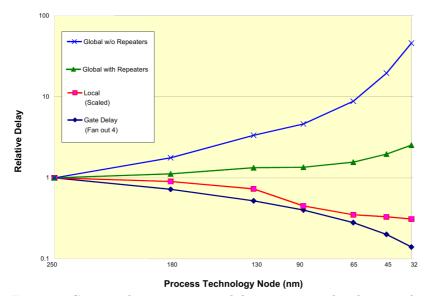

2007; ALPERT; CHU; VILLARRUBIA, 2007). However, in technologies below 250 nm, interconnections became more resistive and thus their delays are much more significant as compared to the delays of logic gates (HO; MAI; HOROWITZ, 2001; SAXENA et al., 2004). As a consequence, timing estimates without physical information would be so inaccurate to the point that the physical design steps could invalidate the optimizations obtained during logic synthesis (PAPA et al., 2011). Figure 4 shows the dramatic increase of global interconnect delay with technology scaling. Being up to 3 orders of magnitude higher than gate delay for 32nm, it represents one of the major challenges to be overcome during the physical synthesis of modern VLSI circuits. In face of this trend, **physical synthesis** became again an intensive research field (ALPERT; CHU; VILLARRUBIA, 2007).

Figure 4: Gate and interconnect delay versus technology scaling. Local wires correspond to Metal 1 level (intra-cell connections), while global wires correspond to upper metal levels (inter-cell connections). Notice that although local interconnect and gate delays have scaled down, global interconnect delays have grown (even with repeaters) and represent a bottleneck for circuit timing. Obtained from (ITRS, 2005).

#### 1.3 PHYSICAL SYNTHESIS

The main objective of physical synthesis is to obtain a circuit layout that satisfies the timing constraints induced by the target clock frequency (VISWANATHAN et al., 2010; KAHNG, 2015). During the physical synthesis, several optimization techniques are used to gradually reduce the number of timing violations<sup>2</sup> until the circuit reaches the specified clock frequency. Such an iterative process, known as timing closure, corresponds to the most critical task of modern SoCs (ALPERT et al., 2007; KAHNG, 2015)

This section first reviews the main steps of physical synthesis. Then it reviews the timing closure flow and points out some important challenges faced by contemporary physical synthesis. The section ends

$<sup>^2{\</sup>rm Timing}$  violations represent a measure of how far from the timing constraints (specified to achieve the target frequency) the circuit is.

up with a description of the problems tackled in the thesis.

## 1.3.1 Main Steps

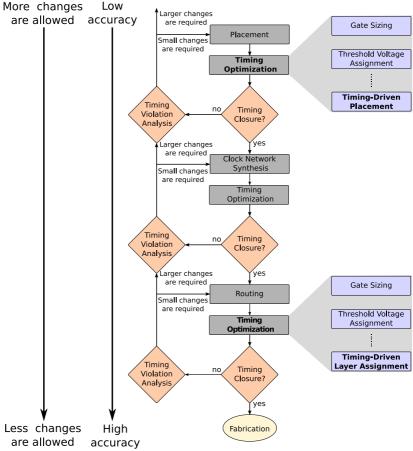

As illustrated on the right-hand side of Figure 3, physical synthesis consists of the following steps:

- Floorplanning defines the chip dimensions and locations of I/O pins and macro blocks (e.g., memories and intellectual property blocks) and defines how to partition the circuit into smaller subcircuits, when possible;

- Placement finds the planar locations of standard cells so as to minimize an estimate of the wirelengths between the cells and keep the density<sup>3</sup> profile under control;

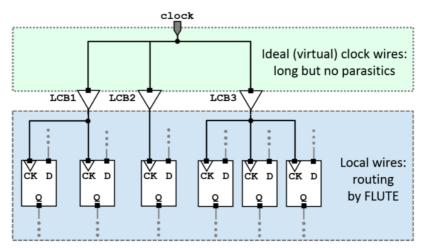

- Clock Network Synthesis determines the clock network topology to deliver the clock signal to each sequential<sup>4</sup> element and also adds buffers in some specific parts of the clock network so as to meet skew<sup>5</sup> and delay requirements;

- Routing connects the instantiated standard cells using different metal layers so as to minimize the wirelength and comply with limited routing resources;

- Timing Optimization techniques are used between different steps of physical synthesis to gradually achieve the circuit timing constraints. The earlier in the design flow, the more opportunities for changes, but the lower the accuracy; the later in the design flow, the higher the accuracy, but the more limited the amount of changes.

During the Placement and Routing steps, the primary goals are to minimize the interconnect wirelength and comply with some design

<sup>&</sup>lt;sup>3</sup>Density gives an indication of the average standard cell utilization over the whole chip area. Generally, the chip area is divided into squares and there is a density constraint, say 0.7, which indicates that the average standard cell area over the available area on each square is below 0.7. It is important to keep density under control to ensure that the routing step can provide an effective solution (KIM et al., 2012). More details are given in Section 2.1.4.

$<sup>^4\</sup>mathrm{A}$  storage element controlled by the clock signal such as a register or a latch.

$<sup>^5{\</sup>rm The}$  skew is the maximum delay difference of the clock signal between any pair of sequential elements.

constraints, while timing is generally considered as a secondary objective metric (ALPERT; MEHTA; SAPATNEKAR, 2008). That is why incremental optimization techniques play a major role during physical synthesis to improve previously optimized solutions (COUDERT et al., 2000). This thesis targets two incremental timing optimization problems at different steps of the physical synthesis flow (as highlighted on the right-hand side of Figure 3). The **first** is solved right after the Placement step, when the planar locations of the cells were already defined. Although this step of the design flow provides more opportunity for changes, it relies on wirelength estimates since the actual routing has not yet been defined. The second problem is tackled right after the Routing step, when the interconnection topologies and metal layers were already defined. This step provides much higher accuracy for the interconnect delays, but the opportunity for changes is smaller. The next two subsections provide illustrative examples to show the importance of each of the two timing optimization problems.

### 1.3.2 The Impact of Placement on Timing

Placement is a key step to physical synthesis and has a huge impact on circuit timing due to four main reasons (WANG; CHANG; CHENG, 2009) (PAPA et al., 2011):

- 1. The cell locations have a strong impact on the interconnections wirelengths, which affect signal delays due to their resistance and capacitance.

- 2. The locations of sequential elements determined by the placement step serve as the starting point for clock network synthesis (therefore, a poor placement can undermine the quality of the clock network).

- 3. The distribution of cells along the planar surface has a substantial impact on the routing step (therefore a well-placed circuit will have shorter interconnections).

- 4. The density of cells has a direct relation with heat distribution throughout the chip and therefore affects power consumption.

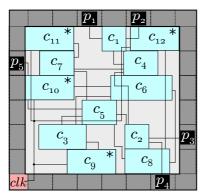

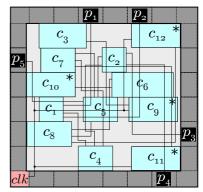

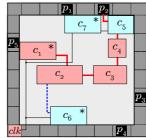

Figure 5 illustrates the impact of placement through a toy example. Note that the interconnections are longer for the solution on

Figure 5: **Impact of placement.** The symbols c and p represent standard cells and circuit pads (i.e. an electrical terminal used as a connection for external inputs and outputs), respectively. To mark the cells consisting of a sequential element, we employ an asterisk. Comparing the alternative placement solutions, observe that the poor placement on the right-hand side dramatically increases the circuit wirelength and, therefore degrades circuit timing and routability.

the right-hand side. This illustrates how cell locations influence the resulting wirelength and, therefore, circuit timing. For this reason, techniques that optimize cell locations are likely to drive the next generation of research on physical synthesis (ALPERT et al., 2012; MARKOV; HU; KIM, 2012).

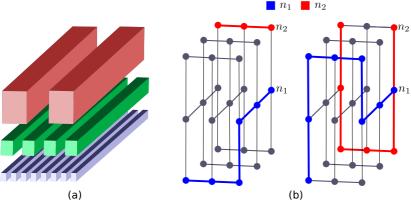

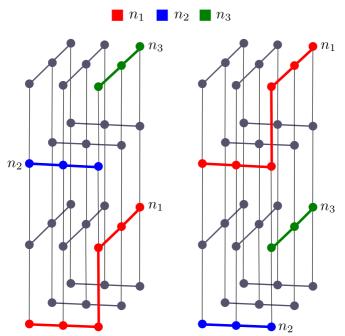

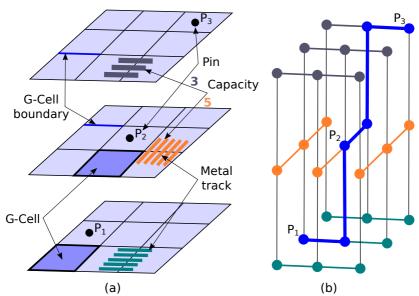

# 1.3.3 The Impact of Routing on Timing

The global routing step has a major impact on circuit timing as it defines the interconnection topologies and the metal layers (HELD et al., 2015). Modern technologies provide several metal layers with different widths and thicknesses, where upper layers are wider and thicker than lower ones, as illustrated in Figure 6(a). Figure 6(b) illustrates the impact of routing through a toy example. Note that the interconnections are much longer for the solution on the right-hand side. In addition, the critical net  $(n_2)$  is routed in the lowest layer, which is much more resistive than the upper layer, degrading the net delay. This illustrates how the choice of interconnect topology and routing layer affects the circuit timing.

Technology nodes below  $32~\mathrm{nm}$  provide between four to six different metal widths and thicknesses where upper layers can be up to  $20~\mathrm{cm}$

times thicker than lower ones (ALPERT et al., 2010). Despite the dramatic reduction of resistance on upper layers, they require more area and thus offer less resources for routing. Therefore, upper metal layers must be wisely used to reduce the delay of critical interconnects. For this reason, efficient interconnect synthesis techniques are of utmost importance for the timing closure of contemporary circuits (LI et al., 2008; HU; LI; ALPERT, 2009; WEI et al., 2013).

Figure 6: **Impact of routing.** (a) 3 groups of metal layers with different widths and thicknesses. (b) 3x3 routing grids with 3 metal layers and 2 nets. Comparing the alternative routing solutions, observe that the poor routing on the right-hand side introduces a lot of detours, dramatically increasing the interconnect wirelengths and also degrading the circuit timing.

# 1.3.4 Timing Closure

Timing closure of modern circuits is not a straightforward task that can be easily achieved by a simple top-down process. In practice, it is hardly achieved in a single iteration (PAPA et al., 2011). An industrial timing closure flow is an iterative process that is integrated to several steps of physical synthesis, as illustrated in Figure 7.

Observe that, at different stages of the design flow, there are decision steps to check for timing closure. During the timing closure steps, a timing analysis engine is employed (for the timing violation analysis) to assess whether the target clock frequency is met or not. In other words, it determines the difference between the clock period and how long a signal takes to traverse the longest path (PAPA, 2010).

Figure 7: **Timing closure during physical synthesis.** Although the design flow varies from vendor to vendor, this flowchart captures the iterative nature of timing closure process (GREG, 2016).

Failing to achieve timing closure in a given step means that designers must analyze the violations reported by the timing analysis engine, identify the failing steps, and backtrack in the design flow. Therefore, the physical synthesis turnaround time strongly depends on the success of timing closure.

Notice that the design flow enforces gradual reduction in the amount of changes to enforce convergence. The timing models also become more accurate as the flow progresses. For example, after the placement step, although optimization techniques rely on wirelength estimates (since routing information is not yet available) many changes can be made to improve timing. Therefore, at the beginning of the design flow, the timing closure step also checks the timing constraints assuming approximative timing models. As the design converges to final steps, although the accuracy of timing information increases, the scope and magnitude of changes are reduced. Therefore, it is expected that the amount of violations in late steps is small enough. Failing to achieve timing closure in late steps may require to backtrack to the placement, or even to the logic synthesis step, which can undermine the tight design schedule, resulting in a late time-to-market, which may lead to millions of dollars of loss in revenue.

During physical synthesis, timing optimization techniques such as gate sizing and threshold voltage assignment are widely used to modify the electrical characteristics of standard cells so as to improve timing. These techniques take advantage of the fact that a standard cell library provides, for each cell, many implementation options with different timing and power characteristics (OZDAL; BURNS; HU, 2012). Being limited to exploiting cell characteristics, these techniques are not able to modify the interconnection characteristics to optimize the circuit timing. In the scenario of contemporary designs, where the interconnections play a very important role, **timing-driven placement** and **timing-driven layer assignment** appear as promising optimization techniques, and therefore, attracts the attention from both industry and academia (ALPERT et al., 2012; KIM; HU; VISWANATHAN, 2014; YU et al., 2015).

Although there has been research in timing optimization techniques for more than 20 years, most of them were conceived for old technological scenarios. Since the evolution and changes in the semiconductor industry is very rapid, new research and techniques must consider the challenges to be tackled for contemporary physical synthesis. The next subsection presents a set of challenges to be tackled by optimization techniques in contemporary physical synthesis, accord-

ing to the EDA industry.

## 1.3.5 Challenges for Contemporary Physical Synthesis

The continuous evolution of technology brings new challenges that require the EDA industry to review many supposedly consolidated solutions. Some of the challenges are detailed below.

- Heterogeneous fabrics: The high-complexity and short time-to-market requires the use of hierarchical methodologies with thirdy-party macro (IP) blocks. This demands an heterogeneous integration of standard cells and macro blocks, causing serious challenges to circuit legalization<sup>6</sup> and timing closure (PAPA et al., 2011; ALPERT; MEHTA; SAPATNEKAR, 2008).

- Fast turnaround time: The time-to-market pressure leads to very fast turnaround time requirements. Recent papers from the industry point out a very tight turnaround time of 12 hours per million of cells for the whole physical synthesis (PAPA et al., 2011; REIMANN; SZE; REIS, 2016). Therefore, only near-linear-time optimization algorithms can be applied to fit in that runtime budget.

- Problem size: The number of cells in modern circuit grows at a steep rate so as to address the increasing demand for new functionalities. Although hierarchical approaches can alleviate the problem complexity, modern optimization techniques must be scalable enough to handle subcircuits with millions of cells (ALPERT; MEHTA; SAPATNEKAR, 2008).

- NP-complete problems: A number of optimization problems to be solved during physical design belong to the NP-complete<sup>7</sup> class (PAPA et al., 2011). In short, very large instances of NP-complete problems must be solved quickly to cope with the runtime budget required by contemporary physical synthesis. This renders the need of very efficient algorithms and heuristics that

$<sup>^6\</sup>mathrm{A}$  step performed to ensure that cells and macro blocks do not overlap and satisfy some design rules required for the circuit fabrication.

<sup>&</sup>lt;sup>7</sup>It refers to the class of problems for which the solution cannot be found in polynomial time w.r.t. the number of inputs, but it can be verified in polynomial time (CORMEN et al., 2009). For example, the solution of timing optimization problems, which are the scope of this thesis, can be verified in polynomial time using a static timing analysis tool.

must take advantage of problem specific characteristics and technology parameters.

Therefore, the proposed solutions for the problems tackled in this thesis take into account the aforementioned challenges<sup>8</sup>.

#### 1.3.6 Problems Tackled in the Thesis

Recent position papers from industry and academia point out the importance of efficient interconnect synthesis techniques to satisfy the circuit timing constraints and close on timing (ALPERT et al., 2012; MARKOV; HU; KIM, 2012; LI et al., 2012; WEI et al., 2013). Therefore, this thesis focuses on specific optimization techniques that have a direct impact on circuit interconnects, one applied right after the global placement step and another applied right after the global routing step (as highlighted in Figure 7). The specific motivations and definitions for the **two** problems tackled in the thesis are detailed in the following:

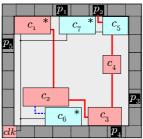

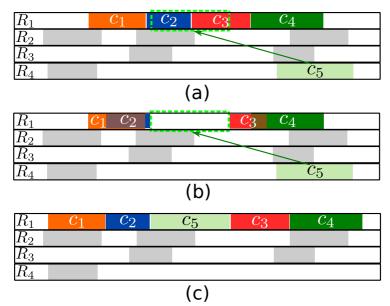

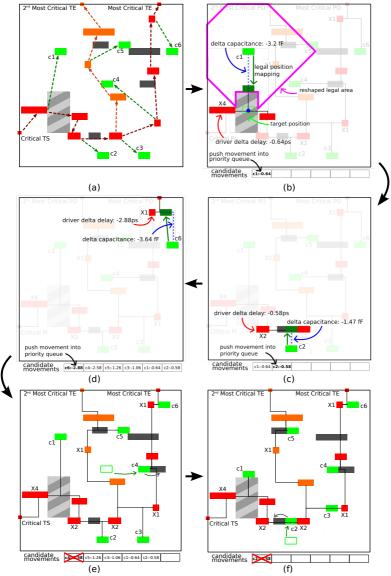

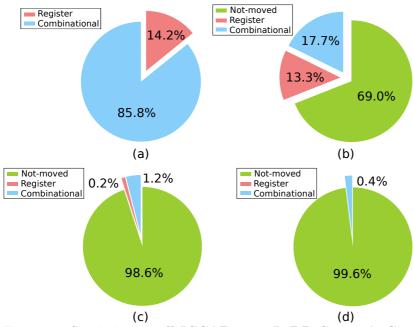

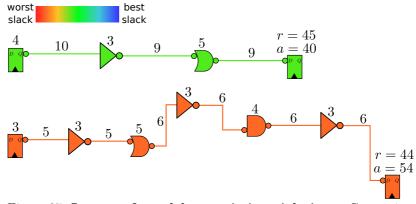

- 1. Incremental Timing-Driven Placement (ITDP) finds new locations for standard cells (both logic and sequential cells) so as to improve the circuit timing and preserve the placement quality in terms of wirelength and density. Figure 8 illustrates the basic idea of ITDP through a toy example. Although there have been significant advances in ITDP, there is a lack of efficient techniques to handle the growing number of cells and macro blocks in current and future designs. This problem is addressed in Chapter 3.

- 2. Incremental Timing-Driven Layer Assignment (ITLA) reassigns the metal layers of critical and non-critical net segments so as to improve the circuit timing while observing the routing capacity constraints. Figure 9 illustrates the basic idea of ITLA through a toy example. Although many timing-driven layer assignment techniques can be found in the literature, most were conceived with inaccurate timing models, which is not appropriate for late stages of the physical design flow. This problem is addressed in Chapter 4.

$<sup>^8{\</sup>rm Other}$  important challenges like complex manufacturing rules for advanced technology nodes can also be considered (XU et al., 2016).

Figure 8: Basic idea of incremental timing-driven placement. Thick (red) wires on the left-hand side solution indicate those that most affect the circuit timing and thus should be shortened as much as possible. The idea of incremental timing-driven placement is to relocate some cells to shorten those critical wires without increasing too much the length of the others. The alternative solution on the right-hand side relocates cells  $c_1$ ,  $c_2$ ,  $c_3$ , and  $c_4$  to shorten those critical wires so as to reduce the signal delay and improve the circuit timing. Note that care must be taken to preserve the placement quality. For instance, avoiding the introduction of significant overhead in the wires connected to other cells, such as the wire from  $c_2$  to  $c_6$  (dotted blue line).

#### 1.4 SCIENTIFIC CONTRIBUTIONS

The solutions presented in this thesis to solve the two problems listed in the previous subsection bring the following innovations that represent the main scientific contributions:

- 1. A novel incremental timing-driven placement formulation based on Lagrangian Relaxation: A new Lagrangian Relaxation formulation for ITDP that minimizes the total negative slack for both setup and hold timing violations, where Lagrange multipliers are used as net weights and are dynamically updated with an accurate timing analyzer. To solve the formulation, this work proposes a technique that relies on a novel discrete search and employs Euclidean distance to define a proper neighborhood. To further improve circuit timing, we also propose a technique to exploit non-critical interconnect branches and to reduce the capacitive load of critical cells. Discussion of detailed contributions in face of related works will be addressed in Chapter 3.

- 2. A novel incremental layer assignment technique driven

Figure 9: Basic idea of incremental timing-driven layer assignment. A 3x3 routing grid with 4 layers and 3 nets: one critical  $(n_1)$  and two non-critical  $(n_2$  and  $n_3)$ . The idea of incremental timing-driven layer assignment is to re-assign the layers of critical and non-critical nets so as to improve the circuit timing while satisfying routing constraints. The alternative solution on the right-hand side re-assigns non-critical nets to release upper layers for the critical net. Care must be taken to satisfy the routing capacity constraints.

by an external signoff timing engine<sup>9</sup>: The new approach handles simultaneously critical and non-critical segments and Karush-Kuhn-Tucker to extract timing information for each net segment individually, thereby enabling the use of an external timing engine. Discussion of detailed contributions in face of related works will be addressed in Chapter 4.

$<sup>^9\</sup>mathrm{A}$  timing analysis tool that employs high-order models to obtain accurate delay estimates (KAHNG et al., 2011).

#### 1.5 PUBLICATIONS, AWARD, AND DISTINCTION

The results of the research described in this thesis were previously reported in four conference papers and two articles, as follows:

- Timing-Driven Placement Based on Dynamic Net-Weighting for Efficient Slack Histogram Compression published in the proceedings of the ACM International Symposium on Physical Design<sup>10</sup> (GUTH; LIVRAMENTO et al., 2015).

- Exploiting Non-Critical Steiner Tree Branches for Post-Placement Timing Optimization published in the proceeding of the ACM/IEEE International Conference on Computer-Aided Design (LIVRAMENTO et al., 2015).

- Speeding up Incremental Legalization with Fast Queries to Multidimensional Trees published in the proceedings of the IEEE Computer Society Annual Symposium on VLSI (NETTO; LIVRAMENTO et al., 2016b).

- Evaluating the Impact of Circuit Legalization on Incremental Optimization Techniques published in the proceedings of the IEEE Symposium on Integrated Circuits and Systems Design (NETTO; LIVRAMENTO et al., 2016a)

- Clock-Tree-Aware Incremental Timing-Driven Placement published in the ACM Transaction on Design Automation of Electronic Systems (LIVRAMENTO et al., 2016).

- Incremental Layer Assignment Driven by an External Signoff Timing Engine published in the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (LIVRAMENTO et al., 2017).

Besides, the implementations of the proposed techniques were submitted to international contests on Computer-Aided Design (CAD) to allow a direct comparison of their results with other groups worldwide. This effort resulted in one award and one distinction.

• First place in the ACM/SIGDA ICCAD Contest on Incremental Timing-Driven Placement 2015 among 42 teams (KIM et al., 2015).

$<sup>^{10}</sup>$ This paper was among the three candidates for best paper award.

• Fifth place in the ACM/SIGDA ICCAD Contest on Incremental Timing-Driven Placement 2014 among 27 teams (KIM; HU; VISWANATHAN, 2014).

### 1.6 REPRODUCIBILITY

To allow for reproducibility of the proposed techniques reported in this thesis, the algorithms are fully described in pseudo-code and the experimental infrastructure are available in the public domain. The experimental parameters adopted on each algorithm are also reported.

### 1.7 ORGANIZATION OF THIS THESIS

The rest of this thesis is organized as follows. Chapter 2 presents enough fundamental concepts to keep this thesis self-contained. Chapters 3 and 4 present the solution techniques to address the target problems. Each of the chapters identifies the contribution of proposed techniques in face of related works, reports experimental results, and discusses partial conclusions. Finally, Chapter 5 draws the overall conclusions and perspectives.

#### 2 FUNDAMENTAL CONCEPTS

To keep this thesis self-contained, this chapter presents the fundamental concepts needed to understand the next chapters. First, it introduces basic placement concepts, terminology, and modeling. Then it formalizes timing modeling. Finally, it reviews the basic concepts of Lagrangian Relaxation.

### 2.1 PLACEMENT GOALS AND CONSTRAINTS

This section first reviews the main concepts associated with designs that use standard and macro cells as the building blocks of circuits' layouts. It briefly describes how placement tools produce an **abstraction** of the actual layout where circuit components are assigned to locations, but whose actual interconnections will be defined later on during the upcoming routing step. It discusses how **estimates** of the actual interconnection wirelength can be obtained for guiding placement. This is because the circuit wirelength gives a reasonable first-order approximation of real objective functions like timing, power, and routability (ALPERT; MEHTA; SAPATNEKAR, 2008).

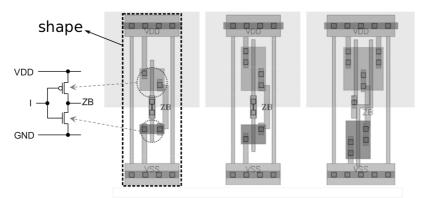

# 2.1.1 Cell-Based Design

A standard cell corresponds to a predesigned block composed of a shape, a set of electrical characteristics, and a layout. During physical synthesis, EDA tools handle the external attributes of cells (front-end view): the shape (height and width) of the envelop containing the layout and the set of electrical characteristics (delay, power etc). The inner layout (back-end view) relates to the geometries of the various materials and/or steps that are used by foundries for fabrication. Standard cells follow a restricted layout style so as to reduce the design complexity and therefore the time-to-market (KAHNG et al., 2011). All cells have a fixed height and must be placed in rows to be connected to power and ground supply rails, as exemplified by the inverter layout shown in Figure 10.

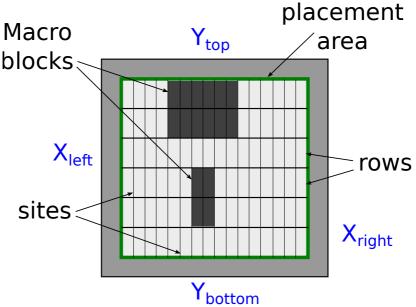

The floorplanning step defines the chip physical boundaries (left, right, bottom, and top), denoted as  $X_{left}, X_{right}, Y_{bottom}$ , and  $Y_{top}$ . It also defines the placement area, which is divided into a grid of standard

Figure 10: Layout examples with different electrical characteristics and shapes. All layouts have the same functionality (an inverter) and are built for the same technology (65 nm). The leftmost layout corresponds to the slowest inverter; the rightmost, to the fastest. Observe that the three options have exactly the same height, although the width can vary from one option to another. Adapted from (KAHNG et al., 2011).

cells rows (horizontal) and sites (vertical) that are used for wiring during the routing step, as exemplified in Figure 11. Therefore, the height of cells must be a multiple of the row height; the width, a multiple of site width. The routing between cells can only be performed in horizontal and vertical directions, also known as Manhattan routing. The locations of the macro blocks are also defined during the floorplanning step<sup>1</sup>. Macro blocks are large pieces of reusable logic (also known as IP blocks) that are employed to reduce the design cost and complexity. A macro block can be a processor core, a memory block, or even a video hardware accelerator (as in the SoC from Figure 1). These blocks can have very different shapes and sizes and are treated as blockages during the placement of standard cells.

Placement is generally performed in two phases. The **first phase**, which is called global placement, aims to put the standard cells within the placement area assuming cells as dimensionless elements (i.e. points). Global placement is generally performed using analytical techniques, which try to minimize the total circuit wirelength by solving a huge system of linear equations (KAHNG et al., 2011). During global place-

<sup>&</sup>lt;sup>1</sup> Although there are a few works that move macro blocks during the placement stage (known as mixed-size placement) (KIM et al., 2012), as a general rule the macros are placed during the floorplanning step and remain fixed for the rest of the design flow.

Figure 11: Circuit boundaries and grids. The thick rectangle (green) identifies the boundaries of the cells' placement area. The gray ring is reserved for I/O pads.

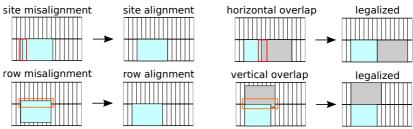

ment, the alignment to rows and sites is ignored, as well as overlaps between cells. Then there is a **second phase** called legalization (also known as detailed placement), which aligns all cells to rows and sites, removes overlaps, and tries to maintain the wirelength from the first phase. Figure 12 depicts examples of movements to align cells to sites and rows, as well as movements to remove horizontal and vertical overlaps.

Figure 12: Examples of standard cell alignment and legalization.

## 2.1.2 Abstract Design Representation

Placement techniques generally represent the circuit as a hypergraph  $G(V, \mathcal{N})$ . The vertex set is composed of two disjoint subsets  $\mathcal{C}$  and  $\mathcal{P}$ , i.e.,  $V = \{\mathcal{C} \cup \mathcal{P}\}$  with  $\mathcal{C} \cap \mathcal{P} = \emptyset$ . The elements of subset  $\mathcal{C} = \{c_1, c_2, ..., c_n\}$  represent standard cells while the subset  $\mathcal{P} = \{p_1, p_2, ..., p_n\}$  contains pre-placed elements such as macro blocks and I/O pads, which have fixed locations and cannot be moved. The set of hyperedges  $\mathcal{N} = \{n_1, n_2, ..., n_m\}$  represents the nets (wires) connecting two or more vertices (ALPERT; MEHTA; SAPATNEKAR, 2008). For each  $c_i \in \mathcal{C}$ , its attributes  $w_i$  and  $h_i$  denote the width and the height dimensions of the corresponding cell, while the pair  $(x_i, y_i)$  denotes its location, expressed by the coordinates of the cell's bottom left corner.

Let us sketch a formulation for placement as an optimization problem: given the hypergraph  $G(V,\mathcal{N})$ , find a location  $(x_i,y_i)$  for every  $c_i \in \mathcal{C}$  so as to optimize some design goal(s). Depending on the design requirements, placement may have distinct objectives such as minimizing wirelength, timing violations, or improving routability. Although placement is in general a multi-objective optimization problem, even a single-objective instance of it is NP-hard<sup>2</sup> problem. Therefore, the direct handling of multiple objectives is not viable. That is why, in practice, placement tools usually try to minimize the wirelength, a simple metric that correlates quite well with timing, power, routability, among others (ALPERT; MEHTA; SAPATNEKAR, 2008).

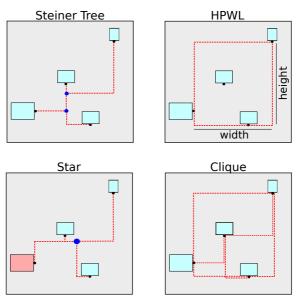

# 2.1.3 Wirelength Estimation

Since routing information is not yet available during the placement step, optimization techniques rely on interconnection estimates as a metric to minimize the total circuit wirelength (SPINDLER, 2008). There are several models that can be used during placement to estimate interconnections, each with different accuracy, footprint and runtime cost. Figure 13 presents four different models. The most accurate model is the Steiner tree due to its good correlation with the final routing (OBERMEIER; JOHANNES, 2004). However, using the Steiner tree model can be computationally expensive and the Half-Perimeter

<sup>&</sup>lt;sup>2</sup>It refers to the class of problems for which the optimal solution cannot be found nor verified in polynomial time with respect to the number of inputs. In other words, the time complexity cannot be defined as  $O(n^k)$ , where n is the number of inputs of the problem and k is a constant (CORMEN et al., 2009).

Figure 13: Different net models that can be used during placement. The dots (in blue) along the net in the Steiner model represent the Steiner points. The blue dot in the Star model represents a star point (i.e. the interconnection center of mass).

Wirelength (HPWL) model is generally used instead (due to its reasonable accuracy and low computational cost). HPWL estimates the wirelength through the half-perimeter of the rectangle that encloses all cell pins in a given interconnection. It is as accurate as the Steiner tree model for nets involving two or three pins, but underestimates the length for nets with four or more pins (KAHNG et al., 2011). The star model connects all interconnect pins with the interconnect center of mass while the clique model connects all pairs of pins. Both star and clique models overestimate the interconnect wirelength but are often preferred in analytical placement tools<sup>3</sup>, although they are less accurate than HPWL.

<sup>&</sup>lt;sup>3</sup>Analytical tools generally model the wirelength as a quadratic term due to differentiability purposes. That is why those tools often rely on the star or clique models, where each net length is computed using the Euclidean distance (ALPERT; MEHTA; SAPATNEKAR, 2008).

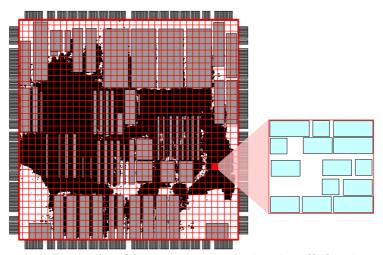

### 2.1.4 Cell Density Control

Besides minimizing wirelength, placement tools must also spread the cells through the placement area to reduce cell density. Controlling the density is important to reduce cell overlaps and also to leave space for routing and for layout intrusive optimization techniques like gate sizing and buffer insertion (ALPERT; MEHTA; SAPATNEKAR, 2008; VISWANATHAN et al., 2010). Placement tools try to keep the density below a given limit. A common metric to estimate density is to divide the placement area into squares called bins and compute their utilization dividing the occupied area by the total bin area (excluding the bins occupied by macro blocks) (KIM et al., 2012). Figure 14 presents an example of how to divide the placement area into bins. An efficient metric used to measure the impact of placement density is the Average Bin Utilization (ABU), which will be detailed in Section 3.2.1.1.

Figure 14: **Example of how to compute circuit cell density.** To compute density, the placement area is divided into squares (bins) whose edges are 9 times larger than the row height. The utilization of each bin (excluding those occupied by macro blocks) is computed dividing the occupied area by the total area. Supposing that each bin has a total area of  $324\mu m^2$  and the highlighted bin has an occupied area of  $250\mu m^2$ , thus the bin utilization is  $\frac{250}{324} \approx 0.77$ . Placement snapshot adapted from (SPINDLER, 2008).

#### 2.2 TIMING MODELING AND CONSTRAINTS

To evaluate the circuit performance and assess how far from the target clock frequency the circuit is, proper modeling of timing and adequate tracking of violations are required. This section firstly reviews the concepts of setup and hold timing constraints, which are both exploited in this thesis. Then it introduces timing analysis concepts and metrics through a small example. Finally, it details the adopted modeling for cell and interconnection electrical behavior.

### 2.2.1 Setup and Hold Timing Constraints

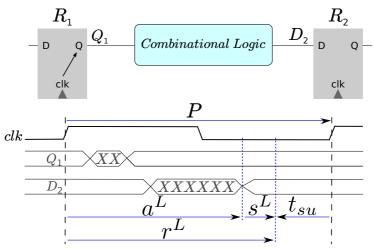

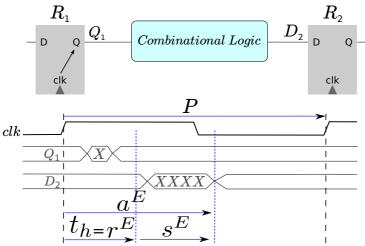

Timing constraints are applied to the circuit **combinational blocks**<sup>4</sup>, delimited by the **timing startpoints** (output of sequential elements and circuit input pads) and the **timing endpoints** (input of sequential elements and circuit output pads) (SAPATNEKAR, 2004). The timing model captures setup and hold constraints separately by comparing them with late and early arrival times, respectively. This leads to two timing scenarios which are referred to as **late** and **early**. Figures 15 and 16 illustrate these scenarios by showing two registers, named  $R_1$  and  $R_2$ , interleaved with a combinational block. To achieve a target frequency of  $\frac{1}{P}Hz$ , the clock period must be no greater than P time units.

The **setup time** corresponds to the amount of time during which a data signal must be stable at the input of a sequential element **before** the clock edge to ensure its correct sampling (capture) (SAPAT-NEKAR, 2004). The setup time of  $R_2$  in Figure 15 is labeled as  $t_{su}$ . The sum of the maximum delay of  $R_1$  (i.e. clock-to-output delay) and the maximum delay of the combinational block gives the **late arrival time**  $a^L$  at the input of  $R_2$ . The difference between P and  $t_{su}$  gives the latest time when data is allowed to be stable at the input of  $R_2$  so as to respect the setup constraint, and is denoted as the **late required time**  $r^L$ . The **late slack**  $s^L$  is computed as the difference between  $r^L$  and  $r^L$ . A non-negative value indicates that the setup constraint is satisfied.

The **hold time** corresponds to the amount of time during which a data signal must be stable at the input of a sequential element **after** the clock edge to ensure its correct sampling (capture) (SAPAT-

$<sup>^4{\</sup>rm A}$  combinational block implements a given logic that depends only on the block inputs and does not depend on any previous state.

Figure 15: Review of setup timing constraint (late scenario).

Figure 16: Review of hold timing constraint (early scenario).

NEKAR, 2004). The hold time of  $R_2$  in Figure 16 is labeled as  $t_h$ . The sum of the minimum delay of  $R_1$  and the minimum delay of the combinational block gives the **early arrival time**  $a^E$  at the input of  $R_2$ . The hold time  $t_h$  defines the earliest time when data is allowed to be stable at the input of  $R_2$  so as to respect the hold constraint, and is denoted as the **early required time**  $r^E$ . The **early slack**  $s^E$  is computed as the difference between  $a^E$  and  $r^E$ . A non-negative value indicates that the hold constraint is satisfied.

## 2.2.2 Timing Analysis and Metrics

To propagate the maximum and minimum delays through each combinational block and compute the arrival times, required times, and slacks, a timing analysis engine must be employed. The most used technique to estimate the clock frequency of a given digital circuit is called static timing analysis (STA). The idea is to propagate the signals from timing startpoints to timing endpoints assuming pessimistic conditions for the late scenario and optimistic conditions for the early scenario (BHASKER; CHADHA, 2009).

Timing analysis tools generally transform the hypergraph  $G(V, \mathcal{N})$  into a directed acyclic graph (DAG) D(V, E) by mapping each hyperedge  $\mathcal{N}$  into a set of binary edges E. Then the DAG is partitioned into subgraphs representing each combinational block. Finally, the DAG is traversed in topological order<sup>6</sup> while arrival times are computed at each  $v_j \in V$ .

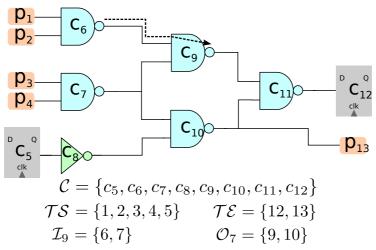

The boundaries of each combinational block are usually represented by two sets of integers, denoted as  $\mathcal{TS}$  and  $\mathcal{TE}$ , which identify each vertex producing a timing startpoint or consuming a timing endpoint, respectively. The index of a vertex serves as its actual identifier. Formally, given a subgraph  $(V_k, E_k)$  with  $V_k \subset V$  and  $E_k \subset E$  representing a combinational block k,  $\mathcal{TS}_k = \{i \mid i \text{ is integer and } v_i \in V_k \text{ produces a timing startpoint}\}$  and  $\mathcal{TE}_k = \{i \mid i \text{ is integer and } v_i \in V_k \text{ consumes a timing endpoint}\}$ . For simplicity, when referring to a given block, the index k is dropped in shorthand notation.

Timing analysis tools usually rely on the fanin and on the fanout of each vertex  $v_j \in V$  to determine arrival times. Let  $\mathcal{I}_j$  be the set of integers serving as identifiers for the vertices connected to its inputs, formally  $\mathcal{I}_j = \{i \mid i \text{ is integer and } v_i \in V \text{ produces an input for } v_j \in V\}$ . Let  $\mathcal{O}_j$  represent the set of integers serving as identifiers for the vertices connected to its output, formally  $\mathcal{O}_j = \{i \mid i \text{ is integer and } v_i \in V \text{ produces an output for } v_j \in V\}$ . Figure 17 presents a small circuit to illustrate the aforementioned concepts.

Let  $d_{i,j}^L$  and  $d_{i,j}^E$  denote the late and early values for the delay measured between the output of cell  $c_i$  and the output of cell  $c_j$  (e.g. late and early delays from  $c_6$ 's output and  $c_9$ 's output (dashed arrow in Figure 17) are denoted  $d_{6,9}^E$  and  $d_{6,9}^E$ , respectively). Given a combi-

$<sup>^5</sup>$ This is similar to the Critical Path Method used in project management (SAP-ATNEKAR, 2004).

<sup>&</sup>lt;sup>6</sup>Corresponds to the ordering where a node  $v_j$  is processed only after all its predecessor nodes have been processed.

Figure 17: Circuit example with timing analysis notation. A circuit example containing 5 timing startpoints, 8 standard cells, and 2 timing edpoints. The fanin set for  $c_9$  and the fanout set for  $c_7$  are also presented.

national block, late and early arrival times of each vertex  $v_j$ , denoted as  $a_j^L$  and  $a_j^E$ , can be recursively defined from its timing startpoints towards its timing endpoints, as follows:

$$a_{j}^{L} = \max_{i \in \mathcal{I}_{i}} (a_{i}^{L} + d_{i,j}^{L}), \qquad a_{j}^{E} = \min_{i \in \mathcal{I}_{i}} (a_{i}^{E} + d_{i,j}^{E})$$

(2.1)

The late (early) required time, denoted as  $r_j^L$  ( $r_j^E$ ), corresponds to the latest (earliest) time when the signal transition must reach each timing endpoint to ensure the target clock frequency. Given a combinational block, the required times can be recursively defined from its timing endpoints towards its timing startpoints, as follows:

$$r_j^L = \min_{k \in \mathcal{O}_j} (r_k^L - d_{j,k}^L), \qquad r_j^E = \max_{k \in \mathcal{O}_j} (r_k^E - d_{j,k}^E)$$

(2.2)

To evaluate how far a design is from the target clock frequency, late and early slacks are tracked at timing endpoints (SINHA et al., 2013), as follows:

$$slk_j^L = r_j^L - a_j^L, \quad slk_j^E = a_j^E - r_j^E, \ \forall j \in \mathcal{TE}$$

(2.3)

Figure 18 presents a small example of computing arrival times, required times, and slacks for both timing scenarios.

Timing optimization techniques such as incremental timing-driven placement and gate sizing, typically try to improve a timing metric known as worst negative slack (WNS). It can be defined, under late and early scenarios, as follows:

$$WNS^{L} = \min_{j \in \mathcal{T}\mathcal{E}} (0, slk_{j}^{L})$$

(2.4)

$$WNS^{L} = \min_{j \in \mathcal{T}\mathcal{E}}(0, slk_{j}^{L})$$

$$WNS^{E} = \min_{j \in \mathcal{T}\mathcal{E}}(0, slk_{j}^{E})$$

$$(2.4)$$

Note that WNS either captures the most severe violation (as a negative value corresponding to the timing endpoint with worst slack) or a non-violation (as a zero valued upper bound). For the example in Figure 18 (b),  $WNS^L = -5$  and  $WNS^E = 0$ .

Although the WNS metric represents timing violations on the worst path, a circuit may have several other near-critical paths violating the timing constraints. That is a why a second metric, called total negative slack (TNS), captures the criticality of other critical paths, as follows:

$$TNS^{L} = \sum_{j \in \mathcal{T}\mathcal{E}} \min(0, slk_{j}^{L})$$

(2.6)

$$TNS^{E} = \sum_{j \in \mathcal{T}\mathcal{E}} \min(0, slk_{j}^{E})$$

(2.7)

Note that the TNS adds up the impact of all violations into a single number. For the example in Figure 18 (b),  $TNS^L = -6$  and  $TNS^E = 0.$

# 2.2.3 Cell and Interconnection Modeling

The timing analysis of a circuit requires the modeling of standard cell and interconnection electrical behaviors. Next, the adopted cell and interconnection modeling are explained.

Figure 18: Small example of static timing analysis. (a) A circuit example containing 5 timing startpoints, 6 combinational gates, and 2 timing endpoints. (b) The DAG for circuit example and timing analysis considering late and early scenarios. The small table on the right-hand side defines late and early delays for the combinational gates. The example assumes that interconnections delays are zero,  $t_{su} = 1, t_h = 5$ and P = 7. The pairs  $(a^L, a^E)$  indicate the late and early arrival times obtained for each vertex. The arrival times for combinational gates are computed at their output pins. The example supposes that all timing startpoints have the same arrival times (2,1). The resulting values for required times  $(r^L \text{ and } r^E)$  and slacks  $(slk^L \text{ and } slk^E)$  are shown for each timing endpoint. Since setup and hold constraints only apply to  $v_{12}$  (which represents a register) but not to  $v_{13}$  (which represents a pad), the late required time of the former is one time unit less than the latter and the early required time of the former is 5 whereas it is zero for the latter. Note that the paths ending at both vertices  $v_{12}$  and  $v_{13}$ violate the late timing constraints (negative slacks), although the early time constraints are satisfied (positive slacks).

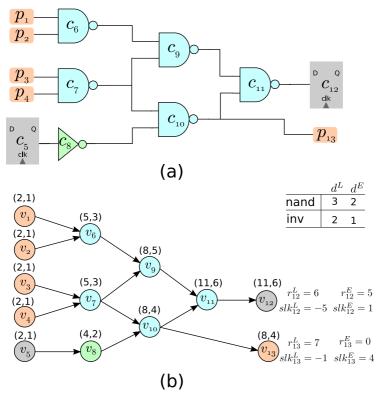

### 2.2.3.1 Cell Modeling and Concepts

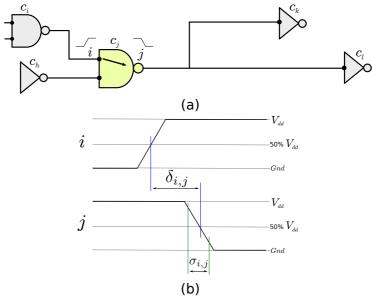

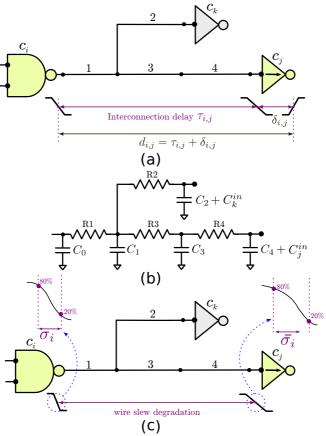

The main electrical characteristics of cells are explained with the aid of Figure 19. Assume that the output of a cell  $c_j$  is wired to the inputs of other cells, say  $c_k$  and  $c_l$ . Since the timing of an output signal depends on which input signal transition has been observed, timing is defined between a given input, say i, and the output, say j. This notion, known as timing arc, is illustrated in Figure 19 (a). The following electrical characteristics are defined for each timing arc:

Figure 19: Electrical characterization of a cell. (a) A subcircuit with emphasis on timing arc i, j of  $c_j$ . (b) Waveforms to illustrate the concepts of arc delay  $(\delta_{i,j})$  and arc slew  $(\sigma_{i,j})$ .

- arc delay of  $c_j \in C$  with respect to its input i, denoted as  $\delta_{i,j}$ , corresponds to the time difference between the instant that that input signal crosses 50% of  $V_{dd}$  and the instant that signal j crosses 50% of  $V_{dd}$ . Although separate rise and fall arc delays are considered, such detailing is omitted for clarity.