# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS - GRADUAÇÃO EM ENGENHARIA DE AUTOMAÇÃO E SISTEMAS

Renan Augusto Starke

## DESIGN AND EVALUATION OF A VLIW PROCESSOR FOR REAL-TIME SYSTEMS

Florianópolis 2016

#### Renan Augusto Starke

## DESIGN AND EVALUATION OF A VLIW PROCESSOR FOR REAL-TIME SYSTEMS

A Thesis submitted to the Automation and Systems Engineering Postgraduate Program in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Automation and Systems Engineering.

Supervisor: Rômulo Silva de Oliveira

Florianópolis 2016

#### Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Starke, Renan Augusto

Design and Evaluation of a VLIW Processor for Real-Time Systems / Renan Augusto Starke; orientador, Rômulo Silva de Oliveira - Florianópolis, SC, 2016. 204 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia de Automação e Sistemas.

Inclui referências

1. Engenharia de Automação e Sistemas. 2. Real time systems. 3. Very Long Instruction Word (VLIW) processor. 4. Worst-Case Execution Time (WCET) Analysis. I. Oliveira, Rômulo Silva de. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia de Automação e Sistemas. III. Título.

## DESIGN AND EVALUATION OF A VLIW PROCESSOR FOR REAL-TIME SYSTEMS

#### Renan Augusto Starke

This Thesis is hereby approved and recommended for acceptance in partial fulfillment of the requirements for the degree of "Doctor of philosophy in Automation and Systems Engineering."

| June 6th, 2016.                                                            |   |

|----------------------------------------------------------------------------|---|

| June oui, 2016.                                                            |   |

|                                                                            |   |

|                                                                            | _ |

| Prof. Rômulo Silva de Oliveira, Dr.<br>Supervisor                          |   |

|                                                                            |   |

| Prof. Daniel Coutinho, Dr.                                                 |   |

| Coordinator of the Automation and Systems Engineering Postgraduate Program |   |

| Examining Committee:                                                       |   |

|                                                                            | _ |

| Prof. Rômulo Silva de Oliveira, Dr. – UFSC<br>Chair                        |   |

|                                                                            |   |

| Prof. Anderson Luiz Fernandes Perez, Dr. – UFSC                            |   |

|                                                                            | _ |

| Prof. Joni da Silva Fraga, Dr. – UFSC                                      |   |

Prof. Rafael Rodrigues Obelheiro, Dr. – UDESC

Prof. Rodolfo Jardim de Azevedo, Dr. – UNICAMP

Prof. Werner Kraus Junior, Dr. – UFSC

Explanations exist: they have existed for all times, for there is always an easy solution to every problem – neat, plausible and wrong.

- H.L. Mencken, "The Divine Afflatus", in the New York Evening Mail, November 16, 1917

#### **ACKNOWLEDGEMENTS**

I thank to professor Rômulo Silva de Oliveira for his dedication, encouragement, patience and the great suggestions when the way seemed unclear.

I thank my family for their trust and support during the course. In particular I thank my parents allowing access to high quality education. A special thank to my future wife Allessa Mariá Maiochi who waited and supported me for these years.

I also thank to laboratory colleagues for friendship, help in corrections, sharing and improvement of ideas. A special thank to my friend Andreu Carminati who helped to make this work possible with the compiler back-end implementation, ideas and tips.

Finally thanks to CAPES for the financial support that enabled this work.

#### **ABSTRACT**

Nowadays, many real-time applications are very complex and as the complexity and the requirements of those applications become more demanding, more hardware processing capacity is necessary. The correct functioning of real-time systems depends not only on the logically correct response, but also on the time when it is produced. General purpose processor design fails to deliver analyzability due to their non-deterministic behavior caused by the use of cache memories, dynamic branch prediction, speculative execution and out-of-order pipelines. In this thesis, we design and evaluate the performance of VLIW (Very Long Instruction Word) architectures for real-time systems with an in-order pipeline considering WCET (Worst-case Execution Time) performance. Techniques on obtaining the WCET of VLIW machines are also considered and we make a quantification on how important are hardware techniques such as static branch prediction, predication, pipeline speed of complex operations such as memory access and multiplication for high-performance real-time systems. The memory hierarchy is out of scope of this thesis and we used a classic deterministic structure formed by a direct mapped instruction cache and a data scratchpad memory. A VLIW prototype was implemented in VHDL from scratch considering the HP VLIW ST231 ISA. We also show some compiler insights and we use a representative subset of the Mälardalen's WCET benchmarks for validation and performance quantification. Supporting our objective to investigate and evaluate hardware features which reconcile determinism and performance, we made the following contributions: design space investigation and evaluation regarding VLIW processors, complete WCET analysis for the proposed design, complete VHDL design and timing characterization, detailed branch architecture, low-overhead full-predication system for VLIW processors.

**Keywords**: Real time systems, Very Long Instruction Word (VLIW) processor, Worst-Case Execution Time (WCET) Analysis.

#### RESUMO EXPANDIDO

### CONSIDERAÇÕES SOBRE PROJETO DE PROCESSADORES VLIW PARA SISTEMAS DE TEMPO REAL

**Palavras-chave**: Sistemas de tempo real, processadores VLIW (*Very-Long Instruction Word*), análise de pior tempo de computação (WCET – *Worst-case Execution Time*)

#### Introdução

Atualmente, aplicações de tempo estão tornando-se cada vez mais complexas e, conforme os requisitos destes sistemas aumentam, maior é a demanda por capacidade de processamento. Contudo, o correto funcionamento destas aplicações não está em função somente da correta resposta lógica, mas também no tempo que ela é produzida.

Nos últimos anos, houve uma quantidade significativa de pesquisas voltadas a arquiteturas de processadores temporalmente previsíveis com o intuito de utilizá-los em sistemas de tempo real. Como o principal objetivo de projeto de processadores de propósito geral tem-se mantido na melhora do desempenho de caso médio, a utilização destes em sistemas de tempo real tornou-se consideravelmente complexa devido à necessidade de análises para obtenção de parâmetros temporais.

Sistemas de tempo real são geralmente modelados por um conjunto de tarefas onde cada uma possui seu pior tempo de execução (WCET – Worst-case Execution Time), período e prazo (deadline) e estes parâmetros são utilizados em testes de escalonabilidade formais. Em conjunto com um algoritmo de escalonamento de tarefas, é formado um problema de escalonabilidade onde o objetivo é verificar se todas as tarefas cumprem seus deadlines: o tempo de resposta de uma tarefa deve sempre ser menor ou igual ao seu respectivo deadline. Obter o pior tempo de computação tem se mostrado complexo e dependente de parâmetros relacionados ao hardware como arquitetura do processador e da memória. Obter o WCET eficientemente e com precisão é necessário tanto para o mais simples quanto ao mais complexo teste de escalonabilidade.

As principais abordagens para obter o WCET são medições, análises estáticas e análises híbridas. A prática mais comum na indústria é o uso de medições executando o sistema no hardware alvo. Nas análises estáticas, não há execução mas a estimação do WCET é realizada utilizando-se de um modelo matemático constituído pelo o binário da tarefa e características da plataforma alvo. No caso das análises híbridas, são combinadas análises estáticas com medições. Independentemente da abordagem, ferramentas de análise WCET fornecem uma estimativa do tempo de execução de um código que deverá ser igual ou maior que WCET real. Aplicações complexas são difíceis de analisar por qualquer abordagem (GUS-TAFSSON, 2008). Análises estáticas podem gerar problemas complexos não escaláveis geralmente relacionados ao *hardawre*, enquanto medições necessitam de casos de uso que não necessariamente produzem o WCET de uma aplicação. Para amenizar o problema relacionado a estimação do WCET, tem-se mostrado interesse em arquiteturas projetadas especificamente para sistemas de tempo real, como os trabalhos de (SCHOEBERL et al., 2011), (LIU et al., 2012) e (SCHOEBERL et al., 2015)

Nesta tese, investiga-se uma arquitetura de processador VLIW – Very-Long Instruction Word especificamente projetada para sistemas de tempo real considerando sua análise do pior tempo de computação (WCET - Worst-case Execution Time). Técnicas para obtenção do WCET para máquinas VLIW são consideradas e quantifica-se a importância de técnicas de hardware como previsor de fluxo estático, predicação, bem como velocidade do processador para instruções complexas como acesso a memória e multiplicação. A arquitetura de memória não faz parte do escopo deste trabalho e para tal utilizamos uma estrutura determinista formada por uma memória cache com mapeamento direto para instruções e uma memória de rascunho (scratchpad) para dados. Nós também consideramos a implementação em VHDL do protótipo para inferir suas características temporais mantendo compatibilidade com o conjunto de instruções (ISA) HP VLIW ST231. Em termos de avaliação, foi utilizado um conjunto representativo de código exemplos da Universidade de Mälardalen que é amplamente utilizado em avaliações de sistemas de tempo-real.

#### **Objetivos**

O objetivo desta tese é investigar características de arquitetura de processadores que levam a um projeto determinista mas também que consideram o desempenho de pior caso (redução do WCET). A tese a ser demonstrada é que é possível utilizar elementos de *hardware* que aumentam o desempenho mas que são previsíveis o suficiente para garantir uma análise estática eficiente e precisa. Para demonstrar previsibilidade, é interessante demonstrar as técnicas de análise envolvidas na obtenção de WCET de tarefas. Portanto, a construção de uma ferramenta de WCET assim como os aspectos envolvidos na modelagem do *hardware* também são assuntos cobertos neste trabalho.

Entre os elementos arquiteturais considerados, têm-se:

#### • Pipeline:

Pipeline é uma técnica que permite que operações complexas sejam organizadas em outras mais simples com o objetivo de aumentar desempenho. No caso de processadores deterministas, pipelines são necessários mas as instruções devem ser executadas em ordem. Pipelines com execução fora de ordem permitem um alto desempenho de caso médio mas prejudicam a análise de WCET devido a anomalias temporais (LUNDQVIST; STENSTROM, 1999).

#### • Paralelismo entre instruções:

Nos processadores modernos, o termo superescalar é utilizado quando mais de uma instrução é executada em cada estágio de *pipeline*. Este projeto supera a limitação de desempenho (*throughput*) de apenas uma instrução executada por ciclo de máquina. No caso de processadores para sistemas de tempo-real, a execução de múltiplas instruções por estágio de *pipeline* também pode ser utilizado utilizando um projeto *Very Long Instruction Word* (VLIW) (FISHER; FARABOSHI; YOUNG, 2005). Máquinas VLIW são mais adequadas para sistemas de tempo real pois o escalonamento de instruções é determinado pelo compilador e não em tempo de execução. Isso simplifica a análise estática, pois escalonamento dinâmico de instruções

não precisa ser modelado.

#### • Primeiro nível do sub-sistema de memória:

O sub-sistema de memória é um assunto relevante em vários trabalhos (REINEKE et al., 2011). Há diversas abordagens e algumas delas requerem modificações complexas no compilador ou no *hardware* (SCHOEBERL et al., 2011). Neste trabalho, nós tratamos da previsibilidade do sub-sistema de memória utilizando uma memória cache de instruções com mapeamento direto bem como uma memória de rascunho (*scratchpad*) para dados. Memórias de rascunho são similares às caches mas seu conteúdo é gerenciado explicitamente pelo *software*.

#### • Previsão de fluxo:

Modificações no controle de fluxo de um programa são realizadas por instruções especiais chamadas *branches*. Elas são utilizadas para estruturas com condicionamentos (*if*), laços (*for* e *while*) e geralmente degradam o desempenho do *pipeline* devido a ciclos de paradas (*stalls*). Uma maneira de reduzir esta limitação é o uso de previsores de fluxo. Há os previsores dinâmicos e os estáticos. Os dinâmicos prejudicam a previsibilidade enquanto os estáticos possuem características interessantes para sistemas de tempo real (BURGUI-ERE; ROCHANGE; SAINRAT, 2005). Nós consideraremos os previsores estáticos, demonstrando sua importância em termos de desempenho bem como a metodologia para considerá-los na análise WCET.

#### • Predicação:

Predicação é uma técnica na qual instruções são condicionalmente executadas baseando-se em um registrador *Booleano*. É diferente dos *branches* pois não há qualquer modificação no fluxo do programa para ignorar instruções. Há dois tipos de predicação: completa e parcial. Predicação completa permite que instruções sejam executadas ou ignoradas diretamente conforme o valor de um registrador *Booleano* (esta predicação é comumente empregada nos processadores ARM). No caso da predicação parcial, instruções não

são ignoradas mas dois valores podem ser selecionados utilizando um tipo especial de instrução (*select*). Predicação é uma técnica importante para reduzir caminhos em um programa induzindo o paradigma da programação de caminho único (*Single-path programming paradigm*) (PUSCHNER, 2005). Nós suportamos ambos os tipos de predicação e a versão completa é reestruturada para reduzir o impacto no *hardware*.

#### Instruções aritméticas complexas:

Há várias instruções aritméticas complexas como divisão e multiplicação que diminuem o desempenho do processador. Frequentemente estas instruções são suportadas apenas por *software*, principalmente a divisão. Neste trabalho, tanto divisão quanto multiplicação por *hardware* são implementadas para que tenham previsibilidade independentemente de seus parâmetros de entrada.

#### Contribuições

Dentre as contribuições deste trabalho, nós podemos citar: investigação sobre o espaço de projeto, avaliação de desempenho através de conjunto representativo de códigos exemplos, detalhamento completo da análise estática, implementação VHDL, caracterização temporal de cada componente de *hardware*, detalhamento da arquitetura de controle de fluxo e um sistema de predicação completo de baixo impacto para processadores VLIW.

Realizou-se uma avaliação extensiva das técnicas apontadas acima considerando os benefícios em termos de desempenho de pior caso. Notou-se que uma avaliação tão ampla nunca havia sido considerada nos trabalhos relacionados pois nestes são focados objetivos específicos como subsistema de memória, *multi-threading* ou *multi-core*. Nossa avaliação pode guiar novas linhas de pesquisas relacionadas com sistemas de tempo real.

Foram também abordadas todas as análises necessárias para estimar o WCET de programas compilados para o processador considerado neste trabalho, incluindo *cache*, modelagem do *pipeline* e busca do pior cami-

nho do programa. Uma descrição completa de uma análise WCET para processadores VLIW também não foi abordada nos trabalhos relacionados.

Todos os detalhes da arquitetura de controle de fluxo são descritos, incluindo a metodologia para modelagem durante a análise WCET. Também ampliamos o ISA para suportar previsão de desvio estático, bem como os benefícios de usar ou não esta tecnologia em sistemas de tempo real.

Quanto ao sistema de predicação completo, foi proposto um sistema que adiciona baixa sobrecarga nos caminhos de dados de *hardware* e na sua lógica de atalhos (*forwarding logic*). O sistema proposto diminui o uso de instruções de controle de fluxo, bem como permite a utilização de técnicas de desenrolamento de laços (*loop unrolling*). No entanto, a predicação sozinha não é suficiente para aumentar o desempenho e previsibilidade e seu uso pode aumentar o tempo de execução (WCET). Devido a isso, propõe-se o uso de uma abordagem híbrida com suporte de *hardware* para predicação e previsão estática de fluxo. Isto leva a uma redução significativa do pior tempo de computação e permite otimizações durante a compilação que pode selecionar a técnica apropriada para cada estrutura.

#### Conclusão

Neste trabalho considerou-se elementos arquiteturais de processadores que beneficiam a análise estática mas também contribuem para o aumento do desempenho, principalmente para o pior caso de execução.

Como sistemas modernos impõem maiores requisitos funcionais, processadores de maior desempenho são necessários. Portanto, é necessário analisar os pontos fortes das técnicas de hardware usadas em processadores modernos, por exemplo paralelismo temporal e espacial na execução de instruções, previsão de desvios e predição, e para adaptá-los para aplicações em tempo real. Algumas destas técnicas exigem modificações, devido à alta complexidade do hardware, enquanto outros precisam de um comportamento temporal bem definido. Para atingir esses objeti-

vos, foram propostas novas abordagens, a fim de melhorar a eficiência e a escalabilidade da análise temporal, especialmente a análise de tempo de execução do pior caso. Mostrou-se que o projeto de processadores deve aumentar o nível de importância do determinismo.

Foi possível verificar através dos testes de desempenho que as técnicas abordadas aumentaram o desempenho em todos os programas considerados. Além disso, mostrou-se detalhadamente as técnicas necessárias para realizar análise estática obtendo assim o WCET para todos programas testados.

A implementação VHDL do processador mostrou-se desafiadora mas contribuiu significativamente para a caracterização temporal de cada elemento de *hardware*.

#### LIST OF FIGURES

| Figure 1 – The worst-case execution time problem                           | 2  |

|----------------------------------------------------------------------------|----|

| Figure 2 – Example of timing anomaly                                       | 4  |

| Figure 3 – Generic 5-stage pipeline representation                         | 9  |

| Figure 4 – Generic 5-stage pipeline with forward paths 5                   | 1  |

| Figure 5 – Diversified pipeline example 5                                  | 3  |

| Figure 6 – Example of a dynamic pipeline                                   | 4  |

| Figure 7 – Example of a two-bit branch predictor (SHEN et al.,             |    |

| 2005)                                                                      | 7  |

| Figure 8 – Instruction bundle decoding example 8                           | 7  |

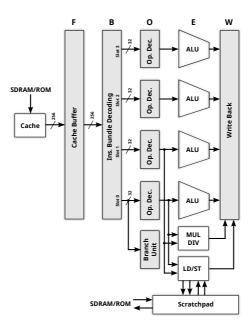

| Figure 9 - VLIW processor overview 9                                       | 0  |

| Figure 10 – Detail of execution units stages 9                             | 2  |

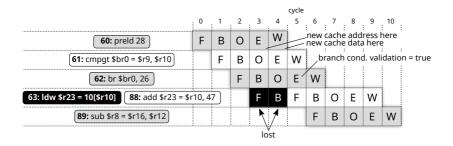

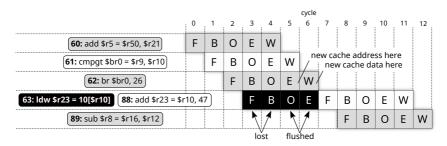

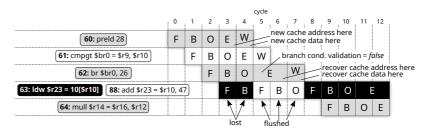

| Figure 11 – Pipeline behavior of a "not taken" branch 9                    | 8  |

| Figure 12 – Pipeline behavior of a "taken" directed branch 10              | 0  |

| Figure 13 – Pipeline behavior of a "taken" branch without direction        |    |

| change or other direct control flow operations 10                          | 0  |

| Figure 14 – Pipeline behavior of a mispredicted direction 10               | 1  |

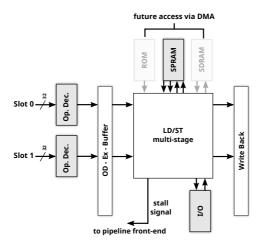

| Figure 15 – Memory unit logic diagram                                      | 14 |

| Figure 16 – VLIW processor overview (reproduced from Figure 9). 11         | 2  |

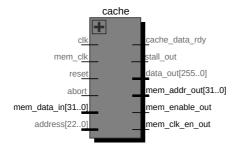

| Figure 17 – Cache VHDL component                                           | 2  |

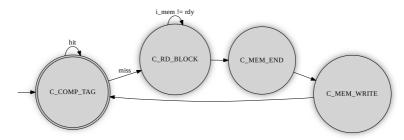

| Figure 18 – Cache states and behavior                                      | 3  |

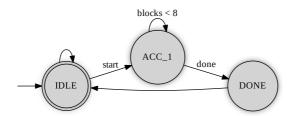

| Figure 19 – ROM controller behavior                                        | 4  |

| Figure 20 – Instruction bundle decoder VHDL component                      | 5  |

| Figure 21 – Cache buffer component                                         | 6  |

| Figure 22 – Front-end control behavior                                     | 8  |

| Figure 23 – Wave form of the pipeline front-end                            | 9  |

| Figure 24 – Control flow unit component                                    | 1  |

| Figure 25 – Logic diagram for one read port                                | 4  |

| Figure 26 – Pipeline inter-stage responsible for the predication logic. 12 | 6  |

| Figure 27 – Pipeline behavior of interlock RAW dependency 12               | 8. |

| Figure 28 – Arithmetic and logic unit diagram                              | 0  |

| Figure 29 – Forward logic multiplexers for one ALU                         | 0  |

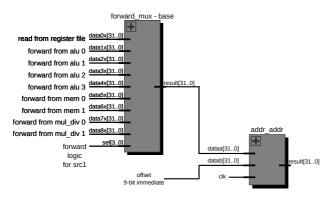

| Figure 30 – Memory unit states and behavior                                | 2  |

| Figure 31 – | Memory effective address calculation with forward 133             |

|-------------|-------------------------------------------------------------------|

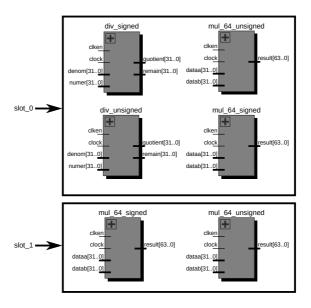

| Figure 32 – | Multiplication and division unit components per slot 135          |

| Figure 33 – | Multiplication and division unit states and behavior 136          |

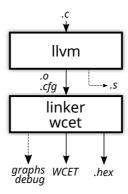

| Figure 34 – | Data-flow between the compiler and WCET/linker $\ensuremath{141}$ |

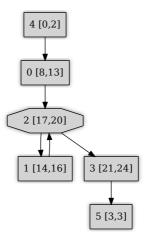

| Figure 35 – | Control flow graph example                                        |

| Figure 36 – | Cache abstract reachable state example 148                        |

| Figure 37 – | CONFLICT classification example                                   |

| Figure 38 – | Example of timing composition of two successive (lin-             |

|             | ear addresses) basic blocks                                       |

| Figure 39 – | Example of a C program and its control-flow graph 157             |

| Figure 40 – | Multigraph of the example                                         |

| Figure 41 – | WCET final result of example of Figure 39 162                     |

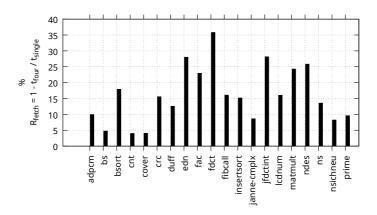

| Figure 42 – | WCET reduction between single-issue and four-issue 170            |

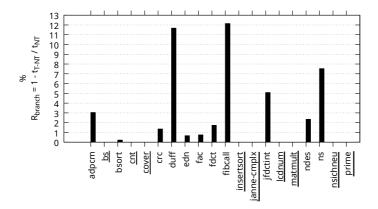

| Figure 43 – | WCET reduction on using branch prediction. Under-                 |

|             | lined ones have null reduction                                    |

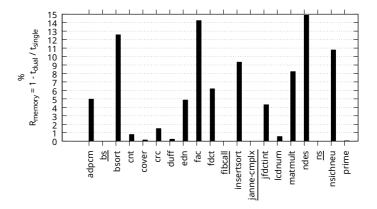

| Figure 44 – | WCET reduction with dual-ported scratchpad. Under-                |

|             | lined ones have null reduction                                    |

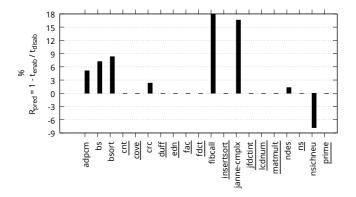

| Figure 45 – | WCET reduction on using predication 174                           |

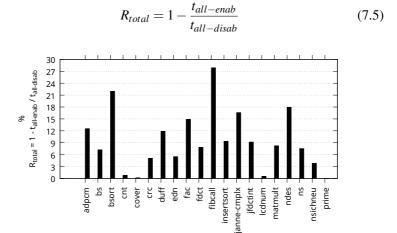

| Figure 46 – | Total WCET reduction                                              |

#### LIST OF TABLES

| Table 1 – Arithmetic instructions specification                       |

|-----------------------------------------------------------------------|

| Table 2 – Memory instructions specification                           |

| Table 3 - Control flow instructions specifications 47                 |

| Table 4 – Maximum necessary stall cycles for dependency reso-         |

| lution                                                                |

| Table 5 - Maximum necessary stall cycles for dependency reso-         |

| lution with forward paths                                             |

| Table 6 - Basic differences between VLIW and Superscalar designs 55   |

| Table 7 - Comparison between branch code, full and partial pred-      |

| ication (HP ST200 ISA – Apendix A) 59                                 |

| Table 8 - Comparison of techniques for general-purpose and real-      |

| time processors                                                       |

| Table 9 - Summary of related project objectives                       |

| Table 10 – Operation encoding                                         |

| Table 11 – Example of simple true mode predication system 95          |

| Table 12 – Example of complete mode predication system 96             |

| Table 13 – Example of nested if-then-else with full and partial pred- |

| ication systems                                                       |

| Table 14 – Example of data dependency between operations 106          |

| Table 15 – Operation packing considering anti-dependencies, and       |

| ignoring them                                                         |

| Table 16 – Instruction alignment in basic blocks                      |

| Table 17 – Pipeline features comparison                               |

| Table 18 – Cache address fields                                       |

| Table 19 – Example of interlock cases                                 |

| Table 20 – FPGA resources usage (Cyclone IV GX – EP4CGX15             |

| 0DF31C7). Resource usage reported by Quartus II 64-                   |

| bit V 15.0.0 Build 145 WEB Edition                                    |

| Table 21 – Processor instruction timing                               |

| Table 22 – Additional time for multicycle instruction timing 153      |

| Table 23 – Modeling factor for each type of transition flow 155       |

| Table 24 - Objective function modeling using Language MathProg. 156   |

| Table 25 – Control-flow conservation restrictions using language |

|------------------------------------------------------------------|

| MathProg                                                         |

| Table 26 – Loop restrictions using language MathProg 159         |

| Table 27 - Conservation restrictions using language MathProg 159 |

| Table 28 – Cache restrictions using language MathProg 162        |

| Table 29 – Mälardalen WCET benchmarks (GUSTAFSSON et al.,        |

| 2010)                                                            |

| Table 30 – Execution and worst-case performance comparing VEX    |

| and our prototype and WCET absolute values. WCET                 |

| and Exec. time in cycles. IPC is Instructions per cycle . 168    |

| Table 31 – List of operation operands                            |

| Table 32 – List of supported operations                          |

|                                                                  |

#### **CONTENTS**

| 1     | INTRODUCTION 31                       |

|-------|---------------------------------------|

| 1.1   | Basic concepts and motivation         |

| 1.1.1 | Timing anomalies                      |

| 1.1.2 | Timing predictability                 |

| 1.1.3 | Timing composability                  |

| 1.2   | Thesis objective                      |

| 1.3   | Contributions                         |

| 1.4   | Text organization 41                  |

| 2     | PROCESSORS AND PREDICTABILITY CONSID- |

|       | <b>ERATIONS</b>                       |

| 2.1   | Pipeline principles                   |

| 2.1.1 | Minimizing pipeline stalls 47         |

| 2.2   | Multiple instruction fetching         |

| 2.2.1 | Out-of-order execution                |

| 2.2.2 | In-order execution                    |

| 2.3   | Branch prediction                     |

| 2.4   | Predication                           |

| 2.5   | Cache memories                        |

| 2.6   | Scratchpad Memory 61                  |

| 2.7   | Chip Multithreading 62                |

| 2.8   | Chip Multiprocessing 63               |

| 2.9   | <b>Summary</b>                        |

| 3     | RELATED WORK 67                       |

| 3.1   | The Komodo approach 67                |

| 3.1.1 | Real-time jamuth                      |

| 3.2   | The JOP Java processor 69             |

| 3.3   | The MCGREP processor                  |

| 3.4   | The PRET architecture 71              |

| 3.5   | The Patmos approach                   |

| 3.6   | The CarCore processor                 |

| 3.7     | Multicore solutions                                      |

|---------|----------------------------------------------------------|

| 3.7.1   | The Merasa project                                       |

| 3.7.2   | The T-CREST project                                      |

| 3.8     | <b>Summary</b>                                           |

| 4       | THESIS RATIONALE AND DESIGN DECISIONS 79                 |

| 4.1     | Target systems and requirements 80                       |

| 4.2     | Thesis Objective 81                                      |

| 4.3     | Architecture                                             |

| 4.4     | Design decisions 85                                      |

| 4.4.1   | Instruction set and encoding 85                          |

| 4.4.1.1 | Instruction bundle encoding 85                           |

| 4.4.1.2 | Operation encoding                                       |

| 4.4.2   | Processor pipeline                                       |

| 4.4.3   | Predication                                              |

| 4.4.4   | Branch prediction                                        |

| 4.4.5   | First level of the memory subsystem                      |

| 4.4.5.1 | Instruction cache                                        |

| 4.4.5.2 | Data memory interface                                    |

| 4.4.6   | Compiler support                                         |

| 4.5     | Summary                                                  |

| 5       | VHDL IMPLEMENTATION AND TIMING CHAR-                     |

|         | ACTERISTICS                                              |

| 5.1     | Instruction cache                                        |

| 5.2     | Pipeline front-end                                       |

| 5.3     | The control-flow system                                  |

| 5.4     | <b>Register files</b>                                    |

| 5.5     | Predication support                                      |

| 5.6     | Pipeline interlock                                       |

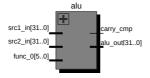

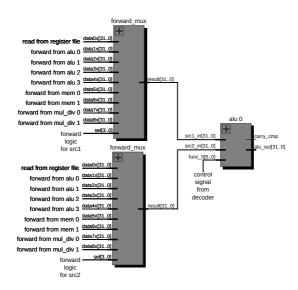

| 5.7     | Arithmetic and Logic units 129                           |

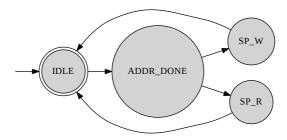

| 5.8     | Data memory interface                                    |

| 5.9     | Multiplication and division unit                         |

| 5.10    | Timing characteristics and FPGA resource utilization 137 |

| 5.11       | Summary                                             | 137 |

|------------|-----------------------------------------------------|-----|

| 6          | WORST-CASE EXECUTION TIME ANALYSIS .                | 141 |

| 6.1        | Basic concepts                                      | 142 |

| <b>6.2</b> | Instruction cache analysis                          | 145 |

| 6.2.1      | Reachable and effective abstract state              | 146 |

| 6.2.2      | Cache accesses classification                       | 149 |

| 6.3        | Pipeline modeling                                   | 150 |

| 6.4        | Worst-case path search                              | 154 |

| 6.4.1      | ILP Constraints                                     | 157 |

| 6.5        | Summary                                             | 163 |

| 7          | EVALUATION                                          | 165 |

| 7.1        | Impact of the compiler on the performance           | 167 |

| 7.2        | Use of processors with wider fetch                  | 169 |

| 7.3        | Use of "taken"/"not taken" static branch prediction | 171 |

| 7.4        | Reducing execution stage overhead                   | 172 |

| 7.5        | <b>Predication</b>                                  | 173 |

| <b>7.6</b> | Overall reduction and impact on WCET calculation    | 174 |

| 7.7        | Contributions to the state of the art               | 176 |

| 8          | FINAL REMARKS                                       | 179 |

| 8.1        | <b>Publications</b>                                 | 183 |

| 8.2        | Suggestions of future work                          | 184 |

|            | BIBLIOGRAPHY                                        | 187 |

|            | APPENDIX                                            | 195 |

|            | APPENDIX A – LIST OF SUPPORTED OPERATIONS           | 197 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ALU Arithmetic Logic Unit

BCET Best-Case Execution Time

CISC Complex Instruction Set Computing

FPGA Field-Programmable Gate Array

FSM Finite State Machine

ISA Instruction Set Architecture

LLVM Low Level Virtual Machine compiler infrastructure

LVT Live Value Table

NOP No Operation

RAM Random Access Memory

RISC Reduced Instruction Set Computing

ROM Read-Only Memory

SRAM Static Random Access Memory

VEX VLIW Example

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLIW Very Long Instruction Word

WCET Worst-Case Execution Time

#### LIST OF SYMBOLS

CFG Control-Flow Graph

$d_{i_{-i}}$  Edge from node j to i

$\delta$  Transition-flow modeling factor

E Edge set of a graph

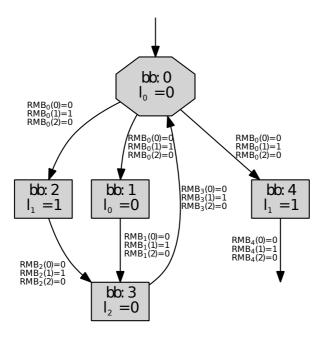

$EMB_i(c)$  Effective Memory Block set of a basic block i and

cache line c

G Graph

$n_c$  Total number of cache misses inside a basic block

$n_m$  Total number of high latency memory access inside

a basic block

$RMB_i(c)$  Reaching Memory Block set of a basic block i and

$cache\ line\ c$

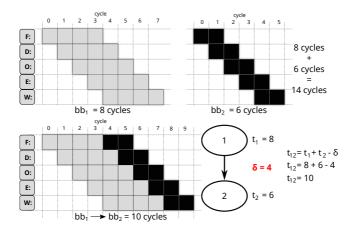

$t_{bb}$  Basic-block time

$t_c$  Cache-miss time

$t_{i,j}$  Time of basic block i when executing from predeces-

sor j

$t_m$  High-latency memory access time

$t_p$  Pipeline modeling time

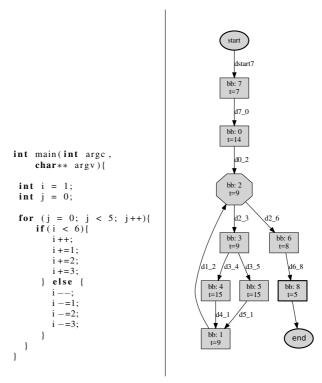

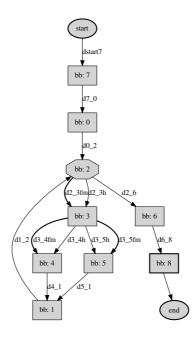

$t_i$  Time of basic block i

V Vertex set of a graph

v Vertex of a graph

$x_i$  Total number of times a basic block executes

#### 1 INTRODUCTION

Real-time computer systems are defined as those subject to temporal requirements. They are relevant for diverse applications such as aviation, spacecrafts, automotive electronics and diverse industrial plants. Future real-time applications will require processors with higher performance and they must satisfy strict timing constraints for their correct functioning.

General-purpose processors usually are designed to perform the common case fast and the uncommon case correct (SCHOEBERL, 2009b). This design philosophy leads to machines optimized for average-case performance, which is not necessarily suitable for real-time systems. In order to verify strict timing constraints, we need to obtain the computation time or Worst-Case Execution Time (WCET) of every task of the systems. It has a considerable complexity and it depends on hardware features such as processor and memory architecture.

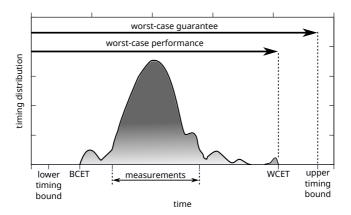

The Worst-case execution time problem, well described in Wilhelm et al. (2008), can be summarized by Figure 1. It is a timing distribution of the possible application execution time. There are two well defined limits: the BCET (Best-case execution time) and the WCET. The greater the difference between them, the worst is the predictability of a system. Since there is hardware complexity in modern systems, the BCET and the WCET cannot be calculated precisely, giving us the lower and the upper timing bounds. There is also a common industry practice of making measurements to obtain the system execution time. Measurements are generally not safe for strict timing constrained systems.

Modern processors use pipeline, various levels of data and instruction caches, dynamic branch prediction, out-of-order and speculative execution and fined-grained multithreading (instructions of various threads are dynamically executed in the processor pipeline). It can be incredibly difficult to model the software timing behavior when executing on a processor which uses such techniques for WCET timing analysis. The purpose of such timing analysis is to provide a safe worst-

Figure 1 – The worst-case execution time problem (WILHELM et al., 2008).

case execution time bound but it should not be extremely pessimistic for practical use.

Future real-time systems need processors designed for predictability instead of investing a lot of effort in temporal analysis (SCHOE-BERL, 2009b), (EDWARDS; LEE, 2007), (SCHOEBERL et al., 2011). But predictability alone is not enough. In such case, we would be employing 1980's processors where instruction timing is entirely known in datasheets. Real-time processors should have predictability and still a reasonable WCET performance. The purpose of a real-time architecture is to increase the worst-case performance (decrease the WCET) and simplify system analysis. This is the object of study of this thesis.

#### 1.1 BASIC CONCEPTS AND MOTIVATION

Real-time systems are classified considering the criticality of their timing requirements. There are *soft real-time systems* and *hard real-time systems* (LIU, 2000). If timing requirements are not completely met in soft real-time systems, the quality of service is jeopardized like video streaming for instance. For hard real-time systems, timing requirements must always be met. Those systems are found

in critical applications like aviation or space systems where temporal failures could lead to catastrophic consequences.

Real-time systems are modeled by tasks which are abstractions of works competing for resources. Tasks are comprised by timing parameters like WCET (C), maximum activation frequency or period (T) and deadline (D). The feasibility of a system is verified through schedulability analysis where it is ensured that all deadlines are respected. There is a lot of scheduling approaches for real-time systems (DAVIS; BURNS, 2011) and knowledge of the tasks WCET is always a concern.

The importance of obtaining the WCET of each task for system analysis is not a new problem. The question is how to estimate this fundamental parameter for systems where they are not only restricted to strict timing constraints but reasonable WCET performance is also required. This is the main motivation of this work where we will investigate processor architecture features capable of guaranteeing timing predictability, timing composability and increasing WCET performance.

#### 1.1.1 Timing anomalies

The term anomaly denotes a deviation of the expected behavior from the real behavior. A timing anomaly is the unexpected deviation of real hardware behavior compared with the model used during temporal analysis (WENZEL et al., 2005). Predictions from models become wrong and this could lead to erroneous calculation results by WCET analysis methods. Thus, the concept of timing anomalies rather relates to WCET analysis and does not denote malicious behavior during execution.

WCET analysis is commonly performed in many phases. One phase is responsible for the processor hardware modeling and it computes upper bounds for program code snippets called basic blocks. The timing of each block is usually calculated independently from the others and it must consider an initial state. Due to lack of state information (the processor model may contain simplifications), it is assumed the worst behavior of hardware components (e.g. cache misses). Due to

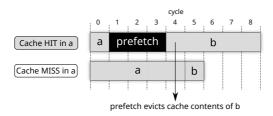

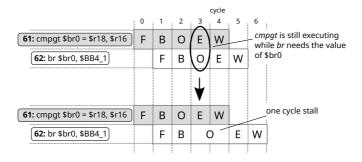

timing anomalies, assuming local worst case not necessarily means that the worst computation time is calculated. Figure 2 illustrates an example of timing anomaly. A cache hit in code snippet "a" triggers a prefetch. This prefetch evicts the contents of snippet "b" and the execution of  $a \to b$  takes 8 cycles. On the other side, if there is a miss in "a", there is no eviction of "b" and the execution of  $a \to b$  takes 5 cycles. This simple example demonstrates that local worst case of "a" does not necessarily produces the global worst case of  $a \to b$  execution due to a simple 3-cycle prefetch.

Figure 2 – Example of timing anomaly. Adapted from (WENZEL et al., 2005).

Timing anomalies are common for dynamic scheduling in outof-order processors (LUNDQVIST; STENSTROM, 1999). There are methods to analyze this type of architecture but usually they lead to overestimations or extremely complex approaches. Sometimes processor features (like dynamic branch prediction) must be disabled to guarantee a feasible WCET calculation.

#### 1.1.2 Timing predictability

A real-time system is not necessarily a high-performance system. A common error is to assume that a task has to run on a fast processor to meet its deadline. Fast processors usually improve average-case performance but can easily jeopardize the WCET analysis due to predictability issues.

To make sure that all tasks of the system meet their respective deadlines, it is necessary to determine the WCET of each one. This is possible if the hardware is time predictable or time analyzable. This two concepts are formalized in (GRUND; REINEKE; WILHELM, 2011). Predictability is not a Boolean property. It should be expressed by ranges allowing the comparison of systems, i.e., system X is more predictable than Y. Moreover it considers some level of accuracy and the maximum level is obtained when the system can be exactly predicted. Analyzability is how the system timing is modeled and it indicates the capacity of this modeling to predict timing properties.

There are other predictability definitions as the one described in (THIELE; WILHELM, 2004). They use the difference between the real (exact) WCET and the estimated upper bound. Later, in (KIRNER; PUSCHNER, 2010), they used the range between real BCET and real WCET where a lower range implies a better predictability and BCET equals to WCET is the maximum achievable predictability.

Predictability definitions/quantifications that use exact values of WCET/BCET may be impractical because they actually cannot be known, only estimated (SCHOEBERL, 2012). Systems should be compared considering three basic aspects: hardware, compiler and WCET analysis tool. The relevance of two of them can be characterized as follows. A task  $\tau$  has 1000 WCET cycles running on processor A, but 800 WCET cycles running on processor B (considering hypothetically both exact WCET values). Clearly, if we know those exact WCET values, processor B is better than A. Unfortunately, the WCET estimation is performed by a tool  $S_a$  for processor A and another tool  $S_b$  for processor B and their estimated upper bounds are 1100 cycles and 1300 cycles for A and B respectively. Now processor A is better. If predictability is estimated by  $\frac{WCET\ real}{WCET\ bound}$  for instance,  $P_A=0.91$  and  $P_B=0.61, A$  is more predictable than B and the tool  $S_a$  is also better. An efficiency problem arises if tool  $S_a$  takes one day and tool  $S_b$  takes minutes to estimate the WCET of task  $\tau$ .

As we can see, the notion of predictability should capture whether a specified property of a system can be predicted by an optimal analysis and to what level of precision (GRUND; REINEKE; WILHELM, 2011)

## 1.1.3 Timing composabilty

The complexity and the level of the requirements of real-time systems are reasonable nowadays. It is necessary to analyse the system to verify if timing requirements are met. But as described in (PUSCHNER; KIRNER; PETTIT, 2009), there is a lack of methods and tools to effectively reason about the timing of software. It is difficult for real-time software systems to be constructed hierarchically from components while still guaranteeing timing properties. To achieve a hierarchical construction, system components should be both composable and compositional from the timing perspective. Composability focuses on preservation of properties of an individual component when it is integrated in an application and compositionality is the ability of deducing global properties of the composed system from properties of its constituent modules (MARTÍNEZ; CUEVAS; DRAKE, 2012). Besides compositionality and composability, other properties should be present (PUSCHNER; KIRNER; PETTIT, 2009) to achieve a composable timing analysis: support for hierarchical development process, predictability, scalability and performance.

Most hardware architectures used today can not provide the properties listed by (PUSCHNER; KIRNER; PETTIT, 2009). Regarding composability, real-time tasks executing on the same hardware compete for resources whose access times are state-dependent such as data cache memories and branch buffers (used in branch prediction). The state of these resources depends on the data addresses and on the access history. We can see that state depends on spatial and temporal aspects and, of course, the update strategy because both cache and branch buffers have space limitations. The use of those hardware mechanisms degrade composability because the property of an individual module or task is not preserved when it is integrated with other tasks. The lack of composability when using branch prediction and data cache memories degrades scalability as well because branch prediction interferes with cache contents. WCET analysis must consider both branch directions when the analysis cannot anticipate the outcome

of the prediction.

Composability and predictability are also greatly affected in the presence of timing anomalies. Timing anomalies related to WCET analyses were first described by (LUNDQVIST; STENSTROM, 1999). A timing anomaly is a situation where the local worst case does not contribute to the global worst case, i.e., a cache miss, though increasing the execution time, results in shorter global execution time. The first condition to avoid timing anomalies is the use of in-order resources (LUNDQVIST; STENSTROM, 1999) what is not common in today hardware architectures. Timing anomalies jeopardize the composability because we cannot divide WCET calculation in subproblems. Predictability is also affected because simplifications on the analyses will not produce results with a reasonable accuracy margin.

In order to guarantee a composable timing analysis, state-of-the-art processor technologies such as dynamic branch prediction and cache memories with out-of-order pipelines should be avoided. Yet, as stated by (PUSCHNER; KIRNER; PETTIT, 2009), strategies adopted in real-time architectures should not lead to significant performance losses when compared to state-of-the-art technologies.

### 1.2 THESIS OBJECTIVE

The objective of this thesis is to investigate various processor architecture features that lead to a predictable design with reasonable WCET performance. The thesis to be demonstrated is that it is possible to assemble together hardware elements that increase performance but are predictable enough to ensure efficient and precise analyses. As described in the previous section, one of the first steps to demonstrate predictability is by obtaining the WCET. The construction of a WCET analysis tool as well as aspects involved with the hardware are also subjects of this work.

Among the architectural elements that are covered, we have:

## • Processor pipeline:

Pipelining is a technique where complex operations are organized into sequential simpler ones to increase throughput. In the case of predictable processor design, pipelines are necessary but instructions should be executed in-order. Pipelines with out-of-order execution allow high average-case performance but jeopardize WCET analysis due to timing anomalies (LUNDQVIST; STENSTROM, 1999).

## • Instruction parallelism:

In modern processor design, the concept of superscalar is extensively used where more than one instruction is executed in each pipeline stage. This design overcomes the limitation of standard pipelines where the maximum throughput is one instruction per cycle. In the case of real-time processors, multiple instructions could also be executed in each pipeline stage using the Very Long Instruction Word (VLIW) design philosophy (FISHER; FARA-BOSHI; YOUNG, 2005). VLIW machines are better for real-time systems because instruction scheduling is fixed and defined offline during compilation time and, that enhances the analyzability. No hardware for instruction scheduling have to be modeled in VLIW design.

## • First level of the memory subsystem:

Memory subsystems designed for real-time systems are the subject of various recent works (REINEKE et al., 2011). There are several approaches and some of them require complex modifications in the compiler and/or overload the hardware (SCHOE-BERL et al., 2011). In this work, we will address the memory predictability issues using a direct-mapped instruction cache and a scratchpad memory for data. Scratchpad memories are similar to caches but their contents must be managed explicitly by software.

## • Branch prediction:

Branches are instructions that perform conditional control-flow modifications. They are used for *if*, *for* and *while* structures and they usually decrease pipeline performance adding stall cycles to the pipeline. One way to overcome this limitation is the use of branch prediction. There are dynamic branch predictions and static branch predictions. The use of dynamic branch predictions jeopardizes predictability and the static ones provide interesting WCET performance (BURGUIERE; ROCHANGE; SAINRAT, 2005). We support static branch prediction demonstrating its importance in terms of performance and we provide methods for correct WCET analyzability.

### • Predication:

Predication is a technique where instructions are conditionally executed based on a Boolean register. It is different from branches because there is not any control flow modification to execute or ignore instructions. There are two types of predication: partial and full. Full predication allows instructions to be executed or ignored directly based on a Boolean register (this type of predication is common in ARM architectures). In case of partial predication, instructions cannot be ignored through a Boolean operator but two values can be selected using special *select* instructions. Predication is an important technique to reduce program paths through inducing to the single-path programming paradigm (PUSCHNER, 2005). We support both partial and full predication but the latter is simplified to improve WCET analysis without jeopardizing performance.

# • Complex arithmetic instructions:

There are complex arithmetic instructions like division and multiplication that impose considerable overhead to the processor pipeline. Frequently, those instructions are only supported via software, mainly division. In this work we support both hard-

ware division and multiplication and they are implemented to have constant timing independently of their input parameters.

We conduct a study of the impact on the WCET performance of those processor features that are typically disabled or not fully explored in real-time applications. Such features include the use of static scheduling VLIW processor with wide fetch, the importance of static branch prediction, the performance of complex instructions (memory, multiplications, division) and the use of predication.

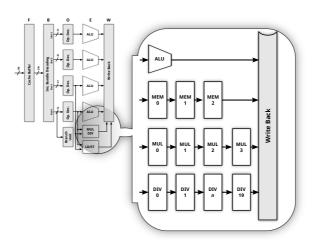

Increasing the performance of real-time processors while preserving analyzability is a relevant subject. For that purpose, we analyze the WCET performance of the deterministic four-issue Very Long Instruction Word (VLIW) processor prototype describing its features and its timing characteristics. This prototype is implemented in VHDL using an Altera Cyclone IV GX (EP4CGX150DF31C7) in a DE2i-150 development board.

Besides the VHDL prototype, there are other products of this thesis like the implementation of the hardware modeling of the WCET analysis tool and cycle accurate software simulator. Both WCET analysis tool and the simulator are written in C++. In order to have a compiler for the architecture and to provide a customizable environment to research real-time compiler capabilities, a new code generator back-end for LLVM (LATTNER; ADVE, 2004) was implemented but it is out of the scope of this thesis.

In terms of test cases, we used representative examples of Mälardalen WCET benchmarks (GUSTAFSSON et al., 2010) which are commonly used for WCET evaluations.

### 1.3 CONTRIBUTIONS

Regarding our main contributions to real-time processor architectures, we can highlight:

• Design space investigation and evaluation:

We made a complete evaluation of the proposed techniques and we highlighted their performance benefits.

## • Complete WCET analysis for the proposed design:

We present all necessary analyses to perform WCET estimations of programs compiled for the design proposed in this thesis. Such analyses include cache modeling, pipeline modeling and worst-case path search. An integrated environment between WCET and compiler is utilized to enhance WCET estimation.

## • Complete VHDL design and timing characterization:

We describe the implementation of the researched approaches regarding our deterministic real-time processor. We describe the timing of each module and their VHDL implementation, which are necessary for WCET modeling and estimation.

#### • Detailed branch architecture:

All details of the branch architecture are described including our methodology to model it during WCET analyses. We also extended the ISA to support static branch prediction and estimated the performance benefits of using or not this technology in real-time systems.

# $\bullet$ Low overhead full predication system for VLIW processors:

We propose a low-overhead full-predication system without adding overhead to the hardware data paths or its forwarding logic. The proposed predication system enhances the support of the single path execution as well as loop unrolling techniques.

### 1.4 TEXT ORGANIZATION

This thesis is organized in eight chapters including the Introduction which covers some basic concepts about predictability considerations, our main motivation and the thesis objective. Chapter 2 describes techniques employed in modern processors and how they affect hardware predictability. Pipeline principles, in- and out-of-order execution, branch prediction and predication are topics in the scope of this chapter.

Chapter 3 presents a list of related researches with their main contribution and objectives.

Chapter 4 is the core of this thesis. We describe the thesis rationale and the problem defining our target system and its requirements. We discuss design decisions for the proposed architecture comparing them with the related researches and we highlight our contributions.

Chapter 5 presents the VHDL hardware implementation of the design. This chapter is important because the implementation is the architecture realization of the proposed design. With this realization, we can infer hardware complexity of each component and the timing of the processor. The timing behavior is important for the WCET estimation which is covered in Chapter 6. This particular chapter describes how we propose to analyze the processor using composability. Instruction cache modeling, pipeline analysis and worst-case path search are topics in the scope of this chapter.

Chapter 7 describes our evaluation methodology. We assess the impact of architecture techniques upon WCET performance. The main idea is to quantitatively show WCET performance gains considering features employed in our design such as wide instruction fetching, latency of memory operations, static branch prediction and predication.

Finally, Chapter 8 presents our final remarks and suggestions for future work.

### 2 PROCESSORS AND PREDICTABILITY CONSIDERATIONS

In this chapter we briefly describe some important processor aspects that will be used throughout this thesis. We also consider the impact of using those techniques in the design of a processor suitable for future real-time systems.

The design and specification of a microprocessor include its Instruction Set Architecture (ISA). It specifies what instructions the processor can execute. The hardware implementation is characterized by a Hardware Description Language (HDL) and it describes simple Boolean logic (logic gates), registers and more complex structures such as decoders and multiplexers. Entire functional modules such as adder and multiplier circuits can be developed with these HDL structures.

Literature usually defines three abstraction levels (SHEN et al., 2005) for computer architectures: architecture, implementation and realization. The architecture specifies the ISA and defines the fundamental processor behavior. All software must be encoded using such ISA. Some examples of ISA are MIPS32, AMD x86\_64, ARM e ST200. The implementation specifies the project of the architecture, known as microarchitecture. The implementation is responsible for pipeline, cache memories and branch prediction specifications. The realization of a processor implementation is the physical encapsulation. In the case of microprocessors, this encapsulation is the chip. Realizations can vary depending on operating frequency, cache memory capacity, buses, lithography and packing. Realization also impacts on attributes as die size, power and reliability.

The ISA also defines a contract between the software and the hardware. This contract leads to an independent software and hardware development. Programs encoded using a particular ISA can be executed on different implementations with different levels of performance.

## 2.1 PIPELINE PRINCIPLES

Pipelining is a powerful technique to increase performance without massive hardware replication. Its main purpose is to increase the processor throughput with a low hardware increment. Throughput is the amount of instructions performed per unit of time – Instructions per cycle (IPC) . If a processor performs one instruction per unit of time, its throughput is 1/D where D is the instruction's latency. When using a pipeline, the processor subsystem is decomposed between several multiple simple stages adding a memory (buffer) between each of those stages. The original instruction is now composed of k stages and a new instruction can be initialized immediately after the previous one reaches the second stage. Instead of issuing an instruction after D units of time, the processor issues a new one after D/k units of time and the instructions are overlapped along the pipeline stages.

The performance improvement is ideally proportional to the pipeline length. However, there are physical limitations that reduce the number of feasible pipeline stages. In general, the limit of how a synchronous system can be divided into stages is associated with the minimum time required for the circuit operation: the uncertainty associated on using high frequencies and the distribution of circuit delays. Besides physical limitations, there is a cost and performance ratio that determines the optimal number of pipeline stages for a processor (SHEN et al., 2005) since hardware needs to be added for each added pipeline stage.

There are three basic challenges on using pipelines:

- Pipeline stages should be balanced to provide uniform sub-computations with same latency.

- Instructions should be unified to provide identical sub-computations using all stages.

- Instructions should be independent to reduce pipeline stalls.

Uniform sub-computations with the same latency reduce internal pipeline fragmentation. It is difficult to provide perfect and balanced stages and the pipeline operating frequency will be associated with the stage with higher latency. Processors also execute different types of instructions and not all of them will require all stages to execute. Since usually it is not possible to unify all sub-computations for all types of instructions, some degree of external fragmentation will exist and instructions need to pass every pipeline stage even if a particular stage is not required. If all computations were independent, a pipeline could operate in a continuous stream and it achieves to maximum throughput. Unfortunately, processor instructions are not fully independent and the result of one instruction could be required for the computation of the next one. If there is no hardware mechanism to forward this result to the next instruction, the pipeline must stall to guarantee instruction semantics.

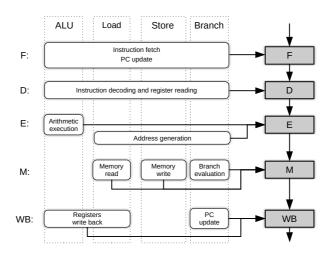

One generic 5-stage pipeline is naturally formed by one basic instruction cycle divided into the next five generic sub-computations:

- 1. Fetching (F).

- 2. Decoding (D).

- 3. Executing (E).

- 4. Memory accessing (M).

- 5. Results writing back (WB).

This generic pipeline begins with an instruction being fetched from memory. Next, it is decoded to determine which type of work will be performed and one or more operators are fetched from the processor registers. As soon as the operators are available, the decoded instruction is executed and the cycle ends by writing back the result in the memory or in the registers. During these five generic sub-computations, some exceptions can occur by changing the machine state and they are not explicitly specified in the instruction. The complexity and latency of each stage varies significantly depending on the processor's ISA.

Considering a modern RISC processor, the generic 5-stage pipeline executes three basic instructions classes:

- 1. Arithmetic and logical instructions (add, sub, shift) performed by an ALU (Arithmetic Logical Unit);

- 2. Memory instructions (load/store): performed by a memory unit that moves data between register and memory;

- 3. Control flow instructions (branch, calls and jumps): performed by a branch unit that manipulates the control flow.

Arithmetic instructions are restricted only to processor register operands. Only memory instructions access the memory. These restrictions form a load/store RISC architecture. Control flow instructions are used to manipulate the control flow to support function calls/returns as well as loop, if-then-else and while structures. They usually use relative addressing and the calculation of target address uses the program counter (PC) as reference.

Tables 1, 2 and 3 present instruction details related to the three basic instruction classes and the 5-stage generic pipeline (SHEN et al., 2005). Although they share sub-computation, they require different resources leading to idle stages.

| Stage | Task                      |

|-------|---------------------------|

| F     | Memory instruction access |

| D     | Decode and read registers |

| E     | Perform calculation       |

| M     |                           |

| WB    | Write data into registers |

|       |                           |

Table 1 – Arithmetic instructions specification.

| Stage | Load Store                |

|-------|---------------------------|

| F     | Memory instruction access |

| D     | Decode and read registers |

| E     | Generate memory address   |

|       | (base + offset)           |

| M     | Access data memory        |

| WB    | Write data into registers |

Table 2 – Memory instructions specification.

Table 3 – Control flow instructions specifications.

| Stage | Unconditional             | Conditional                |  |

|-------|---------------------------|----------------------------|--|

| F     | Memory instruction access |                            |  |

| D     | Decode and read registers |                            |  |

| E     | Generate target address   |                            |  |

| M     |                           | Evaluate condition         |  |

| WB    | Write back new PC         | If true, write back new PC |  |

# 2.1.1 Minimizing pipeline stalls

A computer program is an assembly instruction stream. Shen et al. (2005) define an instruction as a function  $i: T \leftarrow S_1$  op  $S_2$ , where  $D(i) = \{S_1, S_2\}$  is its domain and  $I(i) = \{T\}$  is its image.  $S_1$  and  $S_2$  are source operands (e.g. registers) and T is the destination (e.g. register). The relation between the domain and the image is defined by operator op. Let these be two instructions i and j where i precedes j. Instruction j could be dependent on i if one of the following three conditions of Equations 2.1, 2.2 and 2.3 holds.

$$I(i) \cap D(j) \neq \emptyset \tag{2.1}$$

$$I(j) \cap D(i) \neq \emptyset \tag{2.2}$$

$$I(i) \cap I(j) \neq \emptyset \tag{2.3}$$

The condition of Equation 2.1 happens when an instruction j needs an operand belonging to instruction's i image. This is a readafter-write (RAW) or true dependency and it denotes that j must not execute until i completes. Equation 2.4 shows this situation using generic assembly instructions. Instruction i writes to register  $R_3$  which is immediately read by j.

$$i: R_3 \leftarrow R_1 \text{ op } R_2$$

$$j: R_5 \leftarrow R_3 \text{ op } R_4 \tag{2.4}$$

The condition of Equation 2.2 happens when an instruction j writes into an operand of i. This is a write-after-read (WAR) or antidata dependency and it denotes that j must not execute before i or i will operate using a wrong operand value. Equation 2.5 exemplifies this dependency in which register  $R_1$  is read by i and it is immediately written by j.

$$i: R_3 \leftarrow R_1 \text{ op } R_2$$

$$j: R_1 \leftarrow R_4 \text{ op } R_5 \tag{2.5}$$

The third condition, Equation 2.3, happens when both instructions i and j write into the same register. This is write-after-write (WAW) or output dependency and it denotes that an instruction j must not complete before i. Equation 2.6 shows this dependency where both instructions i and j write into register  $R_3$ .

$$i: R_3 \leftarrow R_1 \text{ op } R_2$$

$$j: R_3 \leftarrow R_6 \text{ op } R_7$$

$$(2.6)$$

All above dependencies must be respected to ensure correct program semantics. Pipelines could easily break instruction semantics and there must be mechanisms for identifying and resolving them. A potential dependency violation is known as a *pipeline hazard*.

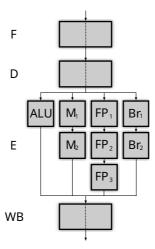

Figure 3 – Generic 5-stage pipeline representation.

Observing our generic 5-stage pipeline represented in Figure 3, not all hazards are automatically resolved. Considering the registers, they are read in stage D and written in stage WB. The *output dependency* is respected since writes are always sequential and only executed by stage WB. The *anti-data dependency* is also respected because every instruction i reads its operand before an instruction j writes into it. However, *true dependency* is not respected. If two instructions i and j are directly sequential and true dependent, when j reaches the stage D, i is still executing in stage E and, therefore, j must hold until i reaches stage WB.

There are also control dependencies involving program control flow semantics in our generic 5-stage pipeline. A control flow hazard is a *true dependency* on the program counter (PC). Control flow instructions write into PC and stage F reads and updates its value every cycle. If a conditional control flow is executed, it could update the PC with

the target address on true condition or the next linear address could be fetched on false. Since the control flow instructions update the PC only in the stage WB, there is a *true dependency* violation because PC is read before WB updates the new address.

A simple way to resolve pipeline hazards is to prevent instructions progression until the dependent instruction leaves the critical pipeline stage. This could be done by an interlock hardware mechanism which identifies dependency violations and stalls the pipeline or by the compiler with instruction reordering (better instruction scheduling) and/or adding "no operation" instructions. Table 4 shows the necessary stall cycles for each type of instruction to guarantee instruction semantics.

|                  | Instruction type |           |          |

|------------------|------------------|-----------|----------|

|                  | ALU              | Memory    | Flow     |

| Registers        | $R_i/R_j$        | $R_i/R_j$ | PC       |

| Write stage (i)  | WB (5)           | WB (5)    | WB (5)   |

| Read stage $(j)$ | D (2)            | D (2)     | F (1)    |

| Latency          | 3 cycles         | 3 cycles  | 4 cycles |

Table 4 – Maximum necessary stall cycles for dependency resolution.

We can see that adding stalls to prevent pipeline hazards substantially decreases the overall processor performance. Another feasible solution is to include hardware to build *forwarding paths* that forwards newer results to the necessary pipeline stage. On using forwarding paths, hardware mechanisms detect possible dependencies and multiplexers are added to units inputs to use newer values. For instance, stalls of two arithmetic sequential true dependent instructions are removed since the result of the first is ready in stage M and it is forwarded to stage W. Table 5 shows the updated stall values if we add this hardware to our 5-stage generic pipeline.

Most of dependency resolution stalls could be removed by using

| F                |           |                  |          |

|------------------|-----------|------------------|----------|

|                  |           | Instruction type |          |

|                  | ALU       | Memory           | Flow     |

| Registers        | $R_i/R_j$ | $R_i/R_j$        | PC       |

| Write stage (i)  | WB (5)    | WB (5)           | WB (5)   |

| Read stage $(j)$ | D (2)     | D (2)            | F (1)    |

| Forward output   | E, M, WB  | M, WB            |          |

| Forward input    | ALU       | ALU              | F        |

| Latency          | 0 cycles  | 1 cycle          | 4 cycles |

Table 5 – Maximum necessary stall cycles for dependency resolution with forward paths.

forward paths, specially for ALU instructions. Memory to ALU stalls could not be totally removed since memory reads are executed in stage M and its value is not ready when a truly dependent instruction is already in stage E. The most critical situation is related to control flow instructions. The fetch stage reads the PC at the beginning of the pipeline stage and control flow instructions update it only at stage WB. It cannot be forwarded since it will never be updated before new instructions are fetched. One way to reduce control flow latency is using branch prediction but it could decrease predictability and it will be discussed in a further section. Figure 4 displays the data-flow overview when using our generic 5-stage pipeline with forward paths.

Figure 4 – Generic 5-stage pipeline with forward paths.

## 2.2 MULTIPLE INSTRUCTION FETCHING

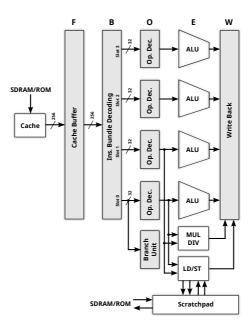

Pipelines described in the previous section reach a theoretical k speed-up factor where k is the number of stages. Their maximum throughput could also reach about 1 instruction per cycle (IPC). Instead of dividing the work in k simpler stages, we can reach this performance replicating the work with k copies allowing a different type of instruction level parallelism (ILP). Standard pipelines provide temporal parallelism while allowing multiple instruction execution give us spatial parallelism. If temporal and spatial parallelism are combined, processors could reach more than one instruction per cycle. Pipelining allied with wider instruction fetch constitute superscalar and VLIW (Very Long Instruction Word) machines. Both types of machines provide higher ILP and the basic difference between them is related to instruction scheduling. In superscalar machines, the hardware is responsible for instruction scheduling while in VLIW machines, instructions are statically scheduled by the compiler.

Figure 5 shows a dual-issue pipeline where the execution stage E is composed of different types of execution units. This machine can, for instance, execute at the same time one ALU and one memory instruction. In this design, each functional unit can be customized to a particular instruction resulting in a more efficient hardware. Each type of instruction has its own latency and uses all stages of its functional unit. If the intra-instruction dependencies are resolved before being forwarded to the functional units, there will be no pipeline stalls. This scheme allows distributed and independent control of each sub-pipeline execution. Replicated units such as ALUs can be added to this design allowing dual arithmetic instruction execution.

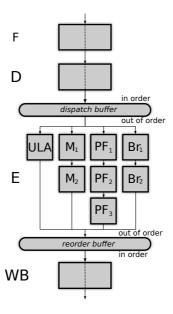

### 2.2.1 Out-of-order execution

If out-of-order execution is allowed in the execution stage of a diversified pipeline, we constitute a superscalar machine with a dynamic pipeline. This is one of the most successful designs and this is the type of machine used in general purpose applications such as smartphones,

Figure 5 – Diversified pipeline example:  $M_x$  are memory sub-stages,  $FP_x$  are floating-point stages and  $BR_x$  are branch stages.

desktop computers and laptops. Figure 6 shows an example of this design.

Dynamic pipelines have two special buffers (dispatch and reorder) and a hardware instruction scheduler. Instructions are fetched and decoded in a multi-issue fashion and the hardware scheduler is responsible for instruction assignment in the correct execution subpipeline. Instruction dependencies are also checked and when there are stall generating instructions, independent ones are issued into the execution stage. After all dependencies are resolved, stalled instructions in the dispatch buffer are executed. In the pipeline end, there is a reorder buffer to guarantee correct semantic order.

Superscalar processors are complex machines intended to extract the maximum performance abstracting latency details during the compilation phase. These abstractions also provide better code compatibility allowing different processor implementations and realizations to be binary compatible. Complex hardware is necessary to provide out-of-order execution and more details of this design is presented in Shen et al. (2005). However, out-of-order execution leads to timing anomalies

Figure 6 – Dynamic pipeline example:  $M_x$  are memory sub-stages,  $FP_x$  are floating-point stages and  $BR_x$  are branch stages.

and the high hardware complexity leads to unbounded states during WCET analysis.

## 2.2.2 In-order execution

Multiple instruction fetching with in-order execution and without hardware instruction scheduling leads to a VLIW (Very Long Instruction Word) design. The VLIW philosophy exposes the hardware not only at the ISA level but also at Instruction Level Parallelism (ILP). Superscalar machines extracted ILP using hardware features rearranging operations not directly specified in the code. VLIW processors do not perform any instruction scheduling and ILP must be provided by the compiler. Instruction rearranging (scheduling) is performed offline during compilation and the processor executes instructions exactly as defined by the compiler. The main idea is not to let the hardware do things that cannot be seen in programming, to reduce processor com-

VI IW Superescalar Instruction Instructions are fetched Multiple scalar operaflow tions are fetched sequentially but with multiple operations Scheduling Hardware dynamic Compiler static schedscheduler uler Fetch width Hardware dynamically Compiler determines determines the number statically the number of of fetched instructions fetched instructions Instruction Dynamic fetching al-Static fetching with ordering lowing out-of-order and only in-order execution in-order execution **Implications** Superescalar design is VLIW is an architecrelated to microarchitural technique. Hardtecture techniques ware details are exposed to the compiler

Table 6 – Basic differences between VLIW and Superescalar designs (FISHER; FARABOSHI; YOUNG, 2005).

plexity, to have only simple instructions and to increase predictability when needed. Table 6 shows basic differences between superscalar and VLIW designs.

VLIW designs are not commonly used in general purpose computing but they are very popular in embedded applications. Several DSPs (Digital Signal Processors) like Texas Instrument C6x, Agere/Motorola StarCore, Suns's MAJC, Fujitsu's FR-V, STss HP/ST Lx (ST200), Philips' Trimedia, Silicon Hive Avispa, Tensilica Xtensa Lx and Analog Devices TigerShark are VLIW processors. Intel's Itanium architecture for servers also uses this design philosophy.

VLIW compilers are more sophisticated since they must perform operations usually executed by the superscalar hardware. A superscalar

control unit avoids sophisticated compilers. The fact that all ILP extraction is done by the hardware every time an instruction is fetched by the processor control unit shows that this work could be easily done by the compiler. The code reordering after out-of-order execution is relatively trivial and compilers can handle it easily and they can evolve faster than a new processor construction.

Considering real-time systems, VLIW is a very interesting solution since hardware modeling is considerably less complex, in-order execution avoids timing anomalies and higher performance can be achieved using multi-issue instruction fetching.

### 2.3 BRANCH PREDICTION

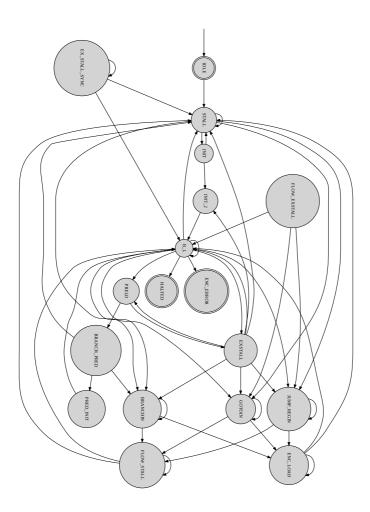

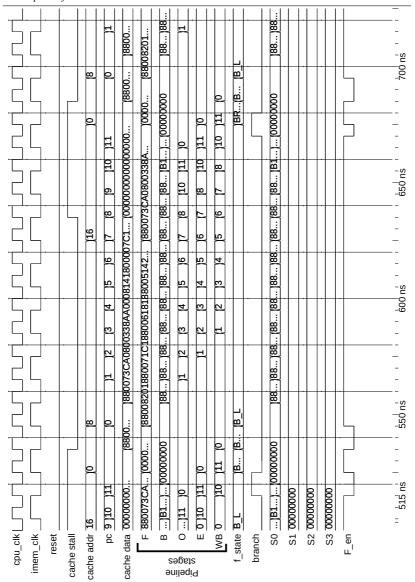

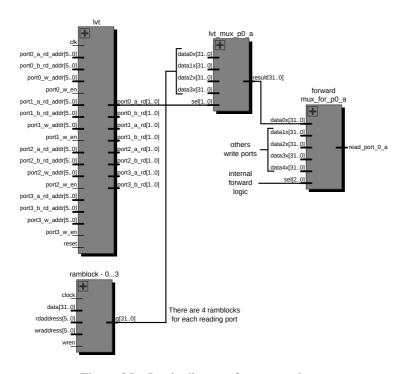

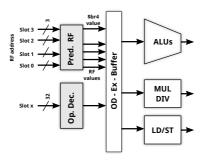

Conditional control flow instructions are usually responsible for *if* and *loop* program constructions and, unfortunately, they break the ideal pipeline flow reducing performance. Since control flow dependencies cannot be forwarded, as showed in Section 2.1, branch prediction techniques are commonly used to reduce this performance loss.