### UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Fabian Leonardo Cabrera Riaño

# CONTRIBUIÇÕES À OTIMIZAÇÃO DA EFICIÊNCIA NA TRANSFERÊNCIA DE ENERGIA SEM-FIO PARA DISPOSITIVOS ELETRÔNICOS MINIATURIZADOS

Tese submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do grau de Doutor em Engenharia Elétrica.

Orientador:

Prof. Doutor Fernando Rangel de Sousa

Florianópolis

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Cabrera Riaño, Fabian Leonardo Contribuições à Otimização da Eficiência na Transferência de Energia Sem-fio para Dispositivos Eletrônicos Miniaturizados / Fabian Leonardo Cabrera Riaño; orientador, Fernando Rangel de Sousa - Florianópolis, SC, 2016. 136 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia Elétrica.

Inclui referências

1. Engenharia Elétrica. 2. Circuitos integrados CMOS. 3. Transferência de energia sem-fio. 4. Acoplamento indutivo. I. Rangel de Sousa, Fernando. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

#### Fabian Leonardo Cabrera Riaño

# CONTRIBUIÇÕES À OTIMIZAÇÃO DA EFICIÊNCIA NA TRANSFERÊNCIA DE ENERGIA SEM-FIO PARA DISPOSITIVOS ELETRÔNICOS MINIATURIZADOS

Esta Tese foi julgada adequada para obtenção do Título de Doutor em Engenharia Elétrica e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina.

| Florianópolis, 7 de março de 2016. | Colo              |

|------------------------------------|-------------------|

| Carlos Galup<br>Coordena           | Montoro, Doutor V |

# Banca Examinadora:

| aminadora:                         |

|------------------------------------|

| Dermando Raugh de Don              |

| Fernando Rangel de Sousa, Doutor   |

| Orientador                         |

| V/ V                               |

| Robson Nunes de Lima, Doutor       |

| ali Phy                            |

| Tales Cleber Pimenta, Doutor       |

| Cauldays to Dal Film               |

| Paulo Augusto Dal Fabbro, Doutor   |

| Walter Pereira Carpes Jr., Doutor  |

| melle.                             |

| Marcelo Lobo Heldwein, Doutor      |

| · JAI                              |

| Eduardo Luiz Ortiz Batista, Doutor |

#### RESUMO

Os acoplamentos indutivos têm sido amplamente estudados para a transferência de energia sem-fio aos dispositivos médicos implantados e às etiquetas de identificação por radiofrequência, entre outros. Com a aparição de novos paradigmas como a "Internet das coisas", fica evidente a necessidade de miniaturizar os receptores de energia sem-fio. Essa miniaturização é ainda mais relevante no caso dos implantes médicos, porque ela visa à redução dos riscos para a saúde do paciente. Esta tese procurou uma solução que é natural no quesito de miniaturização: a implementação de um receptor de energia sem-fio completamente integrado na tecnologia CMOS.

Na busca pela miniaturização foi definida a eficiência como objetivo principal do projeto. Por esse motivo, a primeira parte da tese é dedicada a estudar as escolhas que otimizam a eficiência em acoplamentos indutivos. Inicialmente, esse estudo é feito com indutores planares fabricados sobre placas de circuito impresso. São apresentados modelos para o indutor e para o acoplamento indutivo. Com base nesses modelos é proposta uma metodologia de projeto através de programação geométrica. O resultado mostra quais devem ser a frequência de operação e as dimensões dos indutores para uma determinada distância entre eles. Esses resultados são verificados através de simulações eletromagnéticas e também experimentalmente.

Depois é apresentado o projeto do receptor de energia sem-fio. Esse projeto esteve focado em dois aspectos: a otimização da eficiência e a possibilidade de ser testado verdadeiramente sem-fio. Quanto à eficiência, a principal variável a ser otimizada é o fator de qualidade do indutor integrado. O indutor projetado e fabricado apresenta um fator de qualidade de 20,8 em 990 MHz, o qual é verificado experimentalmente através de um método semcontato. Esse fator de qualidade é considerado alto para um indutor integrado em tecnologia CMOS convencional. A carga do receptor é projetada especialmente para o teste e consiste em um oscilador que converte a tensão de alimentação em uma variação da frequência. Essa frequência modula a portadora, sendo que essa informação pode ser percebida na entrada do indutor primário. Com esse método é possível estimar a eficiência do sistema sem usar fios conectados ao chip receptor. O receptor é fabricado em um chip de 1,5 mm × 1,5 mm, enquanto o indutor transmissor é impresso em uma placa de FR4. A eficiência do acoplamento, quando o indutor primário tem um diâmetro médio de 22 mm e uma distância de 15 mm do receptor, foi medida como sendo -25,4 dB na frequência de 986 MHz. Considerando as características do receptor: implementação monolítica, área do chip, eficiência do

acoplamento e distância, o sistema projetado apresenta o melhor desempenho reportado na literatura.

Finalmente, é proposta uma metodologia de projeto para um amplificador de potência CMOS destinado a energizar o sistema projetado. Essa metodologia concilia o compromisso entre a resistência de condução e a capacitância de porta das chaves. A área ocupada é 1,5 mm², maior parte dela é usada pelos pads e as largas ligações de metal. Simulações pós-layout mostram uma eficiência de potência de 58% quando entregados 25,1 dBm ao indutor primário.

**Palavras-chave**: Acoplamento indutivo, circuitos integrados CMOS, medições sem-contato, ressonador LC, transferência de energia sem-fio.

#### ABSTRACT

Inductive links have been widely studied for wireless energy transfer to implanted medical devices and radiofrequency identification tags among others. With the development of new paradigms such as "Internet of Things" it becomes evident the need for miniaturization of the wireless energy receivers. The miniaturization is even more relevant in the case of the medical implants, because it aims to reduce the risks on the patient health. This thesis was focused into a solution that is natural when talking about miniaturization: the implementation of a CMOS fully integrated wireless power receiver.

On the path to miniaturization, the efficiency was defined as the main objective of the design. For that reason, the first part of this thesis is dedicated to study the choices that optimize the efficiency in inductive links. This study is done first with planar inductors manufactured on printed boards. Several models are presented for the inductor and the inductive link. Based on those models, a design methodology is proposed using geometric programming. The results show the inductor dimensions and the operating frequency that optimize the efficiency for a given distance. The predicted values are verified through electromagnetic simulations and also experimentally.

Next the design of the wireless power receiver is presented. Such design is focused on two aspects: the optimization of efficiency and the possibility of being truly wireless tested. Regarding efficiency, the main factor to be optimized is the quality factor of the integrated inductor. The designed and fabricated inductor has a quality factor of 20.8 at 990 MHz, which is experimentally verified using a contact-less method. That quality factor is considered high for an inductor integrated in a conventional CMOS process. The load of the receiver is designed specially for the test and it consists of an oscillator that converts the supply voltage into a frequency quantity. That frequency is used to modulate the carrier and that information can be perceived at the primary inductor input. With the proposed method it is possible to estimate the system efficiency without wires connected to the receiver chip. The receiver was implemented in a 1.5 mm × 1.5 mm chip, while the transmitter inductor is printed in a FR4 board. The link efficiency was measured when the primary inductor has an average diameter of 22 mm and with a distance of 15 mm from the receiver, resulting in -25.4 dB at the frequency of 986 MHz. Considering the characteristics of the receiver: monolithic implementation, chip area, link efficiency and distance to the transmitter, the designed wireless power transfer system exhibits a better performance than state-of-the-art systems.

Finally, a design methodology is proposed for a CMOS power amplifier intended to drive the designed system. That methodology solves the trade-off between the ON-resistance and gate capacitance of the switches. The area occupied is 1.5 mm², most of it is used by the pads and the wide interconnects. Post-layout simulations showed a power efficiency of 58% when delivering 25.1 dBm to the primary inductor of the wireless power transferring system.

**Keywords**: CMOS integrated circuits, contactless measurements, inductive link, LC resonator, wireless power transfer.

# LISTA DE FIGURAS

| 1  | Exemplo de sistema de assistência médica                               | 21 |

|----|------------------------------------------------------------------------|----|

| 2  | Composição geral de um implante corporal                               | 22 |

| 3  | Transferência de energia ao implante usando acoplamento in-            |    |

|    | dutivo                                                                 | 24 |

| 4  | Comparação da eficiência obtida em diferentes trabalhos so-            |    |

|    | bre acoplamentos indutivos                                             | 26 |

| 5  | Diagrama simplificado de um sistema de RFID                            | 33 |

| 6  | (a) Autoindutância. (b) Indutância mútua. (c) Indutor real             | 34 |

| 7  | Fator de perdas modelado comparado com simulações                      | 38 |

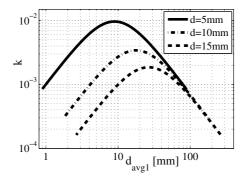

| 8  | Fator de acoplamento magnético quando $d_{avg2} = 4 \text{ mm.}$       | 39 |

| 9  | Resposta em frequência das partes real e imaginária da per-            |    |

|    | missividade para um dielétrico hipotético, mostrando vários            |    |

|    | fenômenos que contribuem.                                              | 41 |

| 10 | Permissividade relativa nos modelos Cole-Cole 4 polos                  |    |

|    | (CC4) e Debye-Drude 3 polos (DD3)                                      | 43 |

| 11 | Modelo do indutor: (a) Isolado no ar. (b) Próximo a um ma-             |    |

|    | terial dielétrico ideal ( $\sigma = 0$ ). (c) Rodeado de material dis- |    |

|    | persivo. (d) Circuito equivalente em uma faixa de frequências          |    |

|    | determinada                                                            | 44 |

| 12 | (a) Correntes parasitas geradas no material. (b) Modelo do             |    |

|    | indutor incluindo correntes parasitas no material dispersivo.          |    |

|    | (c) Modelo reduzido                                                    | 44 |

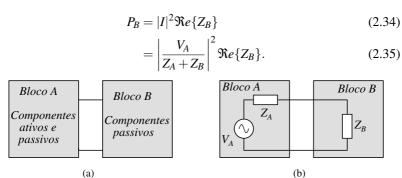

| 13 | Ligação de dois circuitos elétricos: (a) Diagrama de blocos.           |    |

|    | (b) Circuito equivalente.                                              | 46 |

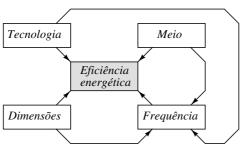

| 14 | Relação entre os principais fatores que afetam a eficiência do         |    |

|    | acoplamento indutivo                                                   | 48 |

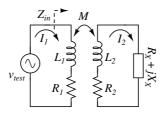

| 15 | Modelo elétrico do acoplamento indutivo                                | 51 |

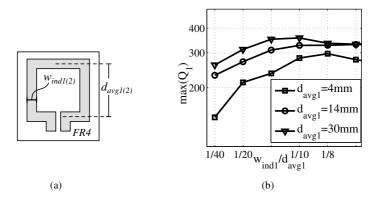

| 16 | (a) Geometria dos indutores. (b) Dependência do máximo                 |    |

|    | fator de qualidade com o fator de preenchimento                        | 55 |

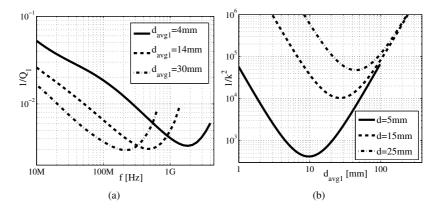

| 17 | (a) Recíproco do fator de qualidade variando com a                     |    |

|    | frequência, para $d_{avg1}/w_{ind1} = 8$ . (b) Recíproco do qua-       |    |

|    | drado do fator de acoplamento magnético quando $d_{avg2}$ =4 mm.       | 57 |

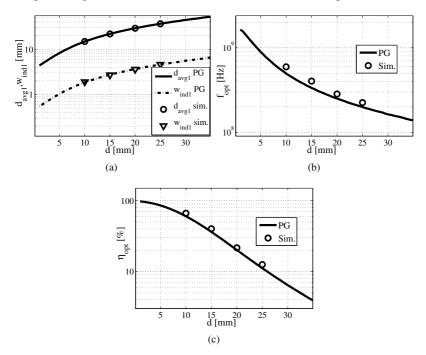

| 18 | Resultados do projeto ótimo: (a) Diâmetro médio e largura              |    |

|    | de linha do indutor primário. (b) Frequência. (c) Eficiência           | 58 |

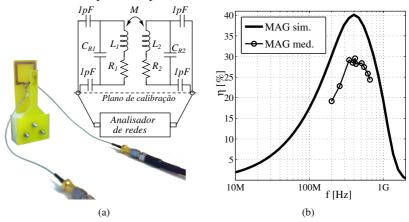

| 19 | Acoplamento indutivo ótimo para <i>d</i> =15 mm: (a) Configuração      |    |

|    | do teste. (b) Eficiência: Máximo ganho disponível (MAG)                | 59 |

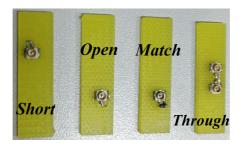

| 20 | Kit de calibração para conectores U.FL                                 | 60 |

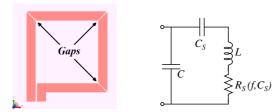

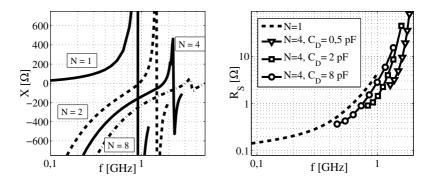

| 21 | (a) Indutor de 4 segmentos. (b) Modelo do indutor segmentado.                 | 62 |

|----|-------------------------------------------------------------------------------|----|

| 22 | (a) Reactância equivalente quando $C_D$ =0. (b) Perdas no indu-               |    |

|    | tor segmentado                                                                | 63 |

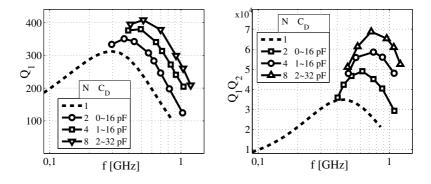

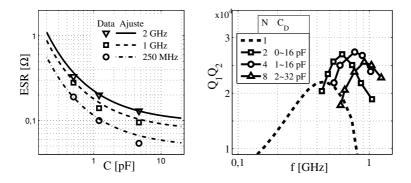

| 23 | (a) Fator de qualidade do indutor segmentado. (b) Produto                     |    |

|    | dos fatores de qualidade dos indutores primário e secundário                  |    |

|    | quando $d_{avg2}$ =4 mm                                                       | 63 |

| 24 | (a) Resistência série equivalente dos capacitores discretos.                  |    |

|    | (b) Produto dos fatores de qualidade considerando as perdas                   |    |

|    | dos capacitores.                                                              | 64 |

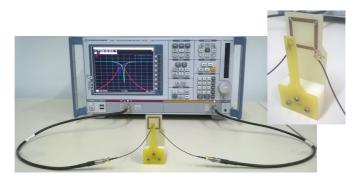

| 25 | Configuração de teste e detalhe do indutor de 4 segmentos                     | 65 |

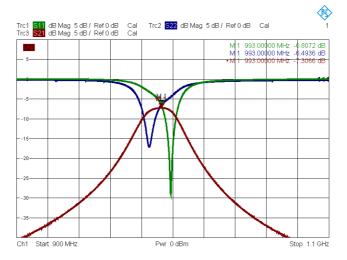

| 26 | Parâmetros S medidos do acoplamento com indutor primário                      |    |

|    | segmentado                                                                    | 65 |

| 27 | Sistema WPT típico com comunicação por backscattering                         | 69 |

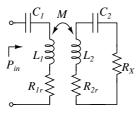

| 28 | Modelo do acoplamento ressonante                                              | 70 |

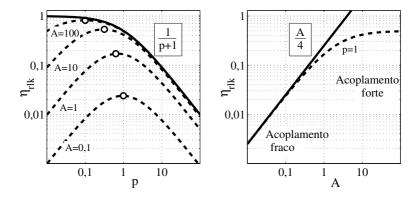

| 29 | Eficiência do acoplamento ressonante mostrando as regiões                     |    |

|    | de acoplamento                                                                | 73 |

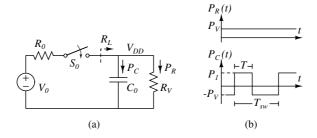

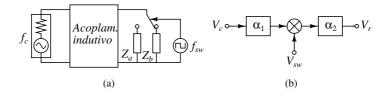

| 30 | Efeito do chaveamento sobre a eficiência. (a) Modelo. (b)                     |    |

|    | Formas de onda                                                                | 73 |

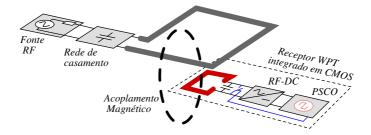

| 31 | Sistema para transferência de energia a receptor completa-                    |    |

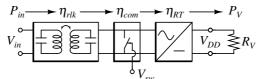

|    | mente integrado em CMOS                                                       | 75 |

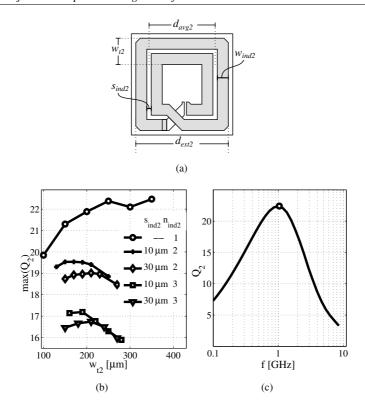

| 32 | (a) Indutor de duas espiras. (b) Máximo $Q_2$ para diferen-                   |    |

|    | tes indutores. (c) $Q_2$ para indutor de uma espira quando                    |    |

|    | $w_{ind2} = 250 \mu\text{m}.$                                                 | 77 |

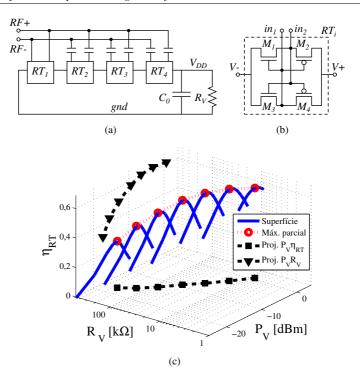

| 33 | Retificador: (a) Diagrama de blocos. (b) Esquemático de                       |    |

|    | cada estágio. (c) Eficiência simulada                                         | 79 |

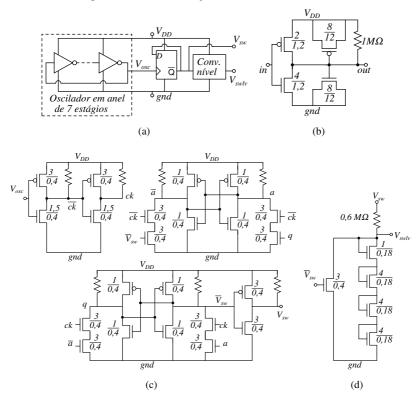

| 34 | Oscilador controlado pela fonte de alimentação: (a) Di-                       |    |

|    | agrama de blocos. (b) Implementação do inversor. (c)                          |    |

|    | Esquemático do flip-flop configurado como divisor de                          |    |

|    | frequência (todos os resistores têm valor de $1\mathrm{M}\Omega$ ). (d)       |    |

|    | Esquemático do conversor de nível                                             | 80 |

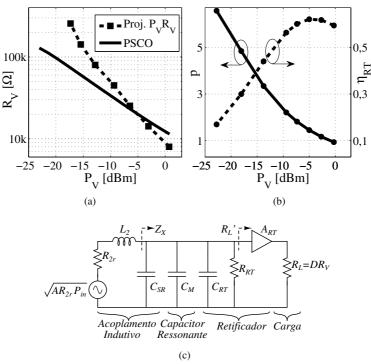

| 35 | Características da carga variável: (a) Curva de $R_V$ . (b) Curvas            |    |

|    | de eficiência e p. (c) Modelo de circuito para a transformação                |    |

|    | de impedância                                                                 | 81 |

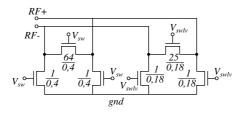

| 36 | Chave usada para a modulação de carga                                         | 83 |

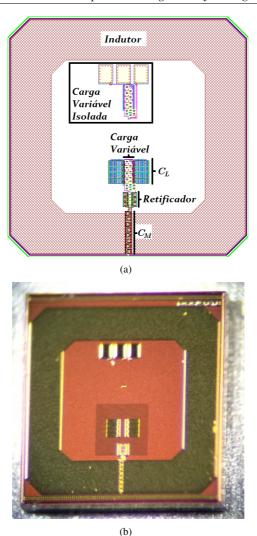

| 37 | Receptor WPT completamente integrado em tecnologia                            |    |

|    | CMOS 180 nm, área de $1,5 \text{ mm} \times 1,5 \text{ mm}$ : (a) Layout. (b) |    |

|    | Fotografia                                                                    | 84 |

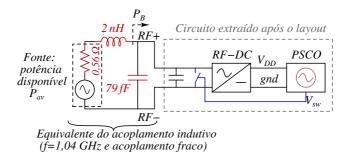

| 38 | Circuito usado para as simulações pós-layout                                  | 85 |

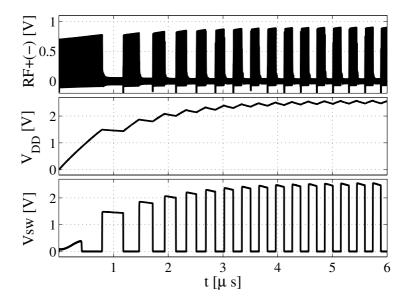

| 30 | Simulação transiente do recentor WPT                                          | 85 |

| 40         | Receptor WPT integrado incluindo o ressonador LC                                   | 87             |

|------------|------------------------------------------------------------------------------------|----------------|

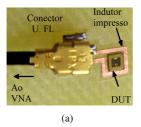

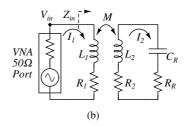

| 41         | Teste do ressonador: (a) Configuração do teste. (b) Modelo                         | 88             |

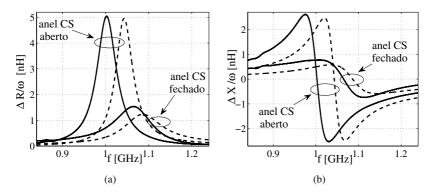

| 42         | Variação de impedância medida (linha sólida) e simulada (li-                       | 00             |

|            | nha pontilhada). (a) Resistência normalizada. (b) Reactância                       |                |

|            | normalizada                                                                        | 90             |

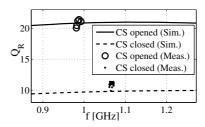

| 43         | Fator de qualidade do ressonador LC medido em várias amos-                         | 70             |

| 73         | tras                                                                               | 91             |

| 44         | Fator de acoplamento magnético com o indutor secundário                            | 71             |

| 44         | integrado ( $d_{avg2} = 1210 \mu\text{m}$ )                                        | 93             |

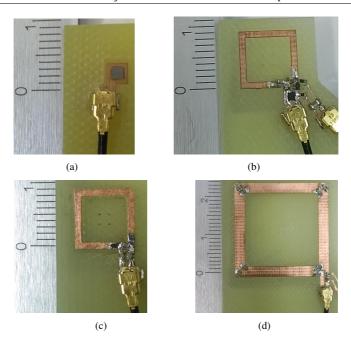

| 45         | Indutores transmissores: (a) $d_{avg1} = 2.4$ mm. (b) $d_{avg1} = 8$ mm            | 93             |

| 43         | com rede de casamento com varactores. (c) $d_{avg1} = 8$ mm sem                    |                |

|            | variatores. (d) $d_{avg1} = 22 \text{ mm}$                                         | 94             |

| 46         | Modelo do backscattering: (a) Diagrama de blocos. (b) Dia-                         | 7 <del>1</del> |

| 40         | grama de fluxo de sinal                                                            | 95             |

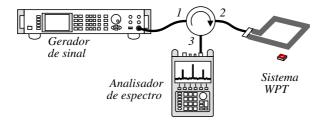

| 47         | Configuração de teste do sistema WPT.                                              | 95             |

|            |                                                                                    | 90             |

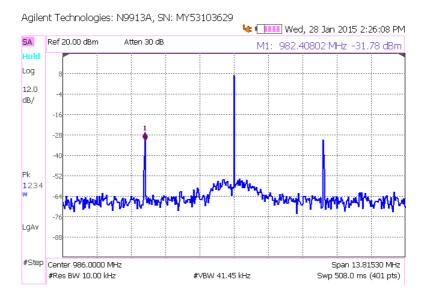

| 48         | Sinal refletido medido quando $d = 10 \text{ mm}$ , $d_{avg1} = 22 \text{ mm}$ e a | 97             |

| 40         | potência de entrada é 21 dBm                                                       |                |

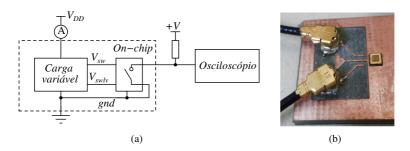

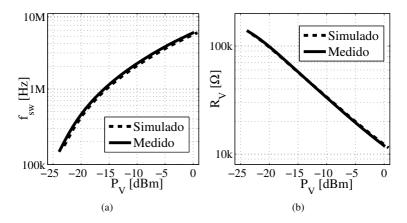

| 49         | Configuração de teste do PSCO: (a) Diagrama. (b) Fotografia.                       | 98             |

| 50         | Medidas do PSCO: (a) Frequência de oscilação. (b) Re-                              | 00             |

| <b>~</b> 1 | sistência equivalente.                                                             | 99             |

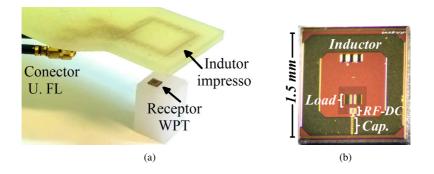

| 51         | Fotografias da configuração de teste: (a) Sistema WPT. (b)                         | 00             |

|            | Detalhe do receptor.                                                               | 99             |

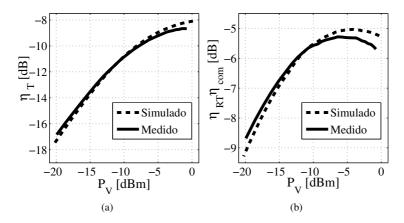

| 52         | (a) Eficiência total no regime de acoplamento forte. (b)                           |                |

|            | Eficiência combinada do retificador e a comunicação                                | 100            |

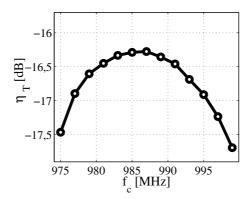

| 53         | Eficiência total do sistema WPT em função da frequência da                         |                |

|            | portadora quando $d = 1$ mm, $d_{avg1} = 8$ mm e $P_{in} = 0$ dBm                  | 101            |

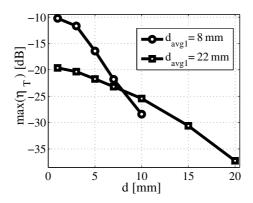

| 54         | Eficiência total medida para várias distâncias com: (a)                            |                |

|            | $d_{avg1} = 8 \text{ mm.}$ (b) $d_{avg1} = 22 \text{ mm.}$                         | 102            |

| 55         | Máxima eficiência total medida em função da distância                              | 103            |

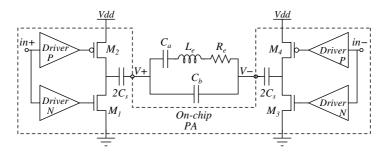

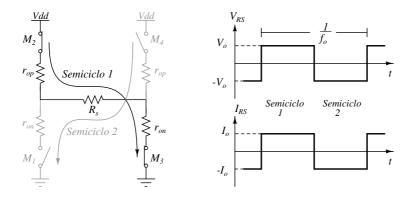

| 56         | (a) Sistema WPT. (b) Conversão DC-RF                                               | 107            |

| 57         | Impedância equivalente do indutor primário em 990 MHz                              | 109            |

| 58         | Topologia do PA.                                                                   | 110            |

| 59         | (a) Modelo do amplificador de potência. (b) Ondas de tensão                        |                |

|            | e corrente                                                                         | 110            |

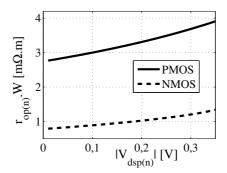

| 60         | Resistência de condução dos transistores em função da tensão                       |                |

|            | dreno-fonte.                                                                       | 113            |

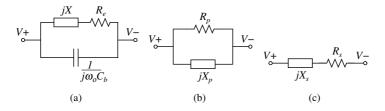

| 61         | Impedância equivalente: (a) Primeira simplificação. (b) Pa-                        |                |

|            | ralela. (c) Série.                                                                 | 114            |

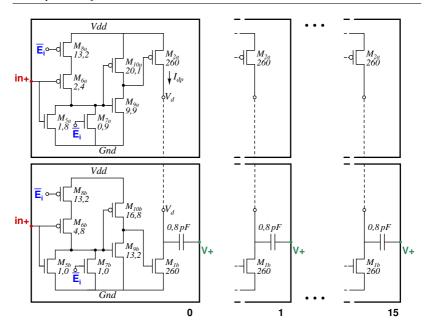

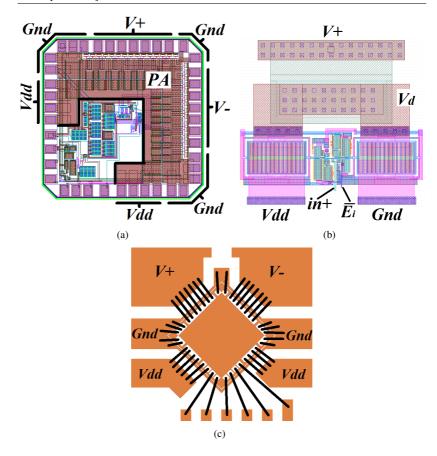

| 62         | Metade do PA diferencial e detalhe das células unitárias                           | 117            |

| 63 | Amplificador de potência CMOS: (a) Layout 1,5 mm × 1,5 mm.      |

|----|-----------------------------------------------------------------|

|    | (b) Layout de célula unitária. (c) Diagrama de micro-soldas 119 |

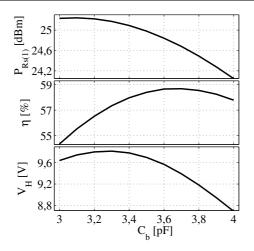

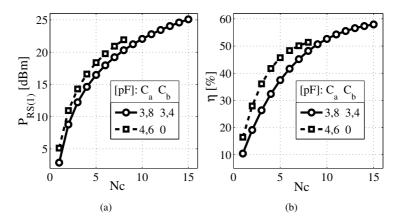

| 64 | Potência de saída, eficiência e tensão de excursão no nó V+ 120 |

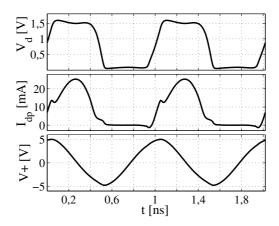

| 65 | Formas de onda no domínio do tempo em célula unitária do PA.120 |

| 66 | Varredura no número de células ativadas no PA. (a) Potência     |

|    | de saída. (b) Eficiência                                        |

# LISTA DE TABELAS

| 1  | Trabalhos recentes sobre acoplamentos indutivos                 | 25  |

|----|-----------------------------------------------------------------|-----|

| 2  | Trabalhos recentes em energização a dispositivos miniaturi-     |     |

|    | zados                                                           | 27  |

| 3  | Resumo das medições do acoplamento indutivo                     | 60  |

| 4  | Resumo de desempenho do acoplamento indutivo com indu-          |     |

|    | tor primário segmentado                                         | 66  |

| 5  | Variáveis envolvidas no projeto ótimo do sistema WPT            | 76  |

| 6  | Simulações de cantos do circuito integrado projetado            | 86  |

| 7  | Média e desvio padrão (DP) das caraterísticas do ressonador     | 91  |

| 8  | Indutores miniaturizados para transferência de energia sem-fio. | 92  |

| 9  | Resumo dos indutores transmissores projetados                   | 93  |

| 10 | Acoplamentos indutivos (rodeados por ar) com receptor WPT       |     |

|    | monolítico                                                      | 104 |

| 11 | Resultados numéricos da metodologia de projeto                  | 116 |

| 12 | Comparação de PAs integrados em CMOS                            | 122 |

|    |                                                                 |     |

#### LISTA DE SIGLAS

BAN Rede de área corporal (Body Area Network).

CNC Computer Numerical Control.

CS Crack-Stop.

DUT Dispositivo a ser testado (*Device Under Test*).

ESR Resistência série equivalente (*Equivalent Series Resistance*).

FoM Figura de mérito (*Figure of Merit*). IoT Internet das coisas (*Internet of Things*).

LTV Linear variante no tempo (*Linear Time – Variant*).

MAG Máximo Ganho Disponível (Maximum Achievable Gain).

MIM Metal-Isolante-Metal (Metal-Insulator-Metal).

PA Amplificador de potência.

PAE Eficiência de potência adicionada (*Power Added Efficiency*).

PG Programa Geométrico.

PSCO Oscilador controlado pela fonte de alimentação (Power-Supply

Controlled Oscillator).

RFID Identificação por radiofrequência (Radiofrequency Identification).

SRF Frequência de autoressonância.

VNA Analisador vetorial de redes (*Vector Network Analyzer*).

WPT Transferência de energia sem-fio (*Wireless Power Transfer*).

# LISTA DE SÍMBOLOS

d Distância entre indutores

$d_{ext2}$  Diâmetro externo do indutor secundário

$\eta$  Eficiência

$\varepsilon$  Permissividade elétrica  $\mu$  Permeabilidade magnética  $\rho$  Resistividade elétrica  $w_{ind}$  Largura de linha do indutor

$\Delta_{ind}$  Distância entre os terminais do indutor

I Corrente elétrica  $\Phi$  Fluxo magnético V Tensão elétrica

t Tempo L Indutância

$L_1$  Indutância do primário  $L_2$  Indutância do secundário

M Indutância mútua

k Fator de acoplamento magnético

R ResistênciaC Capacitância

$\lambda_{eff}$  Comprimento de onda efetivo  $d_{avg}$  Diâmetro médio do indutor

$R_{DC}$  Resistência DC

$F_{skin}$  Fator de multiplicação da resistência por efeito pelicular  $F_r$  Fator de redistribuição radial da corrente no indutor

$R_{rad}$  Resistência de radiação  $t_c$  Espessura do condutor

$\delta$  Profundidade de efeito pelicular  $\alpha_r$ ,  $\beta_{r2}$  e  $\beta_{r2}$  Parâmetros do modelo de  $F_r$  Fator de perdas do indutor Fator de perdas mínimo

$f_{\Lambda min}$  Frequência de fator de perdas mínimo

$K(\gamma)$  e  $E(\gamma)$  Funções elípticas

γ Variável intermédia para o cálculo da indutância mútua

$r_c$  Raio de um indutor circular

E Campo elétrico

H Campo magnético

φ Frequência angular

σ Condutividade elétrica

$\varepsilon_r(\omega)$  Função de permissividade relativa equivalente

$\varepsilon_0$  Permissividade elétrica no vácuo

n Número de polos no modelo da permissividade

$\varepsilon_{\infty}$  Permissividade quando a frequência tende ao infinito

$\Delta \varepsilon_n$  Mudança no valor da permissividade introduzida por cada

polo

$\alpha_n$  Fator de forma da transição da permissividade em cada polo

$\tau_n$  Constante de tempo de relaxação associada a cada polo

$\mu_0$  Permeabilidade magnética no vácuo

Z Impedância

P Potência

X Reatância

$p_0$  Proporção entre a resistência série do indutor e a resistência

de carga

$f_{obi}$  Função objetivo do programa geométrico

$f_i e g_i$  Restrições na forma de desigualdade e igualdade

$n_f e n_g$  Número de funções  $f_i e g_j$ Número de segmentos do indutor

N Número de segmentos do indutorQ Fator de qualidade

$S_0$  Chave no modelo de backscattering

T Intervalo de tempo em que  $S_0$  está fechada  $T_{\text{SW}}$  Período do sinal de controle da chave

D Ciclo útil (*Duty cycle*) do sinal de controle

$f_c$  Frequência da portadora

$f_{sw}$  Frequência do sinal modulador do backscattering

$n_{ind2}$  Número de espiras do indutor secundário

$s_{ind2}$  Espaçamento entre espiras do indutor secundário h Função de transferência do oscilador PSCO

W Largura dos transistores

# **SUMÁRIO**

| 1 Introdução                                                      | 21 |

|-------------------------------------------------------------------|----|

| 1.1 Motivação                                                     | 21 |

| 1.2 Escopo do trabalho                                            | 27 |

| 1.3 Publicações associadas à tese                                 | 29 |

| 1.4 Organização do documento                                      | 31 |

| 2 Fundamentos sobre Acoplamentos Indutivos                        | 33 |

| 2.1 Indutores                                                     | 34 |

| 2.2 Interação entre o Indutor e os Materiais Dispersivos          | 39 |

| 2.2.1 Propriedades Elétricas dos Materiais                        | 40 |

| 2.2.2 Interação entre o Campo Elétrico do Indutor e o Material ao |    |

| seu Redor                                                         | 42 |

| 2.2.3 Interação entre o Campo Magnético do Indutor e o Material   |    |

| ao seu Redor                                                      | 44 |

| 2.3 Adaptação de Impedâncias                                      | 46 |

| , , , , , , , , , , , , , , , , , , , ,                           | 48 |

| 3 Eficiência Ótima em Acoplamentos Indutivos                      | 51 |

| 3.1 Modelo Elétrico                                               | 51 |

| 3.2 Projeto do Acoplamento Indutivo com Eficiência Otimizada      | 53 |

| 3.2.1 Programação Geométrica                                      | 53 |

| 3.2.2 Definição do Caso Usado como Exemplo                        | 54 |

| 3.2.3 Formulação do Problema                                      | 56 |

| 3.3 Execução e Validação Experimental do Método                   | 58 |

|                                                                   | 61 |

| 3.5 Conclusões sobre a otimização da eficiência                   | 66 |

| 1 0                                                               | 69 |

| $\mathcal{E}$                                                     | 69 |

| 1                                                                 | 70 |

| <i>C</i> 1 3 1                                                    | 72 |

| 3 1                                                               | 72 |

| F 5                                                               | 74 |

| $\mathcal{E}$                                                     | 76 |

| $\mathcal{E}$                                                     | 76 |

|                                                                   | 78 |

| e                                                                 | 79 |

|                                                                   | 82 |

| <b>√</b> 5                                                        | 83 |

| 5 Medição do Sistema WPT com Receptor Miniaturizado               | 87 |

| 5.1  | Ca  | racterização do ressonador LC integrado               | 87  |

|------|-----|-------------------------------------------------------|-----|

| 5.1  | .1  | Método proposto                                       | 87  |

| 5.1  | .2  | Aplicação do método                                   | 90  |

| 5.2  | Pro | ojeto do indutor primário                             | 92  |

| 5.3  | Es  | tratégia de teste                                     | 95  |

| 5.4  | Ca  | racterização da carga variável                        | 98  |

| 5.5  | M   | edição do sistema WPT                                 | 98  |

| 5.5  | .1  | Teste em regime de acoplamento forte                  | 99  |

| 5.5  | .2  | Variação da eficiência com a frequência               | 100 |

| 5.5  | .3  | Dependência da eficiência com a distância             | 100 |

| 5.6  | Re  | sumo dos resultados e comparação com o estado da arte | 102 |

| 6 Aı | npl | lificador de Potência para WPT                        | 107 |

| 6.1  | Pro | ojeto do amplificador                                 | 108 |

| 6.1  | .1  | Especificações                                        | 108 |

| 6.1  | .2  | Topologia                                             | 109 |

| 6.1  | .3  | Dimensionamento dos transistores                      | 112 |

| 6.1  | .4  | Rede de transformação de impedância                   | 114 |

| 6.1  |     | Metodologia de projeto                                | 115 |

| 6.2  | Im  | plementação                                           | 116 |

| 6.2  | .1  | Implementação do circuito                             | 116 |

|      |     | Layout                                                | 117 |

| 6.2  | .3  | Resultados                                            | 118 |

| 7 Co | ont | ribuições e desdobramentos                            | 123 |

| 7.1  | Re  | sumo das contribuições                                | 123 |

|      |     | esdobramentos futuros                                 | 126 |

| Refe | rên | cias bibliográficas                                   | 136 |

# 1 INTRODUÇÃO

### 1.1 MOTIVAÇÃO

Com o rápido crescimento do número de aparelhos conectados à internet nos últimos anos, é possível visualizar novas aplicações e serviços em favor do bem-estar humano. Grande parte desses novos serviços e aplicações derivam de um paradigma denominado "Internet das Coisas" ou IoT por suas siglas no inglês (*Internet of Things*) [1]. A IoT habilita a conectividade entre os objetos que fazem parte da vida cotidiana permitindo que qualquer pessoa com um dispositivo móvel e autorização adequada possa controlar ou monitorar qualquer coisa [2].

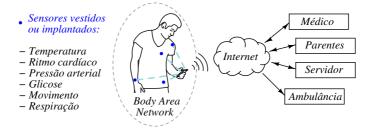

Entre as diversas áreas de aplicação da IoT podem ser citadas as casas inteligentes [3], as cidades inteligentes [4], o monitoramento ambiental [5] e a logística [6]. Na área da saúde são previstos sistemas de assistência médica [7]. Um exemplo é mostrado na Figura 1, onde vários dispositivos são usados para monitorar sinais biológicos de uma pessoa. Esses dispositivos podem comunicar-se entre si e também com um dispositivo móvel formando uma rede de área corporal (*Body Area Network* - BAN). Por sua vez, o dispositivo móvel dispõe de acesso à internet permitindo que a informação sobre o estado de saúde atual da pessoa seja enviada ao médico ou aos parentes, inclusive um aplicativo no dispositivo móvel pode enviar um alerta ao serviço de emergência caso os dados medidos indiquem que é necessário.

Alguns dispositivos que formam as BAN são os denominados "vestíveis", os quais são embutidos em roupas e acessórios de vestir, como óculos, braceletes, relógios e anéis entre outros. Outros dispositivos são implantados no corpo humano complementando a funcionalidade das BAN.

Figura 1: Exemplo de sistema de assistência médica.

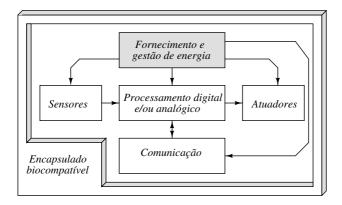

Figura 2: Composição geral de um implante corporal.

Esses implantes corporais podem ser usados com diversos propósitos, tais como o tratamento de doenças crônicas [8–15], o monitoramento da saúde [16–18] e a restauração ou extensão de habilidades motoras através de interfaces cérebro-máquina [19–21]. Em termos de tratamento de doenças crônicas, podem ser citados exemplos como os marcapassos e os desfibriladores cardíacos [8]; os implantes cocleares e oculares que permitem restaurar a audição e a visão [9, 10]; e a estimulação cerebral profunda utilizada para tratamento da doença de Parkinson e alguns transtornos mentais [11]. Soluções implantadas para outras doenças como a diabetes ainda são objeto de pesquisas [12–14], nesse caso é necessária a implementação de sistemas de controle em malha fechada incluindo, por exemplo, sensores de glicose, processamento dos dados, injeção de insulina e comunicação com dispositivos externos [22].

De forma geral, pode-se esquematizar um implante eletrônico como mostrado na Figura 2. Os sensores são transdutores que convertem para sinal elétrico os parâmetros físicos, biológicos ou químicos, tais como a temperatura, a pressão e a concentração de algum tipo específico de molécula ou íon. O sinal dos sensores deve ser condicionado e processado usando circuitos analógicos e/ou digitais. Esse módulo de processamento também é encarregado do controle dos atuadores e da recepção e do envio de dados para o módulo de comunicação. Os atuadores por sua vez, são transdutores que, a partir de um sinal elétrico, interagem com o ambiente circunvizinho ao implante. Dois exemplos de atuador são: o estimulador de tecido cardíaco em marcapassos e a bomba de insulina. Já o módulo de comunicação tem

1.1 Motivação 23

como função enviar os dados medidos e receber instruções de um dispositivo externo ao corpo. Na Figura 2 também é mostrada a necessidade de ter um encapsulamento biocompatível. Esse encapsulamento deve proteger os circuitos e isolar eletricamente o implante dos tecidos, mas também deve ter áreas abertas para permitir a interação entre os tecidos e os sensores e atuadores [23]. Outro módulo importante no implante é o que fornece energia para o funcionamento dos circuitos de processamento e de comunicação. Fornecer energia para o implante constitui um desafio considerável, uma vez que não devem existir fios ligando o implante ao exterior e que o implante deve ter o menor tamanho possível visando uma característica não-invasiva.

A miniaturização dos dispositivos é um dos principais desafios tanto nos implantes corporais quanto nas aplicações IoT. Nos primeiros, a miniaturização é fundamental para diminuir o desconforto e os riscos ao paciente. No caso da IoT também é importante dado que a característica pervasiva<sup>1</sup> da IoT só poderá ser atingida quando o tamanho dos dispositivos for tão pequeno que eles tendam a "desaparecer" [24]. A maioria dos implantes comerciais atuais usa baterias para alimentar os circuitos, sendo que tais baterias ocupam a maior parte do volume do dispositivo. Além das dimensões físicas, as baterias armazenam uma quantidade de energia limitada, portanto precisam ser trocadas periodicamente. Cada troca do implante significa um procedimento cirúrgico com riscos para a saúde do paciente. Por esse motivo é necessário encontrar alternativas para alimentar os dispositivos implantados. Muito tem sido pesquisado sobre como recuperar a energia disponível nas imediações dos implantes [25–30]. Por exemplo, em [25], busca-se utilizar a luz para alimentar dispositivos implantados. Em [26], o gradiente de temperatura é convertido para uma tensão elétrica por meio de um gerador termoelétrico. Outras fontes de energia que podem ser aproveitadas são as vibrações mecânicas [27-29] e as variações na pressão sanguínea [30]. Porém, essas fontes de energia só estão disponíveis em algumas aplicações e em quantidades limitadas. Outra opção é usar o campo magnético para transferir energia de um dispositivo externo ao implante usando os denominados acoplamentos indutivos [31].

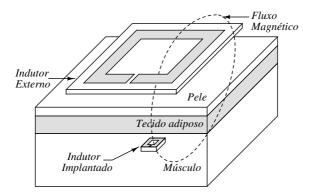

A alimentação do implante com um acoplamento indutivo é mostrada na Figura 3. A energia é transferida do indutor externo para o indutor implantado usando o fluxo magnético que liga os dois indutores. A diferença entre o tamanho dos indutores na figura é para destacar que o indutor implantado deve ser o menor possível, enquanto que o indutor externo não está sujeito

<sup>&</sup>lt;sup>1</sup>Que se espalha, difunde por toda parte, ou que tende a propagar-se ou estender-se totalmente por meio de diversos canais, tecnologias, sistemas, dispositivos etc.

Figura 3: Transferência de energia ao implante usando acoplamento indutivo.

à mesma restrição. A figura também apresenta uma possível configuração dos tecidos biológicos ao redor do implante com três camadas: pele, tecido adiposo e músculo.

A interação entre os campos eletromagnéticos e os tecidos biológicos causa perdas de energia, as quais são convertidas em calor e, portanto, aquecem os tecidos. Esse aquecimento é limitado pelos padrões que estabelecem os níveis de segurança a respeito da exposição de seres humanos aos campos eletromagnéticos em radiofrequências [32]. Por conseguinte, a potência máxima que pode ser transmitida pelo indutor externo é restrita. Para aumentar a potência recebida no implante, o projeto do sistema deve eleger a otimização da eficiência na transferência de energia como principal objetivo.

O projeto do acoplamento indutivo geralmente parte de uma tecnologia de fabricação disponível, de uma distância entre indutores especificada (d), e de uma restrição no diâmetro<sup>2</sup> externo do indutor implantado  $(d_{ext2})$ . A tecnologia escolhida limita o máximo fator de qualidade dos indutores, ao passo que o máximo fator de acoplamento magnético depende dos valores de d e  $d_{ext2}$  especificados. Depois de ter esses parâmetros especificados, a eficiência pode ser otimizada pela cuidadosa escolha da adaptação de impedâncias, da geometria do indutor externo e da frequência. Vários trabalhos publicados têm focado sua atenção em otimizar a eficiência de acoplamentos indutivos [33–36]. Em [33] são mostradas expressões analíticas para a carga apresentada ao indutor secundário que maximiza a eficiência. Outros

<sup>&</sup>lt;sup>2</sup>Neste caso, foi definido o diâmetro do quadrado como sendo a distância entre dois dos seus lados paralelos.

1.1 Motivação 25

trabalhos exploram a escolha das dimensões dos indutores que otimizam a eficiência [34, 35]. Quanto à frequência, geralmente empregam-se sinais na faixa dos MHz. Todavia, a análise feita em [37] levantou a possibilidade de alimentar os implantes com frequências bem mais elevadas, na escala dos GHz. Em [36], indutores de diferentes tamanhos foram simulados para investigar a frequência ótima, mas a relação entre os tamanhos que maximiza o coeficiente de acoplamento magnético não foi considerada [34].

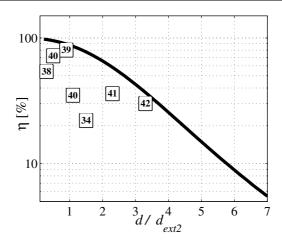

Na Tabela 1 são comparados os resultados de trabalhos recentes sobre acoplamentos indutivos, inclusive com resultados preliminares deste trabalho publicados em [42]. A eficiência obtida nessas referências é plotada na Figura 4 em função da distância entre indutores normalizada pelo diâmetro externo do indutor receptor. A linha sólida corresponde à máxima eficiência estimada quando os indutores são implementados em placa de circuito impresso (dielétrico FR4, com  $\varepsilon = 4,4\varepsilon_0$  e espessura do cobre de 35  $\mu$ m) para uma dada distância relativa entre indutores, normalizada pelo diâmetro externo do indutor receptor [42], usada como referência para comparar os trabalhos. A referência [39] aproxima-se da eficiência máxima, mas é importante notar que são usados indutores implementados com fios, os quais podem apresentar melhor fator de qualidade do que aqueles implementados em placa de circuito impresso. A eficiência obtida experimentalmente em [42] difere levemente da curva devido às perdas introduzidas pelos capacitores e pelas ilhas de solda usadas no protótipo experimental desenvolvido. O diâmetro dos indutores receptores da Tabela 1 varia entre 3 mm e 30 mm, notando que o indutor com diâmetro de 3 mm da referência [41] foi apenas simulado e não fabricado. No entanto, espera-se que os implantes possam ter tamanhos menores.

A Tabela 2 resume as características de trabalhos recentes relevantes

| Referência                 | [34]  | [38] | [39] | [40] | [40] | [41]        | [42] |

|----------------------------|-------|------|------|------|------|-------------|------|

| Diâmetro externo ind.      | 10    | 30   | 22   | 19   | 19   | 3           | 4,5  |

| receptor $(d_{ext2})$ [mm] |       |      |      |      |      |             |      |

| Distância (d) [mm]         | 15    | 10   | 20   | 10   | 20   | 7           | 15   |

| Distância normali-         | 1,5   | 0,3  | 0,9  | 0,5  | 1,1  | 2,3         | 3,3  |

| zada $(d/d_{ext2})$        |       |      |      |      |      |             |      |

| Frequência [MHz]           | 6,8   | 4,5  | 0,7  | 12,1 | 12,1 | 3000        | 415  |

| Eficiência (η) [%]         | 22    | 54   | 80   | 72   | 35   | 36          | 30   |

|                            |       |      |      |      |      | (Simulação) |      |

| Tecnologia                 | PCB + | fios | fios | PCB  | PCB  | PCB         | PCB  |

|                            | fios  |      |      |      |      |             |      |

Tabela 1: Trabalhos recentes sobre acoplamentos indutivos.

Figura 4: Comparação da eficiência obtida em diferentes trabalhos sobre acoplamentos indutivos.

quanto à miniaturização de dispositivos alimentados por WPT. Entre as cinco referências mostradas na tabela, somente em [43] e [16] sistemas são integrados em um mesmo substrato contendo todos os blocos. A integração em apenas uma tecnologia pode significar a redução em tamanho, a redução no custo, o aumento da robustez mecânica e a facilidade para a produção em massa. Essas vantagens podem ser reforçadas no caso da tecnologia CMOS, devido à maturidade dessa tecnologia na fabricação de circuitos analógicos e digitais. Os circuitos de radiofrequência também têm ganhado espaço nos processos CMOS mais recentes que buscam otimizar os dispositivos passivos. Sendo que o principal mecanismo limitante no fator de qualidade dos indutores integrados em CMOS é a indução de correntes no substrato. Esse efeito é notório em decorrência da proximidade entre o substrato e a camada de metal na qual é implementado o indutor. Em [44], foi aplicado um método de pós-processamento para fabricar o indutor sobre o chip CMOS. No entanto, a distância entre o indutor e o substrato não muda muito, assim como a espessura do metal em que é fabricado o indutor (3  $\mu$ m), consequentemente, o fator de qualidade reportado é de apenas 3. Em uma tecnologia CMOS convencional sem pós-processamento, pode ser atingido um fator de qualidade de até 22,5 [45]. No processo MEMS usado em [20] foi obtido um fator de qualidade de 29. Considerando que não existe o substrato resistivo embaixo do indutor, indutores com melhores fatores de qualidade poderiam ser implementados nessa tecnologia. Todavia, além de demandar várias tecnologias, essa abordagem apresenta outra desvantagem, a necessidade em ocupar o dobro da área, considerando que o indutor não compartilha o espaço com os outros componentes. Em outras palavras, só a metade da área do implante estaria aproveitando o fluxo magnético gerado pelo indutor externo. Em [46] não foi reportado o fator de qualidade do indutor, mas é possível ter uma referência sabendo-se que um indutor implementado em PCB pode atingir fatores de qualidade de até 350 [42].

Referência [44] [46] [43] [20] [16] 2008 2010 2011 2013 2013 Ano CMOS + CMOS + CMOS MEMS+ CMOS Tecnologia pós-proces. **PCB** CI + diodos Área [mm<sup>2</sup>] 0,5 4,4 1 5 4,8 2,5 5 0.4 5,2 Freq. [GHz] Elemento Indutor Indutor Antena Indutor Antena Receptor Efic. [%] 0,02 0,06 0,008 0,0003 @ dist. [mm] @ 0.5 @ 25 @ 10 @ 1 @ 35 Meio 10 mm ar + 30 mm ar + 5 mm 15 mm músculo e tecidos solução salina

Tabela 2: Trabalhos recentes em energização a dispositivos miniaturizados.

Nas referências [16, 43] foram implementadas antenas para captar a energia transferida a partir de uma antena externa. Por esse motivo, escolheram uma frequência relativamente alta (5 GHz). É importante notar que o comprimento de onda de um sinal se propagando no vácuo na frequência de 5 GHz é de 60 mm, ou seja, as distâncias escolhidas para teste, 10 mm e 35 mm respectivamente, estão dentro da região de campo próximo reativo. Nessa região o tratamento do dispositivo captador de energia supondo o acoplamento capacitivo ou indutivo pode resultar em um projeto mais eficiente.

#### 1.2 ESCOPO DO TRABALHO

O tema central desta tese é a transferência de energia sem-fio (Wireless Power Transfer - WPT) a dispositivos miniaturizados. O interesse na miniaturização do indutor/antena receptor de energia nos implantes levantou a possibilidade de usar frequências altas (na ordem de GHz) mantendo os níveis seguros de exposição dos tecidos aos campos eletromagnéticos [37]. Porém, a procura pela frequência ótima para a transferência de energia

sem-fio através dos tecidos biológicos depende da resposta a uma pergunta mais fundamental: qual é a frequência que otimiza a eficiência no caso em que o acoplamento indutivo está rodeado apenas por ar? E além disso, quais são as variáveis que afetam a eficiência do acoplamento indutivo? Para responder a essas perguntas e conseguir a miniaturização do receptor WPT, foi definido o escopo da tese em três esferas:

- Pesquisa sobre os fatores que influenciam a eficiência na transferência de energia em acoplamentos indutivos. Além de conhecer esses fatores, deve-se construir um modelo teórico que mostre a dependência entre eles e a eficiência. Com base nesse modelo, é possível estabelecer os compromissos de projeto e, assim, propor um método de projeto para os acoplamentos indutivos.

- Projeto do receptor WPT completamente integrado em CMOS. A completa integração do receptor significará uma verdadeira miniaturização, além de trazer outras vantagens como a redução de custo, melhor confiabilidade e testabilidade e também a possibilidade de implementar blocos analógicos e digitais no mesmo chip. Nesse sentido, o principal desafio é conseguir o fator de qualidade ótimo para o indutor integrado, dado que em tecnologia CMOS os indutores costumam ter baixo fator de qualidade, principalmente por causa da proximidade com o substrato resistivo.

- Considerações de projeto ao nível de blocos e do sistema WPT. A eficiência total do sistema WPT depende da eficiência de cada um dos blocos que o compõem, mas também da arquitetura e do projeto no nível de sistema. Apesar de não generalizar, o projeto e teste do receptor WPT completamente integrado deixa algumas lições importantes para o projeto do sistema WPT. Quanto aos blocos, cabe destacar o projeto do amplificador de potência necessário para entregar potência ao acoplamento indutivo.

Nos três itens descritos anteriormente, a otimização, a simulação e as medidas são feitas considerando apenas que o material em torno dos indutores é ar. No entanto, os conceitos desenvolvidos nesta tese também poderão ser utilizados em trabalhos futuros para projetar acoplamentos indutivos rodeados por tecidos biológicos.

Outra preocupação comum quanto ao uso dos acoplamentos indutivos para WPT é a variação da eficiência com relação ao alinhamento dos indutores e sua orientação angular. Esse assunto não será abordado nesta tese. O

foco será a otimização da eficiência para o caso nominal, ou seja, quando o centro dos indutores está alinhado e os indutores estão orientados paralelamente.

### 1.3 PUBLICAÇÕES ASSOCIADAS À TESE

No decorrer da pesquisa de doutorado foram apresentados quatro artigos em conferências e um artigo de revista como resultado das atividades desenvolvidas. Segue um resumo dessas publicações.

**Paper I.** Projeto ótimo de acoplamentos indutivos energeticamente eficientes para alimentar dispositivos implantados [42].

CONFERÊNCIA: 2014 IEEE Topical Conference on Biomedical Wireless Technologies, Networks, and Sensing Systems (BioWireleSS).

RESUMO: Este paper apresenta um método para o projeto ótimo de acoplamentos indutivos usando programação geométrica. A otimização proposta permite a inclusão de todos os requisitos elétricos e geométricos de projeto associados ao acoplamento. É mostrado como exemplo o dimensionamento do indutor primário e a escolha da frequência quando o indutor secundário tem um diâmetro de 4 mm. Os indutores projetados para uma distância de 15 mm foram implementados em placas de FR4. A máxima eficiência medida foi 30% a 415 MHz, a qual está de acordo com os valores esperados em simulação.

**Paper II.** Receptor de energia sem-fio completamente integrado em CMOS para dispositivos implantados autônomos [45].

CONFERÊNCIA: 2014 IEEE International Symposium on Circuits and Systems (ISCAS).

RESUMO: Este artigo apresenta o projeto de um receptor de energia sem-fio totalmente integrado. O sistema utiliza backscattering para responder ao transmissor, permitindo inferir a eficiência total na transferência de energia. O circuito foi limitado a uma área de silício de 1,5 mm × 1,5 mm em um processo CMOS 180 nm. O objetivo principal foi otimizar a parte da eficiência relacionada com o receptor. Para tanto, foram otimizados: o fator de qualidade do indutor integrado, o casamento de impedância e a eficiência do retificador. O fator de qualidade simulado do indutor integrado foi de 22 na frequência de 1 GHz. Simulações pós-layout do sistema mostram que a eficiência combinada da adaptação de impedância e do retificador é de 57%

quando a potência disponível no indutor é 1 dBm.

**Paper III.** Caracterização sem-contato de um ressonador LC integrado em CMOS para transferência de energia sem-fio [47].

REVISTA: IEEE Microwave and Wireless Components Letters.

RESUMO: Neste paper é proposto um método para caracterização semcontato de um ressonador LC integrado em CMOS. O método proposto usa uma interação magnética bem modelada entre o DUT e o setup de teste para extrair os dois parâmetros principais do ressonador: o fator de qualidade e a frequência de ressonância. Com esse método foi medido um ressonador LC que faz parte de um receptor WPT integrado em uma área de  $1.5 \, \mathrm{mm} \times 1.5 \, \mathrm{mm}$ , resultando em um fator de qualidade de  $20.8 \, \mathrm{e}$  uma frequência de ressonância de  $0.99 \, \mathrm{GHz}$ .

**Paper IV.** Amplificador de potência de 25 dBm e 1 GHz integrado em CMOS para transferência de energia sem-fio [48].

CONFERÊNCIA: 2015 28th Symposium on Integrated Circuits and Systems Design (SBCCI).

RESUMO:Este artigo apresenta o projeto de um amplificador de potência integrado em uma tecnologia CMOS 180 nm, destinado a entregar potência a um acoplamento indutivo operando a 990 MHz. Uma topologia classe D é utilizada para evitar o uso de indutores. É proposta uma metodologia de projeto para encontrar a largura ótima dos transistores MOS, solucionando o compromisso entre a resistência das chaves e as capacitâncias de porta. A área total é de 1,5 mm², sendo que a maior parte é ocupada pelos pads e pelos largos metais de interconexão. Simulações pós-layout mostraram uma eficiência de 58% na entrega de 25,1 dBm para o indutor primário de um sistema WPT.

**Paper V.** Ampliação da frequência de operação do indutor para sistemas WPT otimamente acoplados [49].

CONFERÊNCIA: 2015 SBMO/IEEE MTT-S International Microwave Optoelectronics Conference (IMOC).

RESUMO: Este artigo apresenta uma técnica para estender a frequência de operação de um acoplamento indutivo utilizado para transferência de energia sem-fio. A ampliação é conseguida através da segmentação do indutor primário. Um circuito RLC é proposto para modelar o indutor quadrado de uma espira, servindo como base para o modelo do indutor segmentado. Estes modelos ajudam a compreender o funcionamento do indutor segmentado e

servem como guia para seu projeto. Um protótipo do acoplamento indutivo foi fabricado. O indutor primário tem um diâmetro médio de 22 mm e quatro segmentos, e o indutor secundário tem um diâmetro médio de 4 mm. É esperado que os dois indutores estejam otimamente acoplados para uma distância de 15 mm entre eles. O acoplamento indutivo foi constatado experimentalmente na frequência de 980 MHz, a qual é maior do que os 415 MHz medidos para um acoplamento convencional com as mesmas dimensões, enquanto a eficiência é mantida no mesmo valor de 30%.

### 1.4 ORGANIZAÇÃO DO DOCUMENTO

O restante desta tese está organizado conforme descrito a seguir.

Capítulo 2. São apresentados alguns conceitos que ajudam no entendimento dos acoplamentos indutivos. Primeiro, um circuito RLC é usado para descrever o comportamento elétrico do indutor planar de uma espira. Depois são estudados os efeitos da interação entre o indutor e os materias dispersivos. O tema da adaptação de impedâncias também é abordado já que ela influencia a eficiência na transferência de energia. Finalmente, são discutidas as considerações sobre a escolha da frequência de operação do acoplamento.

- Capítulo 3. Mostra a construção de um modelo de circuito que descreve a operação do acoplamento indutivo. Com base nesse modelo é proposta uma metodologia de projeto usando programação geométrica. Os resultados são verificados com simulações eletromagnéticas e experimentalmente. Também é apresentada uma solução para estender a frequência de operação do indutor primário usando indutores segmentados.

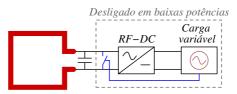

- **Capítulo 4.** Descreve o projeto e simulação de um receptor WPT completamente integrado na tecnologia CMOS. O receptor é concebido dentro de um sistema que pode ser testado sem nenhum contato com o receptor. Também é mostrado o projeto dos blocos funcionais.

- **Capítulo 5.** Mostra os resultados da fase de medição do sistema WPT envolvendo o receptor WPT completamente integrado na tecnologia CMOS. O capítulo começa com a proposta de uma metodologia para medir

as principais características de um ressonador LC integrado. Também é apresentada uma metodologia para medir a eficiência total do sistema WPT. Os resultados são comparados com os de outros trabalhos publicados.

**Capítulo 6.** Uma metodologia para o projeto do amplificador de potência que energiza o sistema WPT é apresentada. O amplificador de potência é projetado para ser integrado em tecnologia CMOS.

**Capítulo 7.** Resume as contribuições apresentadas na tese e discute alguns desdobramentos possíveis para pesquisas futuras.

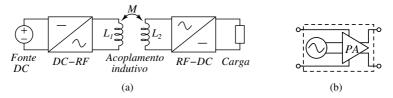

#### 2 FUNDAMENTOS SOBRE ACOPLAMENTOS INDUTIVOS

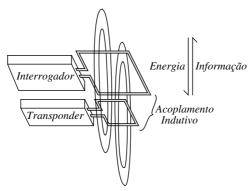

Uma tecnologia bastante conhecida que usa acoplamentos indutivos é a identificação por radiofrequência (RFID). Um sistema de RFID típico é esquematizado na Figura 5. Nele podem ser identificados três componentes principais: o interrogador, o transponder e o acoplamento indutivo. Outros componentes para implementar o acoplamento podem ser encontrados em sistemas de RFID, tais como capacitores ou antenas, contudo, esses componentes são pouco vantajosos no caso de sistemas implantados devido à forte atenuação do campo elétrico nos tecidos biológicos. O interrogador é encarregado de transmitir energia e dados ao transponder através do acoplamento indutivo, assim como receber e interpretar a informação contida na resposta do transponder. O transponder contém a informação de interesse, que no caso dos implantes pode ser um conjunto de dados medidos por algum sensor de parâmetros biológicos. O transponder deve ser capaz de capturar do acoplamento indutivo energia suficiente para seu funcionamento, inclusive para retornar uma resposta ao interrogador. Dado que o transponder deve ter um funcionamento minimalista, a resposta é geralmente informada a partir de um procedimento de modulação de carga também denominado "backscattering", que é fundamentado na modificação da impedância de entrada do transponder em função da informação que se deseja transmitir.

Nas próximas seções busca-se oferecer um aprofundamento sobre os componentes e conceitos mais relevantes concernentes ao uso dos acoplamentos indutivos. A Seção 2.1 explica o funcionamento dos indutores e a

Figura 5: Diagrama simplificado de um sistema de RFID.

forma como podem ser modelados eletricamente. A teoria envolvendo esses modelos permite prever a dependência do comportamento elétrico dos indutores com as caraterísticas do meio (permissividade elétrica  $\varepsilon$ , permeabilidade magnética  $\mu$ ), com a resistividade do condutor ( $\rho$ ) e com a geometria do indutor (diâmetro médio  $d_{avg}$ , largura de linha  $w_{ind}$  e distância entre os terminais do indutor  $\Delta_{ind}$ ). A Seção 2.2 apresenta as propriedades dos materiais dispersivos e sua interação com os indutores. Posteriormente é introduzido o conceito de adaptação de impedâncias do ponto de vista dos circuitos elétricos. Ao final do capítulo é discutida a escolha da frequência de operação para a transferência de energia.

#### 2.1 INDUTORES

Um indutor pode ser construído com uma trilha de metal formando uma malha de corrente como mostrado na Figura 6(a). Quando a corrente I atravessa a trilha de metal, ela gera uma quantidade de fluxo magnético  $\Phi$ . Simultaneamente, o fluxo magnético induz uma diferença de potencial (V) nos terminais do indutor conforme a equação de Faraday:

$$V = \frac{d\Phi}{dt} = \frac{d(LI)}{dt}$$

(2.1)

$$=L\frac{dI}{dt}. (2.2)$$

onde t é o tempo. Em (2.1), o fluxo magnético é considerado diretamente proporcional à corrente que o gerou. A constante de proporcionalidade L é denominada a indutância ou autoindutância. Assim, pode ser obtida a equação

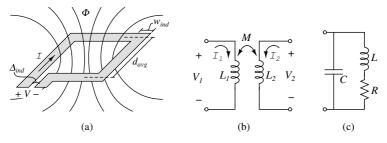

Figura 6: (a) Autoindutância. (b) Indutância mútua. (c) Indutor real.

2.1 Indutores 35

(2.2), que é usada para representar o comportamento elétrico de um indutor.

Quando dois indutores compartilham o fluxo magnético, obtém-se um acoplamento indutivo. Esse caso é representado pelo circuito da Figura 6(b). A tensão induzida nos terminais dos indutores é dada por (2.3) e (2.4). Cada equação contém dois termos: o primeiro devido às autoindutâncias  $L_1$  e  $L_2$ , e o segundo devido à indutância mútua  $M = k\sqrt{L_1L_2}$ , onde k é o fator de acoplamento magnético. A quantidade k pode ter valores entre 0 e 1, indicando a porção de fluxo magnético que é compartilhada pelos dois indutores. Por exemplo, k = 1 significa que todo o fluxo magnético é compartilhado pelos dois indutores, tal como acontece em um transformador ideal.

$$V_1 = L_1 \frac{dI_1}{dt} + M \frac{dI_2}{dt}$$

(2.3)

$$V_2 = L_2 \frac{dI_2}{dt} + M \frac{dI_1}{dt}.$$

(2.4)

Um indutor real pode ser modelado com o circuito da Figura 6(c). A resistência R(f) foi incluída para modelar a perda de energia no indutor em função da frequência f. O capacitor C serve para modelar o fenômeno de autoressonância do indutor. A frequência de autoressonância (SRF) acontece quando a metade do comprimento de onda efetivo do sinal que se propaga  $(\lambda_{eff}/2)$  é igual ao perímetro médio do indutor. No caso do indutor da Figura 6(a), essa condição pode ser escrita como

$$\frac{\lambda_{eff}}{2} \approx 4d_{avg}. (2.5)$$

Essa condição de ressonância é obtida do ponto de vista da onda que viaja ao longo da trilha. Alternativamente, a mesma ressonância é colocada no modelo elétrico da Figura 6(c), como a ressonância entre o indutor e o capacitor.

Os valores de indutância e a capacitância na Figura 6(c) podem ser modelados como constantes nas frequências menores do que a autoressonância, mas o valor da resistência apresenta variações significativas em função da frequência [49]. As perdas no indutor podem ser descritas por

$$R = R_{DC}F_{skin}F_r + R_{rad}, (2.6)$$

onde podem ser identificados quatro termos: a resistência DC ( $R_{DC}$ ); dois fatores  $F_{skin}$  e  $F_r$  modelando o efeito pelicular e o efeito de redistribuição radial da corrente no condutor, respectivamente; e a resistência de radiação  $R_{rad}$ . A

resistência DC pode ser aproximada como a resistência de um condutor de comprimento  $4d_{avg}$  e área de seção transversal  $w_{ind}t_c$ :

$$R_{DC} = \frac{\rho (4d_{avg})}{w_{ind}t_c},\tag{2.7}$$

onde  $t_c$  é a espessura do condutor. O fator do efeito pelicular é dado por (2.8) e (2.9) [50]:

$$F_{skin} = \frac{t_c}{2\delta} \frac{\sinh(t_c/\delta) + \sin(t_c/\delta)}{\cosh(t_c/\delta) - \cos(t_c/\delta)} \approx \frac{t_c}{2\delta}$$

(2.8)

$$\delta = \sqrt{\frac{\rho}{\pi f \mu}},\tag{2.9}$$

onde  $\delta$  é chamada de profundidade de efeito pelicular. A aproximação de  $F_{skin}$  para  $t_c/(2\delta)$  é válida quando  $t_c$  é muito maior do que  $\delta$ . Por outro lado, a corrente tem um perfil de distribuição na direção radial do indutor, ou seja, a densidade de corrente em um determinado ponto no condutor depende de sua distância até o centro do indutor. Esse perfil é diferente em altas frequências quando comparado com o perfil em DC, por esse motivo foi adicionado o fator  $F_r$  em (2.6). Como este efeito ainda não foi derivado analiticamente, pode ser usado o seguinte modelo empírico:

$$F_r = \alpha_r w_{ind}^{\beta_{r1}} f^{\beta_{r2}}, \tag{2.10}$$

onde  $\alpha_r$ ,  $\beta_{r2}$  e  $\beta_{r2}$  são parâmetros calculados a partir de simulações eletromagnéticas<sup>3</sup> de um conjunto de indutores. Para um conjunto de indutores (supondo uma tecnologia de circuito impresso convencional de cobre sobre FR4) com  $d_{avg}$  variando entre 4 mm e 30 mm, e  $w_{ind}$  variando entre 0,3 mm e 4,5 mm, os parâmetros resultantes são:  $\alpha_r = 128$ ,  $\beta_{r1} = 0$ ,3 e  $\beta_{r2} = -0$ ,1. A faixa de frequência simulada está entre 10 MHz e 10 GHz.

A resistência de radiação foi calculada em [51] para um indutor circular. A equivalência para o indutor quadrado pode ser feita considerando que os dois indutores devem ter o mesmo perímetro, ou seja, se o raio do indutor circular é  $r_c$  então  $2\pi r_c = 4d_{avg}$ , portanto  $r_c = 2d_{avg}/\pi$ . Finalmente, a resistência equivalente é mostrada em (2.11) e é composta por dois termos: o primeiro corresponde às perdas no condutor e o segundo às perdas

<sup>&</sup>lt;sup>3</sup>O software EMPRO foi usado para realizar simulações eletromagnéticas de onda completa com o método de elementos finitos (*Finite Element Method* - FEM).

2.1 Indutores 37

por radiação.

$$R = 256\sqrt{\pi\rho\mu} \, d_{avg} w_{ind}^{-0.7} f^{0.4} + \frac{128\pi}{3} \sqrt{\varepsilon^3 \mu^5} f^4 d_{avg}^4. \tag{2.11}$$

A autoindutância é calculada em [52]:

$$L = \frac{2d_{avg}\mu}{\pi} \ln\left(\frac{0.59\pi d_{avg}}{w_{ind}}\right). \tag{2.12}$$

A capacitância C é dada por (2.13), que é composta por dois termos: o primeiro corresponde à capacitância intrínseca  $C_{int}$ , que não depende de  $w_{ind}$ , e o segundo termo é a capacitância extrínseca  $C_{ext}$  que depende de  $w_{ind}$ ,  $d_{avg1}$  e  $\Delta_{ind}$ . A capacitância intrínseca é calculada considerando que a frequência de ressonância é  $1/\sqrt{LC}$  e que a velocidade da onda na trilha é  $1/\sqrt{\mu\varepsilon}$ . Para indutores com trilhas estreitas o valor de C é aproximadamente  $C_{int}$ .

$$C = C_{int} + C_{ext}(w_{ind}, d_{avg1}, \Delta_{ind})$$

(2.13)

$$C_{int} = \frac{(4d_{avg})^2 \mu \varepsilon}{\pi^2 L}.$$

(2.14)

O fator de perdas ( $\Lambda$ ) é igual a  $R/(2\pi fL)$ , ou seja, o recíproco do fator de qualidade do indutor. Usando (2.11) e (2.12) é possível calcular o valor de  $\Lambda$ :

$$\Lambda = 64\sqrt{\frac{\pi\rho}{\mu}} \frac{w_{ind}^{-0.7} f^{-0.6}}{\ln\left(\frac{0.59\pi d_{avg}}{w_{ind}}\right)} + \frac{32\pi}{3} \frac{\sqrt{\varepsilon^3 \mu^3} f^3 d_{avg}^3}{\ln\left(\frac{0.59\pi d_{avg}}{w_{ind}}\right)}.$$

(2.15)

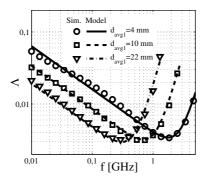

Analisando essa equação, pode ser visto que o primeiro termo é dominante em baixas frequências e tem uma caraterística decrescente com a frequência ( $f^{-0.6}$ ). O segundo termo é dominante para altas frequências e tem uma inclinação positiva ( $f^3$ ). Na Figura 7, o fator de perdas modelado com (2.15) é comparado com os valores obtidos em simulações eletromagnéticas feitas no software EMPRO da Keysight. Como pode ser observado, o modelo está bastante próximo dos resultados obtidos em simulação. O mínimo fator de perdas ( $\Lambda_{min}$ ) para cada indutor é calculado a partir de (2.15), fazendo com

Figura 7: Fator de perdas modelado comparado com simulações.

que  $\frac{\partial \Lambda}{\partial f} = 0$ . Esse ponto de mínimo acontece na frequência  $f_{\Lambda min}$ :

$$f_{\Lambda min} = \left(\frac{0,46 \,\rho}{\varepsilon^3 \mu^4 d_{avg}^6 w_{ind}^{1,4}}\right)^{1/7,2}.\tag{2.16}$$

É importante notar que  $f_{\Delta min}$  depende principalmente de  $d_{avg}$ ,  $\mu$  e  $\varepsilon$ . Substituindo (2.16) em (2.15) é possível obter

$$\Lambda_{min} = \frac{145,3}{\ln\left(\frac{0.59\pi d_{avg}}{w_{ind}}\right)} \left(\frac{\rho^5 \varepsilon^3 d_{avg}^6}{\mu^2 w_{ind}^7}\right)^{1/12},\tag{2.17}$$

que depende principalmente de  $(d_{avg}/w_{ind})$ ,  $\rho$ ,  $\varepsilon$  e  $\mu$ . Excluindo a escolha do valor de  $d_{avg}/w_{ind}$  que otimiza (2.17), o mínimo fator de perdas depende unicamente dos parâmetros da tecnologia. Por outro lado,  $f_{\Lambda min}$  é fortemente dependente de  $d_{avg}$ .

A indutância mútua entre duas espiras circulares coaxiais pode ser calculada com ajuda das funções elípticas  $K(\gamma)$  e  $E(\gamma)$  [53], onde  $\gamma$  é calculado conforme (2.19), em função do diâmetro dos indutores ( $d_{avg1}$  e  $d_{avg2}$ ) e da distância entre eles (d). A equação (2.18) foi adaptada para indutores quadrados a partir do valor obtido para os indutores circulares. A aproximação da forma circular para a forma retangular pode ser feita mantendo a mesma área envolvida pelo condutor para as espiras equivalentes. Por exemplo, se uma

Figura 8: Fator de acoplamento magnético quando  $d_{avg2} = 4$  mm.

espira tem raio  $r_c$ , então  $\pi r_c^2 = d_{avg}^2$ , portanto  $r_c = d_{avg}/\sqrt{\pi}$ .

$$M = \mu \sqrt{\frac{d_{avg1}d_{avg2}}{\pi}} \left[ \left( \frac{2}{\gamma} - \gamma \right) K(\gamma) - \frac{2}{\gamma} E(\gamma) \right]$$

(2.18)

$$\gamma = \sqrt{\frac{4d_{avg1}d_{avg2}}{(d_{avg1} + d_{avg2})^2 + \pi d^2}}$$

(2.19)

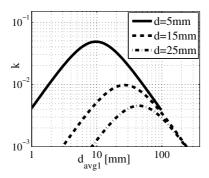

As curvas de  $k=M/\sqrt{L_1L_2}$  em função de  $d_{avg1}$  são plotadas na Figura 8 para três distâncias entre os indutores. Nesse caso, as dimensões do indutor secundário são  $d_{avg2}=4$  mm e  $w_{ind2}=0,5$  mm. Na figura podem ser identificados pontos de máximo para cada distância, permitindo concluir que para uma distância maior, maior será o diâmetro do indutor primário que maximiza o fator de acoplamento.

### 2.2 INTERAÇÃO ENTRE O INDUTOR E OS MATERIAIS DISPERSI-VOS

Na prática, o indutor nunca está isolado de outros materiais, o que implica que os valores de R, L e C, calculados na seção anterior, são modificados pelos materiais ao redor do indutor. No caso dos indutores feitos em placa de circuito impresso, o indutor está em contato direto com o substrato de FR4. Outro caso é aquele do indutor integrado na tecnologia CMOS, esse indutor está rodeado por dióxido de silício, e próximo a ele está o substrato de silício dopado. Um terceiro caso de material ao redor dos indutores são os tecidos

biológicos nos quais o implante está imerso. A análise da interação dos indutores com esses materiais começa com o estudo das propriedades elétricas dos materiais. Em seguida, são estudados de forma independente os efeitos dos materiais nos campos elétrico e magnético do indutor. A suposição de que os dois efeitos são independentes facilita a sua compreensão.

#### 2.2.1 Propriedades Elétricas dos Materiais

Uma forma comum de representar os campos harmônicos é apresentada em (2.20) e (2.21), onde as letras E e H denotam os campos elétrico e magnético respectivamente, sendo que as letras em negrito representam vetores e as letras normais representam magnitudes. De acordo com essa representação, a terceira e a quarta equações de Maxwell podem ser escritas como (2.22) e (2.23):

$$\mathbf{E} = Ee^{-j\omega t} \tag{2.20}$$

$$\mathbf{H} = He^{-j\omega t} \tag{2.21}$$

$$\nabla \times \mathbf{E} = -\mu \frac{\partial \mathbf{H}}{\partial t} = j\omega \mu \mathbf{H}$$

(2.22)

$$\nabla \times \mathbf{H} = \sigma \mathbf{E} + \varepsilon \frac{\partial \mathbf{E}}{\partial t} = (\sigma - j\omega \varepsilon) \mathbf{E}, \qquad (2.23)$$

onde  $\omega$  é a frequência angular e  $\sigma$  é a condutividade elétrica. O fator que multiplica  ${\bf E}$  em (2.23) é formado por duas componentes: o termo proporcional a  $\sigma$ , que representa a corrente de cargas livres, e o termo proporcional a  $j\omega\varepsilon$ , que corresponde à corrente de deslocamento. No caso de um material dielétrico ideal, o valor de  $\sigma$  é nulo e o valor de  $\varepsilon$  é uma quantidade real independente da frequência. No entanto na prática, todos os materiais apresentam uma permissividade complexa e variante com a frequência. Por causa dessa caraterística, os materiais são denominados dispersivos. O termo foi adotado porque a velocidade de propagação da luz nesses materiais varia com a frequência. Uma nova quantidade, a permissividade relativa equivalente  $\varepsilon_r(\omega)$ , é obtida reescrevendo (2.23) como (2.24). Desta forma, o valor de  $\varepsilon_r(\omega)$  é dado por (2.25).

$$\nabla \times \mathbf{H} = -j\omega \varepsilon_r \varepsilon_0 \mathbf{E} \tag{2.24}$$

$$\varepsilon_r(\omega) = \frac{\varepsilon}{\varepsilon_0} + j\frac{\sigma}{\omega\varepsilon_0},$$

(2.25)

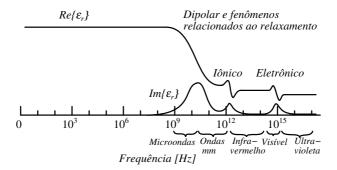

Figura 9: Resposta em frequência das partes real e imaginária da permissividade para um dielétrico hipotético, mostrando vários fenômenos que contribuem [51].

onde  $\varepsilon_0$  é a permissividade elétrica no vácuo. Deve-se notar que somente a parte imaginária de  $\varepsilon_r$  é responsável pela dissipação de energia no material. Os efeitos de  $\sigma$  e da parte imaginária de  $\varepsilon$  estão somados na parte imaginária de  $\varepsilon_r$ . A Figura 9 mostra a resposta em frequência das partes real e imaginária da permissividade em um dielétrico hipotético. Para baixas frequências, o dielétrico apresenta uma permissividade aproximadamente real e constante. Nesse caso, os dipolos elétricos no material conseguem acompanhar a variação na direção do campo elétrico. Quando a frequência aumenta, o efeito de relaxamento se torna significativo, o que quer dizer que o movimento dos dipolos não consegue acompanhar as mudanças na direção do campo elétrico. Qualquer deslocamento da nuvem de carga em torno do seu centro, produz uma força restauradora. A interação dessa força restauradora com a inércia da nuvem de carga em movimento produz uma ressonância como em um sistema mecânico mola-massa [51]. Outros tipos de ressonância no nível iônico e eletrônico acontecem em frequências maiores. Perto de cada ressonância, a parte da permissividade que causa as perdas apresenta um pico. A contribuição para a parte real de  $\varepsilon_r$  a partir de uma dada ressonância, assim como na reatância de um circuito LC sintonizado, mostra picos opostos em ambos os lados da ressonância.

A escolha dos modelos para os materiais usados na simulação eletromagnética depende do tipo de material e da faixa de frequências de interesse. O substrato das placas de circuitos impressos é de FR4, o qual está incluído nas bibliotecas padrão do programa de simulação eletromagnética EMPRO. O modelo do FR4 apresenta um valor de  $\varepsilon = 4,6\varepsilon_0$  e um valor de

$\sigma=0,0026$  S/m. No caso do substrato da tecnologia de integração CMOS, o material é silício dopado tipo P com  $\varepsilon=11,9\varepsilon_0$  e  $\sigma=7,41$  S/m. Os dielétricos usados para isolar as camadas de metal no chip são feitos de óxido de silício com  $\varepsilon\approx4,1\varepsilon_0$  e  $\sigma\approx0$ . O modelo usado nos materiais referidos é simples, dado que inclui somente um valor de permissividade constante real e um valor de condutividade. Porém, no caso dos tecidos biológicos é necessário usar um modelo mais complexo.

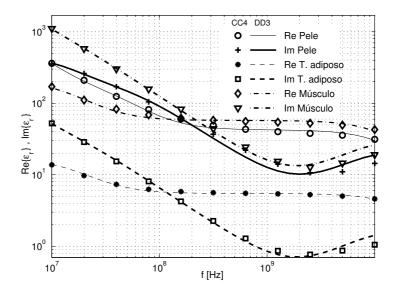

Em [54] foram caraterizados vários tecidos biológicos usando o modelo Cole-Cole de 4 polos, correspondente a (2.26) [55, 56]. No modelo, n é o número de polos,  $\varepsilon_{\infty}$  é a permissividade quando a frequência tende ao infinito,  $\Delta\varepsilon_n$  é a mudança no valor da permissividade introduzida por cada polo,  $\alpha_n$  indica a forma da transição em cada polo, e  $\tau_n$  é a constante de tempo de relaxação associada a cada polo. Esses dados foram ajustados ao modelo Debye-Drude de 3 polos para serem usados no simulador eletromagnético EMPRO. O Modelo Debye-Drude é o caso particular de (2.26) em que  $\alpha_n = 0$ . O ajuste dos dados foi feito na faixa de frequências entre 10 MHz e 10 GHz, o resultado do ajuste é mostrado na Figura 10 para a pele, o tecido adiposo e o músculo.

$$\varepsilon_r(\omega) = \varepsilon_\infty + \sum_n \frac{\Delta \varepsilon_n}{1 + (j\omega \tau_n)^{(1-\alpha_n)}} + j\frac{\sigma}{\omega \varepsilon_0}.$$

(2.26)

De acordo com a Figura 10, o tecido adiposo apresenta permissividade relativa equivalente muito menor que os outros dois tecidos na faixa de frequências analisada. Isto significa que o seu comportamento elétrico está mais próximo de um isolante, portanto a maior parte das perdas estão concentradas na pele e no músculo. Na prática, a maior parte das perdas está concentrada na pele devido às características do tecido e à proximidade do indutor transmissor.

# 2.2.2 Interação entre o Campo Elétrico do Indutor e o Material ao seu Redor

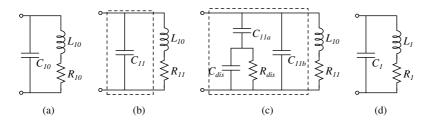

Considerando o modelo do indutor rodeado com ar como sendo aquele apresentado na Figura 11(a). O fato do indutor estar perto de um material dielétrico ideal ( $\sigma=0$ ) muda o valor da permissividade ( $\varepsilon$ ) usado para calcular a capacitância do modelo, conforme (2.13) e (2.14). Essa variação muda a capacitância do modelo como mostrado na Figura 11(b). A nova capacitância  $C_{11}$  deve ser maior do que a original  $C_{10}$ , indicando assim uma diminuição na

Figura 10: Permissividade relativa nos modelos Cole-Cole 4 polos (CC4) [54] e Debye-Drude 3 polos (DD3).

frequência de autoressonância. Outro componente do modelo que muda é a resistência, o novo valor  $(R_{11})$  deve ser maior que o original, pois a resistência de radiação depende do valor de  $\varepsilon$ .

Quando o indutor é colocado próximo ao material dispersivo, uma parte das linhas de campo elétrico associadas ao indutor entra em contato com o material. Esse campo elétrico no material gera correntes proporcionais a  $j\omega\varepsilon_r\varepsilon_0$ . O fenômeno como um todo pode ser modelado acrescentando três componentes ao modelo do indutor como mostrado na Figura 11(c). A capacitância  $C_{11}$  foi dividida entre  $C_{11a}$  e  $C_{11b}$  para modelar as linhas de campo que entram no material e as que não entram, respectivamente. Essa divisão depende da distância entre o indutor e o material dispersivo, quanto menor a distância, maior o valor de  $C_{11a}$ . Um maior valor de  $C_{11a}$  significa que há uma maior interação entre o campo elétrico e o material, consequentemente a potência dissipada no material é maior também. As correntes no material estão representadas pela resistência  $R_{dis}$  e pela capacitância  $C_{dis}$  no modelo da Figura 11(a). O circuito da Figura 11(c) é reduzido ao circuito da Figura 11(d) para uma determinada faixa de frequências. Em resumo, a interação com o campo elétrico, principalmente, deve diminuir a frequência de autores-

Figura 11: Modelo do indutor: (a) Isolado no ar. (b) Próximo a um material dielétrico ideal ( $\sigma=0$ ). (c) Rodeado de material dispersivo. (d) Circuito equivalente em uma faixa de frequências determinada.

Figura 12: (a) Correntes parasitas geradas no material. (b) Modelo do indutor incluindo correntes parasitas no material dispersivo. (c) Modelo reduzido.

sonância do indutor e aumentar as perdas.

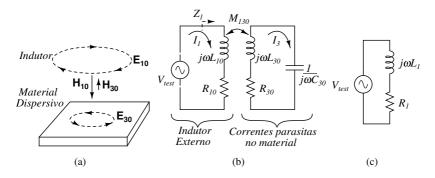

# 2.2.3 Interação entre o Campo Magnético do Indutor e o Material ao seu Redor