## UNIVERSIDADE FEDERAL DE SANTA CATARINA DEPARTAMENTO DE PÓS-GRADUAÇÃO

Daniel Körbes

# INVERSOR MULTINÍVEL SIMÉTRICO HÍBRIDO MODIFICADO

Florianópolis

2012

#### Daniel Körbes

# INVERSOR MULTINÍVEL SIMÉTRICO HÍBRIDO MODIFICADO

Dissertação submetida ao Programa de Pós-graduação em Engenharia Elétrica para a obtenção do Grau de Mestre em Engenharia Elétrica.

Orientador: Prof. Samir Ahmad Mussa, Dr.

Florianópolis

2012

#### Catalogação na fonte pela Biblioteca Universitária da Universidade Federal de Santa Catarina

#### K84i Körbes, Daniel

Inversor multinível simétrico híbrido modificado [dissertação] / Daniel Körbes ; orientador, Samir Ahmad Mussa. - Florianópolis, SC, 2012. 164 p.: il., tabs.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia Elétrica.

Inclui referências

1. Engenharia elétrica. 2. Inversores elétricos. I. Mussa, Samir Ahmad. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

CDU 621.3

#### Daniel Körbes

# INVERSOR MULTINÍVEL SIMÉTRICO HÍBRIDO MODIFICADO

Esta Dissertação foi julgada aprovada para a obtenção do Título de "Mestre em Engenharia Elétrica", e aprovada em sua forma final pelo Programa de Pós-graduação em Engenharia Elétrica.

|         | Florianópolis, 23 de abril 2012.                    |  |

|---------|-----------------------------------------------------|--|

|         | Prof. Patrick Kuo Peng, Dr.<br>Coordenador do Curso |  |

| Banca E | Examinadora:                                        |  |

|         |                                                     |  |

|         | Prof. Samir Ahmad Mussa, Dr.<br>Orientador          |  |

|         |                                                     |  |

|         | Prof. Yales Rômulo Novaes, Dr.                      |  |

|         |                                                     |  |

|         | Prof. Denizar Cruz Martins, Dr.                     |  |

#### AGRADECIMENTOS

Agradeço inicialmente a meus pais, Patrício e Roswitha, pelo apoio, incentivo e afeto incondicionais. A meu irmão André, pela motivação e inspiração para a minha continuidade nos estudos. A Ana Carolina, por ser uma real companheira ao final da jornada, por toda sua compreensão e apoio.

Ao corpo docente e técnico do INEP-UFSC, de excelentíssima qualidade. Sempre pronto a transmitir conhecimento em qualquer situação.

Aos colegas de estudo, mestrandos e doutorandos: Alessandro Batschauer, André Lange, Bruno Nora, Daniel Collier, Daniel Flores, Felipe Tureck, Joselito Heerdt, Márcio Ortmann nas incontáveis horas de estudo e dedicação compartilhadas no INEP.

O estudo em geral, a busca da verdade e da beleza são domínios em que nos é consentido ficar crianças toda a vida.

Albert Einstein

#### RESUMO

Este trabalho apresenta o estudo de uma nova topologia de inversor multinível e suas variações, baseado no inversor híbrido simétrico descrito em (RUIZ-CABALLERO et al., 2010b), fazendo uso de técnicas de modulação já difundidas e também de uma técnica hibrida de modulação para essas estruturas. As topologias e modulações são comparadas entre si, donde a estrutura e modulação que obteve os melhores resultados numéricos e simulados foi implementada para obtenção de resultados experimentais. A parte experimental fez uso de técnicas de descrição de hardware (VHDL) para implementação dos moduladores necessários em controladores programáveis (FPGA´s).

Palavras-chave: Inversor multinível, Modulação híbrida, FPGA.

#### ABSTRACT

This work shows a novel multilevel topology and its variations, based on the symetrical hibrid multilevel described at (RUIZ-CABALLERO et al., 2010b), using already known modulation technics and also a new proposed one. These topologies and modulation technics were compared and the best ones were chosen to be prototyped, where was obtained the experimental results. This prototype uses hardware description language (VHDL) for the modulators in a programable device (FPGA) **Keywords:** Multilevel inverter, Hybrid Modulation, FPGA.

## LISTA DE FIGURAS

| Figura 1 Motor de induçã   | o usado em moinho de bolas na indústria             |

|----------------------------|-----------------------------------------------------|

| de mineração (6500kW, $13$ | 800V). Fonte: Catálogo Weg                          |

| Figura 2 Trolebus na Esp   | panha. Fonte: Associação Brasileira do              |

| Veículo Elétrico           |                                                     |

|                            | Configuração monofásica (a) e trifásica             |

| ` '                        | 3                                                   |

| Figura 4 Forma de onda o   | das tensões $v_o, v_{ref}, e v_{ab}$ 3:             |

| 9                          | cas do inversor NPC. Monofásica (a) e 3:            |

| ` '                        | das tensão nas configurações monofásica             |

| (a) e trifásica (b)        | 3: 3:                                               |

| Figura 7 Topologia Flying  | g Capactor de 3 níveis 3                            |

| Figura 8 Células usadas i  | no conversores cascata. (a) Ponte com-              |

| pleta e (b)Meia ponte      |                                                     |

| Figura 9 Ilustração de con | nversor cascata                                     |

| Figura 10 Célula da topolo | ogia MMC 38                                         |

| Figura 11 Estruturas do co | nversor ANPC. (a)Mono e (b) Trifásica. 39           |

| Figura 12 Organização das  | técnicas de modulação para conversores              |

| multiníveis                | 43                                                  |

| Figura 13 Topologia VSI    | 4                                                   |

| Figura 14 Diagrama de vet  | tores do VSI                                        |

| Figura 15 Sequência de con | mutação escolhida para $\vec{V_{ref}}$ 4            |

| Figura 16 Exemplo de um    | modulador genérico 4                                |

| Figura 17 Exemplo dos per  | ríodos para definição de $D$ 4                      |

| Figura 18 Exemplos das ar  | mplitudes para definição de $M$ 4                   |

| Figura 19 Exemplo da disp  | osição das portadoras e da moduladora. 5            |

| _                          | ranjos das portadoras com deslocamento $DD e(c)POD$ |

| , , , , , ,                | M naturalmente amostrada 5                          |

|                            | ostragem simples 50                                 |

| -                          | ostragem dupla 5                                    |

| -                          | 3 níveis 59                                         |

| O .                        | a célula de comutação. (b) Substituição             |

| dos interruptores                                                                                                                                   | 60  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 26 Tensão obtida em $V_{ab}$                                                                                                                 | 60  |

| Figura 27 Inversor 5 níveis                                                                                                                         | 61  |

| Figura 28 $V_L$ 5 níveis                                                                                                                            | 61  |

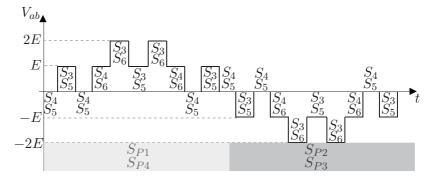

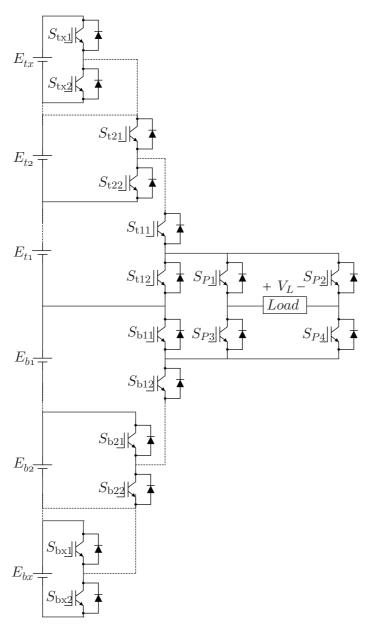

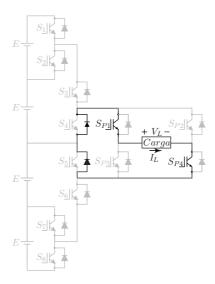

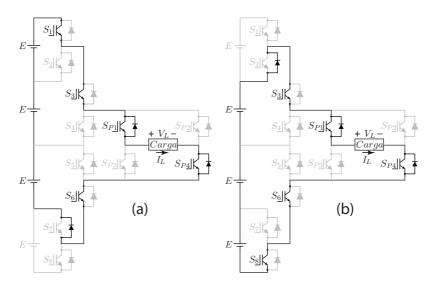

| Figura 29 Topologias propostas 7 níveis                                                                                                             | 62  |

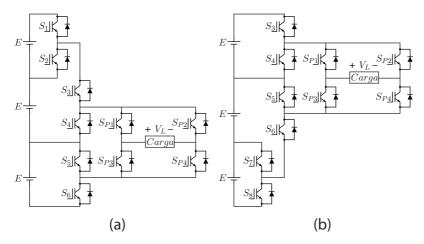

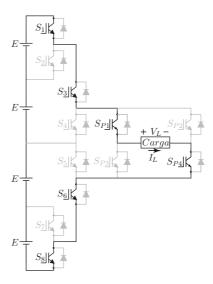

| Figura 30 Topologia proposta 9 níveis                                                                                                               | 63  |

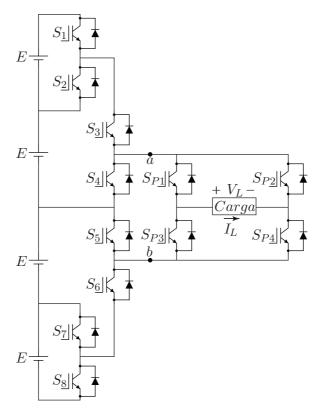

| Figura 31 Topologia sugerida para "N"níveis                                                                                                         | 64  |

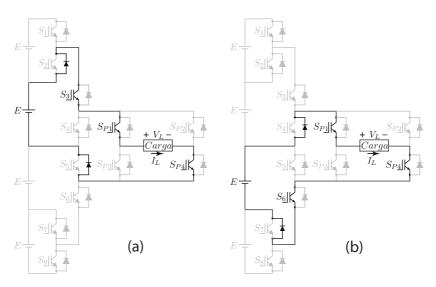

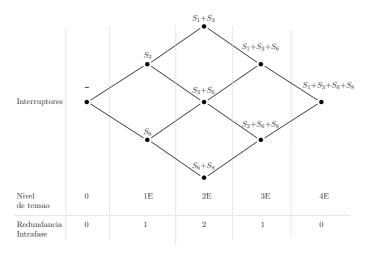

| Figura 32 Primeira etapa de funcionamento                                                                                                           | 67  |

| Figura 33 Estados topológicos referentes a segunda etapa de funcionamento. (a) $S_3$ conduzindo. (b) $S_6$ conduzindo                               | 68  |

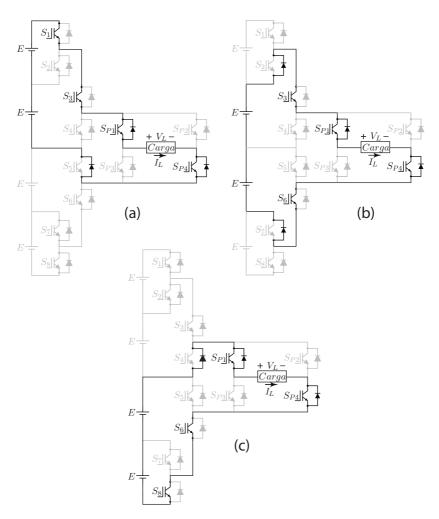

| Figura 34 Estados topológicos referentes a terceira etapa de funcionamento. (a) $S_1$ e $S_3$ conduzindo. (b) $S_3$ e $S_6$ conduzindo. (c) $S_6$ e |     |

| $S_8$ conduzindo                                                                                                                                    | 69  |

| Figura 35 Estados topológicos referentes a quarta de funcionamento. (a) $S_1,S_3$ e $S_6$ conduzindo. (b) $S_3,S_6$ e $S_8$ conduzindo              | 70  |

| Figura 36 Estado topológico referente a quinta etapa de funciona-                                                                                   |     |

| mento                                                                                                                                               | 71  |

| Figura 37 Demonstração Redundância de níveis                                                                                                        | 72  |

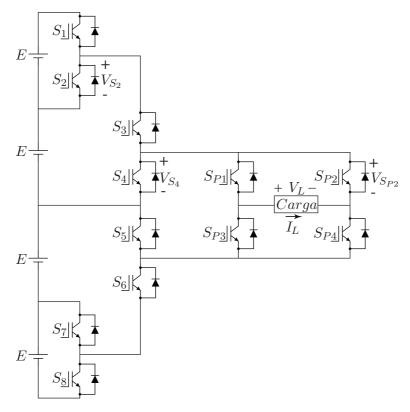

| Figura 38 Topologia com definição das referências de tensões sobre                                                                                  |     |

| os componentes.                                                                                                                                     | 74  |

| Figura 39 Mapa de vetores completo                                                                                                                  | 76  |

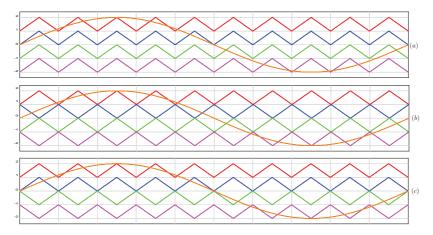

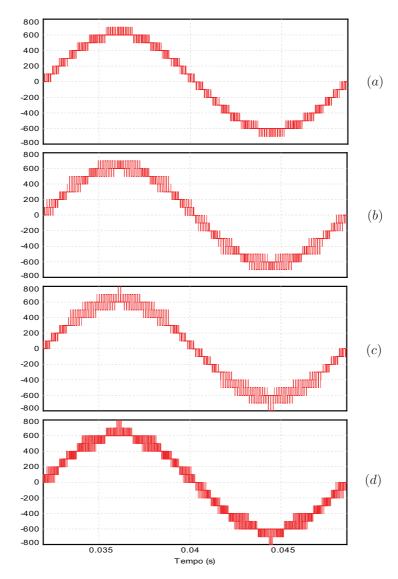

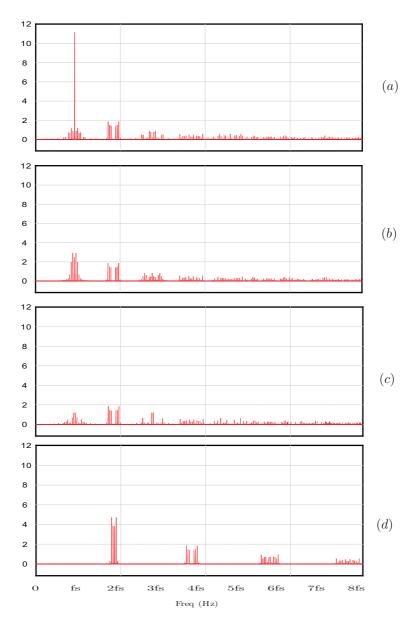

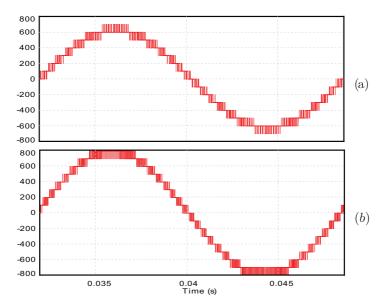

| Figura 40 Formas de onda da tensão de saída para as modulações testadas. (a)IPD, (b)APOD, (c)POD e (d)H                                             | 83  |

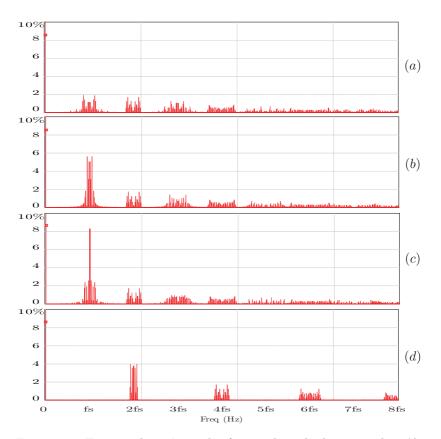

| Figura 41 Espectro harmônico das formas de onda da tensão de                                                                                        |     |

| saída para as modulações testadas. (a)IPD, (b)APOD, (c)POD e                                                                                        | ~ ~ |

| (d)H                                                                                                                                                | 85  |

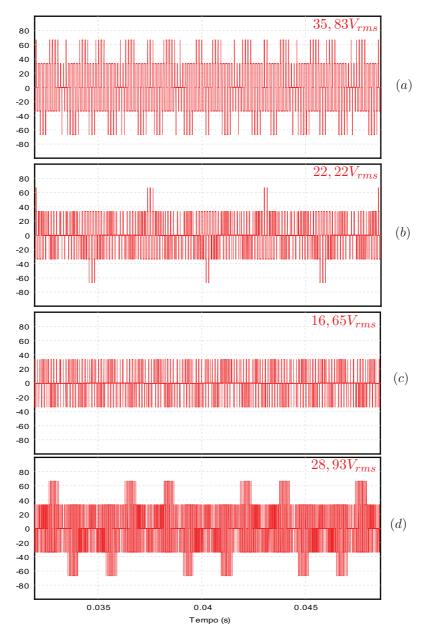

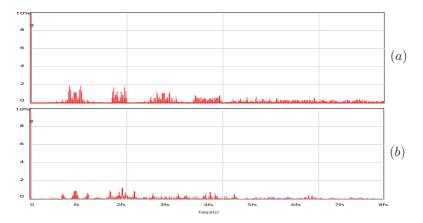

| Figura 42 Tensões de modo comum para as modulações: (a)IPD, (b)APOD, (c)POD e (d)H                                                                  | 87  |

| Figura 43 Espectros normalizados pela tensão de barramento das                                                                                      |     |

| formas de onda geradas segundo as técnicas: (a)IPD, (b)APOD, (c)POD e (d)H                                                                          | 89  |

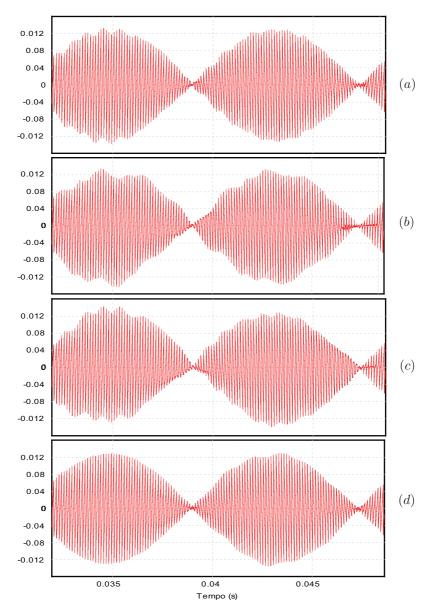

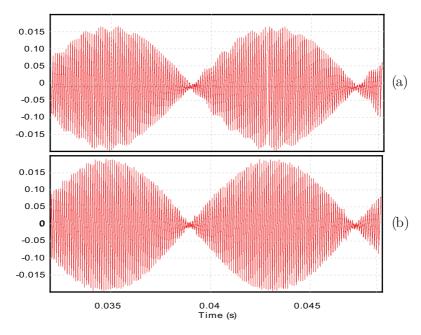

| Figura 44 Ondulações das correntes de carga geradas pelas técnicas: (a)IPD, (b)APOD, (c)POD e (d)H                                                  | 91  |

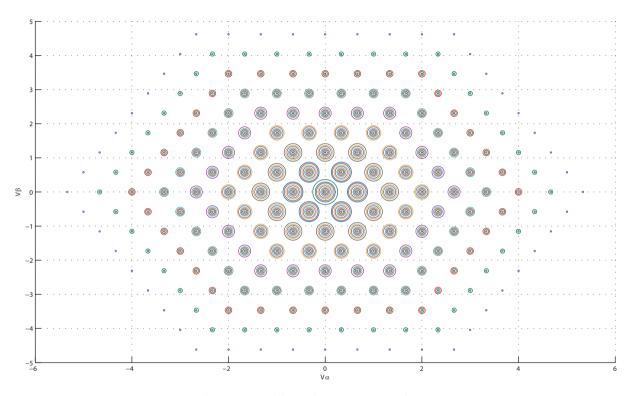

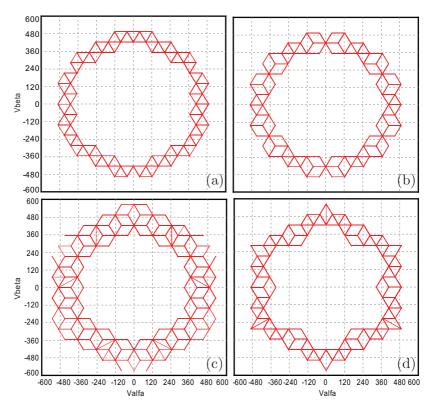

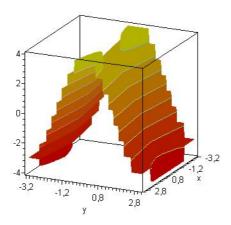

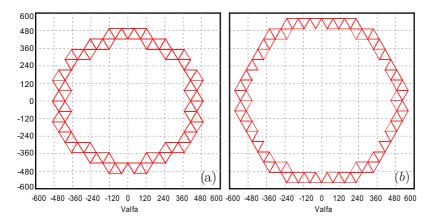

| Figura 45 Planos $\alpha\beta$ gerados pelas técnicas: (a)IPD, (b)APOD, (c)POD e (d)H                                                               | 93  |

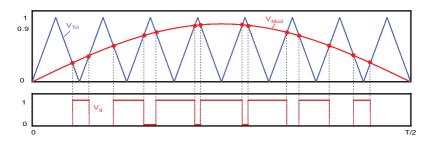

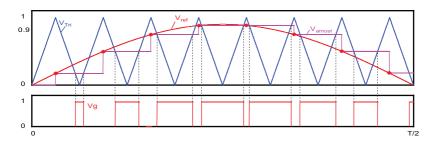

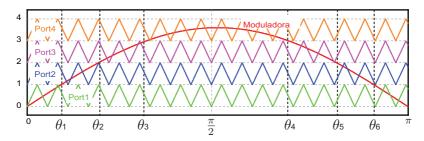

| Figura 46 Forma de onda da moduladora e das portadoras para um                                                                                      |     |

| período da moduladora                                                                                                                               | 95  |

| Figura 47 Célula unitária obtida da topologia proposta usando técnica de modulação IPD                                  |

|-------------------------------------------------------------------------------------------------------------------------|

| Figura 48 Representação da tensão de saída obtida através das                                                           |

| rigura 40 Representação da tensão de salda obtida atraves das células unitárias através da modulação IPD com $M = 0,9,$ |

| Figura 49 Representação gráfica da forma de onda da tensão de                                                           |

| saída do inversor quando $f_c/f_o = 1$                                                                                  |

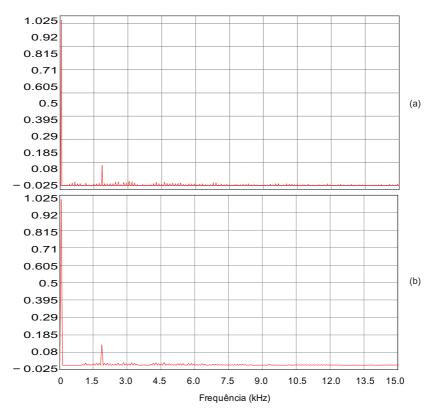

| Figura 50 Componentes harmônicas obtidas por simulação (a) e                                                            |

| calculadas (b) para a forma de onda de tensão                                                                           |

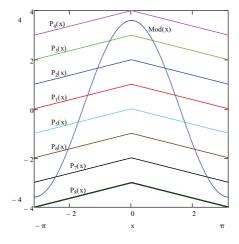

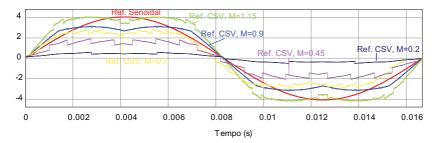

| Figura 51 Apresentação das referências calculadas para diversos                                                         |

| índices de modulação de amplitude comparadas com a referência                                                           |

| senoidal                                                                                                                |

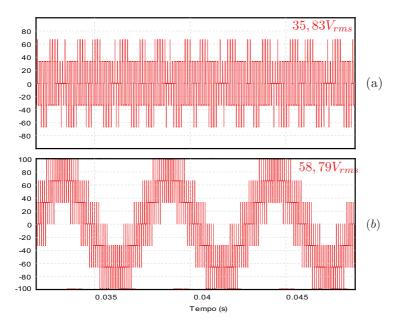

| Figura 52 Comparativo das simulações das tensões de linha para                                                          |

| as técnicas (a)<br>IPD e (b)<br>CSVPWM101                                                                               |

| Figura 53 Espectro harmônico simulado das tensões de linha para                                                         |

| as técnicas (a)IPD e (b)CSVPWM101                                                                                       |

| Figura 54 Tensões de modo comum geradas por (a) técnica IPD e                                                           |

| (b) técnica CSVPWM                                                                                                      |

| Figura 55 Ondulação de corrente                                                                                         |

| Figura 56 Comparativo da utilização dos vetores no plano $\alpha\beta$ para                                             |

| as técnicas (a)<br>IPD e (b)<br>CSVPWM104                                                                               |

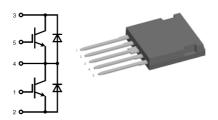

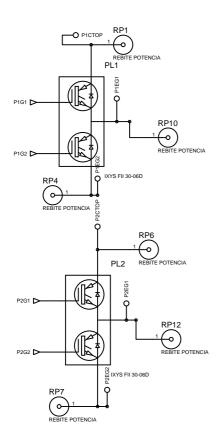

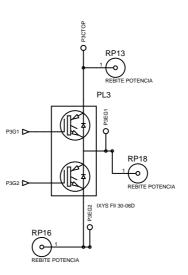

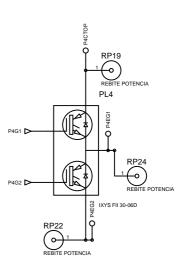

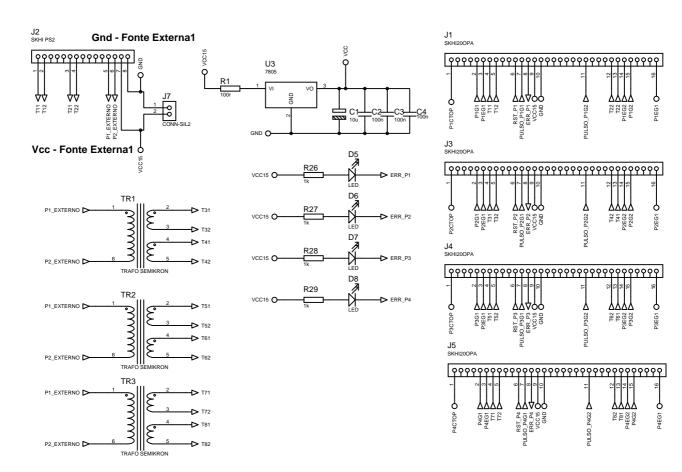

| Figura 57 Montagem do componente FII 30-06D da IXYS 106                                                                 |

| Figura 58 Módulo de potência da plataforma de testes107                                                                 |

| Figura 59 Ângulos de intersecção entre moduladora e portadoras. $108$                                                   |

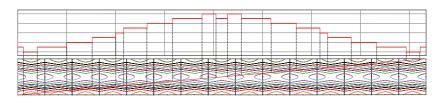

| Figura 60 Funções de comutação                                                                                          |

| Figura 61 Kit de desenvolvimento FPGA Cyclone III da Altera®.114                                                        |

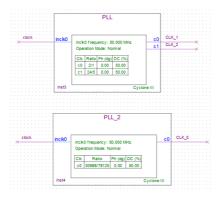

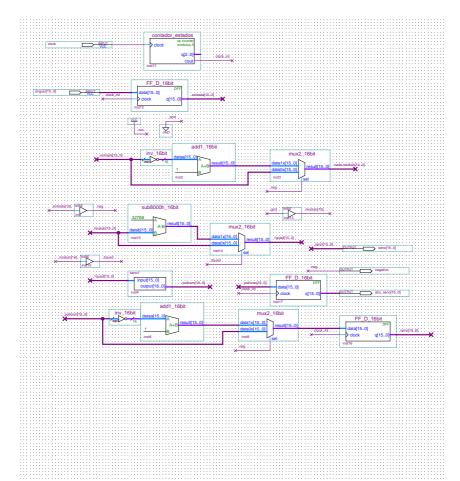

| Figura 62 Blocos PLL da descrição de hardware114                                                                        |

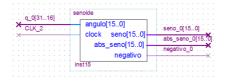

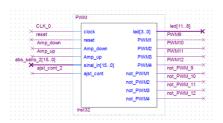

| Figura 63 Bloco contador do ângulo para senoide114                                                                      |

| Figura 64 Bloco multiplicador                                                                                           |

| Figura 65 Bloco que gera a senoide                                                                                      |

| Figura 66 Bloco gera o gatilho                                                                                          |

| Figura 67 Protótipo de testes, englobando os módulos de potência,                                                       |

| fontes isoladas e dispositivo programável117                                                                            |

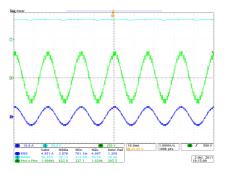

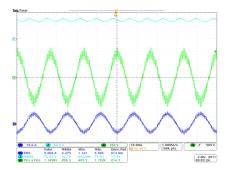

| Figura 68 Formas de onda experimentais obtidas com a técnica de                                                         |

| modulação IPD117                                                                                                        |

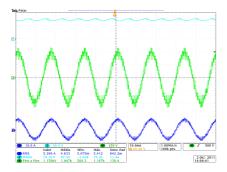

| Figura 69 Formas de onda experimentais obtidas com a técnica de                                                         |

| modulação APOD118                                                                                                       |

| Figura 70 Formas de onda experimentais obtidas com a técnica de |

|-----------------------------------------------------------------|

| modulação POD118                                                |

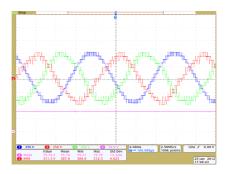

| Figura 71 Formas de onda experimentais obtidas com a técnica de |

| modulação H                                                     |

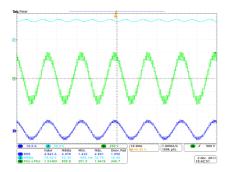

| Figura 72 Senoides formadas pela topologia usando a técnica de  |

| modulação IPD                                                   |

## LISTA DE TABELAS

| Tabela 1 Res     | sumo sobre inversores multiníveis. Aqui "n" repre-                                                                        |    |

|------------------|---------------------------------------------------------------------------------------------------------------------------|----|

| senta o númer    | o de níveis desejado :                                                                                                    | 39 |

| Tabela 2 Vet     | ores Resultantes, Interruptores comandados e Tensão                                                                       |    |

| aplicada a carg  | ga                                                                                                                        | 15 |

| Tabela 3 Est     | ados de condução                                                                                                          | 66 |

| Tabela 4 Est     | ruturas usuais, características para 9 níveis, por fase 7                                                                 | 72 |

| Tabela 5 Cor     | mbinações válidas 7                                                                                                       | 75 |

| modulação usa    | sultados da computação da THD de cada técnica de ando referência puramente senoidal, conforme o índice de amplitude $M_a$ | 36 |

| de modulação     | sultados da computação da WTHD de cada técnica usando referência puramente senoidal, conforme o ulação de amplitude $M_a$ | 36 |

|                  | sultados da computação da THD para as técnicas IPD10                                                                      | )2 |

|                  | sultados da computação da WTHD para as técnicas10                                                                         | )2 |

|                  | mparativo entre resultados calculados e simulados os de corrente na topologia proposta, valores de cor-                   |    |

| rente em $rms$ . |                                                                                                                           | 2  |

| modulação usa    | sultados experimentais da THD de cada técnica de ando referência puramente senoidal, conforme o índice                    |    |

|                  | de amplitude $M_a$                                                                                                        | .9 |

|                  | sultados experimentais da WTHD de cada técnica de ando referência puramente senoidal, conforme o índice                   |    |

|                  | de amplitude $M_a$                                                                                                        | 19 |

|                  | r                                                                                                                         | _  |

## LISTA DE ABREVIATURAS E SIGLAS

| ABVE   | Associação Brasileira de Veículos Elétricos       | 30 |

|--------|---------------------------------------------------|----|

| AC     | Alternate Current                                 | 30 |

| AM     | Amplitude Modulation                              | 30 |

| APOD   | Alternate Phase Opposition Disposition            | 30 |

| CHB    | Cascaded H-Bridge                                 | 30 |

| CSVPWN | Mentered Space Vectored Pulse Width Modulation    | 30 |

| DC     | Direct Current                                    | 30 |

| DSP    | Digital Signal Processor                          | 30 |

| FM     | Frequency Modulation                              | 30 |

| FPGA   | Field Programmable Gate Array                     | 30 |

| GTO    | Gate Turn-Off thyristor                           | 30 |

| IGBT   | Insulated Gate Bipolar Transistor                 | 30 |

| IGCT   | Integrated Gate-Commutated Thyristor              | 30 |

| IPD    | In-Phase Disposition                              | 30 |

| MOSFET | Metal Oxide Semiconductor Field-Effect Transistor | 30 |

| MTBF   | Mean Time Between Fail                            | 30 |

| NPC    | Neutral Point Clamped                             | 30 |

| PD     | Phase Disposition                                 | 30 |

| POD    | Phase Opposition Disposition                      | 30 |

| PWM    | Pulse Width Modulatio                             | 30 |

| SHE    | Selective Harmonic Elimination                    | 30 |

| SPWM   | Senoidal Pulse Width Modulation                   | 30 |

| SVM    | Space Vector Modulation                           | 30 |

| THD    | Total Harmonic Distortion                         | 30 |

| UPS    | Uninterruptable Power Supply                      | 30 |

| WTHD   | Weighted Total Harmonic Distortion                | 30 |

| SI     | Sistema Internacional de unidades1                | 21 |

# LISTA DE SÍMBOLOS

| $a_x$          | Amplitude de componente espectral par          | $\dots 121$ |

|----------------|------------------------------------------------|-------------|

| $b_x$          | Amplitude de componente espectral impar        | 121         |

| E              | Tensão de barramento                           | 121         |

| $V_x$          | Tensão de fase                                 | 121         |

| $V_{xy}$       | Tensão de linha                                | 121         |

| $\lambda$      | Comprimento de onda                            | 121         |

| c              | Velocidade da luz                              | 121         |

| $T_x$          | Período                                        | 121         |

| $M_a$          | Índice de modulação de amplitude               | 121         |

| $M_f$          | Índice de modulação de frequência              | 121         |

| $S_x$          | Denominação de interruptor                     | 121         |

| $f_x$          | Frequências envolvidas                         | 121         |

| $I_{S_x}$      | Corrente de interruptor                        | 121         |

| $\delta_{S_x}$ | Função de comutação de interruptor             | 121         |

| $\theta_x$     | Angulo de intersecção das funções de comutação | 121         |

|                |                                                |             |

# SUMÁRIO

| 1 INTRODUÇÃO                                           |   |

|--------------------------------------------------------|---|

| 2 TOPOLOGIAS DE INVERSORES MULTINÍVEIS .               |   |

| 2.1 INVERSOR NPC                                       |   |

| 2.2 INVERSOR FLYING CAPACITOR                          |   |

| 2.3 INVERSOR CASCATA                                   |   |

| 2.4 INVERSOR CASCADED HÍBRIDOS OU ASSIMÉTRICOS         | 5 |

| 2.5 INVERSOR MMC                                       |   |

| 2.6 INVERSOR ANPC                                      |   |

| 2.7 CONCLUSÃO                                          |   |

| 3 MODULAÇÃO                                            |   |

| 3.1 TÉCNICAS CONHECIDAS                                |   |

| 3.1.1 Modulação Vetorial                               |   |

| <b>3.1.2</b> Controle Vetorial                         |   |

| 3.1.3 PWM de múltiplas portadoras                      |   |

| 3.1.3.1 PWM com deslocamento de fase                   |   |

| 3.1.3.2 PWM com deslocamento de nível                  |   |

| 3.1.4 Modulação Híbrida                                |   |

| 3.1.5 Eliminação Seletiva de Harmônicos                |   |

| 3.1.6 Controle de Nível de Tensão                      |   |

| 3.2 SOBREMODULAÇÃO                                     |   |

| 3.3 APLICAÇÃO DIGITAL                                  |   |

| 3.4 CONCLUSÃO                                          |   |

| 4 TOPOLOGIAS PROPOSTAS                                 |   |

| 4.1 FORMAÇÃO DAS TOPOLOGIAS                            |   |

| 4.2 MODOS DE FUNCIONAMENTO                             |   |

| 4.3 CARACTERÍSTICAS DA TOPOLOGIA                       |   |

| 4.4 CONCLUSÃO                                          |   |

| 5 MODULAÇÃO PROPOSTA E SIMULAÇÃO                       |   |

| 5.1 MODULAÇÕES PROPOSTAS                               |   |

| 5.1.1 Forma de onda da tensão de linha                 |   |

| 5.1.2 Espectro harmônico da tensão de linha            |   |

| 5.1.3 Tensão de modo comum gerada                      |   |

| 5.1.4 Ondulação de corrente                            |   |

| 5.1.5 Uso dos vetores adequados no plano $\alpha\beta$ |   |

| 5.2 ANÁLISE DA MODULAÇÃO                               |   |

| 5.3 MODULAÇÃO CSVPWM                                   |   |

| 5.4 CONCLUSÃO                                          |   |

| 6 PROJETO DO INVERSOR E RESULTADOS EXPE-         |

|--------------------------------------------------|

| <b>RIMENTAIS</b>                                 |

| 6.1 PLATAFORMA DE TESTES                         |

| 6.2 DEFINIÇÃO DE ESFORÇOS NOS SEMICONDUTORES 107 |

| 6.3 DISPOSITIVO PROGRAMÁVEL                      |

| 6.4 RESULTADOS EXPERIMENTAIS                     |

| 7 CONCLUSÃO                                      |

| <b>REFERÊNCIAS</b>                               |

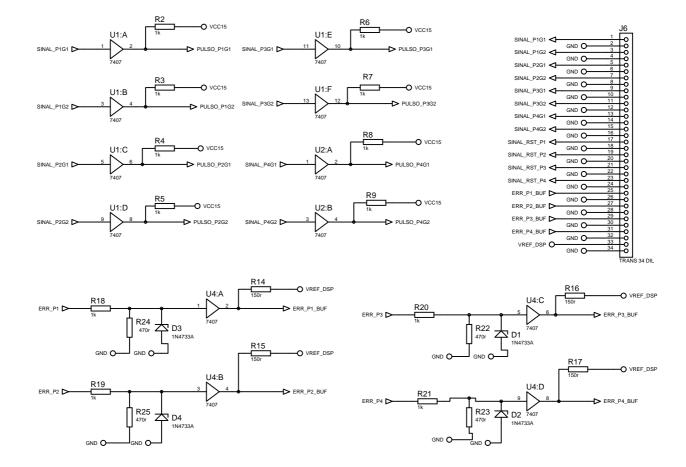

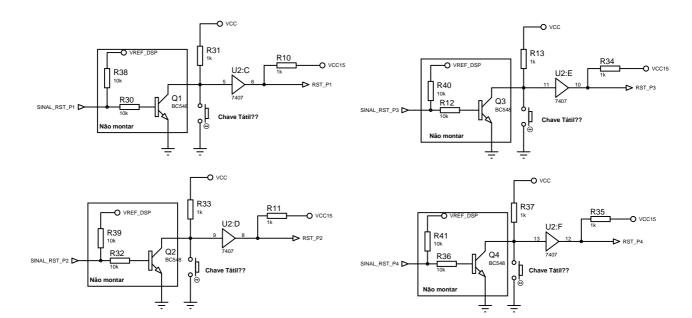

| ANEXO A - Esquemático Plataforma de potência 131 |

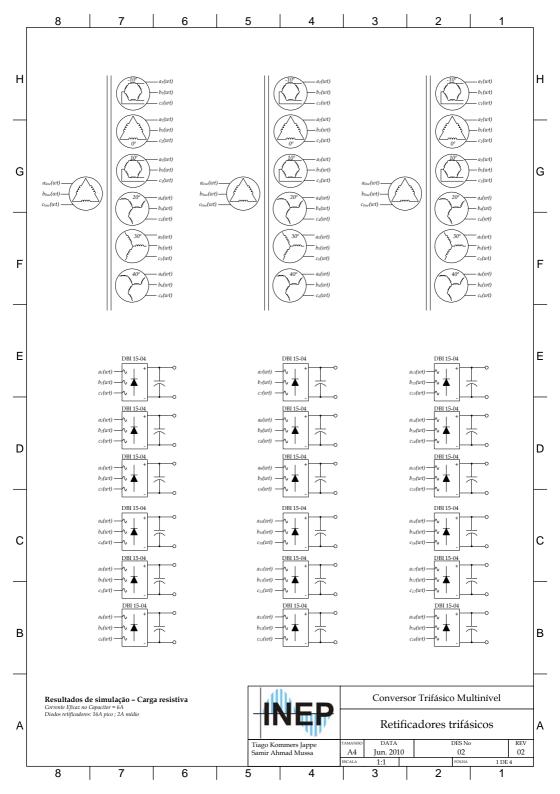

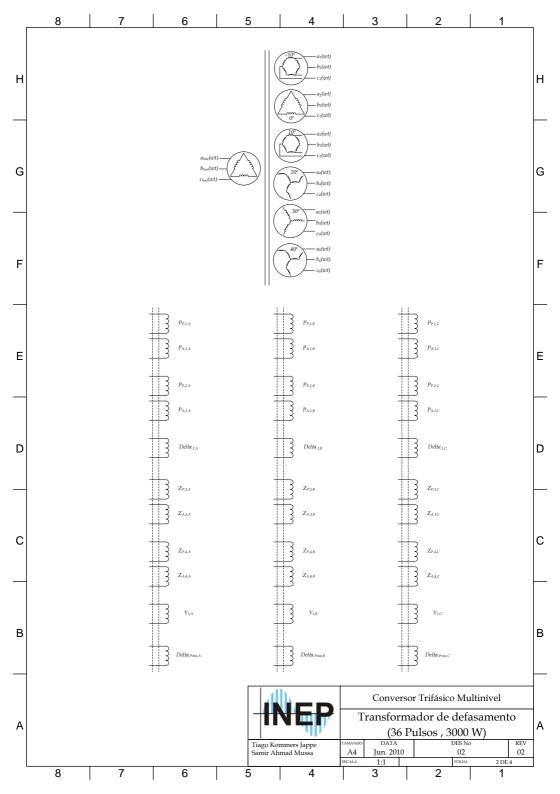

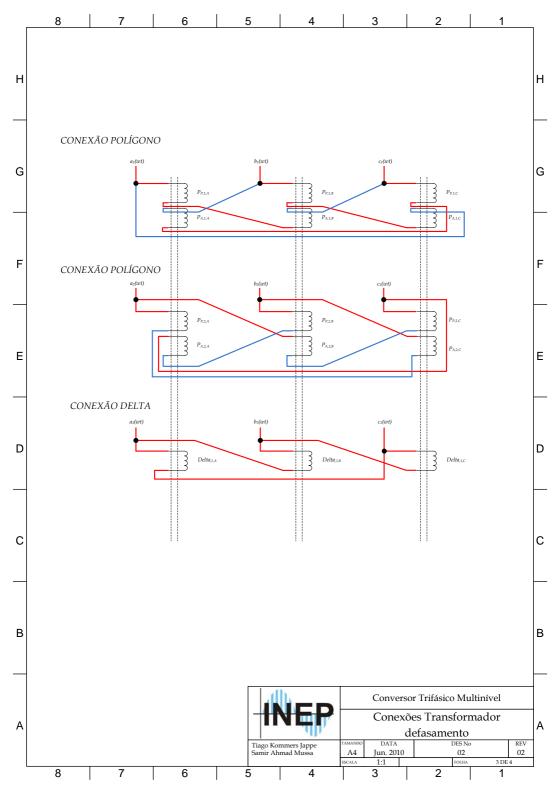

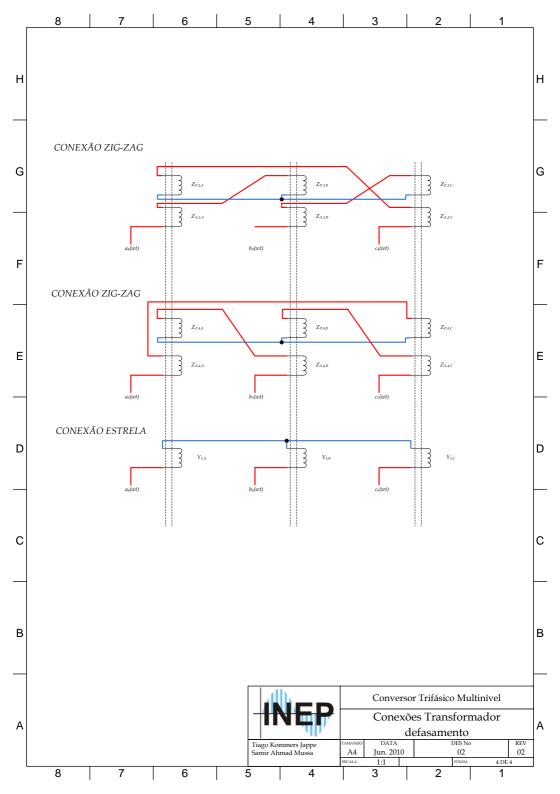

| ANEXO B - Projeto Transformador Multipulsos 137  |

| ANEXO C - Código VHDL                            |

| ANEXO D - Código C para computação CSVPWM 161    |

|                                                  |

# 1 INTRODUÇÃO

Em várias frentes produtivas a capacidade de movimentação de grandes volumes é essencial para o sucesso do processo. Seja na extração de matérias-primas brutas, tais como minérios de ferro, alumínio e cobre, na movimentação em massa de pessoas, usando trens e ônibus urbanos, metrôs e trens de alta velocidade, e até mesmo nas grandes linhas de transmissão de energia é essencial que o produto (minérios, pessoas ou energia elétrica) seja transportado da forma mais adequada possível e da maneira mais eficaz disponível. Em todas essas frentes são encontradas barreiras tecnológicas que faziam com que o processos não atingissem seu máximo potencial.

Vários exemplos são notáveis em quaisquer das áreas supracitadas. Na área de mineração a utilização de grandes motores é crucial, afinal quanto mais material é removido e processado maior tende a ser a lucratividade da empresa. O método mais barato seria a utilização de motores a combustão e bombas hidráulicas associados. Mas a combinação de combustível inflamável, temperatura e ambientes enclausurados é extremamente perigosa. Assim são utilizados motores elétricos de grandes potências nesses ambientes. Solucionado o problema da inflamabilidade, resta o problema do controle desses processos. Grandes motores exigem controle de grandes tensões e correntes e até as últimas décadas, poucos dispositivos eletroeletrônicos eram capazes dessa tarefa.

Nos transportes, com o advento da era industrial, houve a necessidade de transporte de grandes massas populacionais das áreas suburbanas até os centros comerciais e industriais. Somente veículos leves e individuais passaram a ser insuficientes para essa demanda. Os veículos de transporte de massa como ônibus e trens passaram a suprir essa demanda. Porém, com o crescimento acelerado dos nossos centros urbanos novas necessidades foram surgindo. A diminuição de espaços na superfície forçou a recolocação dos trilhos nos subterrâneos de grandes cidades, onde haveria muito espaço para crescimento de uma malha ferroviária, apesar de seus custos e de um problema grave, as locomotivas movidas a combustível fóssil sufocariam seus passageiros apesar de avançados sistemas de exaustão, como os do metrô de Londres. A saída foi a substituição dos motores a combustão pelos motores elétricos, onde mais uma vez recai-se no problema já detectado na mineração, escassez de soluções eficientes.

A maior necessidade por energia levou a exploração de várias

Figura 1 – Motor de indução usado em moinho de bolas na indústria de mineração (6500kW, 13800V). Fonte: Catálogo Weg.

outras fontes de geração. Fontes essas que geralmente encontram-se distantes dos polos consumidores (grandes centrais hidrelétricas, fazendas eólicas), gerando a necessidade de transmissão de toda essa energia, com as menores perdas possíveis. Durante anos o sistema de transmissão predominante foi o alternado (tensão e corrente variando senoidalmente no tempo), escolha feita decorrente das tecnologias predominantes na época das construções das usinas. Com o advento da eletrônica de potência moderna e a melhoria das tecnologias de fabricação de componentes pode-se verificar que para certas linhas de transmissão o uso de tecnologia em corrente contínua tinha melhores resultados.

Em todas as situações acima grande parte do problema é gerada pelas potências envolvidas. Equipamentos de mineração operam na faixa de megawatts de potência. Transportes de massa costumeiramente vão de dezenas até centenas de kilowatts. As linhas de transmissão operam numa faixa mais ampla ainda, podendo variar de centenas de kilowatts a centenas de megawatts. Em todos os casos a faixa de corrente atinge milhares de amperes.

Entretanto, mesmo com os dispositivos mais modernos tem-se vários problemas. A questão da isolação elétrica dos componentes é recorrente, uma vez que os dispositivos que possuem isolação alta são caros, com tempos de comutação elevados entres seus estados de condução e bloqueio e ainda dispendiosos em termos de energia utilizada no pro-

Figura 2 – Trolebus na Espanha. Fonte: Associação Brasileira do Veículo Elétrico.

cesso de comutação. Caso queira ser tentado algum arranjo em série de componentes, com a finalidade de aumentar a tensão de isolação do arranjo, tem-se um grave problema de sincronia. Mesmo que os sinais de comandos dos interruptores sejam impostos ao mesmo tempo, não há garantia que os componentes irão ter a comutação síncrona. E nesse caso, a falta de sincronia pode levar o arranjo todo a destruição.

Nesse contexto surgiram os conversores multiníveis. A necessidade de serem atingidos níveis de tensão mais elevados com o uso de dispositivos comuns no mercado e que nos quais possam ser utilizadas técnicas de modulação e controle que resultem em equipamentos mais eficientes. Apesar dos primeiros artigos datarem do final dos anos 70 e começo dos 80 (NABAE; TAKAHASHI; AKAGI, 1981), uma grande gama de trabalhos foi publicada a partir de 1996.

Este trabalho apresenta uma nova topologia de inversor multinível hibrido de 9 níveis quando das configurações monofásicas chegando a 17 níveis da tensão de fase nas configurações trifásicas, baseadas em células de conversores ponte completa e de conversores NPC. Além disso, são apresentados estudos da aplicação de diferentes técnicas de modulação senoidal conhecidas da literatura, por exemplo (HOLMES, 2003), (WU, 2006) e (MCGRATH; HOLMES, 2002), e um comparativo dessas técnicas senoidais padrão frente a uma técnica de centralização de pulsos (CARMONA et al., 2008).

$\mathcal O$ trabalho está estruturado da seguinte forma: no capítulo 2

serão apresentadas as principais topologias de inversores multiníveis conhecidos na literatura tais como NPC, Flying Capacitor e Cascaded, destacando vantagens e desvantagens de cada topologia. No capítulo 3 serão apresentadas as técnicas de modulação senoidal amplamente difundidas e um comparativo das mesmas. Nos capítulos 4 e 5 serão apresentadas as novas topologias propostas e os resultados das simulações usando algumas das técnicas de modulação apresentadas anteriormente e uma nova técnica hibrida proposta. No capítulo 6 serão apresentados o projeto do inversor e os resultados experimentais.

### 2 TOPOLOGIAS DE INVERSORES MULTINÍVEIS

Os inversores multiníveis surgiram da necessidade do mercado de atender maiores demandas de potência, envolvendo tensões e correntes de níveis acima dos disponíveis nos interruptores de mercado. Associada a essa necessidade, também a inclusão dos inversores a normas de compatibilidade eletromagnética conforme (IEC, 1994) e (FCC, 1992). Assim, uma vez que níveis menores de tensão são comutados, menores são suas emissões de ruído eletromagnético segundo (ERKUAN; LIPO, 1995).

Agora contextualizado, apresentam-se as estruturas de inversores NPC, Flying Capacitor e Cascaded, que são amplamente difundidos da literatura.

#### 2.1 INVERSOR NPC

O inversor NPC foi desenvolvido por (BAKER, 1980) e amplamente explorado por (NABAE; TAKAHASHI; AKAGI, 1981). O inversor NPC é derivado do inversor de 2 níveis, que contando com a inclusão de diodos, que exercem o grampeamento da tensão nos interruptores, e interruptores ativos fazem com que seja possível a obtenção de mais de 2 níveis de tensão.

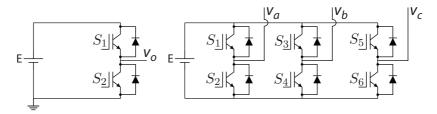

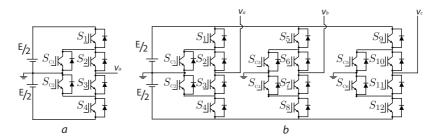

O inversor de 2 níveis, ilustrado na figura 3, gera em sua saída uma forma de onda grampeada nos níveis extremos do seu barramento, fazendo uso de um braço meia-ponte convencional, por fase. Quando em uma configuração trifásica é possível a obtenção de um nível intermediário de tensão de linha com o uso de 3 braços de conversores meia-ponte.

Figura 3 – Inversor 2 níveis. Configuração monofásica (a) e trifásica (b).

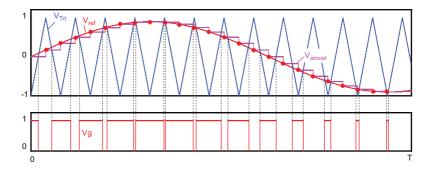

Impondo sinais de comando aos interruptores é possível criar um sinal senoidal. Porém como ilustrado na figura 4, vê-se que a senóide criada está deslocada, situada entre os valores extremos do barramento.

Como nos conversores meia-ponte, o comando dos interruptores nos inversores 2 níveis deve ser feito tomando cuidado para que exista um tempo morto entre o acionamento de cada um dos interruptores do mesmo braço. Caso isso não seja respeitado um curto-circuito será provocado no barramento. Na figura 4 temos as formas de onda de  $v_o$  junto com a referência senoidal (evidenciando os 2 níveis) e de  $v_{ab}$ , mostrando os 3 níveis possíveis.

Essa é a topologia inversora mais difundida na literatura, principalmente em aplicações de baixa tensão e potência, por atender grande faixa de aplicações com fidelidade. Dentre essas aplicações estão UPS e conversores de tensão DC-AC.

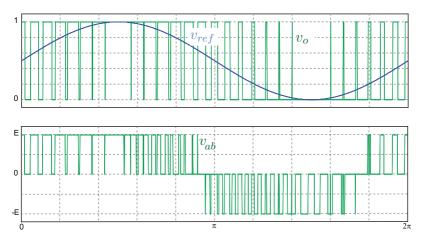

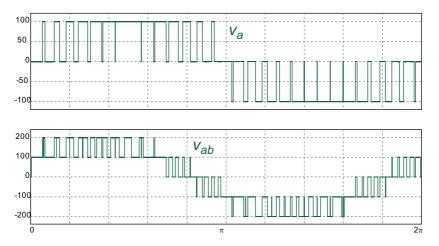

O inversor NPC, em sua estrutura mais simples ilustrado na figura 5, possibilita a geração de uma forma de onda com 3 níveis já na configuração monofásica, elevando esse número para 5 níveis com a configuração trifásica. É prática comum usar uma única fonte de tensão e gerar os níveis intermediários através de um barramento capacitivo, não sendo exigido o uso de fontes isoladas. Em (XIAOMING, 1998) é feito um alerta sobre as características de auto-balanceamento do barramento capacitivo e em (ISHIDA et al., 2000) é apresentada uma técnica para garantia do equilíbrio de tensão.

Trabalhos como o de (RODRIGUEZ; JIH-SHENG; ZHENG, 2002)

Figura 4 – Forma de onda das tensões  $v_o$ ,  $v_{ref}$ , e  $v_{ab}$ .

alertam para problemas associados a recuperação reversa dos diodos de grampeamento, principalmente quando a topologia possibilita maior número de níveis e os de (BUM-SEOK; DONG-SEOK, 1997) e (XIAOMING; BARBI, 2000) para a ocorrência de sobretensão nos interruptores internos devido a indutâncias parasitas e ao grampeamento indireto de tensão.

Na figura 6 são exibidas as formas de onda da tensão de fase, na configuração monofásica, e da tensão de linha, na configuração trifásica, do inversor NPC.

Figura 5 – Estruturas básicas do inversor NPC. Monofásica (a) e Trifásica (b).

Figura 6 – Formas de onda das tensão nas configurações monofásica (a) e trifásica (b).

Seguem as principais características do inversor NPC, onde n é o número de níveis desejados na tensão de fase do inversor:

- Utiliza  $2 \cdot (n-1)$  interruptores ativos por fase;

- Necessita de  $2 \cdot (n-2) \cdot (n-1)$  diodos de grampeamento por fase;

- Os esforços de tensão dos interruptores ativos são idênticos. Todos são submetidos a <sup>E</sup>/<sub>n</sub>;

- Os esforços de tensão nos diodos de grampeamento aumentam conforme o número de níveis do conversor aumenta. Esse problema é contornado com a adição em série de outros diodos, porém deve ser analisada com cautela;

- Caso seja necessário aumentar a tensão de saída, é possível fazê-lo sem a necessária substituição dos interruptores;

- Uma vez que níveis menores de tensão são comutados, há redução das derivadas de tensão dv/dt;

- Para n > 3 o balanceamento das tensões não é possível para cargas ativas, o que limita a aplicação do conversor a compensação de reativos.

#### 2.2 INVERSOR FLYING CAPACITOR

O inversor Flying Capacitor foi desenvolvido por (MEYNARD; FOCH, 1992) como alternativa aos inversores NPC. Na figura 7 é ilustrada uma topologia monofásica para três níveis. Assim como nos inversores NPC, os Flying Capacitor tem por objetivo reduzir os esforços de tensão sobre os interruptores. Esse objetivo é alcançado pois os capacitores de grampeamento aplicam sua tensão sobre os interruptores sem a necessidade do uso de diodos, que nos inversores NPC poderiam ter seus esforços de tensão aumentados conforme são acrescidos níveis ao inversor.

Outro problema resolvido pelos Flying Capacitor é referente ao equilíbrio das tensões do barramento, e nesse caso dos capacitores de grampeamento. Dada a redundância existente na topologia existem várias combinações de interruptores que levam a mesma solução.

Porém, essa redundância gerada na topologia é devida as possibilidades geradas pela combinação dos interruptores em conjunto com os capacitores de grampeamento.

Ainda devido a existência desses capacitores, tem-se a necessidade de pré-carga dos mesmos, feita por circuitos externos ao da topologia apresentada, o que eleva a contagem de componentes e a complexidade geral do inversor.

Figura 7 – Topologia Flying Capactor de 3 níveis.

Um outro problema apresentado por essa topologia é a elevada tensão a qual os capacitores estão sujeitos. O dimensionamento desses componentes deve ser feito levando em consideração tanto a sua capacitância, quanto aos níveis de tensão e corrente eficaz aos quais o capacitor estará imposto.

A ordem dos comandos do inversor Flying Capacitor deve respeitar a não sobreposição dos sinais de comando dos pares  $S_2$  e  $S_3$ ,  $S_6$  e  $S_7$ ,  $S_1$  e  $S_4$  e  $S_5$  e  $S_8$ . Caso essa limitação não seja respeitada os capacitores serão postos em curto gerando danos ao inversor.

Sintetizando as características do conversor Flying capacitor que o diferenciam do NPC temos:

- Redundância no comando dos interruptores leva a um maior controle do inversor, porém mais complexo;

- Tanto o fluxo de potência ativa e quanto o fluxo de potência reativa podem ser controlados;

- São necessários sensores de tensão e um controle dedicado para a manutenção dos níveis de tensão necessários para o correto grampeamento;

#### 2.3 INVERSOR CASCATA

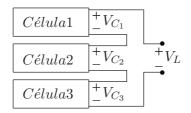

As topologias Cascaded, ou Cascata, como seu nome propõe são formadas pela associação de topologias simples, tais como as formadas por células de comutação meia-ponte ou ponte completa. A forma de associação mais efetiva é a série, pois possibilita o surgimento de formas de onda com níveis de tensão elevados em relação a cada entrada individual. Essas foram as primeiras formas documentadas de geração de multiníveis, publicadas por (BAKER; LAWRENCE, 1975)

As estruturas chamadas CHB (Cascaded H-Bridge ou Cascata Ponte H) são provavelmente as mais usadas em inversores multiníveis por serem baseadas na célula de comutação de ponte completa, de fácil implementação.

As topologias cascata são por definição modulares, pois cada célula tem sua fonte independente e isolada, e os comandos dos interruptores também podem ser gerados localmente, independente do número de níveis desejados no inversor. Nesse caso, o recomendado é que se tenha um comando central para o controle dessas células.

Na estrutura com célula meia-ponte, cada célula acrescenta dois níveis na saída do inversor. Na figura 9 é ilustrada uma conexão cascata

Figura 8 – Células usadas no conversores cascata. (a) Ponte completa e (b)Meia ponte.

generalizada onde  $V_{C_1}$ ,  $V_{C_2}$  e  $V_{C_3}$  são as saídas de tensão de cada célula e  $V_L$  a soma das tensões de todas as células.

Figura 9 – Ilustração de conversor cascata.

No caso das estruturas CHB, baseadas na célula de ponte completa, exibida na figura 8a, as tensões  $V_{C_1}$ ,  $V_{C_2}$  e  $V_{C_3}$  podem atingir 3 níveis por célula -E, E e 0. Caso  $S_1$  e  $S_4$  sejam comandados é imposto em  $V_L$  a tensão da fonte E. Caso os interruptores  $S_2$  e  $S_3$  sejam comandados, a tensão se inverte e -E é imposta na saída. Se nenhum interruptor for comandado a saída é 0.

Como características gerais dos conversores cascata temos:

- Os esforços de tensão sobre os interruptores são idênticos em todas as células. Os interruptores estão sempre submetidos no máximo a tensão da fonte da célula a qual pertencem;

- A estrutura é modular por definição. Podem ser fabricados módulos idênticos o que facilita sua montagem, manutenção e substituição nas aplicações;

- As técnicas de controle para equilíbrio da tensão dos capacitores de barramento são dispensáveis;

- É necessário o mesmo número de fontes isoladas conforme requisito do número de níveis de tensão;

- A contagem total de componentes é elevada.

# 2.4 INVERSOR CASCADED HÍBRIDOS OU ASSIMÉTRICOS

Os inversores ditos híbridos ou assimétricos são assim classificados pois são caracterizados pela assimetria nos valores nominais de tensão e/ou corrente de suas fontes. É possível que essas sejam de valores contíguos , por exemplo "E" e "2E" ou "2E" e "3E", ou não como "E" e "4E".

No caso de fontes de valores não contíguos, algum nível de tensão intermediário poderá estar ausente, piorando quesitos como THD e esforços de tensão nos componentes. Ainda assim podem ser úteis quando trata-se de fontes com potências diferentes, conforme demonstrado em (MANJREKAR; STEIMER; LIPO, 1999).

### 2.5 INVERSOR MMC

As topologias *Modular Multilevel Converter*, ou simplesmente MMC são recentes, conforme apresentado em (LESNICAR; MARQUARDT, 2003). Essas topologias são baseadas em células de comutação meiaponte ou ponte completa cascateadas, de modo a impor a combinação de suas tensões. Assim como na topologia *Flying Capacitor*, os níveis impostos são obtidos de capacitores conectados a essas células de comutação. A figura 10 ilustra essa célula.

Figura 10 – Célula da topologia MMC.

Novamente como na topologia FC, é necessário um maior esforço dos mecanismos de controle para que as tensões nos capacitores tenham seu valor controlado, conforme exibido em (KONSTANTINOU; CIOBOTARU; AGELIDIS, 2011).

#### 2.6 INVERSOR ANPC

Os conversores ANPC, Active Neutral Point Clamped, são similares conceitualmente aos NPC sendo que os ANPC s têm seus níveis de tensão grampeados ativamente, através do comando de interruptores. Os trabalhos de (BARBOSA et al., 2005a) e (BERNET, 2004) apresentam o conversor numa configuração de 3 níveis, mono e trifásica. A figura 11 ilustra essas configurações.

Assim como o inversor MMC, as topologias ANPC são relati-

Figura 11 – Estruturas do conversor ANPC. (a)Mono e (b) Trifásica.

vamente novas porém no trabalho de (BARBOSA et al., 2005b) já são apresentadas modificações nas estrutura do ANPC levando aos conversores ANPC de 5 e 7 níveis de tensão.

## 2.7 CONCLUSÃO

As estruturas aqui apresentadas sintetizam décadas de trabalho e esforço de vários pesquisadores e mostram a evolução do conhecimento quando referido as topologias de conversores multiníveis.

Foram resumidas as características peculiares de cada uma das três topologias mais difundidas na literatura sobre inversores multiníveis (NPC, FC e cascata) e três topologias recentes e ainda em estágio de pesquisa (cascata híbrida, MMC e ANPC). Comparadas entre si, cada uma delas apresenta pontos fortes e fracos em vários quesitos.

A tabela 1 apresenta alguns itens fundamentais que servem como critério de comparação entre as topologias diretamente, sem a interferência de técnicas de controle, referente apenas às topologias mais difundidas (NPC, FC e cascata).

Tabela 1 – Resumo sobre inversores multiníveis. Aqui "n" representa o número de níveis desejado

|                     | Interruptores | Diodos de<br>gramp. | Cap. de<br>gramp.      | Cap. de<br>barramento | Fontes<br>Isoladas | Níveis<br>de fase |

|---------------------|---------------|---------------------|------------------------|-----------------------|--------------------|-------------------|

| CHB                 | 2(n-1)        | 0                   | 0                      | $\frac{(n-1)}{2}$     | $\frac{(n-1)}{2}$  | 2n - 1            |

| NPC                 | 2(n-1)        | (n-1)(n-2)          | 0                      | (n-1)                 | 1                  | 2n - 1            |

| Flying<br>Capacitor | 2(n-1)        | 0                   | $\frac{(n-1)(n-2)}{2}$ | (n-1)                 | 1                  | 2n - 1            |

# 3 MODULAÇÃO

A origem do termo modulação remete à área de telecomunicações (BLACK, 1953). Um bom exemplo é caracterizado nas transmissões sem fio de ondas eletromagnéticas, onde o tamanho da antena varia conforme o comprimento de onda do sinal a ser transmitido. Dependendo do tipo da antena pode-se usar  $\frac{\lambda}{2}$ ,  $\frac{\lambda}{4}$  ou  $\frac{\lambda}{10}$ , onde  $\lambda$  é o comprimento de onda.

O comprimento de onda relaciona-se com a frequência através da equação 3.1, onde c é a constante que representa a velocidade da luz e f é a frequência do sinal a ser transmitido.

$$\lambda = \frac{c}{f} \tag{3.1}$$

Assim, tanto quanto o sinal tiver frequência maior, menor é a antena utilizada. Assim, para a transmissão de áudio na faixa audível (20 Hz a 20 kHz) o comprimento de onda varia aproximadamente de 15 mil km a 15 km, que na melhor das condições resultaria em uma antena com tamanho variando de 1,5 mil km a 1,5 km, parâmetros impraticáveis, (BALANIS, 1992).

Outra condição que torna impraticável a transmissão de sinais em baixas frequências pelo ar é a degradação do sinal, pois sinais de baixa frequência tem capacidade de radiação ruim por serem facilmente absorvidos pelo ambiente necessitando de amplificadores de sinal com muita potência.

Existe ainda a questão de uso de banda. Apenas um sinal pode ser transmitido ou recebido. Caso dois sinais sejam transmitidos simultaneamente o receptor receberá a soma de ambos e não terá condições de discernir um sinal do outro.

Para contornar os problemas citados foram desenvolvidas técnicas para deslocar o sinal das frequências da faixa de áudio para faixas mais altas. Essas técnicas são chamadas genericamente de modulação de sinal.

Nessas técnicas usam-se dois sinais chamados portadora e moduladora. Os termos portadora e moduladora referem-se ao sinal que contém a informação a ser transmitida (moduladora) e ao sinal que vai carregar o sinal para longe dos emissores (portadora). É comum o uso dessa nomenclatura quando tratando-se de transmissões AM e FM.

Em eletrônica de potência a essência da modulação é a mesma, transmitir uma informação. Porém, a informação a ser transmitida

representa a forma de onda desejada na saída de um conversor, seja ele um conversor CC-CC ou CC-CA. Nesse trabalho são tratados os aspectos referentes diretamente a técnicas de modulação aplicáveis a conversores CC-CA, os inversores de tensão.

A escolha da técnica de modulação impacta diretamente em quatro aspectos do comportamento do conversor:

### 1. Conteúdo harmônico;

O conteúdo harmônico é avaliado pelos índices de THD e Weighted THD de primeira ordem da tensão de saída (WTHD). Segundo apresentado por (HOLMES, 2003), THD e WTHD são definidas como:

$$THD = \frac{1}{V_1} \sqrt{\sum_{i=2}^{n} V_i^2}$$

(3.2)

onde i representa a ordem dos harmônicos e n o número de ordens a ser avaliada.

A WTHD é uma avaliação da tensão de saída ponderada pela ordem da mesma. O termo fica definido como:

$$WTHD = \frac{1}{V_1} \sqrt{\sum_{i=2}^{n} \left(\frac{V_i}{i}\right)^2}$$

(3.3)

# 2. Perdas de comutação;

As perdas de comutação estão associadas a frequência com que os interruptores são forçados a comutar seus estados de condução (bloqueio, onde não existe corrente significativa conduzida pelo semicondutor e condução, estado no qual existe um sinal de corrente sendo conduzido).

Essas perdas podem ser minimizadas com algumas técnicas de modulação que privilegiam a redução no número de comutações.

## 3. Perdas de condução;

Da mesma maneira que ocorre com as perdas de comutação é possível minimizar as perdas de condução com a utilização de diferentes técnicas de modulação, conforme mostrado em (QUNJING et al., 2007).

#### 4. Tensões de modo comum.

As tensões de modo comum são causa corriqueira de problemas em várias aplicações de eletrônica de potência. Em acionamentos elétricos por exemplo, pode forçar um acoplamento capacitivo através de peças móveis do motor, como eixo e rolamentos, fazendo com que o tempo de vida útil dos mesmos seja reduzido.

Algumas das técnicas aqui apresentadas são testadas em simulação e ponderadas conforme quesitos a serem apresentados no capítulo 5. Baseado nesses quesitos é apresentado ferramental matemático para avaliação de uma técnica. Essa técnica então será implementada na parte experimental desse trabalho.

### 3.1 TÉCNICAS CONHECIDAS

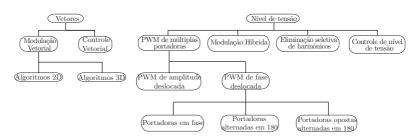

Diversas técnicas de modulação estão disponíveis na literatura. O modo como foram organizadas e apresentadas em (FRANQUELO et al., 2008) é muito interessante e de grande valia para seu estudo. A figura 12, é baseada neste. Apesar de serem apresentadas diversas técnicas, as mesmas se ramificam e tal figura não deve ser interpretada como caracterização definitiva para esse tópico.

Figura 12 – Organização das técnicas de modulação para conversores multiníveis.

As duas grandes famílias apresentadas, Vetores e Nível de Tensão, são basicamente assim agrupadas devido sua natureza. A família baseada em vetores faz uso de representações vetoriais baseadas nos estados topológicos da estrutura. Gera-se a tensão de saída desejada, ou compõe-se o vetor de saída desejado, através de uma soma vetorial. No caso, calcula-se o período de imposição de cada estado topológico necessário para obtenção da saída desejada.

A família de técnicas baseadas em nível de tensão também visa obter um nível de tensão desejado na saída, porém não faz o uso de representações vetoriais para isso. Essa família abrange múltiplas técnicas, conforme a necessidade e a disponibilidade da estrutura em estudo.

Assim como a figura 12 não caracteriza um quadro rígido da organização das modulações possíveis para inversores multiníveis algumas das técnicas abordadas aqui terão equivalentes em ambas famílias.

As técnicas de modulação mais difundidas e aplicadas aos inversores são a modulação vetorial (SVM, Space Vector Modulation) e as modulações SPWM (Senoidal Pulse Width Modulation) de múltiplas portadoras. Ambas são baseadas em regras simples de comando dos interruptores conforme a topologia a qual são empregadas (HOLTZ, 1994).

### 3.1.1 Modulação Vetorial

Essa é uma das técnicas mais difundidas na literatura, principalmente aplicada às topologias de inversores de três níveis, conhecidos comumente como VSI´s (HOLMES, 2003). Passível de ser aplicada com relativa facilidade, poder ser utilizada em todas as topologias de inversores. Uma dificuldade dessa técnica aparece quando o número de vetores da topologia torna-se muito grande, exigindo algoritmos de cálculo complexos (MASSOUD; FINNEY; WILLIAMS, 2008).

As técnicas de modulação vetorial são divididas em 2D e 3D devido a representação dos vetores desejados. Em ambas as técnicas, o processo para obtenção dos vetores desejados passa pelo levantamento dos estados topológicos da estrutura.

Nas técnicas de modulação vetorial 2D, ou SVM, cada estado topológico gera um vetor, porém um mesmo vetor pode levar a estados topológicos diferentes. Essas condições dependem exclusivamente da topologia estudada. Na existência de um vetor que seja gerado por estados topológicos diferentes é dito que existe redundância de vetores (CELANOVIC; BOROYEVICH, 2001).

Na existência de redundância pode-se levar em consideração na escolha do vetor a ser utilizado a redução do número de comutações ou uma possível condição de balanço de carga da fonte utilizada na estrutura. Caso não haja redundância é preferível a utilização de tal vetor na formação de um vetor desejado em suas proximidades.

As mesmas condições são válidas para a modulação vetorial 3D. Logo, quando da existência de vetores redundantes além da possibi-

lidade de escolha dos vetores que leve a redução do número de comutações e do balanço de carga das fontes ainda é possível escolher um vetor que gere menores tensões no terceiro eixo ortogonal, usualmente ligado a tensões de modo comum aplicadas na carga.

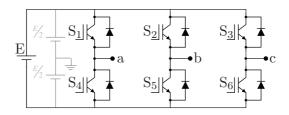

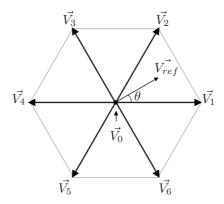

Conforme demonstrado em (HOLMES, 2003), a aplicação da SVM é facilmente compreendida quando aplicada ao VSI. Na figura 13 é ilustrada a topologia típica do VSI.

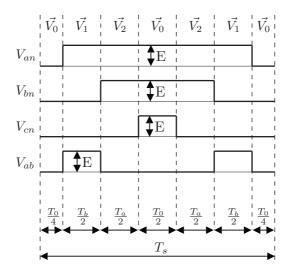

Dada a condição de operação dos interruptores do VSI restam apenas oito combinações possíveis, das quais uma (o vetor nulo, identificados como  $\vec{V_0}$  e  $\vec{V_7}$ ) é redundante, apresentadas na tabela 2

Tabela 2 – Vetores Resultantes, Interruptores comandados e Tensão aplicada a carga

| Vetor       | Interruptor Comandado | Tensão aplicada                                 |

|-------------|-----------------------|-------------------------------------------------|

| $\vec{V_0}$ | $S_1,\!S_2,\!S_3$     | 0                                               |

| $ec{V_7}$   | $S_4,\!S_5,\!S_6$     |                                                 |

| $ec{V_1}$   | $S_1,\!S_5,\!S_6$     | $\frac{2}{3} \cdot E \cdot e^{j0}$              |

| $\vec{V_2}$ | $S_1, S_2, S_6$       | $\frac{2}{3} \cdot E \cdot e^{j\frac{\pi}{3}}$  |

| $\vec{V_3}$ | $S_2, S_4, S_6$       | $\frac{2}{3} \cdot E \cdot e^{j\frac{2\pi}{3}}$ |

| $\vec{V_4}$ | $S_2, S_3, S_4$       | $\frac{2}{3} \cdot E \cdot e^{j\frac{3\pi}{3}}$ |

| $\vec{V_5}$ | $S_3, S_4, S_5$       | $\frac{2}{3} \cdot E \cdot e^{j\frac{4\pi}{3}}$ |

| $\vec{V_6}$ | $S_1, S_3, S_5$       | $\frac{2}{3} \cdot E \cdot e^{j\frac{5\pi}{3}}$ |

Seguindo a metodologia, dado um vetor desejado, faz-se a soma vetorial dos vetores disponíveis mais próximos. No caso da utilização

Figura 13 – Topologia VSI.

Figura 14 – Diagrama de vetores do VSI.

do vetor 0, onde tem-se redundância, deve-se escolher um dos critérios já citados para a definição do vetor a ser utilizado.

Segundo (WU, 2006), o vetor  $\vec{V_{ref}}$  da figura 14 é definido como descrito na equação 3.5 onde  $T_a$ ,  $T_b$  e  $T_0$  são os tempos de aplicação de cada vetor e  $T_s$  é um período suficientemente pequeno onde  $\vec{V_{ref}}$  pode ser considerado constante, atendendo aos conceitos de tensão média instantânea, definido como:

$$T_s = T_a + T_b + T_0 (3.4)$$

$$\vec{V_{ref}} \cdot T_s = \vec{V_1} \cdot T_a + \vec{V_2} \cdot T_b + \vec{V_0} \cdot T_0$$

$$(3.5)$$

Sendo  $\vec{V_{ref}} = V_{ref} \cdot e^{j\theta}$ , e substituindo-o juntamente com definições dos outros vetores envolvidos descritas na tabela 2 na equação 3.5 juntamente com a equação 3.4 resulta após alguma manipulação em:

$$T_{a} = \frac{\sqrt{3} \cdot T_{S} \cdot V_{ref}}{E} \cdot sen\left(\frac{\pi}{3} - \theta\right)$$

$$T_{b} = \frac{\sqrt{3} \cdot T_{S} \cdot V_{ref}}{E} \cdot sen\left(\theta\right)$$

$$T_{0} = T_{s} - T_{a} - T_{b}$$

$$(3.6)$$

Tendo determinado o tempo de aplicação de cada vetor, pode-se concentrar esforços na sequência de comutação mais adequada. Vale ressaltar aqui que o intervalo  $T_s$  é reflexo da frequência de comutação desejada.

Figura 15 – Sequência de comutação escolhida para  $\vec{V_{ref}}$ .

Visando minimizar as comutações necessárias temos a sequência escolhida na figura 15. Vale ressaltar que todos os interruptores comutam apenas duas vezes durante o intervalo e que é feito uso de todos os vetores disponíveis, inclusive os dois vetores redundantes.

Essa foi ocasionalmente a escolha ótima. Várias combinações são possíveis e terão resultados diferentes dessa em relação ao número de comutações de cada interruptor.

O algoritmo para uso da modulação vetorial segue deslocando os vetores de  $60^\circ$  conforme os setores são cruzados pelo vetor de referência.

Em (PRATS et al., 2003) encontra-se um algoritmo e resultados experimentais para aplicação da modulação vetorial 3D.

### 3.1.2 Controle Vetorial

Conforme descrito em (MATHEW; HOUGHTON; OGHANNA, 1995), em essência, as técnicas de controle vetorial são baseadas no controle ativo de componentes vetoriais da carga a qual o conversor está conectado. A exemplo, no trabalho citado o inversor controla o fluxo magnético de um motor de indução tipo gaiola.

O procedimento para descoberta do vetor é o mesmo que o usado na SVM, porém as decisões sobre qual vetor será aplicado e o tempo

de imposição vão depender da realimentação do sistema de controle.

É usual para os casos que o controle vetorial é empregado a utilização das transformadas apresentadas em (PARK, 1929) para realimentação dos vetores de referencia.

Em (RODRIGUEZ; CORREA; MORAN, 2001) é apresentado um algoritmo para uso do controle vetorial em um inversor multinível e alguns critérios de comparação utilizados no estudo com uma modulação senoidal.

### 3.1.3 PWM de múltiplas portadoras

Conforme já comentado, juntamente com a modulação vetorial, as modulações baseadas em portadoras ocupam lugar de destaque como técnicas difundidas na literatura e indústria.

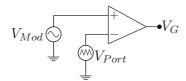

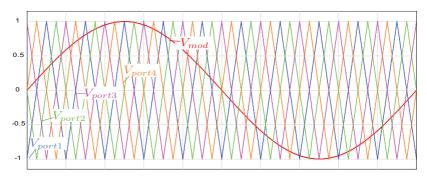

Essas técnicas de modulação visam a obtenção de formas de onda correspondentes a sua moduladora na saída dos inversores de tensão. Para tanto usa-se estruturas comumente chamadas de moduladores para a geração dos sinais de comando dos interruptores das topologias. Esses sinais são gerados a partir da comparação entre os sinais moduladores e os sinais portadores. O sinal modulador refere-se a informação pretendida na saída do inversor e o sinal portador a frequência de comutação dos interruptores. Na figura 16 está ilustrado um modulador genérico, em uma representação analógica idealizada.

Figura 16 – Exemplo de um modulador genérico.

É comum que existam tantas portadoras quanto forem necessárias para controlar todos os níveis de tensão do inversor. Essa quantidade é definida como  $Nr_{port}$  na equação 3.7, onde n é o número de níveis esperado do inversor.

$$Nr_{port} = n - 1 (3.7)$$

A variação da largura dos pulsos é o princípio básico do PWM. Em conversores DC/DC, onde procura-se um ponto de operação fixo e realizam-se ações de controle para que as características desejadas dos

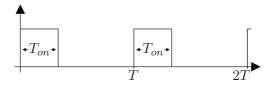

conversores sejam preservadas, define-se o termo razão cíclica D, como apresentado em (MOHAN, 2003) como segue:

$$D = \frac{T_{on}}{T} \tag{3.8}$$

onde  $T_{on}$  é o período que o interruptor está conduzindo e T é o período total entre duas comutações, ilustrados na figura 17. Essa definição restringe a faixa de valores de D entre 0 e 1.

Figura 17 – Exemplo dos períodos para definição de D.

Em conversores DC/AC utiliza-se o termo razão cíclica, definido na equação 3.9, conforme apresentado por (WU, 2006):

$$M_a = \frac{V_{Mod}}{V_{Tri}} \tag{3.9}$$

onde  $V_{Mod}$  é a tensão de pico da moduladora e  $V_{Tri}$  é o valor de pico da tensão da portadora, conforme a figura 18. Assim, o índice de modulação de amplitude poderia assumir quais valores. O uso de valores superiores a 1 é chamada de sobremodulação e será discutida a seguir.

Figura 18 – Exemplos das amplitudes para definição de M.

Além do índice de modulação de amplitude  $(M_a)$ , outra definição importante é o índice de modulação de frequência  $(M_f)$ . Esse índice contém a relação entre a frequência das portadoras e da moduladora.

Fica então definido  $M_f$  como na equação 3.10.

$$M_f = \frac{f_{port}}{f_{mod}} \tag{3.10}$$

A disposição que essas portadoras assume também tem influência sobre os aspectos salientados anteriormente, como WTHD. Em estratégias de modulação com múltiplas portadoras, essas podem assumir disposições em dois grupos: disposição com deslocamento de fase (PS, *Phase Shifted*) ou deslocamento de nível (LS, *Level Shifted*)

### 3.1.3.1 PWM com deslocamento de fase

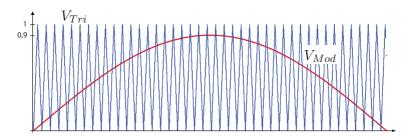

A estratégia de modulação PWM com múltiplas portadoras do tipo PWM com deslocamento de fase é apresentado na figura 19. Nessa estratégia são empregadas portadoras defasadas entre si conforme a topologia do inversor. No caso ilustrado o inversor teria cinco níveis, fazendo com que as portadoras sejam defasadas entre si com o ângulo  $\phi$ , conforme a equação 3.11.

$$\phi = \frac{360^{\circ}}{n} \tag{3.11}$$

Destaca-se que a amplitude e a frequência das portadoras triangulares é a mesma. No caso ilustrado na figura 19, com o pico da moduladora coincidente com o pico das triangulares, o índice de modulação de amplitude é 1.

De acordo com (WU, 2006), a modulação PS tem uma grande vantagem relativa ao espectro gerado. As componentes espectrais aparecem como bandas laterais dos múltiplos de dois da frequência de comutação. Assim, com componentes indesejáveis em frequências elevadas em relação a moduladora a filtragem torna-se muito mais fácil, devido a redução dos componentes dos filtros.

No exemplo apresentado em (WU, 2006), um inversor CHB de sete níveis consegue deslocar as componentes harmônicas para seis vezes a sua frequência de comutação, devido a cancelamentos das componentes entre as fases.

Figura 19 – Exemplo da disposição das portadoras e da moduladora.

#### 3.1.3.2 PWM com deslocamento de nível

Assim como no caso do PWM com deslocamento de fase, aqui também as portadoras tem a mesma amplitude e frequência. Contudo estarão deslocadas verticalmente, com um *offset* que dependerá das amplitudes das mesmas de modo que não haja cruzamento entre as portadoras.

Nesse caso é necessária adaptar o conceito de índice de modulação de amplitude  $M_a$ . Conforme (WU, 2006), nessa situação  $M_a$  fica definido como descrito na equação 3.12.

$$M_a = \frac{V_{\text{mod}}}{Nr_{port} \cdot V_{tri}} \tag{3.12}$$

Mesmo com as portadoras deslocadas verticalmente, ainda podemos ter arranjos de fase entre elas. Caso as portadoras estejam dispostas em fase, esse arranjo é dito *In-Phase Disposition* ou IPD. É possível também a disposição das portadoras em oposição de fase, *Phase Opposite Disposition* ou POD, e ainda com disposição das portadoras alternadas em oposição de fase, *Alternative Phase Opposite Disposition* ou APOD. Essas três disposições de portadoras são ilustradas na figura 20.

O trabalho de (CARRARA et al., 1992), traz um comparativo quantitativo feito entre os três arranjos de portadoras usando o ferramental matemático descrito detalhadamente em (HOLMES, 2003), (WU, 2006) e (MCGRATH; HOLMES, 2002).

Nesses trabalhos são descritos métodos para a avaliação das formas de onda de saída, realizados através da representação em duas

Figura 20 – Ilustração dos arranjos das portadoras com deslocamento de nível. (a) IPD, (b) APOD e (c)POD.

variáveis da série de Fourier do sinal. Esse também será o método utilizado para validação do uso de uma técnica de modulação adequada ao inversor proposto nesse trabalho.

## 3.1.4 Modulação Híbrida

A modulação híbrida é definida por (FRANQUELO et al., 2008) como uma técnica aplicada a conversores que possuem barramentos com tensões diferentes, usualmente conversores CHB, e que dessa forma podem adicionar ou subtrair um nível de tensão à carga. Dessa forma cada barramento poderia ser aproveitado de forma mais otimizada, conforme o nível de potência da célula cascateada, conforme apresentado em (RECH; PINHEIRO, 2007) e (MANJREKAR; STEIMER; LIPO, 1999).

Porém essa definição não é rígida e é possível diversas interpretações. Alguns autores, tais como (AGELIDIS; CALAIS, 1998) e (CHINNAIYAN et al., 2007) consideram modulação híbrida como a utilização de duas técnicas diferentes ao mesmo tempo. Uma fusão de dois arranjos de portadoras.

### 3.1.5 Eliminação Seletiva de Harmônicos

A técnica de eliminação seletiva de harmônicos, Selective Harmonic Elimination ou SHE, foi inicialmente aplicada a conversores de grande potência usando interruptores lentos. O cálculo prévio dos ângulos de disparo em tiristores em inversores é essencial na eliminação de harmônicos de baixa ordem, na correta geração da onda de saída e na redução das perdas por comutação. Em (LI et al., 1998) são apresentados os conceitos e a quantização para obtenção dos intervalos de disparo.

#### 3.1.6 Controle de Nível de Tensão

Conforme descrito em (FRANQUELO et al., 2008), o controle de nível de tensão é utilizado em inversores com grande número de níveis, em que sua operação seja baseada em aproximação de nível. Conclui-se ser um modo de controle do inversor similar ao SHE, porém com o foco no nível de tensão desejado, não nas harmônicas a serem eliminadas.

Esse método está descrito em (KOURO et al., 2007) e de acordo com (FRANQUELO et al., 2008) seus resultados aproximam-se do método de controle vetorial.

# 3.2 SOBREMODULAÇÃO

Quando o valor do índice de modulação de amplitude é forçado a valores superiores a 1, é dito que o conversor opera em sobremodulação. Essa faixa de trabalho, quando usadas técnicas de modulação senoidal, leva a redução no número de pulsos nas formas de onda das tensões de linha e ao aumento do valor da tensão de linha gerada. O custo nesse caso é a perda da relação linear entre a tensão de linha gerada e o índice de modulação de amplitude, conforme apresentado por (WU, 2006).

De acordo com (BAKHSHAI; JOOS; JIN, 1997), as técnicas de modulação baseadas em senóides utilizam apenas 78% da tensão do barramento em uma topologia VSI. Assim, um motor padrão acionado por tal topologia estaria operando abaixo de suas especificações. Do mesmo modo os inversores multinível que baseiam suas modulações em senóides tem o mesmo comportamento conforme (HOLMES, 2003).

Em acionamentos de alta performance, por exemplo carros elétricos,

a utilização de toda a tensão do barramento para obtenção do máximo torque disponível pela máquina em qualquer faixa de operação é essencial.

Com a finalidade de disponibilizar a capacidade toda do barramento surgiram diversas técnicas de sobremodulação aplicadas nas modulações senoidais sem que seja perdida a linearidade entre  $V_{ab}$  e  $M_a$ . No trabalho de (HAVA; KERKMAN; LIPO, 1998) são comparadas diversas técnicas de sobremodulação aplicadas as técnicas de modulação senoidal.

A técnica mais usada é a THIPWM, Third Harmonic Injection Pulse Width Modulation ou Injeção de terceira harmônica. O trabalho de (HOULDSWORTH; GRANT, 1984) apresenta de forma clara os princípios da técnica e seus resultados.

No trabalho de (GRANT, 1981) algumas técnicas e seus resultados são apresentados para a transição da SPWM para a aplicação de uma onda quadrada, de modo a utilizar plenamente o barramento disponível.

È conveniente afirmar que as técnicas de modulação que são baseadas em vetores também tem o mesmo problema. Os trabalhos de (BAKHSHAI; JOOS; JIN, 1997) e (KERKMAN et al., 1996) apresentam técnicas que pretendem o mesmo que a THI, uso total do barramento de tensão.

Como citado anteriormente, várias técnicas de modulação são propostas de maneiras diferentes porém delas obtém-se resultados similares. Assim também na sobremodulação existe uma técnica denominada CSVPWM a qual propõem-se através do cálculo específico de moduladoras obter resultados similares aos registrados pela técnica SVM, porém a custos computacionais inferiores, permitindo inclusive a sobremodulação. Em (HOLMES, 2003) e (VAN; GUN-WOO; MYUNG-JOONG, 2004) são descritos os métodos e processos para implementação da técnica.

# 3.3 APLICAÇÃO DIGITAL

Das técnicas de modulação descritas até esse ponto apenas as definidas como de Múltiplas Portadoras foram descritas de modo analógico. O modulador ilustrador na figura 16, está apresentado também numa forma analógica. O restante das técnicas são comumente implementadas via processamento de dados digitais, sejam microcontroladores, processadores de sinal ou dispositivos de lógica programável.

Porém a implementação analógica dessas técnicas resulta numa

Figura 21 – Exemplo de PWM naturalmente amostrada.

série de inconvenientes tais como geração e adaptação dos sinais a serem utilizados (portadoras triangulares e moduladora senoidal com amplitude variável, por exemplo) com níveis de ruído aceitáveis, condicionamento dos sinais, operações entre portadoras e moduladora entre outras.

Com o aperfeiçoamento dos controladores digitais muitas das tarefas necessárias para geração dos pulsos de disparo dos interruptores foi simplificada. Atualmente existe uma gama de dispositivos que já incluem moduladores PWM entre seus dispositivos padrão e mesmo outros equipamentos comumente utilizados nas tarefas de modulação e controle, tais como contadores externos e conversores analógico/digital.

Dada a grande facilidade da implementação digital de tal tarefa é necessário conduzir uma investigação sobre os efeitos da discretização sobre as técnicas de modulação.

Partindo do modulador analógico da figura 16 temos que as comparações entre portadora e moduladora ocorrem continuamente. Essa é a forma mais simples e direta para posicionamento dos pulsos, chamada PWM Naturalmente Amostrado (Naturally Sampled PWM). Aqui ocorre a comparação direta entre a portadora e a moduladora como ilustrado na figura 21. Para que possa ser obtida uma forma de onda senoidal na saída a moduladora, que é a onda de referência, deve ter a seguinte forma:

$$V_{ref} = M_a \cos(\omega_0 t + \theta_0) = M_a \cos y \tag{3.13}$$

Caso a portadora seja uma onda dente-de-serra esse tipo de modulação passa a ser denominada PWM Naturalmente Amostrado de Borda Simples, *Trailing Edge Naturally Sampled PWM*. Se a portadora for uma onda triangular denota-se PWM Naturalmente Amostrado de Borda Dupla, *Double Edge Naturally Sampled PWM*.

Figura 22 – Exemplo de amostragem simples.

As situações anteriores não ocorrem nas implementações digitais. Os controladores digitais necessitam de períodos para o processamento de outras tarefas e ainda se não o necessitassem, todas as tarefas são temporizadas e naturalmente ocorrem em tempos discretos. Logo as comparações entre portadoras e moduladora também ocorrem em tempos discretos.

Mais ainda, as próprias portadoras e moduladora são discretas, com valores definidos em campos da memória dos controladores. Em (BUSO; MATTAVELLI, 2006) são descritos os conceitos apresentados nessa seção. No trabalho aqui proposto não será feita nenhuma realimentação de informações ou estratégia de controle, situações nas quais os efeitos das implementações digitais tratadas nessa seção são de fundamental importância. Desse modo, não será dada ênfase ou realizado o estudo das consequências da operação em tempos e valores discretos dos controladores.

O princípio de funcionamento é simples, um registrador (campo de memória) é incrementado regularmente (fazendo o papel das portadoras) e quanto seu valor chega a um nível pré estabelecido é feita a comparação para geração do pulso de comando. A questão a ser abordada aqui é sobre o efeito da amostragem na geração dos pulsos.

Caso o valor da moduladora seja amostrada apenas uma vez por período de comutação ela é dita PWM Regularmente Amostrada (*Regularly Sampled PWM*) com amostragem simples, conforme ilustrado na figura 22.

Nesse caso o efeito dessa amostragem é a inclusão de um atraso na função de transferência do modulador PWM, sendo a mesma definida na equação 3.14.

$$PWM_s(s) = \frac{e^{-sM_aT_s}}{V_{tri}^{pk}} \tag{3.14}$$

Figura 23 – Exemplo de amostragem dupla.

Caso a portadora seja uma onda triangular a implementação pode ser assimétrica ou simétrica, dependendo do instante da amostragem. Ela será dita simétrica se a onda for amostrada apenas uma vez por período da portadora, tanto no pico positivo ou negativo, e assimétrica se for amostrada duas vezes por período da portadora, tanto no pico positivo quanto no pico negativo e a função de transferência fica definida como na equação 3.15.

$$PWM_D(s) = \frac{e^{-sM_a\frac{T_s}{2}} + e^{-s(1-M_a)\frac{T_s}{2}}}{2V_{tri}^{pk}}$$

(3.15)

Nas equações 3.14 e 3.15 tem-se que  $V^{pk}_{tri}$  é o valor de pico da portadora triangular,  $M_a$  é o índice de modulação de amplitude e  $T_s$  é o período referente a frequência da portadora.

Em (HOLMES, 2003) são discutidos e apresentados os efeitos de cada tipo de amostragem sobre as forma de ondas de saída de alguns conversores.

## 3.4 CONCLUSÃO

Nesse capítulo foi apresentada uma proposta para organização das estratégias de modulação mais difundidas da literatura. As mesmas formas dispostas conforme seus princípios de operação. Técnicas que operam através da associação de estados topológicos com vetores (SVM e Controle Vetorial) foram agrupadas separadamente de técnicas que utilizam-se da comparação de sinais para a geração de pulsos de comando, tais como PWM de múltiplas portadoras e Controle de nível

de tensão.

Tal organização foi proposta no trabalho de (FRANQUELO et al., 2008) e assim como descrito no citado trabalho, essa organização não deve representar uma estrutura rígida, impassível de mudanças, pois pesquisas continuam a ser feitas sobre modulação e novos resultados sempre são apresentados. E mesmo entre técnicas conhecidas temos resultados similares para técnicas distintas, abordadas de formas completamente diferentes.

Também foram abordados temas como os técnicas de sobremodulação e suas consequências e efeitos da implementação digital das técnicas de modulação.

A principal conclusão é de que a variedade de técnicas é grande, cada qual com vantagens e desvantagens. A decisão sobre qual técnica é mais adequada dependerá da topologia usada, da capacidade computacional disponível, da familiaridade do projetista com a técnica e da aplicação na qual a mesma será implementada.

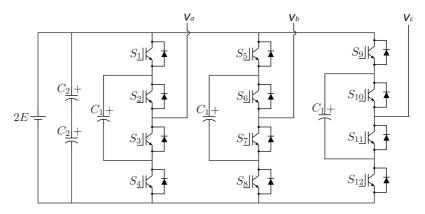

#### 4 TOPOLOGIAS PROPOSTAS

Nos capítulos anteriores foram apresentadas topologias conhecidas da literatura para inversores multiníveis e as técnicas de modulação mais usadas para as mesmas. Nesse capítulo serão apresentadas topologias baseadas no inversor multinível simétrico (RUIZ-CABALLERO et al., 2010b). As topologias são caracterizadas por serem de formação híbrida, uma vez que são criadas por células de conversores já existentes, buscando obter os melhores resultados vindos de seus conversores de origem.

# 4.1 FORMAÇÃO DAS TOPOLOGIAS

Generalizando os conceitos básicos dos conversores de potência, segundo (BARBI, 2002), os inversores de tensão são conversores abaixadores de tensão (tipo Buck). Conversores CC-CC tipo Buck operam controlando o período de imposição da tensão de entrada à saída, fazendo com que a média entre o tempo que a entrada é imposta à saída e o tempo em que nenhuma tensão é imposta represente a tensão desejada.

Assim, pode-se considerar que os conversores tipo Buck operam com dois níveis de tensão (WESTER; MIDDLEBROOK, 1973). Em (XINBO; BIN; QIANHONG, 2002) é apresentada uma topologia Buck onde a tensão de saída é composta por três níveis de tensão.

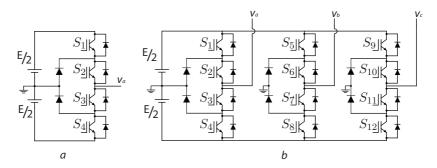

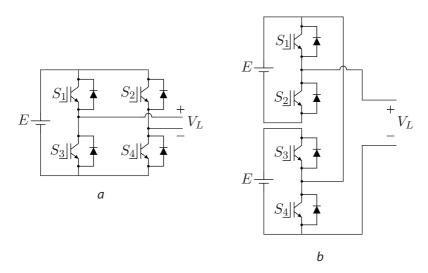

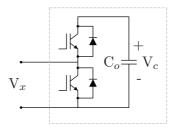

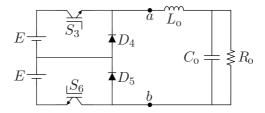

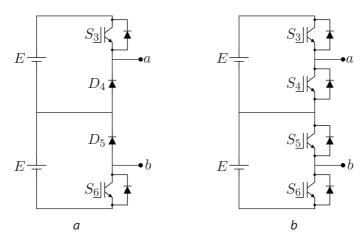

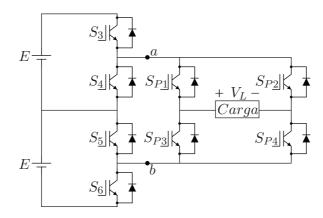

Assim, partindo da topologia de um conversor DC-DC Buck de três níveis, ilustrado na figura 24 são feitos re-arranjos na célula de comutação de modo a obter a topologia da figura 25a. Para possibilitar a conversão com bidirecionalidade de corrente, os interruptores passivos

Figura 24 – Conversor Buck 3 níveis.

$(\mathrm{D4} \to \mathrm{D5})$ são substituídos por interruptores ativos (S4 e S5), conforme 25b.

Figura 25 – (a) Rearranjo da célula de comutação. (b) Substituição dos interruptores.

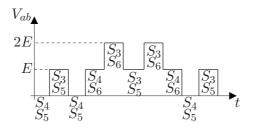

A figura 26 exemplifica, com uma sequência de comandos adequados (destacados na figura), como pode-se formar um sinal com 3 níveis de tensão a serem obtidos entre os pontos a e b da topologia apresentada conforme figura 25b. Destaca-se que os níveis são todos positivos ou zero, quando levada em consideração a polaridade da tensão como sendo  $V_{ab}$ .

Figura 26 – Tensão obtida em  $V_{ab}$ .

Para que possam ser obtidos níveis de tensão negativos usa-se uma célula de comutação tipo ponte completa, a qual possibilita a inversão da referência de tensão, conectada aos pontos a e b, como na figura 27. Dessa forma podemos obter uma forma de onda com 5 níveis

de tensão numa configuração monofásica, conforme ilustrado na figura 28.

Essa dedução foi apresentada em (RUIZ-CABALLERO et al., 2010b) e (RUIZ-CABALLERO et al., 2010a), e de forma similar em (BOOMA; SRIDHAR, 2011), porém para outra célula de comutação. As topologias propostas nesse trabalho são modificações propostas da topologia apresentada em (RUIZ-CABALLERO et al., 2010b).

Figura 27 – Inversor 5 níveis.