# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

ESTUDO E REALIZAÇÃO DE UM ESTABILIZADOR DE TENSÃO ALTERNADA A TRANSISTOR DE POTÊNCIA

DISSERTAÇÃO SUBMETIDA À UNIVERSIDADE FEDERAL DE SANTA

CATARINA PARA OBTENÇÃO DO GRAU DE MESTRE EM ENGENHARIA

CÉSAR MAURO CARDOSO

FLORIANÓPÖLIS, DEZEMBRO 1986

# ESTUDO E REALIZAÇÃO DE UM ESTABILIZADOR DE TENSÃO ALTERNADA A TRANSISTOR DE POTÊNCIA

### CÉSAR MAURO CARDOSO

ESTA DISSERTAÇÃO FOI JULGADA PARA A OBTENÇÃO DO TÍTULO DE MESTRE EM ENGENHARIA, ESPECIALIDADE ENGENHARIA ELÉTRICA E APROVADA EM SUA FORMA FINAL PELO CURSO DE PÓS-GRADUAÇÃO

Prof. Ivo Barbi, Dr. Ing.

ORIENTADOR

Prof. Luiz Gonzaga de Souza Fonseca, Dr. Coordenador do Curso de Pós-Graduação em Engenharia Elétrica

BANCA EXAMINADORA:

Prof. Ivo Barbi, Dr. Ing

Prof. Denizar Cruz Martins, Dr.

$\sim$  101.

Prof. Arnaldo José Perin, Dr. Ing.

Prof. João Batista Vieira Júnior, M.Sc.

A minha Familia

A Eliana

A todos os meus Amigos

#### **AGRADECIMENTOS**

Ao Professor Ivo Barbi, pela amizade, dedicação e orientação a este trabalho.

Aos Professores, colegas e funcionários do programa de Pós-Graduação e do Departamento de Engenharia Elétrica da UFSC que, de uma forma ou de outra, contribuiram para a realização deste trabalho.

À UFSC, CNEN, FINEP e CAPES pelo apoio financeiro.

## SUMÁRIO

| RESUMO                                                                            | x            |

|-----------------------------------------------------------------------------------|--------------|

| ABSTRACT                                                                          | хi           |

| INTRODUÇÃO                                                                        | хii          |

| CAPÍTULO 1 - ESTABILIZAÇÃO DE TENSÃO ALTERNADA                                    |              |

| 1.1 - Introdução                                                                  | 01           |

| 1.2 - As Técnicas Utilizadas em Estabilizadores de Tensão                         |              |

| Alternada                                                                         | 01           |

| 1.2.1 - Estabilizador de Tensão Alternada a Reator                                |              |

| Saturável                                                                         | 01           |

| 1.2.2 - Estabilizador de Tensão Alternada Eletrome-<br>cânico                     | 02           |

|                                                                                   | 02           |

| 1.2.3 - Estabilizador de Tensão Alternada com Mudan  ça de Tap's de Transformador | 03           |

| 1.2.4 - Estabilizador de Tensão Alternada com Trans                               |              |

| formadores de Ajuste                                                              | 04           |

| 1.2.5 - Estabilizador de Tensão Alternada Através                                 |              |

| do Controle de Fase                                                               | 05           |

| 1.2.6 - Estabilizador de Tensão Alternada a Tiris-                                |              |

| tor                                                                               | 06           |

| 1.2.7 - Estabilizador de Tensão Alternada a Transis                               | 2-3<br>38-37 |

| tor                                                                               | 07           |

| 1.3 - Conclusão                                                                   | 08           |

# CAPÍTULO 2 - ANÁLISE DO FUNCIONAMENTO DA ESTRUTURA PROPOS TA

| 2.1 -    | Introdução                                                    | 10  |

|----------|---------------------------------------------------------------|-----|

| 2.2 -    | Apresentação da Estrutura Proposta neste Trabalho             | 10  |

| 2.3 -    | Funcionamento com Tensão de Entrada Fixa e Tensão de          | :   |

|          | Saída Variável (Variador Estático de Tensão Alternada         | L   |

|          | Senoidal)                                                     | 11  |

|          | 2.3.1 - Funcionamento da Estrutura com $\mathbf{R} = 1 \dots$ | 15  |

|          | 2.3.2 - Funcionamento da Estrutura com ℝ = 0                  | 18  |

|          | 2.3.3 - Funcionamento da Estrutura com ℝ = 0,5                | 21  |

|          | 2.3.4 - Funcionamento da Estrutura com 0,5 < $\mathbb{R}$ < 1 | 23  |

| 2.4 -    | Funcionamento com Tensão de Entrada Variável e Tensão         | •   |

|          | de Saída Fixa (Estabilizador de Tensão Alternada Se-          | •   |

|          | noidal                                                        | 26  |

| <b>,</b> | 2.4.1 - Introdução                                            | 26  |

|          | 2.4.2 - Relações de Transformação do Transformador            |     |

|          | TR <sub>2</sub>                                               | 32  |

|          | 2.4.3 - Variação da Razão Cíclica em Função da Varia-         |     |

| •        | ção da Tensão de Entrada                                      | 34  |

| 2.5 -    | Conclusão                                                     | 38  |

| CAPÍT    | ULO 3 - DIMENSIONAMENTO DOS TRANSFORMADORES                   | ,   |

|          |                                                               | , x |

| 3.1 -    | Introdução                                                    | 41  |

|          |                                                               |     |

| 3.2 - Determinação das Relações de Transformação de TR <sub>2</sub>                |    |

|------------------------------------------------------------------------------------|----|

| (n <sub>2</sub> e n <sub>3</sub> ) Adotando-se uma Razão Cíclica Máxima e          |    |

| uma Minima diferentes de Um e Zero                                                 | 41 |

| 3.3 - Determinação de um Ábaco para o Cálculo de n <sub>2</sub> e n <sub>3</sub> . | 45 |

| 3.4 - Potência do Transformador TR <sub>1</sub>                                    | 48 |

| 3.5 - Potência do Transformador TR <sub>2</sub>                                    | 48 |

| 3.6 - Determinação de um Ábaco para o Cálculo da Potência                          |    |

| dos Transformadores TR <sub>1</sub> e TR <sub>2</sub>                              | 49 |

| 3.7 - Exemplo de Cálculo                                                           | 50 |

| 3.8 - Conclusão                                                                    | 54 |

| CAPÍTULO 4 - COMANDO DE BASE DOS TRANSISTORES                                      |    |

| 4.1 - Introdução                                                                   | 55 |

| 4.2 - Comando de Base dos Transistores                                             | 56 |

| 4.2.1 - Circuito Lógico de Comando                                                 | 57 |

| 4.2.2 - Derivação, Amplificação Isolamento                                         | 63 |

| 4.2.3 - Circuito de Comando de Base                                                | 64 |

| 4.2.4 - Proteção                                                                   | 66 |

| 4.3 - Conclusão                                                                    | 70 |

| CAPÍTULO 5 - ESTUDO DA COMUTAÇÃO                                                   |    |

| 5.1 - Introdução                                                                   | 71 |

| 5.2 - Circuito de Ajuda à Comutação                                                | 71 |

| 5.2.1 - Circuito de Ajuda à Comutação no Bloqueio         | 71  |

|-----------------------------------------------------------|-----|

| 5.2.2 - Circuito de Ajuda à Comutação na Entrada em       | •   |

| Condução                                                  | 75  |

| 5.3 - Circuito Grampeador                                 | 77  |

| 5.4 - Sequências de Funcionamento                         | 80  |

| 5.5 - Influência da não Idealidade dos Diodos             | 85  |

| 5.6 - Conclusão                                           | 89  |

| CAPÍTULO 6 - HARMÔNICAS E FILTRAGEM                       |     |

| 6.1 - Introdução                                          | 90  |

| 6.2 - Análise Harmônica de Tensão Gerada pelo Conversor   | 90  |

| 6.2.1 - Determinação da Série de Fourier da Tensão        |     |

| v(t)                                                      | 91  |

| 6.2.2 - Determinação de Série de Fourier da Tensão        |     |

| $\mathbf{v_{F}}$ (t)                                      | 99  |

| 6.3 - Considerações sobre a Filtragem                     |     |

| 6.4 - Conclusão                                           | 104 |

| CAPÍTULO 7 - REALIZAÇÃO DE UM PROTÓTIPO                   |     |

| 7.1 - Introdução                                          | 105 |

| 7.2 - Os Componentes utilizados na Estrutura de Potência. | 105 |

| 7.3 - Ensaio Realizado com o Protótipo, em Malha Aberta   | 108 |

| 7.4 - Conclusão                                           | 113 |

# CAPÍTULO 8 - ANÁLISE DA TENSÃO DE SAÍDA

| 8.1 - Introdução 114                                     |

|----------------------------------------------------------|

| 8.2 - Influência dos Circuitos Grampeadores na Tensão de |

| Saida                                                    |

| 8.3 - Influência do Filtro na Tensão de Saída 121        |

| 8.4 - Influência das Quedas de Tensão nos Diodos e nos   |

| Transistores de Potência, na Tensão de Saida 122         |

| 8.5 - Conclusão                                          |

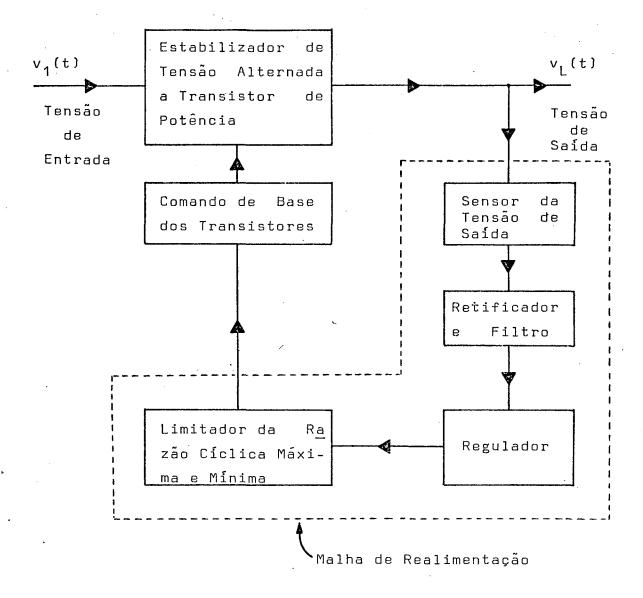

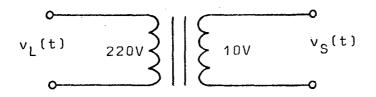

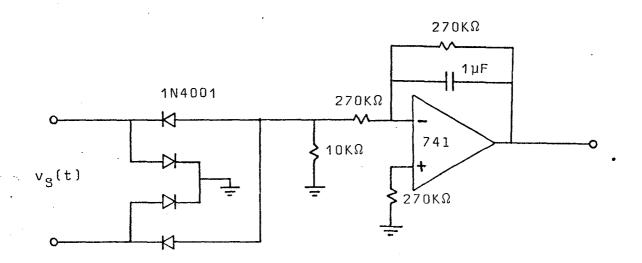

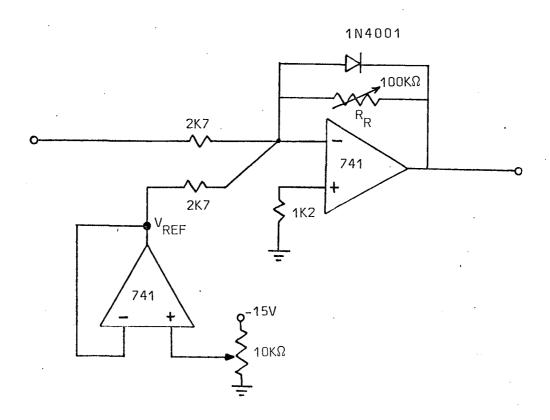

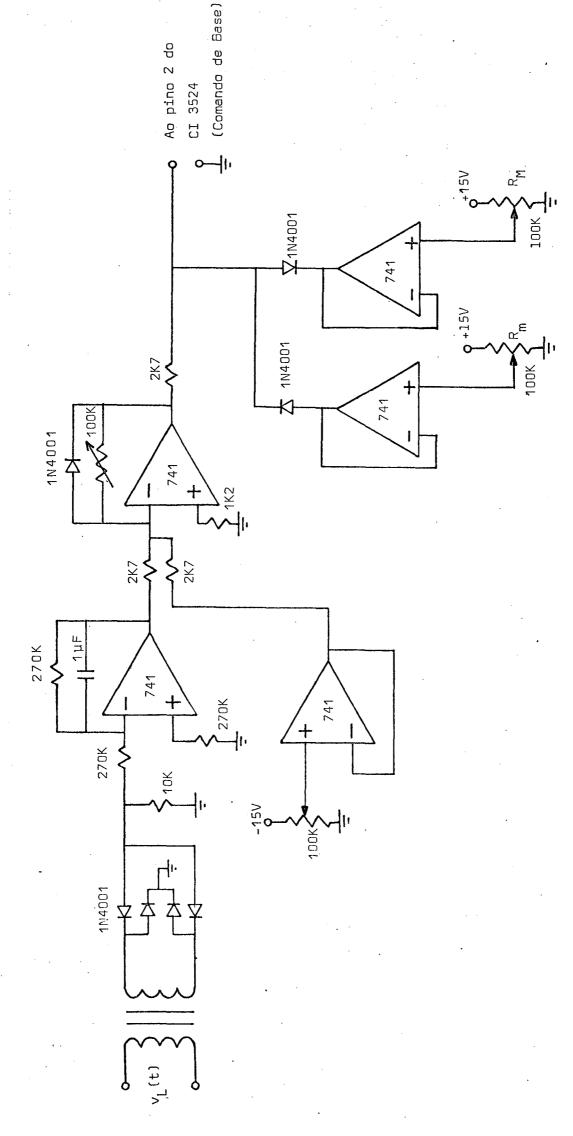

| CAPÍTULO 9 - CONTROLE AUTOMÁTICO DA TENSÃO DE SAÍDA      |

| 9.1 Introdução                                           |

| 9.2 - Malha de Realimentação                             |

| 9.2.1 - Sensor da Tensão da Saída                        |

| 9.2.2 - Retificador e Filtro                             |

| 9.2.3 - Regulador 129                                    |

| 9.2.4 - Limitador da Razão Cíclica Máxima e Mínima . 130 |

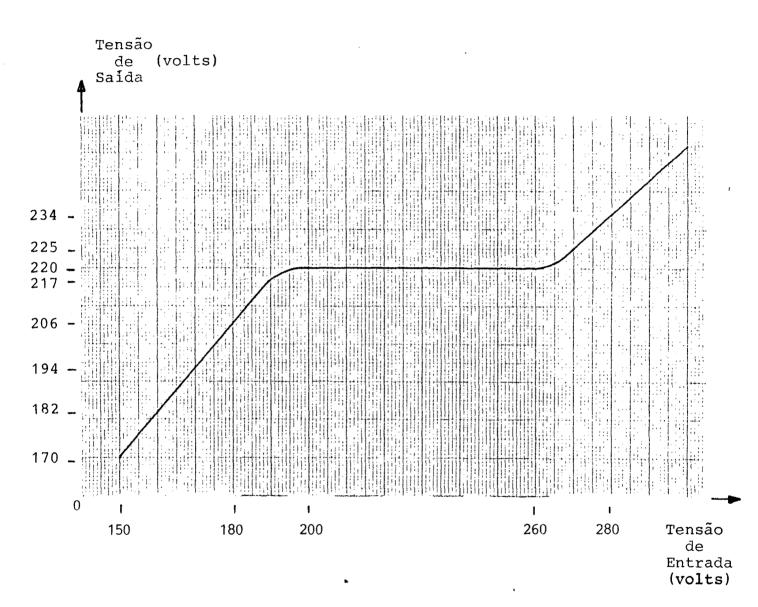

| 9.3 - Ensaio em Malha Fechada                            |

| 9.4 - Conclusão 134                                      |

|                                                          |

| CONCLUSÕES FINAIS                                        |

| REFERÊNCIAS BIBLIOGRÁFICAS                               |

|                                                          |

#### RESUMO

O presente trabalho descreve o estudo, projeto e realização de um estabilizador de tensão alternada a transistor de potência.

A estrutura de potência é constituída por duas chaves bidirecionais, com transistores chaveando complementarmente em alta frequência.

A Comutação dos transistores, que constitui a maior dificuldade deste trabalho, é abordado de forma detalhada, onde se mostra a necessidade da utilização de circuitos auxiliares de ajuda à comutação e de circuitos grampeadores.

Na parte prática, descreve-se o projeto e a implementação de um estabilizador de 220V e 5A.

Foram realizados estudos experimentais com o protótipo implementado, que permitiram a verificação do bom desempenho do ponto de vista da regulação estática e da comutação.

#### ABSTRACT

The present work describes a study, design and realization of a power transistor A.C. Voltage Stabilizer.

The power circuit is made of two bidirectional switches, with the transistors switching alternatively in high frequency.

The transistor commutation, which is the greatest difficulty in this work, is approached in detail, showing the need of using auxiliary circuits for commutation and clipping circuits.

In the practical part the design and implementation of a 220V, 5A Stabilizer is described.

Experimental studies have been undertaken with this prototype, demonstrating its superior performance from the viewpoint of static regulation and commutation.

### INTRODUÇÃO

Este trabalho, apresenta o estudo e a realização de um estabilizador de tensão alternada a transistor de potên cia. A estrutura utilizada, é original tanto a nível de princípio, quanto a nível tecnológico.

O objetivo fundamental desse trabalho, é a análise do princípio de funcionamento da estrutura de potência, principalmente com relação à comutação dos transistores.

O estudo é baseado em carga resistiva, o que se justifica, uma vez que a aplicação do estabilizador, é na alimentação de equipamentos que possuem retificação na entrada, apresentando cos  $\phi$  unitário.

No Capítulo 1 serão citadas algumas técnicas utilizadas, para estabilização de tensão alternada.

No Capítulo 2, será feita a análise do funciona mento da estrutura proposta neste trabalho, onde se mostra que a estrutura pode funcionar como variador estático de tensão al ternada e, como estabilizador de tensão alternada.

No Capítulo 3, será apresentado o dimensionamento dos transformadores utilizados na estrutura de potência. São <u>a</u> presentados ábacos, para facilitar o projeto dos transformadores.

No Capítulo 4 aparesentar-se-á o comando de base dos transistores, onde se fará a análise do seu funcionamento. Mostrar-se-á, também, o circuito de proteção utilizado, contra a desaturação dos transistores.

No Capítulo 5, será feito o estudo da comutação dos transistores, onde se mostra a necessidade da utilização de circuitos de ajuda à comutação, e de circuitos grampeadores.

No Capítulo 6, será feita a análise harmônica da tensão gerada pelo estabilizador, onde se poderá verificar que o conteúdo harmônico é de alta frequência, o que facilita, de forma decisiva, a sua filtragem.

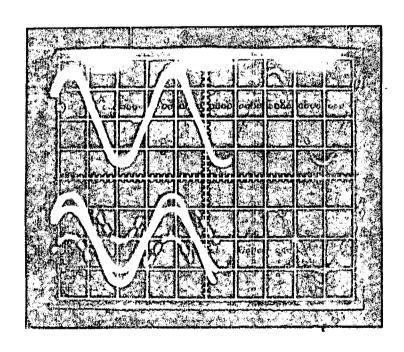

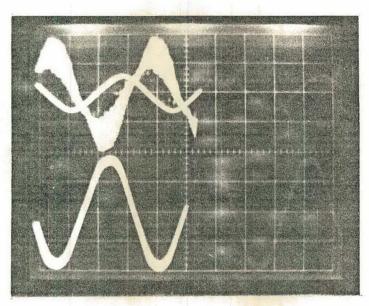

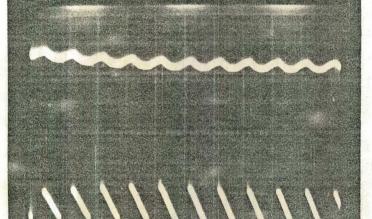

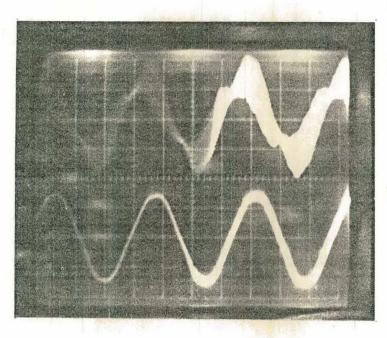

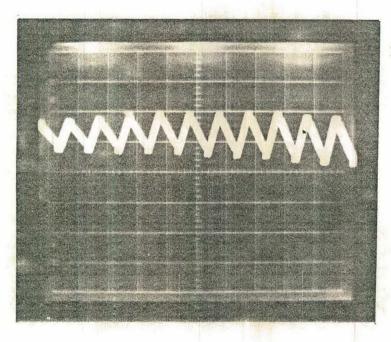

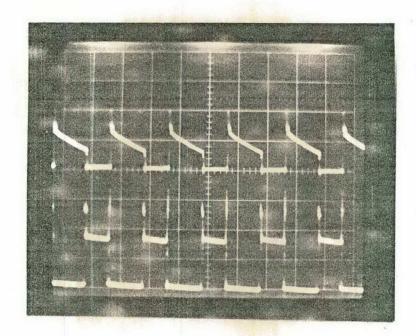

No Capítulo 7, serão feitas considerações sobre os componentes utilizados na estrutura de potência. Serão apresentadas algumas fotografias, que permitem verificar o funcionamento do protótipo desenvolvido.

No Capítulo 8, serão analisados os fatores que influenciam na tensão de saída do estabilizador, onde se verifica a influência dos circuitos grampeadores, do filtro e das que das de tensão nos diodos e transistores de potência.

No Capítulo 9, será estudado o controle automát<u>i</u> co da tensão de saída. Analisar-se-á a malha de realimentação <u>u</u> tilizada no protótipo desenvolvido, onde se poderá observar o seu bom desempenho.

Como última etapa, serão feitas as conclusões f $\underline{i}$  nais sobre o trabalho desenvolvido.

#### CAPÍTULO 1

### ESTABILIZAÇÃO DE TENSÃO ALTERNADA

## 1.1 - Introdução

A qualidade do fornecimento de energia elétrica é fator primordial, considerando-se as características das máquinas modernas, especificamente a grande difusão de computadores e de equipamentos computadorizados na indústria e no comércio.

Quedas e variações de tensão são eventos comuns nas redes elétricas, podendo causar, no caso de sistemas eletrônicos sensíveis, sérios problemas operacionais.

Várias são as técnicas utilizadas para estabilização de tensão alternada. Sem o objetivo de se esgotar o as sunto, serão citadas algumas delas.

# 1.2 - As <u>Técnicas Utilizadas em Estabilizadores de Tensão</u> Alter nada

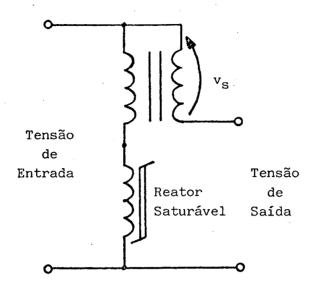

## 1.2.1 - Estabilizador de Tensão Alternada a Reator Saturável

Através da variação do nível de magnetização de um reator saturável, faz-se variar a tensão  $v_s$  no secundário de um transformador em série com a carga. Desta forma, controla-se a tensão de saída (Figura 1.1).

Figura 1.1 - Estrutura Básica do Estabilizador a Reator Saturável.

Os estabilizadores que funcionam baseados neste método, apresentam erro estático muito pequeno (em torno de 0,1%) e tempo de estabilização da ordem de 10 ciclos para uma frequência de 60 Hz.

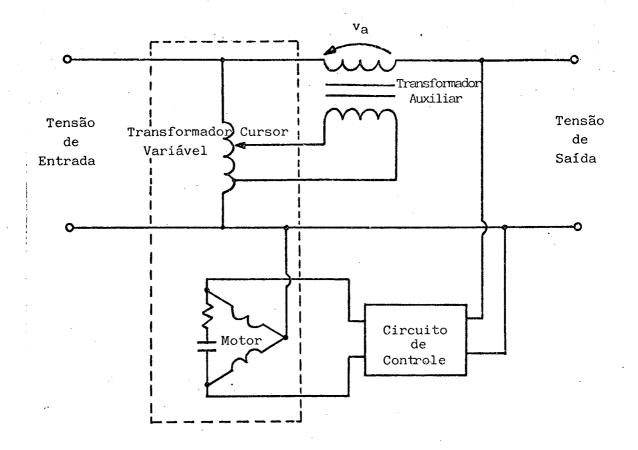

## 1.2.2 - Estabilizador de Tensão Alternada Eletromecânico

A estrutura básica deste estabilizador é mostrada na Figura 1.2.

Quando a tensão de saída se desvia do valor nominal, o circuito de controle faz com que o motor posicione o cur sor do transformador variável, de forma a variar a tensão vano secundário de um transformador auxiliar em série com a carga. Desta forma, a tensão de saída volta ao nível desejado.

Este tipo de estabilizador apresenta um erro est $\underline{\hat{a}}$  tico muito pequeno (pode ser nulo) e um resposta dinâmica lenta.

Figura 1.2 - Estrutura Básica do Estabilizador Eletromecânico.

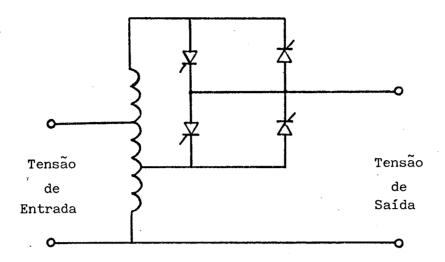

# 1.2.3 - Estabilizador de Tensão Alternada com Mudança de Tap's de Transformador [1]

O método utilizado neste tipo de estabilizador baseia-se na variação da tensão de saída através do chaveamento entre Tap's de um transformador, por intermédio de tiristores.

A Figura 1.3 mostra uma estrutura com chaveamen to em dois níveis, com controle no secundário.

Neste método o conteúdo de harmônicas é elevado, havendo necessidade de filtragem.

Figura 1.3 - Mudança de Tap's no Secundário.

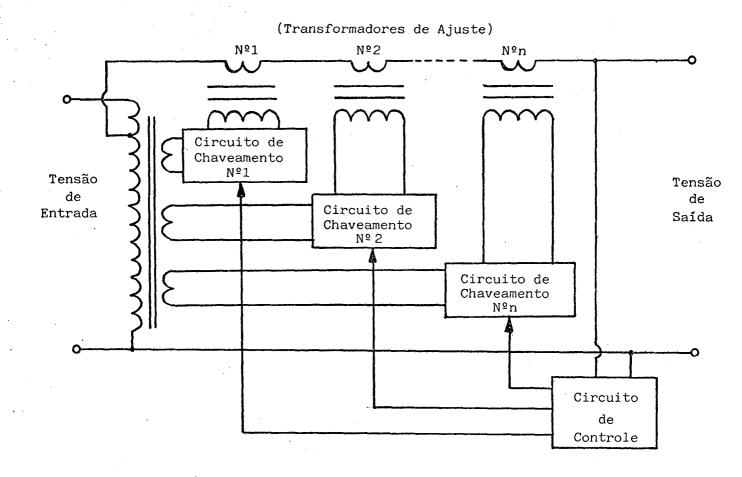

# 1.2.4 - Estabilizador de Tensão Alternada com Transformadores de Ajuste

A estrutura básica do estabilizador é mostrada na Figura 1.4.

Neste método adiciona-se ou retira-se níveis de tensão, através do chaveamento de interruptores estáticos que atuam nos transformadores de ajuste.

Este estabilizador apresenta um erro estático não nulo. No entanto sua resposta dinâmica é rápida e a tensão de saída é isenta de harmônicas.

Figura 1.4 - Estrutura Básica do Estabilizador com Transformadores de Ajuste.

# 1.2.5 - Estabilizador de Tensão Alternada Através do Controle de Fase

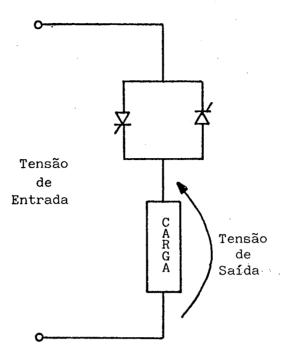

A Figura 1.5 mostra a estrutura básica do estabil<u>i</u> zador.

O controle de fase consiste no disparo de tiristores em instantes diferentes da senóide de modo que se possa con trolar o intervalo de condução dos tiristores.

Figura 1.5 - Estrutura Básica do Estabilizador Através do Controle de Fase.

Quando a amplitude da tensão de entrada é baixa, o intervalo de condução dos tiristores é maior; quando a amplitude da tensão de entrada é alta, o intervalo de condução dos tiristores é menor.

Esta estrutura apresenta um elevado conteúdo de harmônicas na tensão de saída, sendo necessária a presença de filtros, que resolvem apenas parcialmente o problema; para grande variação do ângulo de disparo dos tiristores, mesmo com filtros, o conteúdo de harmônicas é elevado.

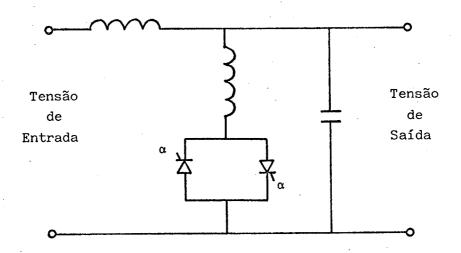

## 1.2.6 - Estabilizador de Tensão Alternada a Tiristor [2]

A estrutura básica do estabilizador é mostrada na Figura 1.6.

Figura 1.6 - Estrutura Básica do Estabilizador a Tiristor.

Neste método, a tensão de saída é uma função do  $\hat{a}\underline{n}$  gulo  $\alpha$  de disparo dos tiristores.

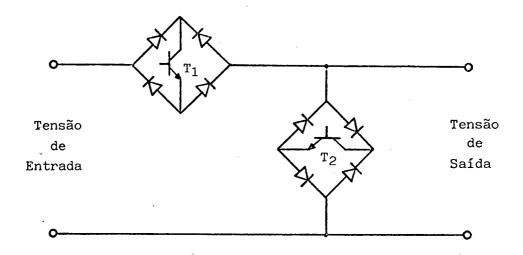

## 1.2.7 - Estabilizador de Tensão Alternada a Transistor [3]

A estrutura básica do estabilizador é mostrada na Figura 1.7.

Neste método os transistores  $T_1$  e  $T_2$  são comandados complementarmente.

A tensão de saída é uma função da razão tempo de condução/tempo de bloqueio do transistor.

Figura 1.7 - Estrutura Básica do Estabilizador a Transistor.

## 1.3 - Conclusão

Quando se analisa os parâmetros que definem um es tabilizador de tensão alternada, são importantes a tolerância na variação da tensão de entrada, a resposta dinâmica, a regulagem estática, a distorção na tensão de saída e também o rendimento. Pode-se ainda considerar o peso e o volume do equipamento.

Na tentativa de se otimizar estes parâmetros temse desenvolvido várias técnicas para estabilização de tensão al

ternada, algumas delas citadas no presente Capítulo. Apesar dis

to nenhuma delas leva a um estabilizador ideal, ou seja, que apre

sente todos os seu parâmetros altamente otimizados. Todas as

técnicas conhecidas apresentam, umas em relação às outras, van

tagens e desvantagens.

Por este motivo pretendemos, através deste traba lho, com a utilização de componentes novos e de técnicas novas, realizar uma estrutura que é original tanto a nível de principio, quanto a nível tecnológico, na tentativa de conseguir parâme tros mais otimizados para um estabilizador.

## CAPITULO 2

### ANÁLISE DO FUNCIONAMENTO DA ESTRUTURA PROPOSTA

### 2.1 - Introdução

Neste Capítulo, será feita a apresentação da estr $\underline{u}$ tura proposta neste trabalho.

Serão analisados dois modos de funcionamento. Inicialmente analisar-se-á o funcionamento da estrutura supondo-se que a tensão de entrada é constante e a tensão de saída é variável (funcionamento como variador estático de tensão alternada). Em seguida, será analisado o funcionamento da estrutura, supondo-se que a tensão de entrada é variável e a tensão de saída é fixa (funcionamento como estabilizador de tensão alternada).

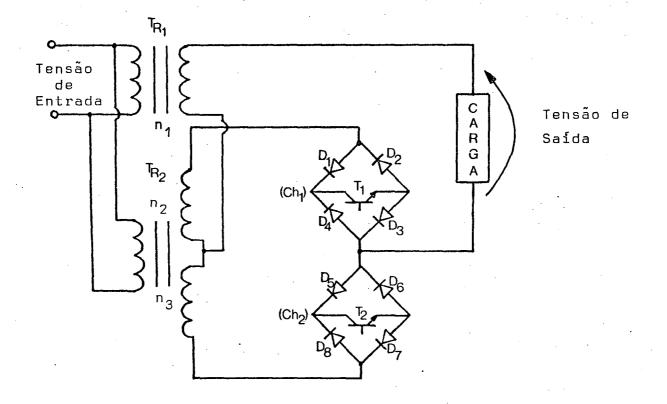

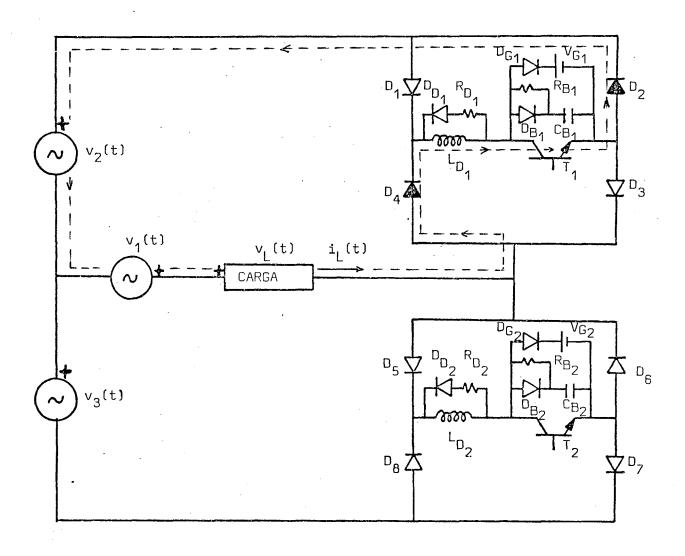

### 2.2 - Apresentação da Estrutura Proposta neste Trabalho

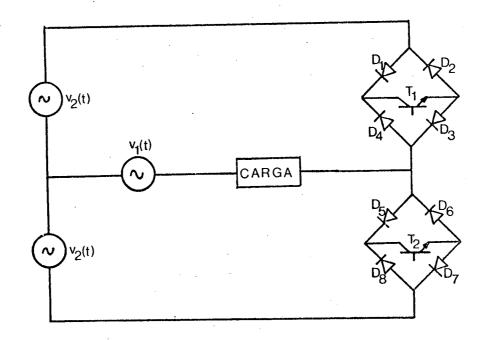

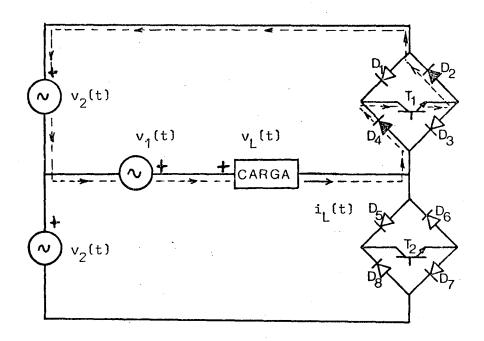

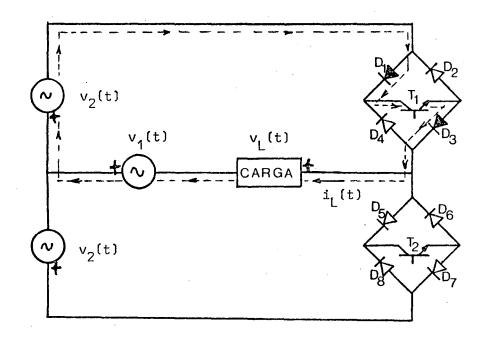

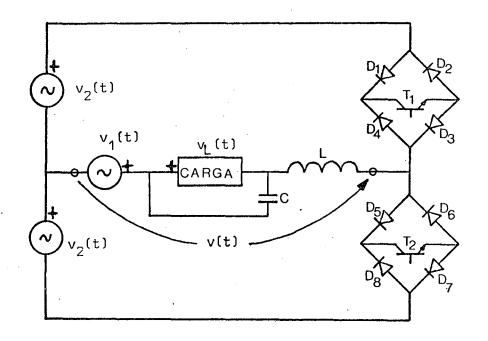

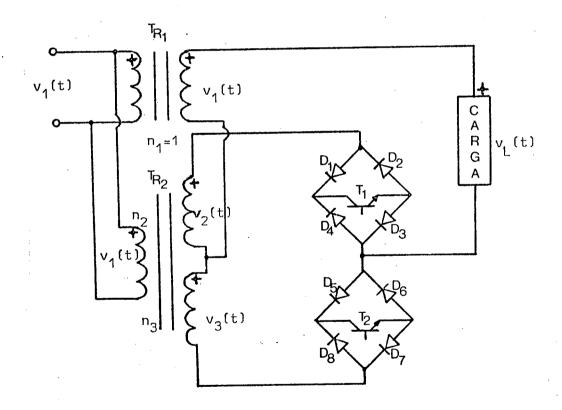

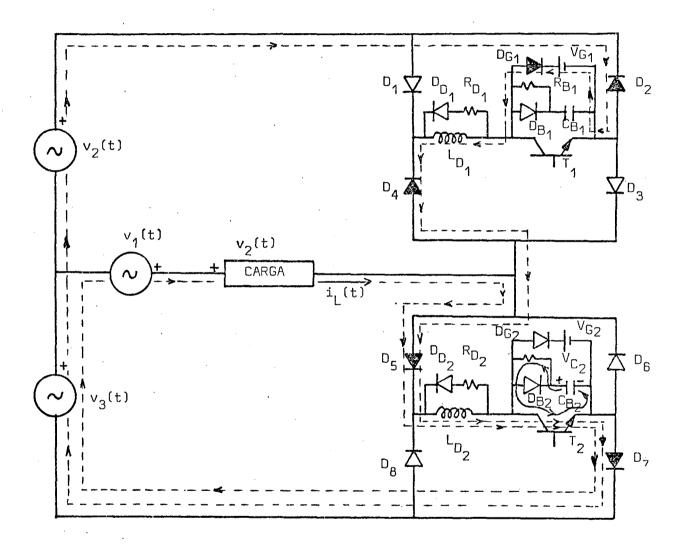

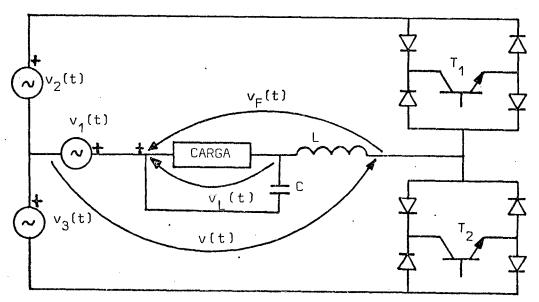

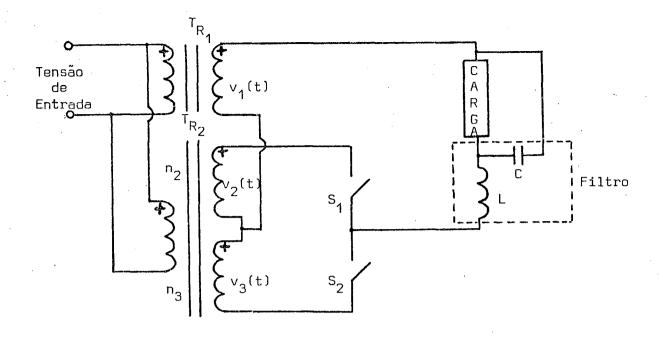

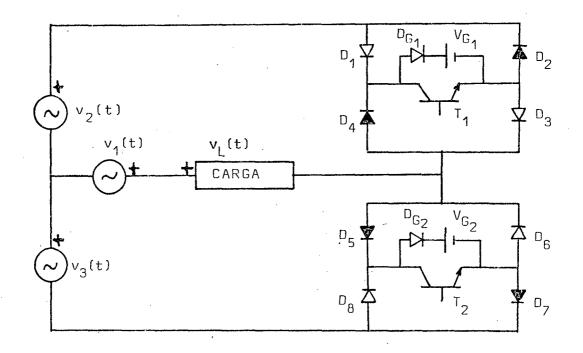

A estrutura proposta no presente trabalho está representada na Figura 2.1.

O transformador  $TR_1$  tem relação de transformação  $n_1$  = 1. Sua função é fazer o isolamento galvânico entre a tensão de entrada e a de saída.

O transformador  $TR_2$  tem dois enrolamentos secund $\underline{\acute{a}}$  rios com relações de transformação iguais a  $n_2$  e  $n_3$ , respect $\underline{\acute{a}}$  vamente. Sua função será vista nos itens seguintes.

Figura 2.1 - Estrutura Proposta Neste Trabalho.

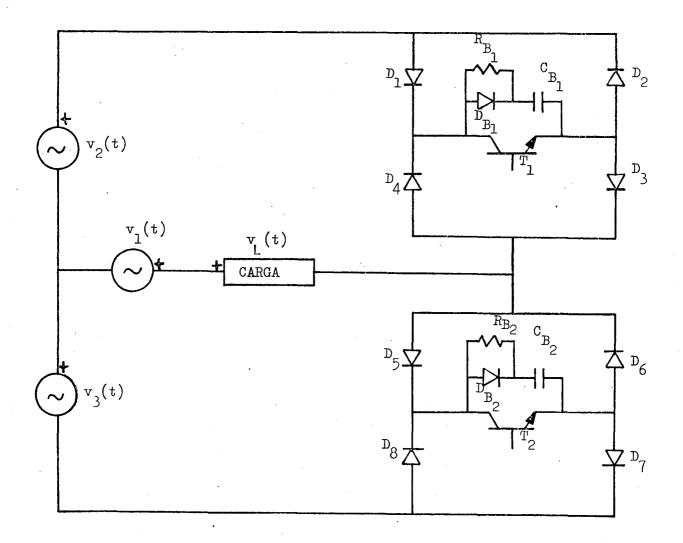

As chaves  $Ch_1$  (composta pelo transistor  $T_1$  e  $p\underline{e}$  los diodos  $D_1$  a  $D_4$ ) e  $Ch_2$  (composta pelo transistor  $T_2$  e  $p\underline{e}$  los diodos  $D_5$  a  $D_8$ ) são bidirecionais.

# 2.3 - <u>Funcionamento com Tensão de Entrada Fixa e Tensão de Saída</u> <u>Variável (Variador Estático de Tensão Alternada Senoidal)</u>

Para este tipo de funcionamento suporemos que  $\$ as relações de transformação do transformador  $\$ TR $_2$  são iguais.

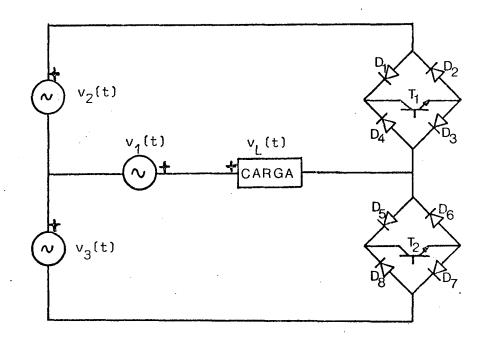

Faremos ainda uma simplificação na estrutura da Figura 2.1, que está representada na Figura 2.2, para facilitar a análise do seu funcionamento.

A carga é resistiva pura.

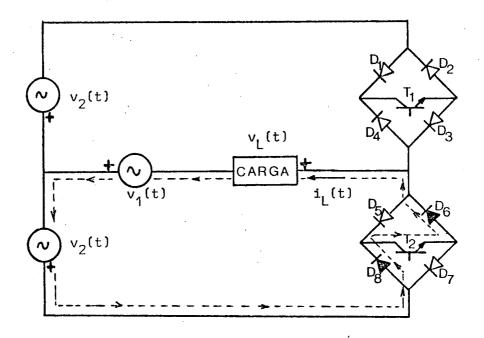

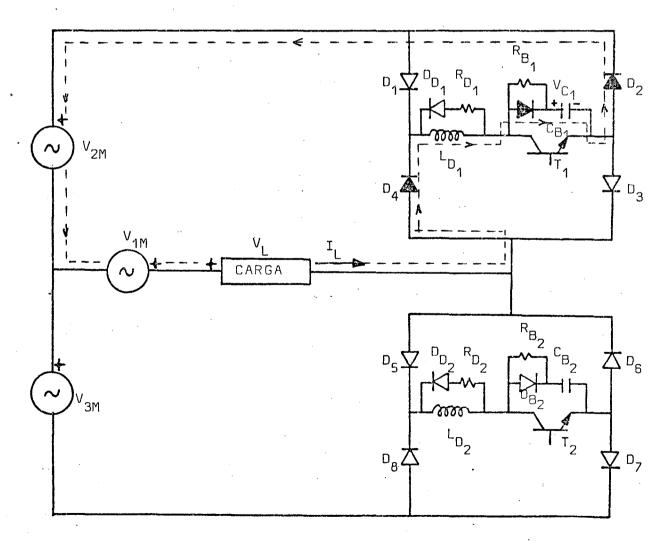

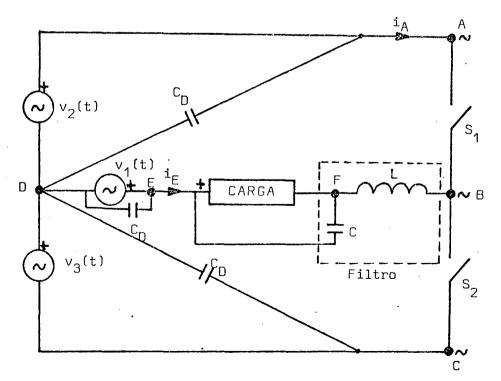

Figura 2.2 - Representação Modificada da Figura 2.1. A fonte  $v_1(t)$  está associada ao secundário de  $TR_1$ . As fontes  $v_2(t)$  estão associadas aos secundários de  $TR_2$ .

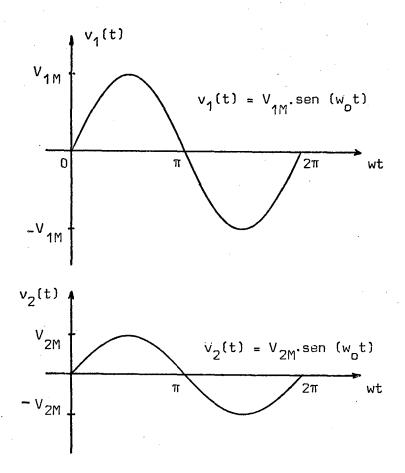

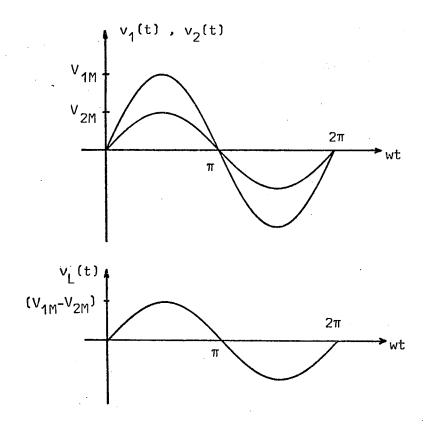

As formas de onda das tensões  $v_1(t)$  e  $v_2(t)$  são mostradas na Figura 2.3.

Figura 2.3 - Formas de Onda das Tensões  $v_1(t)$  e  $v_2(t)$ .

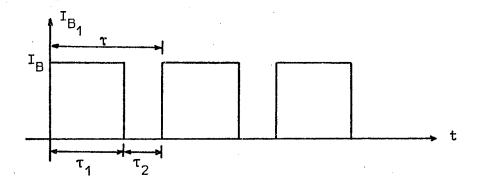

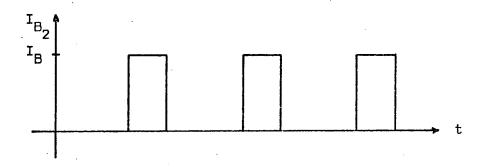

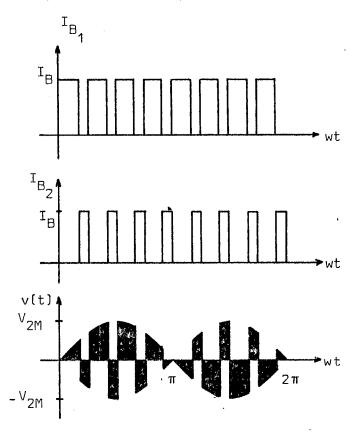

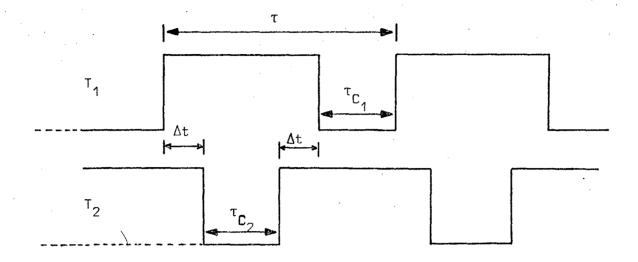

Os transistores  $T_1$  e  $T_2$  da Figura 2.2 são compandados complementarmente. A Figura 2.4 mostra a corrente de base de cada transistor.

Figura 2.4 - Corrente de Base dos Transistores  $T_1$  e  $T_2$ .

Da Figura 2.4, obtém-se:

$$\tau = \tau_1 + \tau_2$$

(Eq 2.1)

Onde:

$\tau_1$  = É o intervalo de tempo em que o transistor  $\tau_1$  está conduzindo.

$\tau_2$  = É o intervalo de tempo em que o transsistor  $\tau_1$  está bloqueado.

$\tau$  = £ o período de chaveamento.

Podemos ainda escrever:

$$\tau = \frac{1}{f}$$

(Eq 2.2)

onde f é a frequência de chaveamento.

Seja a razão cíclica R definida por:

$$\mathbb{R} \stackrel{\triangle}{=} \frac{\tau_1}{\tau}$$

(Eq 2.3)

Através de simples substituições podemos ainda obter para  $\mathbb{R}$ :

$$R = \tau_1 \cdot f$$

(Eq 2.4)

$$\mathbb{R} = \frac{\tau - \tau_2}{\tau}$$

(Eq 2.5)

$$\mathbb{R} = 1 - \frac{\tau_2}{\tau}$$

(Eq 2.6)

## 2.3.1 - Funcionamento da Estrutura com $\mathbb{R} = 1$

Para o funcionamento com  ${\bf R}$  = 1,  ${\bf T}_2$  e os diodos  ${\bf D}_5$  a  ${\bf D}_8$  mantém-se bloqueados o tempo todo.  ${\bf T}_1$  está conduzindo o tempo todo.

Quando  $v_1(t)$  evolui de 0 a  $\pi$ ,  $v_2(t)$  também  $\underline{e}$  volui de 0 a  $\pi$ .  $D_2$  e  $D_4$  conduzem a corrente de carga  $i_L(t)$

através de  $T_1$ .  $D_1$  e  $D_3$  estão bloqueados. A Figura 2.5 ilustra o que acabamos de dizer.

Figura 2.5 - Sequência de Funcionamento quando  $v_1(t)$  e  $v_2(t)$  evoluem de 0 a  $\pi$  com R=1.

Quando  $v_1(t)$  evolui de  $\pi$  a  $2\pi$ ,  $v_2(t)$  também  $\underline{e}$  volui de  $\pi$  a  $2\pi$ . Nestas condições  $D_1$  e  $D_3$  conduzem a corrente de carga através de  $T_1$ .  $D_2$  e  $D_4$  estão bloqueados. A  $F\underline{i}$  gura 2.6 mostra esta sequência.

Figura 2.6 - Sequência de Funcionamento quando  $v_1$ (t)  $v_2$ (t) evoluem de  $\pi$  a  $2\pi$  com  $\mathbb{R}$  = 1.

Através das Figuras 2.5 e 2.6 observa-se que a tensão de carga  $\,v_L^{}(t)\,$  será em qualquer instante:

$$v_L(t) = v_1(t) - v_2(t)$$

(Eq 2.7)

A Figura 2.7 mostra as tensões  $\,v_1^{}\left(t\right)$  ,  $\,v_2^{}\left(t\right)$  e  $\,v_L^{}\left(t\right)$  .

Figura 2.7 - Tensão  $v_1(t)$  ,  $v_2(t)$  e  $v_L(t)$  para  $\mathbb{R} = 1$ .

## 2.3.2 - Funcionamento da Estrutura com $\mathbb{R} = 0$

Para  $\mathbf{R}=\mathbf{0}$  ,  $\mathbf{T}_1$  e os diodos  $\mathbf{D}_1$  a  $\mathbf{D}_4$  mantémse bloqueados o tempo todo.  $\mathbf{T}_2$  está conduzindo o tempo todo.

Quando  $v_1(t)$  e  $v_2(t)$  evoluem de 0 a  $\pi$ , os dio dos  $D_5$  e  $D_7$  conduzem a corrente de carga.  $D_6$  e  $D_8$  estão bloqueados. A Figura 2.8 ilustra esta sequência.

Figura 2.8 - Sequência de Funcionamento quando  $v_1(t)$  e  $v_2(t)$  evoluem de 0 a  $\pi$  com  $\mathbb{R}$  = 0.

No semi-ciclo sequinte, quando  $v_1(t)$  e  $v_2(t)$  e voluem de  $\pi$  a  $2\pi$ ,  $D_5$  e  $D_7$  bloqueiam.  $D_6$  e  $D_8$  conduzem a corrente de carga. A Figura 2.9 ilustra o que acabamos de dizer.

Figura 2.9 - Sequência de Funcionamento quando  $v_1(t)$  e  $v_2(t)$  evoluem de  $\pi$  a  $2\pi$  com  $\Re = 0$ .

Através das Figuras 2.8 e 2.9 observa-se que a tensão de carga  $\,{\rm v}_{\rm L}({\rm t})\,$  será em qualquer instante:

$$v_L(t) = v_1(t) + v_2(t)$$

(Eq 2.8)

A Figura 2.10 mostra as tensões  $\textbf{v}_1(\textbf{t})$  ,  $\textbf{v}_2(\textbf{t})$  e  $\textbf{v}_L(\textbf{t})$  .

Figura 2.10 - Tensão  $v_1(t)$  ,  $v_2(t)$  e  $v_L(t)$  para  $\mathbf{R} = 0$ .

# 2.3.3 - Funcionamento da Estrutura com R = 0,5

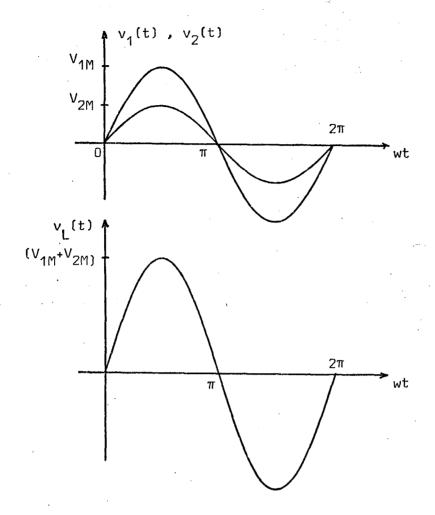

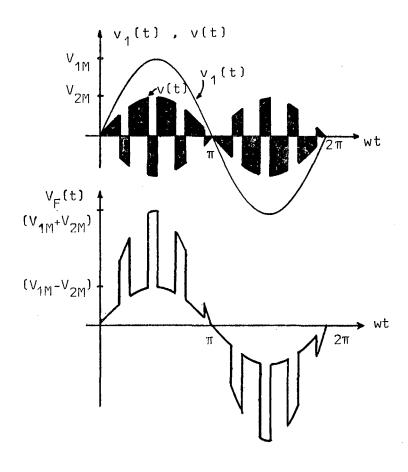

$\label{eq:Vamos considerar o circuito da Figura 2.11, onde est\'a indicada a tensão v(t).$

Figura 2.11 - Indicação da Tensão v(t).

As formas de onda da corrente de base dos tra $\underline{n}$  sistores  $\underline{T}_1$  e  $\underline{T}_2$  e da tensão  $\underline{v}(t)$  são mostradas na Figura 2.12.

Figura 2.12 - Corrente de Base nos Transistores  $T_1$  e  $T_2$  e Tensão v(t).

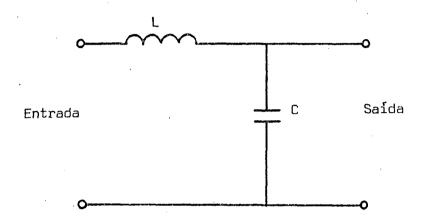

Se introduzirmos no circuito da Figura 2.11 um filtro LC, como mostra a Figura 2.13, as harmônicas de v(t) serão filtradas. Como a componente fundamental de v(t) é nula, teremos:

$$v_L(t) = v_1(t)$$

(Eq 2.9)

Figura 2.13 - Filtro LC introduzido no circuito da F $\underline{i}$ gura 2.11.

## 2.3.4 - Funcionamento da Estrutura com 0,5 < R < 1

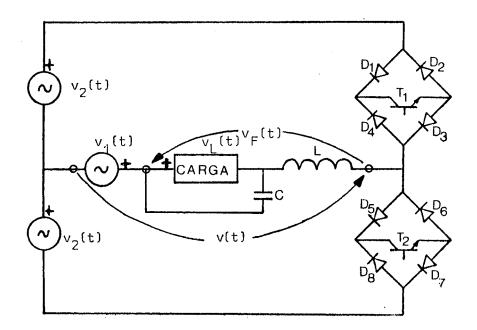

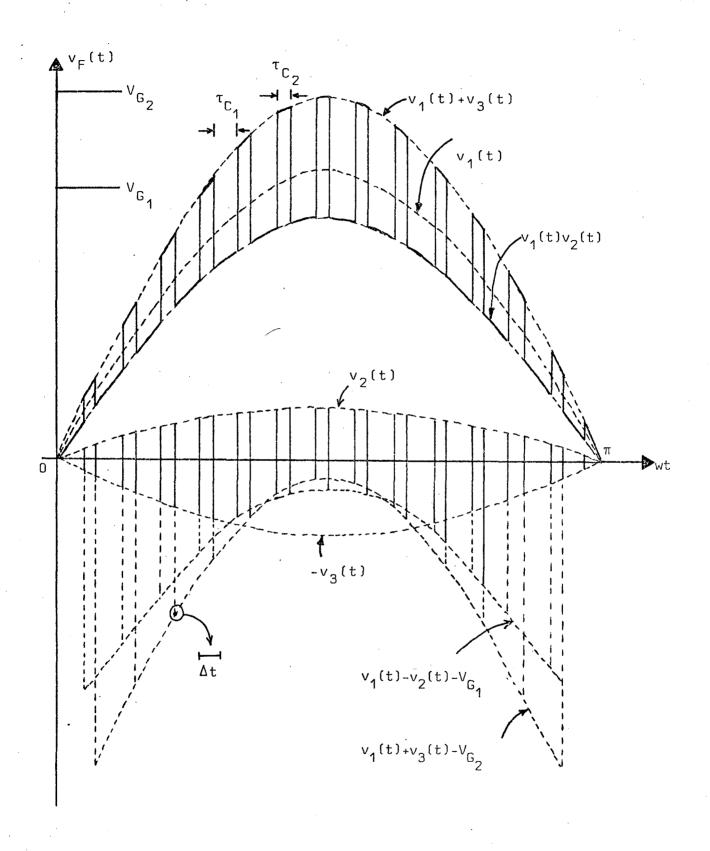

Vamos considerar o circuito da Figura 2.14, onde estão indicadas as tensões v(t) e  $v_F(t)$ , para um modo de funcionamento onde a razão cíclica se situa entre 0,5 e 1.

Figura 2.14 - Indicação das Tensões v(t) e  $v_F(t)$ .

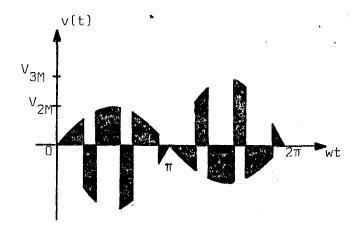

A Figura 2.15 mostra as correntes de base dos tra $\underline{n}$  sistores  $T_1$  e  $T_2$  e a tensão v(t).

Figura 2.15 - Corrente de Base de  $T_1$  e  $T_2$  e Tensão v(t).

Nestas condições, a tensão  $v_F(t)$  indicada no circuito da Figura 2.14 é em qualquer instante:

$$v_F(t) = v_1(t) - v(t)$$

(Eq 2.10)

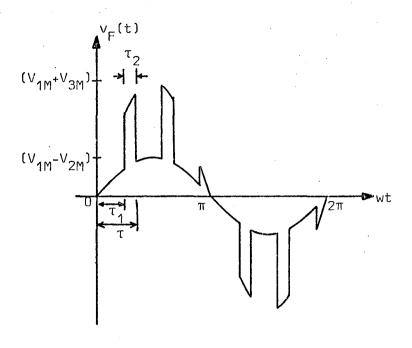

O aspecto da tensão  $v_F^{}(t)$  é mostrado na Figura 2.16.

Figura 2.16 - Aspecto da Tensão  $v_F(t)$ .

A tensão de carga  $v_L(t)$  é obtida a partir da filtragem de  $v_F(t)$  pelo filtro LC. Como pretendemos trabalhar com uma frequência de chaveamento elevada, as harmônicas que se fizerem presentes também possuirão frequências desta ordem ou maior, facilitando assim a filtragem da tensão  $v_L(t)$  a ser apli

cada sobre a carga.

De uma forma geral, para qualquer modo de funcio namento, daqueles que foram analisados, a tensão de carga  $v_L(t)$  será:

$$v_L(t) = v_1(t) + v_c(t) \cdot [1 - 2 R]$$

(eq 2.11)

sendo v<sub>c</sub>(t) a componente fundamental da tensão v(t).

No estudo feito até agora, supusemos a tensão de entrada constante e mostramos que através da modificação da razão cíclica podemos variar a tensão de saída sobre a carga de  $(v_1 - v_2)$  até  $(v_1 + v_2)$ , sendo  $v_1$  e  $v_2$  os valores eficazes das tensões  $v_1$  (t) e  $v_2$  (t), respectivamente.

A seguir verificaremos como se pode modificar a razão cíclica para, a partir de uma tensão de entrada variável, obtermos uma tensão de saída constante sobre a carga.

2.4 - <u>Funcionamento com Tensão de Entrada Variável e Tensão de</u>

Saída Fixa (Estabilizador de Tensão Alternada Senoidal)

# 2.4.1 - Introdução

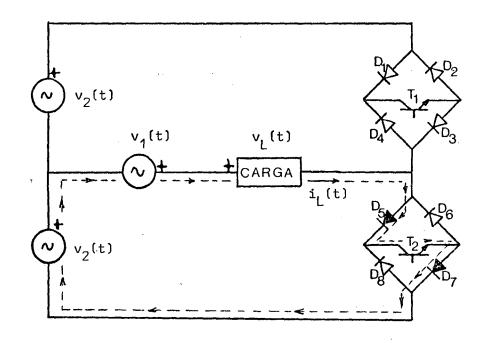

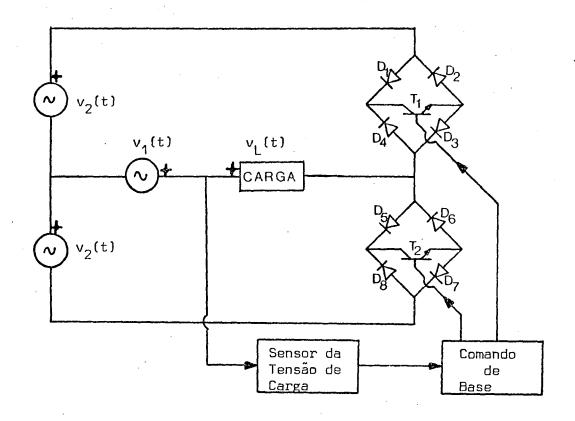

O circuito da Figura 2.2 pode também funcionar como estabilizador de tensão alternada, se nele for introduzido um circuito que monitore a tensão de carga e atue na razão cíclica (Figura 2.17).

Figura 2.17 - Estrutura Básica do Estabilizador.

Se num dado instante houver uma variação na tensão de entrada  $v_1(t)$ , que é a própria tensão que se deseja sobre a carga, esta aparecerá instantaneamente sobre ela. O sensor da tensão de carga atuará sobre o comando de base dos transisto res, fazendo com que a razão cíclica assuma um valor tal que a tensão de carga volte ao seu valor nominal.

A tensão de entrada pode sofrer variações posit<u>i</u> vas ou negativas, em relação ao valor nominal.

Com o circuito da Figura 2.17, a tensão de carga  $v_L(t)$  será estabilizada para variações não simétricas de  $v_1(t)$  em relação ao seu valor nominal, porque as relações de transformação do transformador  $TR_2$  são iquais (a  $n_2$ ) conforme suposto no item 2.3.

Vamos provar isto que acabamos de dizer.

Sejam:

V<sub>T.</sub> = valor eficaz da tensão de carga.

V<sub>1</sub> = valor eficaz da tensão de entrada.

$n_2$  = relação de transformação dos dois secundários de TR<sub>2</sub>.

$\Delta V_1^+$  = valor eficaz da máxima variação positiva da tensão de entrada.

ΔV<sub>1</sub> = Valor eficaz da máxima variação ne gativa da tensão de entrada.

Quando a tensão de entrada sobe até  $(V_1 + \Delta V_1^+)$ , o transistor  $T_1$  deve estar conduzindo o tempo todo e o transistor  $T_2$  deve estar bloqueado o tempo todo. A tensão de carga, como sabemos, deve ficar constante, ou seja,  $V_L = V_1$ . Assim,

$$V_1 = V_1 + \Delta V_1^{\dagger} - n_2 \cdot (V_1 + \Delta V_1^{\dagger})$$

(Eq 2.12)

Como  $V_L = V_1$ , temos:

$$\Delta V_1^+ = n_2 \cdot (V_1 + \Delta V_1^+)$$

(Eq 2.13)

Da equação 2.13 tiramos:

$$\frac{\Delta V_1^+}{V_1} = \frac{n_2}{1 - n_2}$$

(Eq 2.14)

Quando a tensão de entrada desce até  $(V_1 - \Delta V_1^-)$ , o transitor  $T_1$  deve estar bloqueado o tempo todo e o transistor  $T_2$  deve estar conduzindo o tempo todo. Como a tensão de carga de ve ficar constante, temos:

$$V_L = V_1 - \Delta V_1 + n_2 (V_1 - \Delta V_1)$$

(Eq 2.15)

Como  $V_L = V_1$ , obtemos:

$$\Delta V_1 = n_2 (V_1 - \Delta V_1)$$

(Eq 2.16)

Da Equação 2.16 tiramos:

$$\frac{\Delta V_1^-}{V_1} = \frac{n_2}{1 + n_2}$$

(Eq 2.17)

Desta forma, as Equações 2.14 e 2.17 mostram que a máxima variação positiva ( $\Delta V_1^{\dagger}$ ) e negativa ( $\Delta V_1^{\dagger}$ ) da tensão de entrada são diferentes e ambas dependem das relações de transforção  $n_2$  do transformador  $TR_2$ .

Podemos concluir então que se quisermos especificar que a máxima variação positiva e a máxima variação negativa da tensão de entrada devem ser iguais, então as relações de transformação do transformador  $TR_2$  devem ser diferentes.

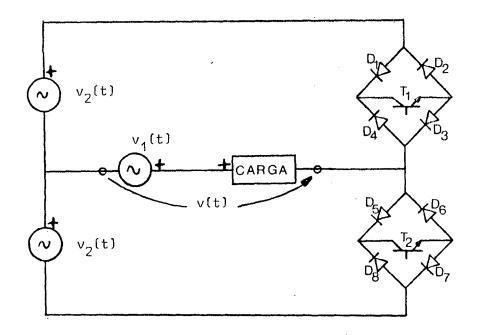

Desta forma a estrutura que iremos analisar daqui para frente é aquela mostrada na Figura 2.18 e de forma mais simplificada na Figura 2.19.

Figura 2.18 - Estrutura do Estabilizador com as Relações de Transformação do Transformador  ${\rm TR}_2$  diferentes.

As relações de transformação do Transformador TR<sub>2</sub> serão determinadas no item seguinte.

As sequências de funcionamento do circuito da Figura 2.19 são as mesmas descritas anteriormente, mudando apenas os níveis de tensão dos secundários do transformador  $TR_2$ .

Figura 2.19 - Representação Simplificada da Estrutura da Figura 2.18.

# 2.4.2 - Relações de Transformação do Transformador TR2

Consideremos o circuito da Figura 2.18.

Sejam:

V<sub>1</sub> = valor eficaz da tensão de entrada.

V<sub>T.</sub> = valor eficaz da tensão da carga.

ΔV<sub>1</sub> = máxima variação especificada para a tensão da rede, em volts eficazes.

$V_2$  e  $V_3$  = tensões eficazes nos secundários do transformador  $TR_2$ .

Quando as tensões primária de  $TR_1$  e de  $TR_2$  sobem até  $(V_1 + \Delta V_1)$ , a tensão secundária de  $TR_1$  também sobe até  $(V_1 + \Delta V_1)$  uma vez que a sua relação de transformação é  $n_1 = 1$ .

Nestas condições o transistor  $T_1$  deve estar conduzindo e o transistor  $T_2$  deve estar bloqueado, ambos, o tempo todo.

Assim podemos escrever para a tensão de carga:

$$V_{L} = V_{1} + \Delta V_{1} - V_{2}$$

(Eq 2.18)

como:

$$V_{L} = V_{1}$$

(Eq 2.19)

então:

$$V_2 = \Delta V_1$$

(Eq 2.20)

Portanto, uma das relações de transformação de  $\label{eq:transformação} {\tt TR}_2 \mbox{ , } {\tt n}_2 \mbox{ , será dada por:}$

$$n_2 = \frac{\Delta V_1}{V_1 + \Delta V_1}$$

(Eq 2.21)

Quando as tensões primária de  $\text{TR}_1$  e de  $\text{TR}_2$  descem até  $(\text{V}_1-\Delta\text{V}_1)$ , a tensão secundária de  $\text{TR}_1$  também desce até  $(\text{V}_1-\Delta\text{V}_1)$ .

Nestas condições o transistor  $T_1$  deve estar bloquado e o transistor  $T_2$  deve estar conduzindo, ambos, o tempo todo.

Assim podemos escrever:

$$V_{L} = V_{1} - \Delta V_{1} + V_{3}$$

(Eq 2.22)

Como:

$$v_{L} = v_{1}$$

(Eq 2.23)

Então:

$$v_3 = \Delta v_1 \tag{Eq 2.24}$$

Portanto, a outra relação de transformação de  ${\tt TR}_2$ ,  ${\tt n}_3$ , será dada por:

$$n_3 = \frac{\Delta v_1}{v_1 - \Delta v_1}$$

(Eq. 2.25)

# 2.4.3 - <u>Variação da Razão Cíclica em Função da Variação da Ten</u> são de Entrada

Para o circuito da Figura 2.18, o valor eficaz da tensão de carga num determinado instante será:

$$V_{L} = (V_{1} \pm \delta \ V_{1}) - n_{2} \cdot (V_{1} \pm \delta \ V_{1}) \cdot \mathbb{R} + n_{3} \cdot (V_{1} \pm \delta \ V_{1}) \cdot (1 - \mathbb{R})$$

(Eq 2.26)

Onde:

V<sub>I.</sub> = valor eficaz da tensão na carga.

V<sub>1</sub> = valor eficaz da tensão de entrada.

$n_2$ ,  $n_3$  = relações de transformação de  $TR_2$ .

R = razão cíclica.

δ V<sub>1</sub> = variação ocorrida na tensão de entrada em um dado intervalo de tempo, em volts eficazes.

Se supusermos que  $\delta$  V<sub>1</sub> pode ser positiva ou neg<u>a</u> tiva, podemos reescrever a Equação 2.26:

$$V_{L} = (V_{1} + \delta V_{1}) - n_{2} (V_{1} + \delta V_{1}) \mathbb{R} + n_{3} (V_{1} + \delta V_{1}) (1 - \mathbb{R})$$

(Eq 2.27)

Desenvolvendo a Equação 2.27 e lembrando que a tensão na carga deve ser a qualquer instante  $V_L = V_1$ , podemos obter uma expressão para a razão cíclica  $\mathbb R$  em função de  $\delta$   $V_1$ . Então, a partir da Equação 2.27, obtemos:

$$V_{L} = V_{1} + \delta V_{1} - n_{2} V_{1} R - n_{2} \delta V_{1} R + n_{3} V_{1} - n_{3} V_{1} R + n_{3} \delta V_{1} - n_{3} \delta V_{1} R$$

$$(Eq 2.28)$$

Lembrando que  $V_L = V_1$  , temos:

$$0 = \mathbb{R} \cdot (-n_2 \, V_1 - n_3 \, V_1 - n_2 \, \delta \, V_1 - n_3 \, \delta \, V_1) + n_3 \, V_1 + \delta \, V_1 + n_3 \, \delta \, V_1$$

(Eq. 2.29)

Assim:

$$\mathbb{R} = \frac{n_3 \cdot (V_1 + \delta V_1) + \delta V_1}{n_2 \cdot (V_1 + \delta V_1) + n_3 \cdot (V_1 + \delta V_1)}$$

(Eq 2.30)

A Equação 2.30 mostra como varia a razão cíclica  ${\bf R}$  em função de  $\delta$   ${\bf V_1}$ .

Da Equação 2.30, podemos verificar várias situa ções:

14) Se  $\delta$  V<sub>1</sub> =  $\Delta$ V<sub>1</sub> (máxima variação positiva especificada para a tensão da rede em Volts eficazes), obtemos das Equações 2.21, 2.25 e 2.30:

$\mathbf{R} = 1$

2ª) Se  $\delta V_1 = -\Delta V_1$  (máxima variação negativa especificada para a tensão da rede em Volts eficazes), obtemos das Equações 2.21, 2.25 e 2.30:

$\mathbb{R} = 0$

3ª) Se  $\delta$  V<sub>1</sub> , num determinado instante, for igual a zero obtemos da Equação 2.30:

$$\mathbf{R} = \frac{n_3}{n_2 + n_3}$$

(Eq 2.31)

A Equação 2.31 mostra que, se num determinado momento a tensão de entrada estiver constante, a razão cíclica  $\mathbb{R}$  depende apenas da relações de transformação do transformador  $\mathrm{TR}_2$ .

Será feito a seguir um desenvolvimento da Equação 2.30, para que se possa verificar graficamente a variação da razão cíclica em função de  $\delta$  V<sub>1</sub>.

A partir das Equações 2.21, 2.25 e 2.30, obtemos:

$$\mathbf{R} = \frac{\frac{\Delta V_1}{V_1 - \Delta V_1} \cdot (V_1 + \delta V_1) + \delta V_1}{\frac{\Delta V_1}{(V_1 + \Delta V_1)} \cdot (V_1 + \delta V_1) + \frac{\Delta V_1}{(V_1 - \Delta V_1)} \cdot (V_1 + \delta V_1)}$$

(Eq 2.32)

Desenvolvendo a Equação 2.32, obtemos:

$$\mathbb{R} = \frac{\frac{\Delta V_{1}}{V_{1}} + \left(\frac{\Delta V_{1}}{V_{1}}\right)^{2} + \frac{\delta V_{1}}{V_{1}} + \frac{\delta V_{1}}{V_{1}} \cdot \frac{\Delta V_{1}}{V_{1}}}{2 \cdot \left(\frac{\Delta V_{1}}{V_{1}} + \frac{\Delta V_{1}}{V_{1}} \cdot \frac{\delta V_{1}}{V_{1}}\right)}$$

(Eq 2.33)

Se definirmos:

$$A \stackrel{\triangle}{=} \frac{\Delta V_1}{V_1}$$

(Eq 2.34)

módulo da máxima variação percentual especificada para a variação na tensão de entrada.

е

$$B \stackrel{\Delta}{=} \frac{\delta V_1}{V_1}$$

(Eq 2.35)

valor algébrico da variação percentual que ocorre na tensão de entrada num dado intervalo de tempo

podemos reescrever a Equação 2.33:

$$\mathbf{R} = \frac{A^2 + A + B + AB}{2.(A + AB)}$$

(Eq 2.36)

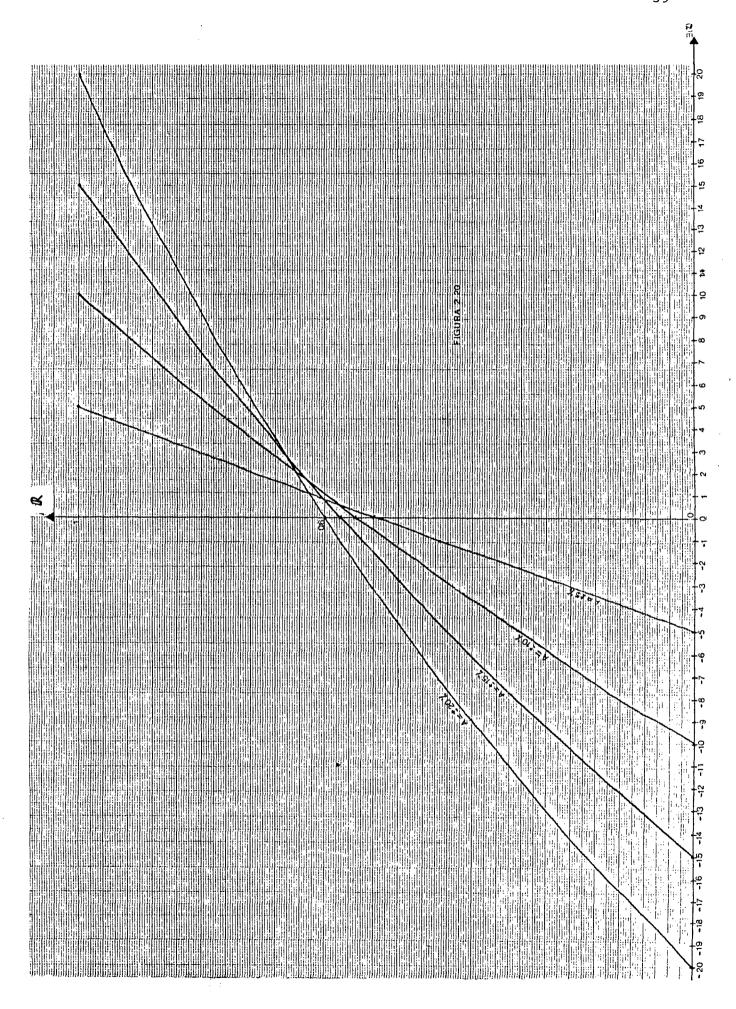

A partir das Equações 2.34, 2.35 e 2.36, vamos plotar uma família de curvas ( $\mathbb R \times \mathbb B$ ), tomando A como parâmetro.

O gráfico é o da Figura 2.20.

### 2.5 - Conclusão

Neste Capítulo foi apresentada a estrutura proposta neste trabalho.

Mostramos o funcionamento da estrutura com tensão de entrada fixa e tensão de saída variável e, também, com tensão de entrada variável e tensão de saída fixa.

Mostramos ainda que no funcionamento da estrutura como estabilizador, se quisermos especificar uma variação simé trica para a tensão de entrada, as relações de transformação de

Figura 2.20

${\tt TR}_2$  devem ser diferentes. Mostramos como determinar estas  ${\tt rel}\underline{\tt a}$  ções.

Finalmente determinamos uma expressão e um ábaco, que permitem verificar como varia a razão cíclica em função da variação na tensão de entrada, para manter a tensão de saída es tabilizada.

#### CAPÍTULO 3

#### DIMENSIONAMENTO DOS TRANSFORMADORES

#### 3.1 - Introdução

No Capítulo anterior determinamos expressões dadas pelas equações 2.21 e 2.25 para o dimensionamento das relações de transformação,  $n_2$  e  $n_3$ , de  $TR_2$ .

Na determinação destas expressões, considerou-se que a razão cíclica pode assumir o valor zero ou um. Sabemos que isto não acontece na prática, ou seja, a razão cíclica pode assumir um valor máximo e mínimo diferentes de um e zero.

Neste Capítulo obteremos expressões que per mitem determinar as relações de transformação de TR2, adotando para a razão cíclica um valor mínimo e um máximo diferentes de zero e um.

Além disso, também serão determinadas as potências dos transformadores  ${

m TR}_1$  e  ${

m TR}_2$ , juntamente com um exemplo de cá $\underline{1}$  culo.

3.2 - <u>Determinação das Relações de Transformação de</u> TR<sub>2</sub> (n<sub>2</sub> e n<sub>3</sub>)

<u>Adotando-se uma Razão Cíclica Máxima e uma Mínima diferen</u>

<u>tes de Um e Zero</u>

Consideremos a estrutura da Figura 2.18.

Sejam:

V<sub>T.</sub> = Valor eficaz da tensão de carga.

V<sub>1</sub> = Valor eficaz da tensão de entrada.

$\Delta V_1$  = Módulo da máxima variação especifica da para a tensão de entrada, em volts eficazes.

$V_2$  e  $V_3$  = Valor eficaz das tensões nos secund $\underline{\acute{a}}$  rios de TR<sub>2</sub>.

$R_{max}$  = Razão cíclica máxima.

R<sub>min</sub> = Razão cíclica minima.

Sabe-se que:

$$\mathbf{R}_{\min} = 1 - \mathbf{R}_{\max} \qquad (Eq 3.1)$$

Quando a tensão de entrada subir até  $(v_1 + \Delta v_1)$  a razão cíclica deve ser máxima, ou seja, o transistor  $T_1$  deve estar conduzindo muito mais tempo que o transistor  $T_2$ .

Nestas condições, a tensão de carga será dada por:

$$V_{L} = V_{1} + \Delta V_{1} - V_{2} \cdot \mathbb{R}_{max} + V_{3} \cdot \mathbb{R}_{min}$$

(Eq 3.2)

Como:  $V_L = V_1$  , temos:

$$0 = \Delta V_1 - V_2 \cdot \mathbb{R}_{max} + V_3 \cdot (1 - \mathbb{R}_{max})$$

(Eq 3.3)

Assim:

$$V_2 = \frac{\Delta V_1 + V_3 \cdot (1 - R_{max})}{R_{max}}$$

(Eq 3.4)

Quando a tensão de entrada descer até  $(V_1 - \Delta V_1)$  a razão cíclica deve ser mínima, ou seja, o transistor  $T_2$  deve estar conduzindo muito mais tempo que o transistor  $T_1$ .

Nestas condições, temos:

$$V_{L} = V_{1} - \Delta V_{1} - V_{2} \cdot \mathbb{R}_{min} + V_{3} \cdot \mathbb{R}_{max}$$

(Eq 3.5)

Como:  $V_L = V_1$  , temos:

$$0 = -\Delta V_1 - V_2 \cdot (1 - \mathbb{R}_{m\acute{a}x}) + V_3 \cdot \mathbb{R}_{m\acute{a}x}$$

(Eq 3.6)

Assim:

$$V_3 = \frac{\Delta V_1 + V_2 \cdot (1 - R_{max})}{R_{max}}$$

(Eq 3.7)

Substituindo a Equação 3.7 na Equação 3.4, obtemos:

$$V_2 = \frac{\Delta V_1 + \frac{[\Delta V_1 + V_2 \cdot (1 - R_{m\acute{a}x})]}{R_{m\acute{a}x}} \cdot (1 - R_{m\acute{a}x})}{R_{m\acute{a}x}}$$

(Eq 3.8)

Desenvolvendo a Equação 3.8, obtemos:

$$V_2 = \frac{\Delta V_1}{(2 R_{max} - 1)}$$

(Eq 3.9)

Como sabemos que:

$$n_2 = \frac{v_2}{v_1 + \Delta v_1}$$

(Eq 3.10)

Podemos obter:

$$n_2 = \frac{\Delta V_1}{(V_1 + \Delta V_1) \cdot (2 \mathbb{R}_{max} - 1)}$$

(Eq 3.11)

Usando um raciocínio analógo podemos obter para n3:

$$n_3 = \frac{\Delta V_1}{(V_1 - \Delta V_1) \cdot (2 R_{max} - 1)}$$

(Eq 3.12)

Desta forma, as Equações 3.11 e 3.12 permitem cal cular as relações de transformação de  $TR_2$ , para uma determinada razão cíclica máxima (e mínima) especificada.

# 3.3 - Determinação de um Ábaco para o Cálculo de n2 e n3

A partir deste ábaco, pode-se fazer:

- 10) A determinação de  $n_2$  considerando  $R_{max} = 1$  e  $R_{min} = 0$ .

- 29) A determinação de  $n_3$  considerando  $R_{m\tilde{a}x} = 1$  e  $R_{min} = 0$ .

- 39) A determinação de  $n_2$  considerando  $R_{m\acute{a}x} = 0.9$  e  $R_{min} = 0.1$ .

- 49) A determinação de  $n_3$  considerando  $\mathbb{R}_{max} = 0.9$  e  $\mathbb{R}_{min} = 0.1$ .

Estas curvas permitem a determinação de  $n_2$  e  $n_3$  para uma máxima variação especificada (A%) para a tensão da rede, no projeto do estabilizador.

Sejam as seguintes Equações:

$$A = \frac{\Delta V_1}{V_1}$$

(Eq 3.13)

$$n_2 = \frac{\Delta V_1}{V_1 + \Delta V_1}$$

(Eq 3.14)

$$n_3 = \frac{\Delta V_1}{V_1 - \Delta V_1}$$

(Eq 3.15)

Combinando as Equações 3.13 e 3.14 e ainda 3.13 e 3.15, obtemos:

$$n_2 = \frac{A}{1 + A}$$

(Eq 3.16)

$$n_3 = \frac{A}{1 - A}$$

(Eq 3.17)

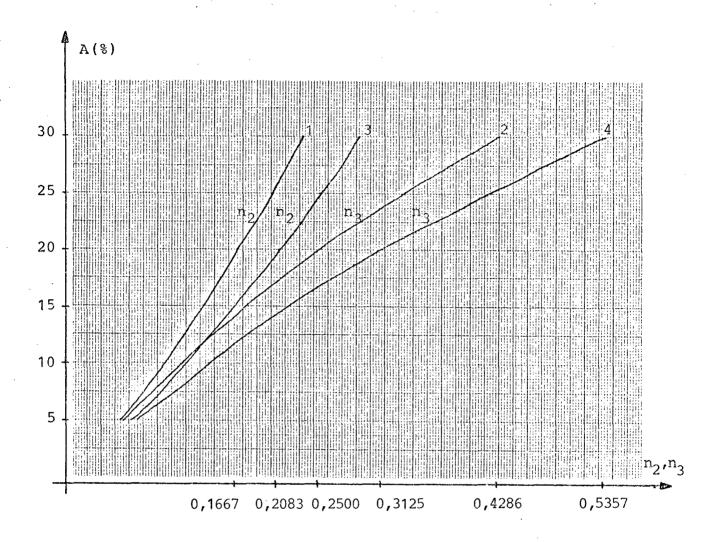

As Equações 3.16 e 3.17 determinam, respectivamente, as curvas l e 2 no ábaco da Figura 3.1.

Consideremos as Equações 3.11, 3.12 e 3.13. A par tir delas podemos obter:

$$n_2 = \frac{A}{(1 + A) \cdot (2 R_{max} - 1)}$$

(Eq 3.18)

$$n_3 = \frac{A}{(1 - A) \cdot (2 R_{max} - 1)}$$

(Eq 3.19)

As Equações 3.18 e 3.19 determinam, respectivamente as curvas 3 e 4 no ábaco da Figura 3.1.

- Curva 1 Determinação de  $n_2$  em função de A% para  $\mathbb{R}_{\text{max}} = 1 \text{ e } \mathbb{R}_{\text{min}} = 0 \text{ (caso ideal)}.$

- Curva 2 Determinação de  $n_3$  em função de A% para  $\mathbb{R}_{\text{máx}} \ = \ 1 \ e \ \mathbb{R}_{\text{mín}} \ = \ 0 \ \text{(caso ideal)}$

- Curva 3 Determinação de  $n_2$  em função de A% para  $\mathbb{R}_{\text{máx}} = 0.9 \text{ e } \mathbb{R}_{\text{min}} = 0.1 \text{ (caso real).}$

- Curva 4 Determinação de  $n_3$  em função de A% para  $\mathbb{R}_{\text{max}} = 0.9 \text{ e } \mathbb{R}_{\text{min}} = 0.1 \text{ (caso real)}.$

# 3.4 - Potência do Transformador TR1

A potência do transformador TR<sub>1</sub> é dada pela Equ<u>a</u> ção 3.20:

$$P_1 = P_L + \Delta V_1 \cdot I_L$$

(Eq 3.20)

Onde:

P<sub>1</sub> = Potência do transformador TR<sub>1</sub>.

$P_L = V_1 \cdot I_L = Potência da carga.$

$\Delta V_1$  = Máxima variação especificada para a tensão de entrada, em Volts eficazes.

I<sub>I.</sub> = Corrente eficaz na carga.

V<sub>1</sub> = Tensão eficaz de entrada.

# 3.5 - Potência do Transformador TR2

A potência do transformador TR<sub>2</sub> é dada pela Equ<u>a</u> ção.3.21:

$$P_2 = n_2 \cdot (V_1 + \Delta V_1) \cdot I_L + n_3 \cdot (V_1 + \Delta V_1) \cdot I_L$$

(Eq 3.21)

Substituindo as Equações 3.11 e 3.12 na Equação 3.21, obtemos:

$$P_2 = \frac{\Delta V_1 \cdot I_L}{(2 R_{max} - 1)} \cdot \left(1 + \frac{V_1 + \Delta V_1}{V_1 - \Delta V_1}\right)$$

(Eq 3.22)

Se supusermos, num caso ideal, que  $\mathbb{R}_{\max} = 1$ , a potência do transformador  $\mathrm{TR}_2$  será dada por:

$$P_2 = \Delta V_1 \cdot I_L \cdot \left(1 + \frac{V_1 + \Delta V_1}{V_1 - \Delta V_1}\right)$$

(Eq 3.23)

3.6 - Determinação de um Ábaco para o Cálculo da Potência dos <u>Transformadores</u> TR<sub>1</sub> e TR<sub>2</sub>

A partir da Equação 3.20, podemos expressar a  $~p\underline{o}$  tência do transformador  $TR_1$  ,  $P_1$  , em pu:

$$P_1 = V_1.I_L + \Delta V_1.I_L$$

(Eq 3.24)

Dividindo a Equação 3.24 por  $(V_1 . I_L)$ , temos:

$$\frac{P_1}{V_1 \cdot I_L} = 1 + \frac{\Delta V_1}{V_1}$$

(Eq 3.25)

Tomando a potência da carga ( $V_1$  .  $I_L$ ) como potência de base e utilizando a Equação 3.13, podemos obter:

$$P_1$$

(pu) =  $\frac{P_1}{V_1 \cdot I_{T_1}}$  = 1 + A (Eq 3.26)

Utilizando um raciocínio análogo, podemos obter a potência do transformador TR2 também em pu:

$$P_2 \text{ (pu)} = \frac{P_2}{V_1 \cdot I_L} = \frac{A}{(2 R_{max} - 1)} \cdot \left(1 + \frac{1 + A}{1 - A}\right)$$

(Eq 3.27)

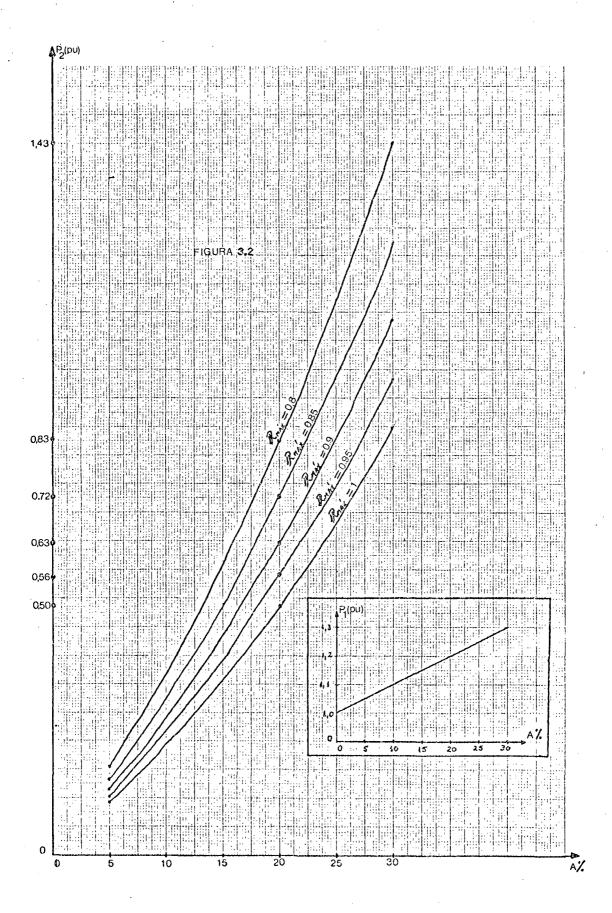

O ábaco da Figura 3.2, obtido a partir das Equações 3.26 e 3.27, permite a determinação da potência dos transformadores TR<sub>1</sub> e TR<sub>2</sub>, para uma determinada tolerância na tensão de entrada (A%) especificada no projeto do estabilizador.

## 3.7 - Exemplo de Cálculo

Neste îtem será feito o dimensionamento dos transformadores  $\text{TR}_1$  e  $\text{TR}_2$ , através do ábaco da Figura 3.2, para um protótipo com as seguintes características:

$V_{I_1}$  = Tensão eficaz na carga = 220 V.

$I_L$  = Corrente eficaz na carga = 5 A

A% = Variação percentual especificada para a tensão de entrada = 20%.

Figura 3.2

Dos valores especificados acima, obtemos a  $\,$  potê ${ ilde{ ext{p}}}$ cia da carga  $\,$  P $_{ ext{L}}$ :

$$P_{L} = V_{1} \cdot I_{L} = 220 \cdot 5 = 1100 \text{ W}$$

Do ábaco da Figura 3.2 tiramos a potência do tran<u>s</u> formador TR<sub>1</sub> em pu:

$$P_1$$

(pu) = 1,2

Assim a potência do transformador TR<sub>1</sub>, em Watts, é:

$$P_1 = P_1$$

(pu) .  $P_L = 1.2$  . 1100 = 1320 W.

Se supusermos, idealmente, uma razão cíclica  $\max\underline{i}$  ma igual a um, obtemos do ábaco da Figura 3.2 e potência do transformador  $\mathrm{TR}_2$  em pu:

$$P_2$$

(pu) = 0,500

Assim, a potência do transformador  $\ensuremath{\text{TR}}_2$  , em Watts, é:

$$P_2 = P_2$$

(pu)  $P_L = 0,500$  . 1100 = 550 W.

No caso de especificarmos (um caso real) como  $rac{a}$

zão cíclica máxima, por exemplo, 0,9, a potência de TR<sub>2</sub> em puvale:

$$P_2(pu) = 0,6250$$

Desta forma, a potência (em Watts) de  $TR_2$  assum<u>i</u> rá o valor:

$$P_2 = P_2(pu)$$

.  $P_L = 0,6250$  . 1100 = 687,5 W

Para a determinação das relações de  $\mbox{transformação}$  de  $\mbox{TR}_2$  , podemos utilizar o ábaco da Figura 3.1.

Para o caso ideal, onde a razão cíclica máxima  $v_{\underline{a}}$  le um, obtemos:

$$n_2 = 0,1667$$

$$n_3 = 0,25$$

Para um caso real, onde a razão cíclica máxima  $v_{\underline{a}}$  le 0,9 , obtemos:

$$n_2 = 0,2083$$

$$n_3 = 0,3125$$

No protótipo desenvolvido o transformador  $TR_2$  foi projetado para o caso ideal (razão cíclica máxima igual a um), ou seja, sua potência é de 550 W e suas relações de transformação são  $n_2$  = 0,1667 e  $n_3$  = 0,25.

Desta forma a tensão de carga é estabilizada em 220 V, no protótipo desenvolvido com razão cíclica máxima igual a 0,9 , para uma variação percentual máxima na tensão da rede me nor do que 20%.

## 3.8 - Conclusão

Neste Capitulo, determinamos expressões para o cálculo da potência dos transformadores TR, e TR2.

Estas expressões foram traduzidas em um ábaco, <u>pa</u>ra facilitar o dimensionamento dos transformadores, no projeto de um estabilizador.

#### CAPÍTULO 4

#### COMANDO DE BASE DOS TRANSISTORES

## 4.1 - Introdução

O circuito de comando de base, é de funtamental  $i\underline{m}$  portância num conversor a transistor de potência.

O desempenho do conversor, é influenciado direta mente pela qualidade do comando de base.

Um bom comando de base, pode ser resumido em qua tro regras [4]:

- 1ª) No disparo, apresentar uma subida na corrente de base tão rápida quanto possível; em geral aplica-se um pico inicial de corrente na base. Isto reduz o tempo de fechamento do transistor.

- 24) Durante a condução do transistor, adaptar a corrente de base à corrente de coletor. Isto evita que o transistor atinja a região de su per-saturação, onde se teria um tempo de estocagem muito grande.

- 3ª) No bloqueio, extrair uma corrente de base in versa limitando sua derivada em relação ao tem po. Esta prática acelera o tempo de bloqueio.

14) Durante o bloqueio, manter a tensão de base negativa em relação ao emissor. Isto protege o transistor contra disparos acidentais provocados por correntes parasitas e por dv/dt, além de permitir que o transistor suporte tensões (coletor-emissor) mais elevadas.

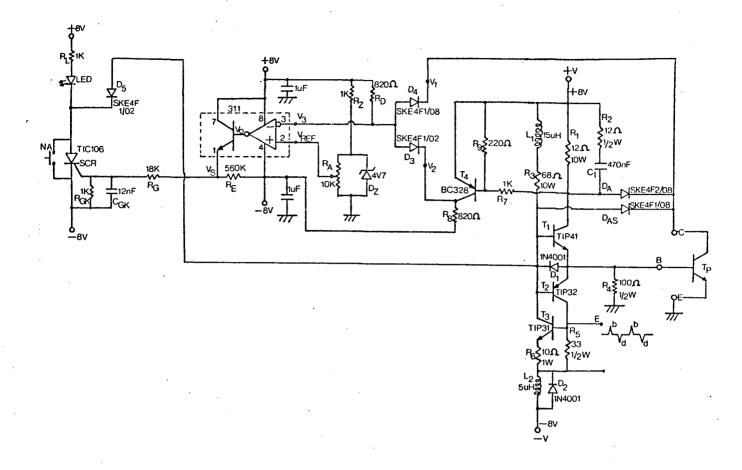

## 4.2 - Comando de Base dos Transistores

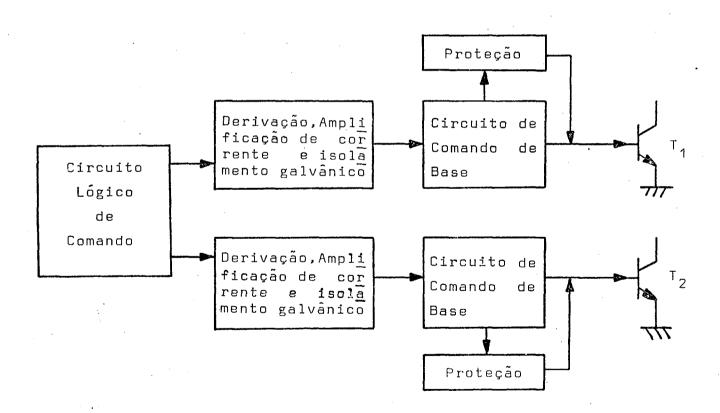

O comando de base dos transistores pode ser representado através do diagrama de blocos da Figura 4.1.

Figura 4.1 - Diagrama de Blocos do Comando de Base dos Transistores.

Mostraremos a seguir, o funcionamento de cada um dos blocos representados na Figura 4.1.

## 4.2.1 - Circuito Lógico de Comando

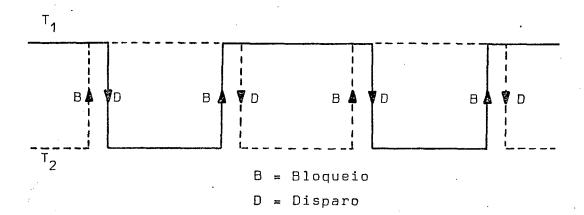

Os sinais de comando dos transistores  $T_1$  e  $T_2$  devem ser complementares e com um pequeno intervalo de tempo  $\Delta t$  entre o bloqueio de um e o disparo de outro, para se evitar a condução simultânea dos mesmos.

Este intervalo de tempo é necessário porque os transistores não são chaves ideais, ou seja, eles levam um cer to tempo para bloquear e para entrar em condução.

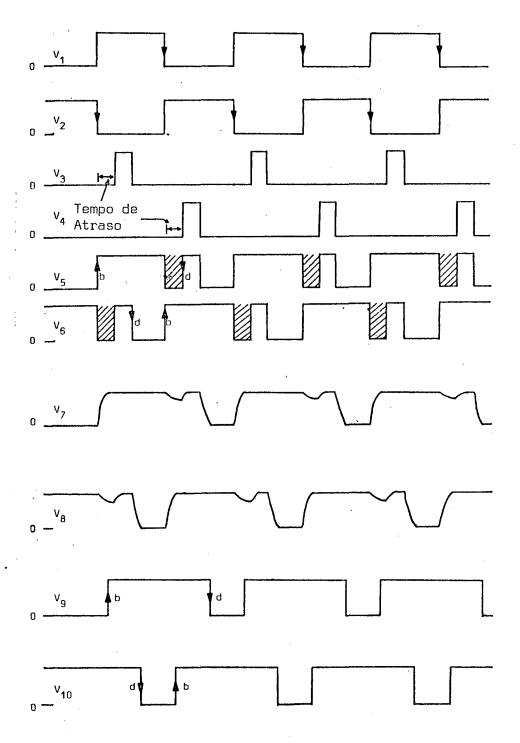

Como saída do circuito lógico de comando temos dois sinais, mostrados na Figura 4.2, que após tratados conveniente mente irão comandar os transistores de potência.

Figura 4.2 - Sinais de Saída do Circuito Lógico de Comando.

Além disso, é no circuito lógico de comando que se controla a razão cíclica, assim como a frequência de chaveamen to dos transistores.

A partir do CI 3524, que é um modulador e regula

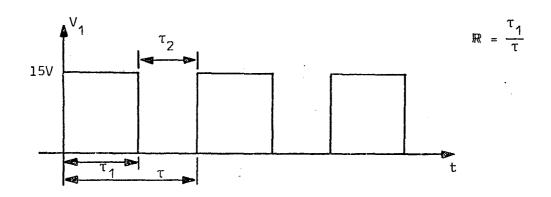

dor por largura de pulso, obtemos um sinal, conforme a Figura 4.3, cuja razão cíclica R pode ser variada através do controle da tensão no pino 2.

Figura 4.3 - Sinal de Saída do CI 3524 (pinos 12 e 13).

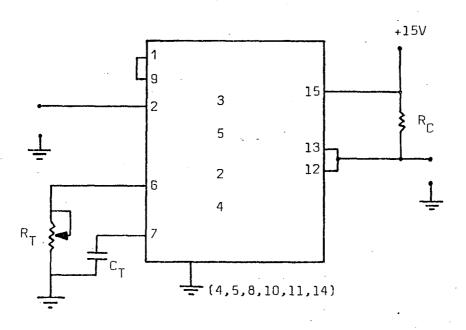

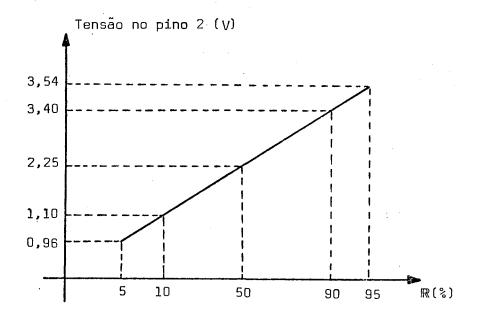

A Figura 4.4 mostra o diagrama de ligações do CI 3524 e a Figura 4.5 mostra a dependência entre a razão cíclica e a ten são no pino 2.

Figura 4.4 - Diagrama de Ligações do CI 3524.

Figura 4.5 - Tensão no Pino 2 x Razão Cíclica para o CI 3524.

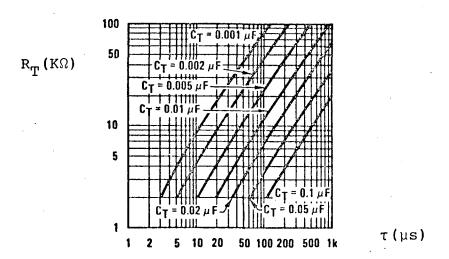

O período  $\tau$  do sinal da Figura 4.3 (e por consequência a sua frequência f) é determinado pelos valores do resistor R $_{T}$  e do capacitor C $_{T}$ . A Figura 4.6 mostra como determinar estes valores.

Figura 4.6 - Período  $\tau$  do Sinal da Figura 4.3 em Função de R $_{T}$  e C $_{T}$ .

O resistor  $R_{\text{C}}$  , indicado na Figura 4.4, limita a corrente da saída do CI 3524.

A alimentação do CI 3524, assim como de todo o circuito lógico, é feita a partir de uma fonte estabilizada de 15 Volts.

O sinal  $V_1$  de saída do CI 3524 é então tratado por um circuito que gera os sinais da Figura 4.2.

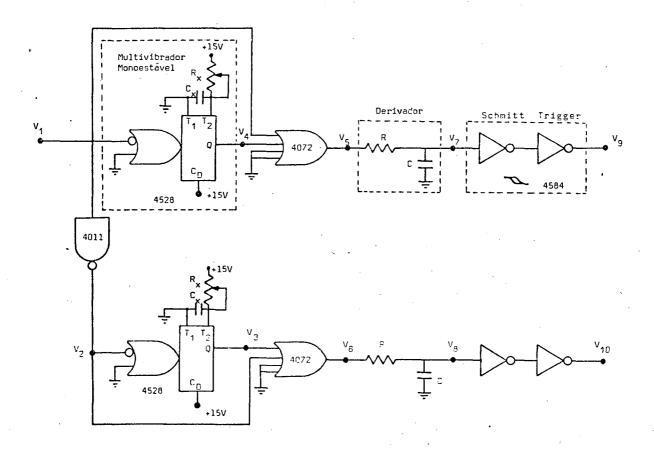

Este circuito é mostrado na Figura 4.7. Os vários sinais indicados no circuito da Figura 4.7 são mostrados na Figura 4.9.

Figura 4.7 - Circuito que Gera os Sinais da Figura 4.2.

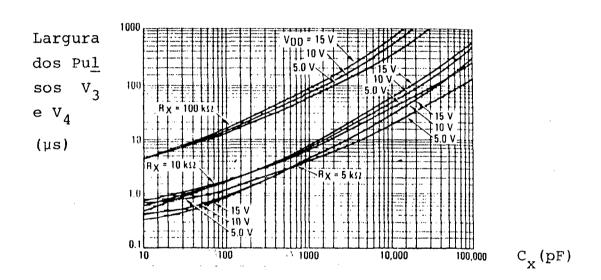

Os sinais  $V_1$  e  $V_2$  (sinal  $V_1$  invertido) são entrada de dois monoestáveis, sensíveis à descida, que fornecem pulsos,  $V_3$  e  $V_4$ , cuja largura é controlada pelos valores de  $R_{\rm x}$  e  $C_{\rm x}$ . A Figura 4.8 mostra como determinar a largura dos pulsos  $V_3$  e  $V_4$  (cuja largura corresponde ao pequeno intervalo de tempo  $\Delta t$  entre o bloqueio de um transistor e o disparo do outro, conforme item 4.2.1) em função de  $C_{\rm x}$  e  $R_{\rm x}$ .

Figura 4.8 - Largura dos Pulsos  $V_3$  e  $V_4$  em Função de  $R_x$  e  $C_x$ .

Na verdade, cada monoestável demora um certo tem po (inerente à sua circuitagem interna) para responder a um sinal de entrada. Isto gera um tempo de atraso que se reflete nos sinais  $V_5$  e  $V_6$ .

Para resolver este problema utilizamos circuitos derivadores cujas saídas são os sinais  $\rm V_7$  e  $\rm V_8$ .

A seguir os sinais  $V_7$  e  $V_8$  passarão por Schmitt Triggers onde serão quadrados e transformados nos sinais  $V_9$  e

V<sub>10</sub>.

Estes sinais serão a seguir derivados, amplifica dos em corrente e isolados galvanicamente.

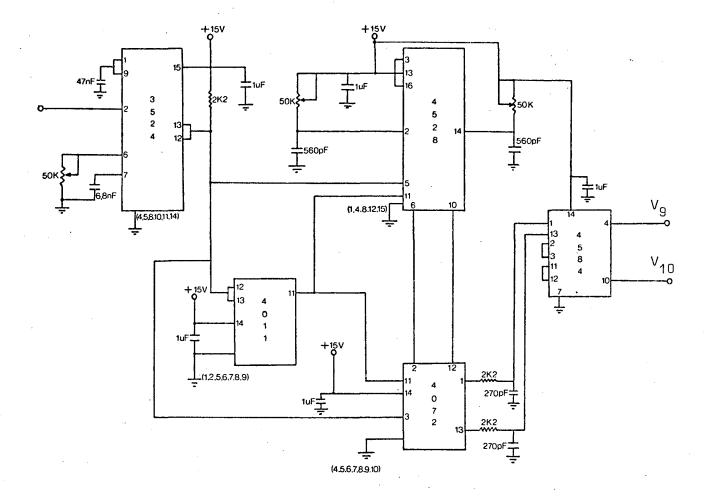

O circuito completo que gera os sinais  ${\rm V_9}$  e  ${\rm V_{10}}$  é aquele da Figura 4.10

Figura 4.9 - Sinais do Circuito da Figura 4.7.

Figura 4.10 - Circuito Lógico de Comando.

# 4.2.2 - Derivação, Amplificação e Isolamento

Os sinais  $v_9$  e  $v_{10}$  da Figura 4.9 são derivados, am plificados em corrente e isolados galvanicamente, uma vez que a massa dos dois transistores de potência são diferentes.

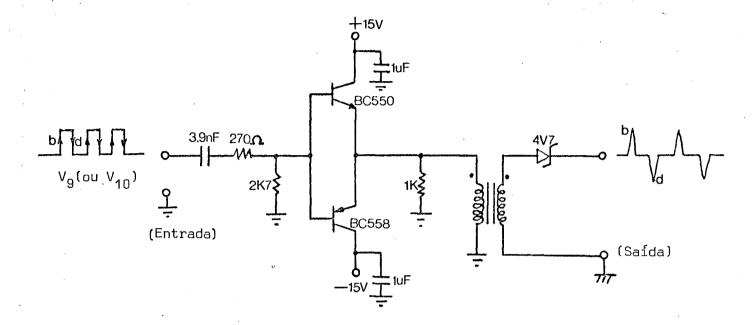

O circuito que desempenha esta função é o da Figura 4.11.

Figura 4.11 - Derivação, Amplificação e Isolamento.

O sinal de saída do circuito da Figura 4.11 atua no circuito de comando de base, que será descrito a seguir.

### 4.2.3 - Circuito de Comando de Base [4], [5]

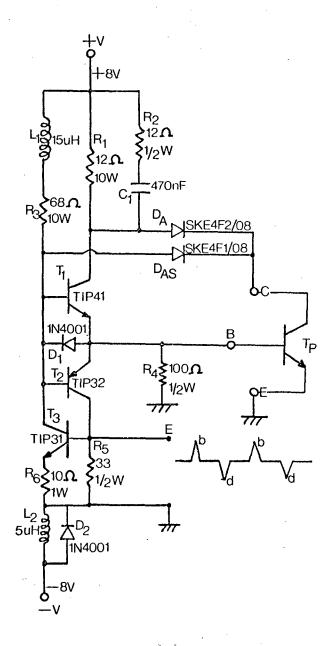

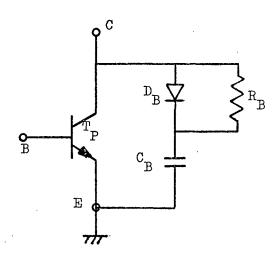

O circuito de comando de base, que é acionado pelo sinal de saída do circuito da Figura 4.11, atua diretamente nos transistores de potência. O circuito de comando de base é aquele mostrado na Figura 4.12.

Figura 4.12 - Circuito de Comando de Base.

O sinal de saída do circuito da Figura 4.11, atua na base do transistor  $T_3$  (Figura 4.12).

Um pulso positivo na base de  $\rm T_3$  faz com que T\_2 e  $\rm T_3$  conduzam, mantendo T\_p bloqueado e fixando sua base a um  $\rm po$  tencial negativo (-V).

Um pulso negativo na base de  $T_3$  bloqueia  $T_2$  e  $T_{3'}$  fazendo com que  $T_1$  injete uma corrente na base de  $T_p$  colocando-o em condução.

No circuito da Figura 4.12, a rede  $R_1$ ,  $R_2$ ,  $C_1$  é responsável pelo fornecimento do pico de corrente à base de  $T_p$  no momento do disparo. Os diodos  $D_A$  e  $D_{AS}$ , que são os diodos de antisaturação, garantem que os transistores  $T_1$  e  $T_p$  trabalhem na região de quase-saturação. O indutor  $L_2$  limita o gradiente de corrente de base inversa no momento do bloqueio de  $T_p$ .

### 4.2.4 - Proteção

Para proteger o transistor de potência contra de feitos que provoquem a sua desaturação, incorporamos ao circuito de comando de base, um circuito disjuntor que bloqueia o transistor de potência no momento do defeito, desta forma protegendo-o.

O circuito de proteção incorporado ao circuito de comando de base, está indicado na Figura 4.13.

O funcionamento do circuito da Figura 4.13 é dado a seguir.

$\hbox{Vamos supor que} \quad \hbox{$\mathbb{T}_p$} \quad \hbox{est\'a conduzindo.} \quad \hbox{$\mathbb{T}_1$ mant\'em} \quad \hbox{a}$   $\hbox{corrente de base de} \quad \hbox{$\mathbb{T}_p$} \quad \hbox{$\mathbb{T}_2$} \quad \hbox{e} \quad \hbox{$\mathbb{T}_3$} \quad \hbox{est\'ao bloqueados.}$

Um pulso positivo na entrada E, dispara  $T_2$  e  $T_3$  que desviam a corrente de base de  $T_1$  bloqueando-o e, por extensão, bloqueando  $T_p$ . A base de  $T_p$  é mantida a um potencial negativo (-V).

Figura 4.13 - Circuito de Proteção Incorporado ao Circuito de Comando de Base.

Um pulso negativo na entrada E, bloqueia  $T_2$  e  $T_3$ . A corrente que circula por  $L_1$  e  $R_3$  é injetada na base de  $T_1$ , fazendo com que ele conduza e, através da rede  $R_1$ ,  $R_2$ ,  $C_1$ , aplique um pico de corrente na base de  $T_p$  desta forma saturando-o.

Nestas condições,  $T_4$  conduz através de  $T_1$  e a tensão  $V_2$  é igual a +V. Assim,  $D_3$  está bloqueado e  $D_4$  está conduzindo através de  $T_p$ , fazendo com que  $V_3$  seja menor que  $V_{REF}$  ( $\approx 2.5V$ ) o que leva a saída do comparador de voltagem CI 311 a um valor  $V_S = -V_{SAT}$  (tensão de saturação do comparador).

Se acontecer, por exemplo, um curto-circuito na carga, a tensão coletor-emissor do transistor de potência ( $V_{\text{CE}_{ ext{TP}}}$ )

tende a subir. Quando  $V_{CE}_{TP}$  >  $V_{REF}$ , o comparador (CI 311) troca de estado e  $V_{S}$  = +  $V_{SAT}$ .

Nestas condições, um pulso positivo é enviado ao gate do SCR (TIC 106 D), fazendo com que ele conduza, extraindo corrente da base de  $T_{\rm p}$  através de D<sub>5</sub>, desta forma bloqueando-o. O LED acende indicando a condição de defeito. Por extensão  $T_{\rm 1}$  também bloqueia, bloqueando  $T_{\rm 4}$ . D<sub>3</sub> conduz por R<sub>8</sub> e V<sub>S</sub> = -V<sub>SAT</sub>.

Eliminado o defeito, bloqueamos o SCR através do fechamento do interruptor NA (normalmente aberto) que está em paralelo com ele.

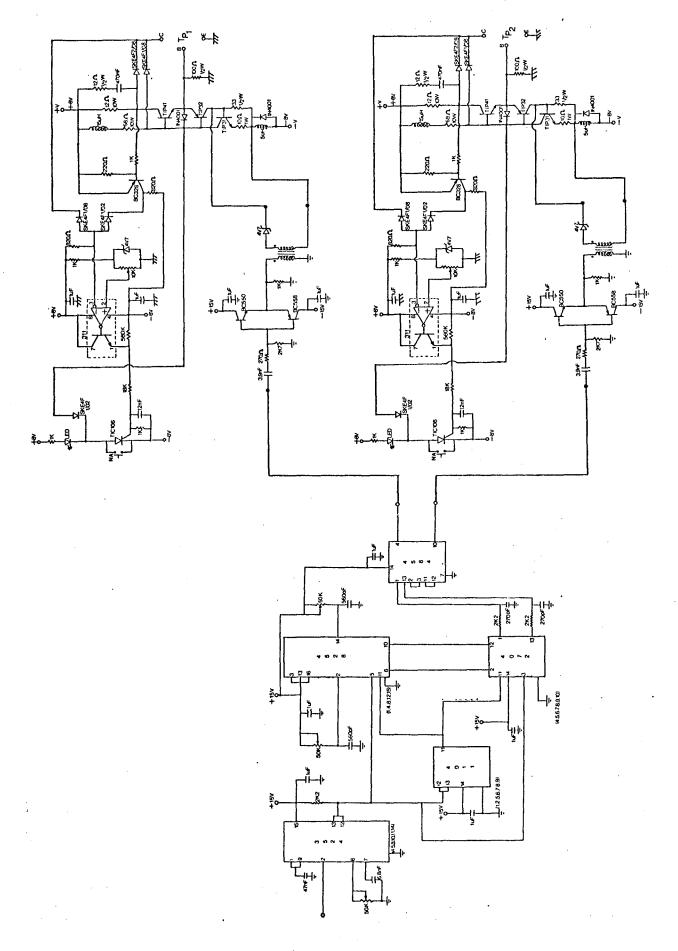

A Figura 4.14 mostra o circuito completo para controle dos transistores de potência.

Figura 4.14 - Circuito Completo de Controle dos Transistores de Potência.

## 4.3 - Conclusão

Neste Capítulo estabelecemos as regras fundamentais, para um bom comando de base de um transistor de potência.

Além disso, mostramos e descrevemos o funcioname $\underline{n}$  to do comando de base que utilizamos, no protótipo desenvolv $\underline{i}$  do em laboratório.

#### CAPÍTULO 5

### ESTUDO DA COMUTAÇÃO

### 5.1 - Introdução

Neste Capitulo, será feita a análise da comutação dos transistores do conversor proposto neste trabalho.

Serão incorporados à estrutura, circuitos de ajuda à comutação e circuitos grampeadores para facilitar a comutação dos transistores de potência.

Mostraremos as várias sequências de funcionamento da estrutura, e consideraremos a influência da não idealidade dos diodos.

### 5.2 - Circuito de Ajuda à Comutação

O circuito de ajuda à comutação (C.A.C.) é um circuito passivo composto por indutores, capacitores, resistores e diodos, capaz de armazenar, momentaneamente, energia. Possui a finalidade de diminuir as perdas do transistor de potência, du rante a comutação e de afastar, no plano  $I_{\rm C}({\rm V_{CE}})$ , a trajetória dos pontos de potências instantâneas elevadas.

## 5.2.1 - Circuito de Ajuda à Comutação no Bloqueio

O circuito de ajuda à comutação no bloqueio, tem a finalidade de retardar a subida da tensão  $V_{\rm CE}$  enquanto é cor

tada a corrente de coletor. A Figura 5.1 mostra o circuito de aju da à comutação no bloqueio associado a um transistor de potên cia.

Figura 5.1 - Circuito de Ajuda à Comutação no Bloqueio.

Quando o transistor inicia o bloqueio ocorre a transferência de sua corrente de coletor para o capacitor através do diodo  $D_B$ . A tensão no capacitor começa a aumentar até atingir o valor máximo  $V_{CE} = V_M$  quando então o diodo  $D_B$  bloqueia. Desta forma, a tensão nos terminais do transistor cresce menos rapidamente.

No momento em que o transistor for colocado em  ${\tt con}$  dução, o capacitor  ${\tt C}_{\tt B}$  se descarrega sobre ele através do resistor  ${\tt R}_{\tt B}.$

$\label{eq:components} \text{Com relação ao dimensionamento dos componentes} \quad \textbf{D}_{B}\text{,} \\ \textbf{R}_{B} \text{ e } \textbf{C}_{B}\text{, deve-se considerar:}$

10) O diodo  $D_{\overline{B}}$  deve ser rápido e capaz de suportar valores de corrente e tensão, compatíveis com os valores envolv $\underline{i}$

dos na estrutura.

2º) A tensão que aparece no Capacitor  $C_B$  e no proprio transistor  $T_p$ , quando está bloqueado, durante o funciona mento de estrutura, é o valor de pico  $V_M$ . Assim, quando o transistor entra em condução, o capacitor  $C_B$  se descarrega sobre ele provocando uma sobrecorrente  $\Delta I$  na sua corrente de coletor, dada por:

$$\Delta I = \frac{V_{M}}{R_{B}}$$

(Eq 5.1)

39) O tempo de descarga do capacitor  $C_B$  deve ser menor que o tempo mínimo  $(t_m)$  de condução do transistor. Assim, a dotando-se 3 constantes de tempo para a descarga do capacitor  $C_B$ , temos:

3 .

$$R_B$$

.  $C_B \le t_m$  (Eq 5.2)

Sendo  $\mathbf{R}_{\mathrm{m}}$  a razão cíclica mínima para o transistor e fasua frequência de chaveamento, podemos escrever:

3.

$$R_B.C_B \le \frac{R_m}{f}$$

(Eq 5.3)

ou

$$R_B \cdot C_B \leq \frac{R_m}{3f}$$

(Eq 5.4)

Do que foi exposto, concluímos que os valores de  ${\tt R}_{\tt B} \ {\tt e} \ {\tt C}_{\tt B} \ {\tt est\~ao} \ {\tt amarrados} \ {\tt um} \ {\tt ao} \ {\tt outro} \ {\tt e} \ {\tt seus} \ {\tt valores} \ {\tt s\~ao} \ {\tt dete}\underline{\tt r}$  minados através das especificações de  ${\tt R}_{\tt m} \ {\tt e} \ {\tt f}$  .

Normalmente se trabalha com as equações 5.1 e 5.4 de forma iterativa, no sentido de maximizar o valor do capacitor  $C_B$ , para que a tensão coletor-emissor seja a menor posivel, no momento em que a corrente de coletor do transistor se anula [4].

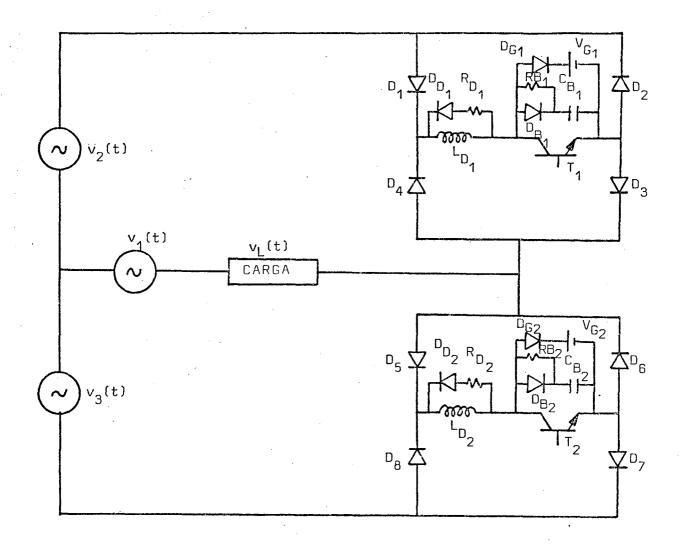

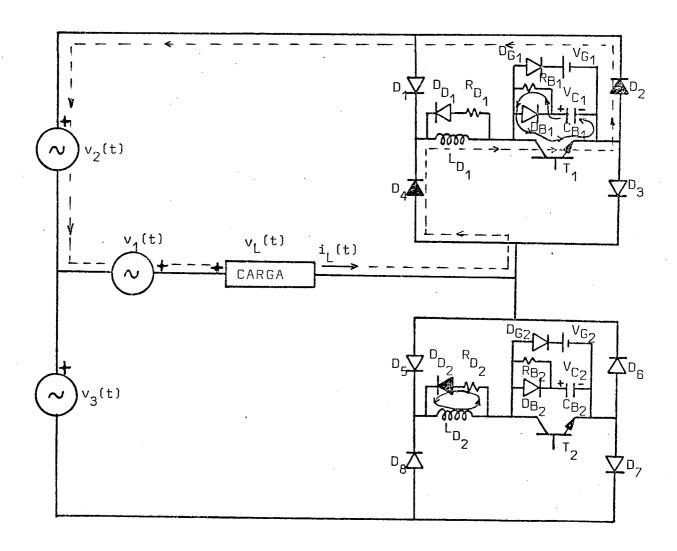

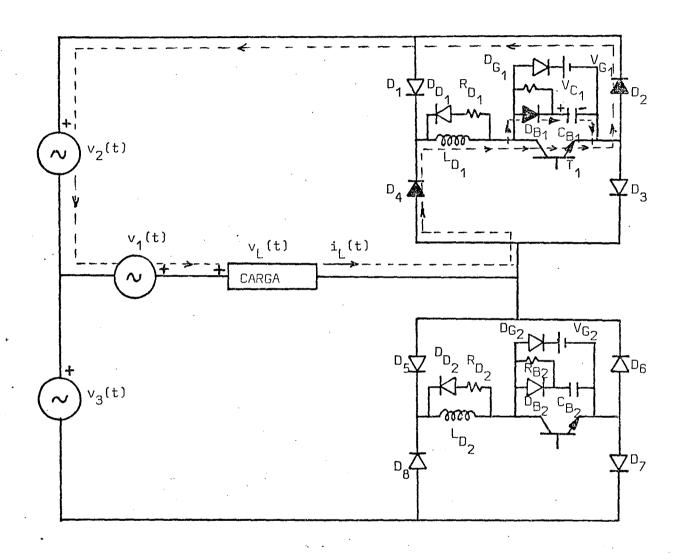

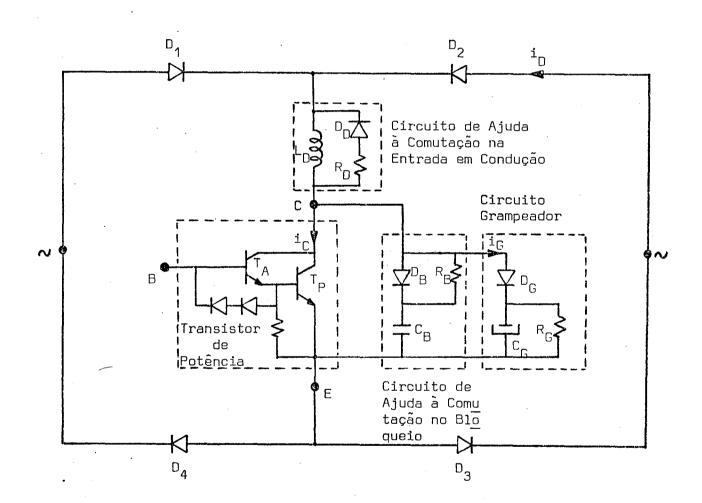

A Figura 5.2 mostra a estrutura da Figura 2.19, on de foi introduzido um C.A.C. no bloqueio para cada transistor.

Figura 5.2 - Circuito de Ajuda à Comutação no Bloqueio Incorporado ao Circuito da Figura 2.19.

Considere-se que, em um dado momento do funciona mento da estrutura da Figura 5.2, o transistor  $T_2$  está bloquea do, a tensão no capacitor  $C_{B_2}$  é menor do que  $(v_2(t)+v_3(t))$  e o transistor  $T_1$  foi colocado em condução. Nestas condições, o transistor  $T_1$  conduzirá, além de corrente de carga, um pico de corrente responsável pela carga do capacitor  $C_{B_2}$ . Este pico de corrente pode ser destrutivo para ele. Para evitar este proble ma, será introduzido no circuito da Figura 5.2 um circuito de a juda à comutação na entrada em condução do transistor, para limitar este pico de corrente.

## 5.2.2 - Circuito de Ajuda à Comutação na Entrada em Condução

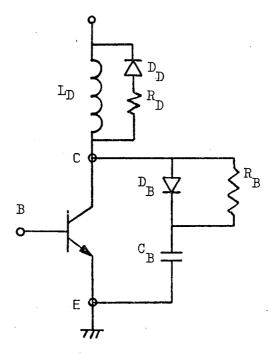

O circuito de ajuda à comutação na entrada em condução, incorporado ao circuito da Figura 5.1, é mostrado na Figura 5.3.

Figura 5.3 - Circuito de Ajuda à Comutação na Entrada em Condução Incorporado ao Circuito da Figura 5.1.

$\label{eq:components} \textbf{Com relação ao dimensionamento dos componentes} \quad \textbf{D}_{D}\text{,}$   $\textbf{L}_{D} \text{ e } \textbf{R}_{D}\text{, devemos considerar:}$

- 19) O diodo D<sub>D</sub> deve ser rápido, para que a sua corrente de recuperação, sobre o transistor, seja a menor possível.

- 29) Quanto maior o valor de  $L_D$ , menor o pico de corrente  $I_p$  e as perdas no transistor, conforme mostra a Equação 5.5,

$$I_{P} = (V_{2M} + V_{3M}) \cdot \sqrt{\frac{c_{B}}{L_{D}}}$$

(Eq. 5.5)

sendo  $V_{2M}$  e  $V_{3M}$  o valor de pico das tensões  $v_2(t)$  e  $v_3(t)$ , respectivamente, porém maior será o tempo de roda-livre na malha  $L_D$ ,  $D_D$ ,  $R_D$ , limitando a frequência de operação da estrutura.

3º) Quanto maior o valor de  $R_{\rm D}$ , maior será a sobretensão no transistor no bloqueio, porém menor será o tempo de descarga da energia armazenada em  $L_{\rm D}$ .

Com base nestas considerações, deve-se escolher de terminados valores para  $L_D$  e  $R_D$ , testá-los na estrutura e ajustar os seus valores de modo que se consiga um bom desempenho.

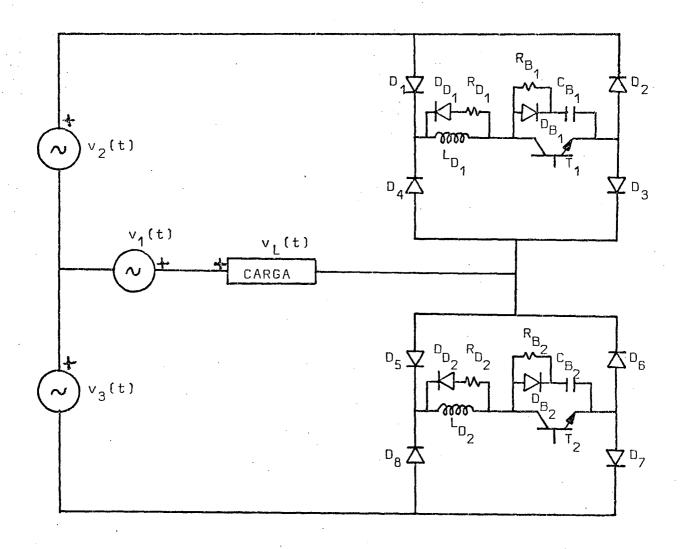

Com a introdução do circuito de ajuda à comutação na entrada em condução, o circuito da Figura 5.2 passa a ter o aspecto mostrado na Figura 5.4

Figura 5.4 - Circuito de Ajuda à Comutação no Bloqueio e na Entrada em Condução dos Transistores  $T_1$  e  $T_2$ .

# 5.3 - Circuito Grampeador

Consideremos que, na estrutura da Figura 5.4, o transistor  $\mathbf{T}_2$  está bloqueado e o transistor  $\mathbf{T}_1$  está conduzin do a corrente de carga. Ao ser dada a ordem de bloqueio para o transistor  $\mathbf{T}_1$ , sua corrente de coletor começa a decrescer ao ser transferida para o capacitor  $\mathbf{C}_{\mathbf{B}_1}$  através do diodo  $\mathbf{D}_{\mathbf{B}_1}$ . A corrente de carga  $\mathbf{I}_{\mathbf{L}}$  é considerada constante durante a comutação.

Durante o intervalo de tempo  $\Delta t$ , entre o bloqueio

do transistor  $T_1$  e a entrada em condução do transistor  $T_2$ , a tensão no capacitor  $C_{B_1}(V_{C_1})$  assume o valor dado pela Equação 5.6:

$$V_{C_1} = \frac{I_L \cdot \Delta t}{C_{B_1}}$$

(Eq 5.6)

e as tensões no circuito da Figura 5.4 vão evoluindo conforme indica a Figura 5.5, onde se está representando o pior caso para esta comutação na qual as tensões  $v_2(t)$  e  $v_3(t)$  passam pelos

Figura 5.5 - Comutação do Transistor  $T_1$ .

seus valores máximos  ${\rm V_{2M}}$  e  ${\rm V_{3M}}$  respectivamente, e a corrente de carga assume o seu valor de pico  ${\rm I_{T.}}$ .

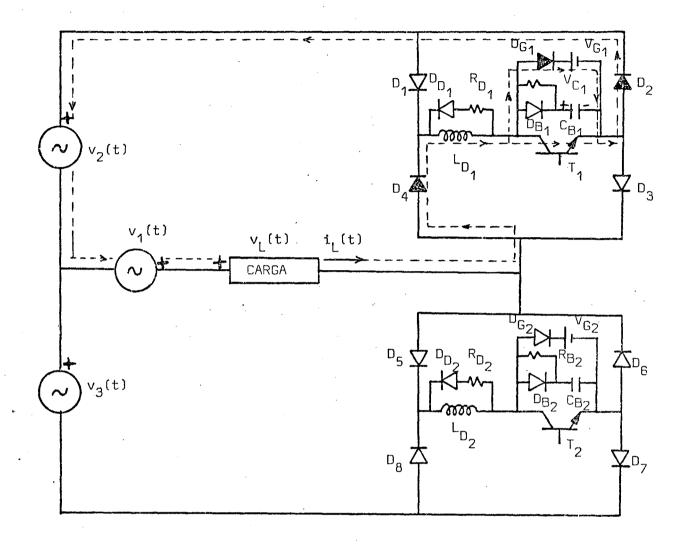

Como o capacitor  $C_{B_1}$  é da ordem de poucas dezenas de nanofarads e o tempo  $\Delta t$  da ordem de poucos microsegundos, con clui-se, a partir da Equação 5.6, que a tensão  $V_{C_1}$  pode assumir valores muito elevados. Para limitar esta tensão, utilizaremos circuitos grampeadores colocados em paralelo com o C.A.C. no bloqueio de cada transistor. O circuito grampeador está representado, de forma simplificada, na Figura 5.6.

Figura 5.6 - Circuito Grampeador.

Com a introdução dos circuitos grampeadores, o circuito da Figura 5.5 assume a forma mostrada na Figura 5.7.

Figura 5.7 - Introdução de Circuitos Grampeadores à Estrutura da Figura 5.5.

A seguir, faremos a análise das sequências de funcionamento para a estrutura da Figura 5.7.

# 5.4 - Sequências de Funcionamento

Considere-se que as tensões  $v_1(t)$  ,  $v_2(t)$  e  $v_3(t)$  estão passando pelo semi-ciclo positivo e que todos os diodos do circuito da Figura 5.7 são ideais.

Considere-se, ainda, como ponto de partida, o exa

to momento em que o transistor T, vai ser colocado em condução.

0 capacitor  $C_{B_1}$  está carregado com uma tensão  $V_{C_1}$  e o capacitor  $C_{B_2}$ , com uma tensão  $V_{C_2}$ .

Quando  $T_1$  entrar em condução, além de conduzir a corrente de carga, se dará a descarga do capacitor  $C_{B_1}$  sobre ele através de  $R_{B_1}$ . Esta sequência está representada na Figura 5.8. O transistor  $T_2$  encontra-se bloqueado.

Figura 5.8 - Sequência de Funcionamento:  $T_1$  entrando em Condução; Descarga de  $C_B$  sobre  $T_1$ ; Roda Livre na malha  $L_{D_2}$ ,  $R_{D_2}$ ,  $D_{D_2}$ .

Ocorre nesta sequência, durante um pequeno intervalo de tempo, a evacuação da energia armazenada no indutor  $L_{D_2}$ , atraves do circuito de roda-livre  $D_{D_2}$ ,  $R_{D_2}$ ,  $L_{D_2}$ .

O final desta sequência (Figura 5.9) se dá com o transistor  $T_1$  conduzindo a corrente de carga, quando já se extinguiram a roda livre na malha  $L_{D_2}$ ,  $R_{D_2}$  e  $D_{D_2}$  e a descarga do capacitor  $C_{B_1}$ .

Figura 5.9 - T<sub>1</sub> Conduzindo a corrente de Carga.

No momento em que o transistor  $T_1$  recebe um comando de bloqueio, a sua corrente de coletor passa a ser desviada para o circuito de ajuda à comutação, como mostra a Figura 5.10.

Figura 5.10 - T<sub>1</sub> Recebe Comando de Bloqueio.

Assim, a corrente de coletor de  $T_1$  vai diminuindo e a corrente de carga do capacitor  $C_{B_1}$  vai aumentando, fazendo com que a sua tensão  $V_{C_1}$  vá crescendo.

Caso a tensão  $V_{C_1}$  atinja o valor  $V_{G_1}$  o diodo  $D_{B_1}$  bloqueia e a corrente é desviada através de  $D_{G_1}$  e  $V_{G_1}$ . Assim a tensão  $V_{C_1}$  fica grampeada em  $V_{G_1}$ . Esta situação é mostrada na

Figura 5.11.

Figura 5.11 - Acionamento do Circuito Grampeador.

Nesta sequência, dependendo do valor da corrente de carga no momento da comutação, é possível que a tensão  $v_{\rm C1}$  não atinja o valor  $v_{\rm G1}$ . Desta forma o circuito grampeador não será acionado.

A partir do momento em que a corrente de coletor de  $T_1$  se anula pode-se colocar o transistor  $T_2$  em condução, a través do conveniente sinal de comando.

As sequências de funcionamento são rigorosamente simétricas em relação às que foram descritas, mudando apenas a ordem de grandeza de alguns parâmetros.

### 5.5 - <u>Influência</u> <u>da</u> <u>não</u> <u>Idealidade</u> <u>dos</u> <u>Diodos</u>

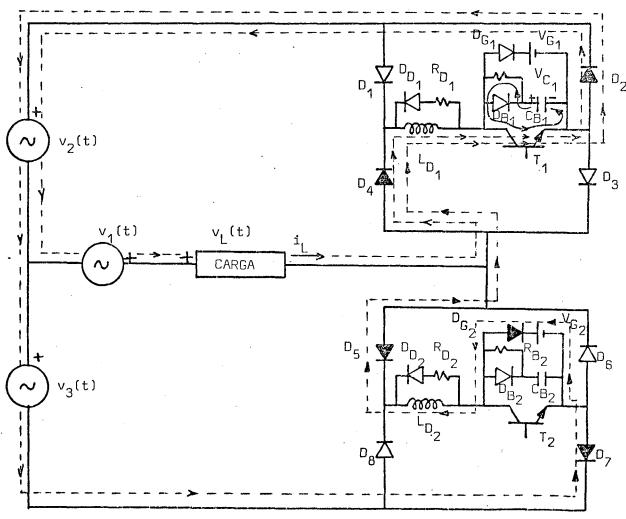

Considere-se que os diodos da estrutura da Fig $\underline{u}$ ra 5.7 não são ideais.

Seja a estrutura da Figura 5.8.

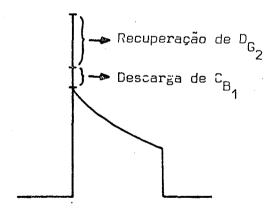

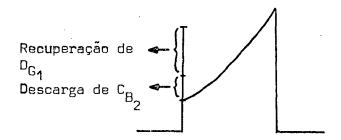

Além de descarga do capacitor  $C_{B_1}$  sobre o transistor  $T_1$  na sua entrada em condução, ocorre também a recuperação do diodo  $D_{G_2}$  (caso o circuito grampeador do qual ele faz parte tenha sido acionado na seqüência anterior). Este fato está ilustrado na Figura 5.12.

Figura 5.12 - Recuperação do Diodo  $D_{G_2}$  sobre o Transistor  $T_1$ .

Uma situação semelhante ocorre com o transistor  $T_2$ . Na sua entrada em condução, além da descarga de  $C_{B_2}$ , ocorre também a recuperação do diodo  $D_{G_1}$  (caso o circuito grampeador do qual ele faz parte tenha sido acionado na sequência anterior). A Figura 5.13 ilustra este fato.

Figura 5.13 - Recuperação do diodo  $D_{G_1}$  sobre o Transistor  $T_2$ .

O caso mais crítico ocorre com o transistor T<sub>1</sub>.

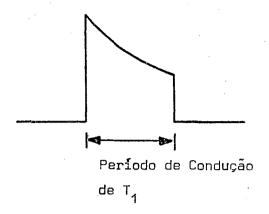

Durante o seu período de condução, a corrente de carga tem o aspecto mostrado na Figura 5.14.

Figura 5.14 - Corrente de Carga durante a Condução, de  $T_1$ .

Quando o transistor  $T_1$  entra em condução além de conduzir a corrente de carga, ocorre a descarga do capacitor  $C_{B_1}$  e a recuperação do diodo  $D_{G_2}$  sobre ele, ocasionando então um pico de corrente. A Figura 5.15 ilustra este fato.

Figura 5.15 - Pico de Corrente no Transistor  $T_1$  na sua Entrada em Condução.

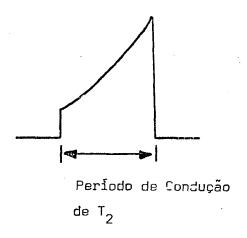

Para o transistor  $T_2$  a situação é menos crítica. Durante o seu período de condução, a corrente de carga tem o aspecto mostrado na Figura 5.16.

Figura 5.16 - Corrente de Carga durante a condução de T2.

Quando o transistor  $T_2$  entra em condução, ele conduz uma corrente de carga crescente. Nestas condições, a descar ga de  $C_{B_2}$  e a recuperação de  $D_{G_1}$  sobre ele ocorrem no instante em que a corrente de carga tem o seu menor valor. Isto que foi dito está ilustrado na Figura 5.17.

Figura 5.17 - Pico de Corrente no Transistor T<sub>2</sub> na sua E<u>n</u> trada em Condução.

Observa-se então a necessidade da utilização de diodos rápidos, para que os transistores (principalmente o transistor  $T_1$ ) não fiquem sobrecarregados comutando potências ele

vadas, reduzindo, portanto, a potência útil que se pode extrair do conversor.

### 5.6 - Conclusão

A partir do que foi apresentado neste Capítulo, constata-se a necessidade da utilização de circuitos de ajuda à comutação, para que o transistor de potência opere confortavel mente.

Constata-se, ainda, a importância da utilização de diodos rápidos na estrutura, com o objetivo de se reduzir a sua corrente de recuperação sobre os transistores de potência.

#### CAPÍTULO 6

### HARMÔNICAS E FILTRAGEM

#### 6.1 - Introdução

A finalidade do presente Capítulo, é determinar as características da forma de onda gerada pelo conversor, no que diz respeito ao seu conteúdo harmônico.

Utilizando-se uma frequência elevada para o chavea mento dos transistores, o conteúdo de harmônicas da tensão gera da pelo conversor é de alta frequência, dando assim a possibili dade de uma fácil filtragem das mesmas.

# 6.2 - Análise Harmônica da Tensão Gerada pelo Conversor

Considere-se a estrutura do conversor, mostrada de forma simplificada na Figura 6.1.

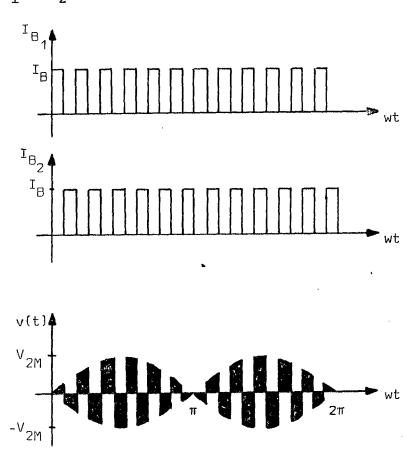

Figura 6.1 - Estrutura Simplificada do Conversor.

A tensão de carga  $v_L^{}(t)$ , é obtida a partir da fi $\underline{l}$  tragem da tensão  $v_F^{}(t)$  gerada pelo conversor.

Para que se possa dimensionar o filtro LC, é ne cessário que se conheça o conteúdo harmônico da tensão  $v_F(t)$ . Faremos então a sua decomposição em série de Fourier.

Da Figura 6.1 tiramos que:

$$v_{F}(t) = v_{1}(t) - v(t)$$

(Eq 6.1)

Como  $v_1(t)$  é a tensão da rede conclui-se, através da Equação 6.1, que a série de Fourier da tensão  $v_F(t)$  será conhecida a partir do momento que se conheça a série de Fourier da tensão v(t).

### 6.2.1 - Determinação da Série de Fourier da Tensão v(t)

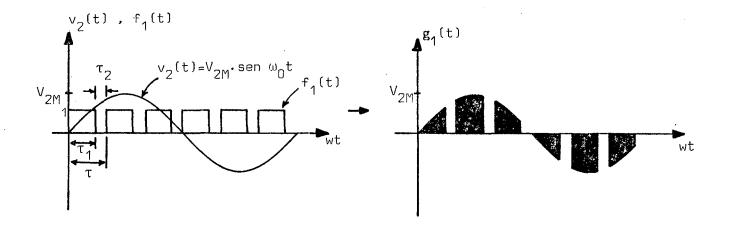

Considere-se a Figura 6.2 onde se mostra a obten ção da tensão v(t). Nesta Figura, tem-se:

$$f = \frac{1}{\tau} = \frac{\omega}{2\pi} = \text{frequência de chaveamento dos transistores}$$

(Eq 6.2)

$$\mathbf{R} = \frac{\tau_1}{\tau} = \text{razão cíclica}$$

(Eq 6.3)

$$f_0 = \frac{1}{T_0} = \frac{\omega_0}{2\pi} = \text{frequencia da rede (60 Hz)}$$

(Eq 6.4)

Figura 6.2.A - Multiplicando-se a Tensão  $\mathbf{v}_2(t)$  pelo Trem de Pulsos  $\mathbf{f}_1(t)$ , obtem-se  $\mathbf{g}_1(t)$ .

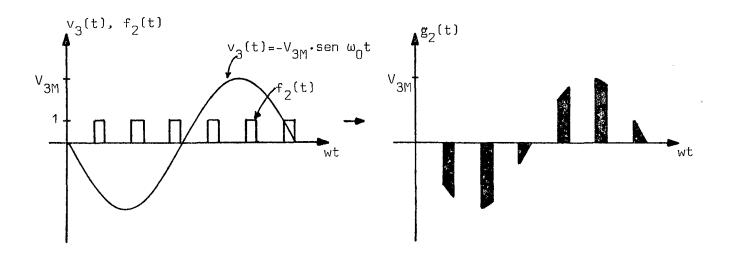

Figura 6.2.B - Multiplicando-se a Tensão  ${\bf v_3}(t)$  pelo Trem de Pulsos  ${\bf f_2}(t)$ , obtem-se  ${\bf g_2}(t)$ .

Figura 6.2.C - Somando-se  $g_1(t)$  com  $g_2(t)$ , obtem-se a Tensão v(t).

A determinação da série de Fourier da tensão v(t) será feita da seguinte forma:

- 19) Multiplicando-se  $v_2(t)$  pela série de Fourier de  $f_1(t)$ , obtém-se a série de Fourier de  $g_1(t)$ ;

- 29) Multiplicando-se  $v_3(t)$  pela série de Fourier de  $f_2(t)$ , obtém-se a série de Fourier de  $g_2(t)$ ;

- 3º) Somando-se a série de Fourier de g<sub>1</sub>(t) com a série de Fourier de g<sub>2</sub>(t) obtém-se a série de Fourier de v(t).

## <u>Série</u> <u>de</u> <u>Fourier</u> <u>de</u> f<sub>1</sub>(t)

Desenvolvendo a série de Fourier para f<sub>1</sub>(t), temse, como expressão geral:

$$f_1(t) = C_0 + \sum_{n=1}^{\infty} C_n$$

. sen  $(n\omega t + \phi_n)$  (Eq 6.5)

O coeficiente Co é dado por:

$$C_0 = \frac{1}{\tau} \cdot \int_0^{\tau_1} dt = \frac{1}{\tau} \cdot \tau_1 = R$$

(Eq 6.6)

O coeficiente C<sub>n</sub> é dado por:

$$C_n = \sqrt{a_n^2 + b_n^2}$$

(Eq. 6.7)

onde:

$$a_{n} = \frac{2}{\tau} \cdot \int_{0}^{\tau_{1}} \cos n\omega t \cdot dt = \frac{2}{n\omega\tau} \cdot \int_{0}^{\tau_{1}} \cos n\omega t \cdot dn\omega t = -1$$

$$= \frac{1}{n\pi} \cdot \operatorname{sen} \left( \frac{2n\pi\tau}{\tau} \right) = \frac{1}{n\pi} \cdot \operatorname{sen} (2n\pi \mathbb{R})$$

(Eq 6.8)

е

$$b_n = \frac{2}{\tau} \cdot \int_0^{\tau_1} \sin n\omega t \cdot dt = \frac{2}{n\omega\tau} \cdot \int_0^{\tau_1} \sin n\omega t \cdot dn\omega t =$$

$$\frac{1}{n\pi} \cdot (1 - \cos{(\frac{2n\pi\tau_1}{\tau})}) = \frac{1}{n\pi} \cdot (1 - \cos{(2n\pi\mathbb{R})}). \text{ (Eq 6.9)}$$

A partir das Equações 6.7, 6.8 e 6.9, obtém-se:

$$C_n = \frac{1}{n\pi} \cdot \sqrt{2 - 2 \cos (2\pi n \,\mathbb{R})}$$

(Eq 6.10)

O ângulo de fase  $\phi_n$  da Equação 6.5 é dado por:

$$\phi_n = \operatorname{arctg}\left(\frac{a_n}{b_n}\right)$$

(Eq 6.11)

Assim, a série de Fourier de f<sub>1</sub>(t) fica dada por:

$$f_1(t) = \mathbb{R} + \sum_{n=1}^{\infty} \frac{1}{\pi n} \cdot \sqrt{2 - 2 \cos(2\pi n \mathbb{R})} \cdot \operatorname{sen}(n\omega t + \phi_n)$$

(Eq 6.12)

## <u>Série</u> <u>de</u> <u>Fourier</u> <u>de</u> g<sub>1</sub>(t)

A tensão  $v_2(t)$  é dada por:

$$v_2(t) = V_{2M} \cdot \text{sen } \omega_0 t$$

(Eq 6.13)

Multiplicando-se as equações 6.12 e 6.13, obtemse:

$$\mathbf{g_1(t)} = \mathbf{V_{2M}}.\mathrm{sen}\ \omega_0 \mathbf{t} \cdot \mathbf{R} + \sum_{n=1}^{\infty}\ \mathbf{V_{2M}} \cdot \mathbf{C_n} \cdot \mathrm{sen}\ \omega_0 \mathbf{t} \cdot \mathrm{sen}\ (\mathrm{n}\omega \mathbf{t} + \phi_n)$$

(Eq. 6.14)

Da trigonometria, tem-se que:

sen A . sen B =

$$\frac{1}{2}$$

. (cos(A-B) - cos(A+B)) (Eq 6.15)

Assim, a série de Fourier de g<sub>1</sub>(t) fica dada por:

$$g_1(t) = V_{2M}.sen \omega_0 t.R + \sum_{n=1}^{\infty} \frac{V_{2M} \cdot C_n}{2} [cos [(\omega_0 - n\omega)t - \phi_n] -$$

$$-\cos [(\omega_0 + n\omega)t + \phi_n]]$$

(Eq 6.16)

# <u>Série</u> <u>de</u> <u>Fourier</u> <u>de</u> f<sub>2</sub>(t)

Desenvolvendo a série de Fourier para  $f_2(t)$ , temse, como expressão geral:

$$f_2(t) = C_0 + \sum_{n=1}^{\infty} C_n \cdot \text{sen (nwt + } \phi_n)$$

(Eq 6.17)

O coeficiente  $C_0$  é dado por:

$$C_0 = \frac{1}{\tau} \cdot \int_{\tau_1}^{\tau} dt = \frac{1}{\tau} \cdot (\tau - \tau_1) = 1 - \frac{\tau_1}{\tau} = (1 - \mathbf{R})$$

(Eq. 6.18)

Os coeficientes  $a_n$  e  $b_n$  da Equação 6.7 são da dos por: