# UNIVERSIDADE FEDERAL DE SANTA CATARINA DEPARTAMENTO DE INFORMÁTICA E ESTATÍSTICA GRADUAÇÃO EM CIÊNCIAS DA COMPUTAÇÃO

Rafael Neves de Mello Oliveira

Analysis of Radiation Effects in Full Adder Circuits at 7nm FinFET Technology

Florianópolis 2024 Rafael Neves de Mello Oliveira

Analysis of Radiation Effects in Full Adder Circuits at 7nm FinFET Technology

Trabalho de Conclusão de Curso apresentado à Universidade Federal de Santa Catarina – UFSC como requisito parcial para obtenção do título de bacharel em Ciências da Computação. Supervisor: Profa. Cristina Meinhardt, Drs. Co-supervisor: Prof. Rafael Budim Schvittz, Dr. Ficha catalográfica gerada por meio de sistema automatizado gerenciado pela BU/UFSC. Dados inseridos pelo próprio autor.

> Neves de Mello Oliveira, Rafael Analysis of Radiation Effects in Full Adder Circuits at 7nm FinFET Technology / Rafael Neves de Mello Oliveira ; orientadora, Cristina Meinhardt, coorientador, Rafael Budim Schvittz, 2024. 87 p.

Trabalho de Conclusão de Curso (graduação) -Universidade Federal de Santa Catarina, Centro Tecnológico, Graduação em Ciências da Computação, Florianópolis, 2024.

Inclui referências.

1. Ciências da Computação. 2. Microeletrônica. 3. Mitigação de falhas. 4. Single Event Transient. 5. FinFET. I. Meinhardt, Cristina. II. Budim Schvittz, Rafael. III. Universidade Federal de Santa Catarina. Graduação em Ciências da Computação. IV. Título. Rafael Neves de Mello Oliveira

## Analysis of Radiation Effects in Full Adder Circuits at 7nm FinFET Technology

O presente trabalho em nível de [graduação] foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof<sup>a</sup> Cristina Meinhardt, Dra. Universidade Federal de Santa Catarina

Prof. Rafael Budim Schvittz, Dr. Universidade Federal de Rio Grande

Alexandra Lackmann Zimpeck, Dra. Cadence Design Systems, Inc.

Deni Germano Alves Neto, Me. Universidade Federal de Santa Catarina

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de Ciência da Computação.

Coordenação do Curso de Graduação em Ciências da Computação

> Prof<sup>a</sup> Cristina Meinhardt, Dra. Orientadora

> > Florianópolis, 2024.

## ABSTRACT

The development of new technologies and new manufacturing processes in the semiconductor industry lead to the integration of billions of transistors into a single chip. This massive integration contributes to the reduction in operating voltage, power consumption, area, and costs of integrated circuits. However, the lower voltage operation and the low capacitance of the nanometer devices contributes to make them more susceptible to be affected by environment noises. This issue renders robustness a relevant aspect to be considered on the design of integrated circuits on advanced technologies nodes. Single Event Transient (SET) are non-destructive errors due to the interaction of environment energetic particles with silicon. A SET can temporarily change the correct value on combinational cells, compromising the expected behavior of the output values and, consequently, the proper functioning of the entire system. Because Full Adder (FA) is one of the primary cells of the Arithmetic and Logic Unit (ALU), and one of the most crucial component on computer systems, mitigating SET effects on them can improve more complex systems robustness. SET mitigation techniques can be adopted in different stages during the integrated circuit design flow. At the circuit level, the most explored techniques found in the literature are the use of Schmitt Triggers (ST), Decoupling Cells (DCELL), Transistor Sizing (TS), and Transistor Reordering. The goal of this work is to evaluate the radiation sensitivity in internal nodes of four full adder topologies. Additionally, the study aims to investigate the impact of using DCELL, TS, and combining these two techniques on SET effects for nominal (NV) and near-threshold voltage operation (NTV). The results show that the critical nodes and critical vectors can vary depending on the voltage operation and mitigation technique applied, mainly because they can influence the sensitivity of the circuit. However, TS can decrease the sensitivity of the output nodes, especially at nominal operation, for all topologies evaluated, while DCELL presented better improvements at NTV operation. Furthermore, at NTV operation, the mitigation techniques have side effects increasing the sensitivity of the internal critical nodes, despite the decrease in the total error occurrence. The adoption of mitigation techniques can reduce up to 60% the total error occurrence at nominal voltage, depending on the topology, and more than 35% at NTV in the circuits investigated. Moreover, the Hybrid topology presented, on average, 2% fewer errors than the Mirror at nominal voltage and 5% more errors than the Mirror for NTV. Among the PTL topologies at nominal voltage TFA presented 12% less errors than the TGA and up to 11% at NTV. Due to the relevance of FAs to digital designs, this set of information about the chosen FA topologies can assist designers to decide which circuit and mitigation technique are the most suitable for different requirements. Moreover, this work also maps all the internal nodes showing the critical parts for the circuits.

**Keywords**: Microelectronics. Circuit-level Design. Reliability. Single Event Transient. Mitigation. FinFET.

#### RESUMO

O desenvolvimento de novas tecnologias e processos de fabricação na indústria de semicondutores levou à integração de bilhões de transistores em um único chip. Essa integração maciça contribui para a redução da tensão de operação, consumo de energia, área e custos dos circuitos integrados. No entanto, a operação em baixa tensão e a baixa capacitância dos dispositivos nanométricos contribuem para serem mais suscetíveis e afetados por ruídos externos. Esse problema torna a robustez um aspecto relevante a ser considerado no projeto de circuitos integrados em nós de tecnologia avançada. Single Event Transient (SET) são erros não destrutivos devido à interação de partículas energéticas do ambiente com o silício. Um SET pode temporariamente alterar o valor correto em células combinacionais, comprometendo o comportamento esperado dos valores de saída e, conseguentemente, o funcionamento adeguado de todo o sistema. Como o Somador Completo (FA) é uma das células principais da Unidade Aritmética e Lógica (ULA) e um dos componentes mais cruciais em sistemas de computadores, a mitigação dos efeitos do SET neles pode aprimorar a robustez de sistemas mais complexos. Técnicas de mitigação do SET podem ser adotadas em diferentes estágios durante o fluxo de design de circuitos integrados. No nível do circuito, as técnicas mais exploradas encontradas na literatura são o uso de Schmitt Triggers (ST), Decoupling Cells (DCELL), Transistor Sizing (TS) e Transistor Reordering. O objetivo deste trabalho é avaliar a sensibilidade à radiação em nós internos de guatro topologias de somadores completos. Além disso, o estudo visa investigar o impacto do uso de DCELL, TS e a combinação dessas duas técnicas nos efeitos do SET para operação de tensão nominal (NV) e operação de tensão próxima ao limiar (NTV). Os resultados mostram que os nós e vetores críticos podem variar dependendo da operação de tensão e da técnica de mitigação aplicada, principalmente porque elas podem influenciar a sensibilidade do circuito. No entanto, TS pode diminuir a sensibilidade dos nós de saída, especialmente na operação nominal, para todas as topologias avaliadas. enquanto DCELL apresentou melhorias mais significativas na operação NTV. Além disso, na operação NTV, as técnicas de mitigação têm efeitos colaterais aumentando a sensibilidade dos nós críticos internos, apesar da diminuição na ocorrência total de erros. A adoção de técnicas de mitigação pode reduzir até 60% a ocorrência total de erros na tensão nominal, dependendo da topologia, e mais de 35% em NTV nos circuitos investigados. Além disso, a topologia Híbrida apresentou, em média, 2% menos erros do que a Mirror na tensão nominal e 5% mais erros do que a Mirror em NTV. Entre as topologias PTL na tensão nominal, a TFA apresentou 12% menos erros do que a TGA e até 11% menos em NTV. Devido à relevância dos FAs para designs digitais, esse conjunto de informações sobre as topologias de FA escolhidas pode auxiliar os projetistas a decidir qual circuito FA e técnica de mitigação são mais adequados para diferentes requisitos. Além disso, este trabalho também mapeia todos os nós internos, mostrando as partes críticas dos circuitos.

**Palavras-chave**: Microeletrônica. Design de Circuitos Integrados. Confiabilidade. Single Event Transient. Mitigação. FinFET.

## LIST OF FIGURES

| Figure 1 – Types of FinFET Technology.                              | 17 |

|---------------------------------------------------------------------|----|

| Figure 2 – Full Adders topologies                                   | 19 |

| Figure 3 – Effects of radiation on a PN junction.                   | 21 |

| Figure 4 – Classification of Single Event Effects.                  | 22 |

| Figure 5 – Decoupling Cell.                                         | 24 |

| Figure 6 – Transitor Sizing.                                        | 25 |

| Figure 7 – Workflow.                                                | 28 |

| Figure 8 – Test environment for simulations.                        | 30 |

| Figure 9 – Charge collection mechanism.                             | 31 |

| Figure 10 – SET waveform example                                    | 32 |

| Figure 11 – Mirror Full Adder critical nodes at nominal voltage     | 42 |

| Figure 12 – Hybrid Full Adder critical nodes at nominal voltage     | 43 |

| Figure 13 – TGA Full Adder critical nodes at nominal voltage        | 44 |

| Figure 14 – TFA Full Adder critical nodes at nominal voltage        | 44 |

| Figure 15 – Mirror Full Adder critical nodes at NTV                 | 50 |

| Figure 16 – Hybrid Full Adder critical nodes at NTV.                | 51 |

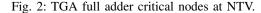

| Figure 17 – TGA Full Adder critical nodes at NTV.                   | 52 |

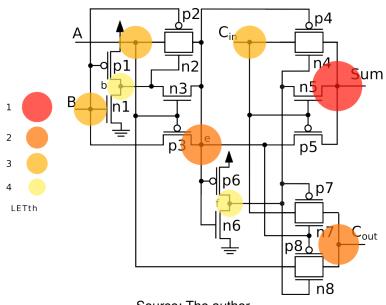

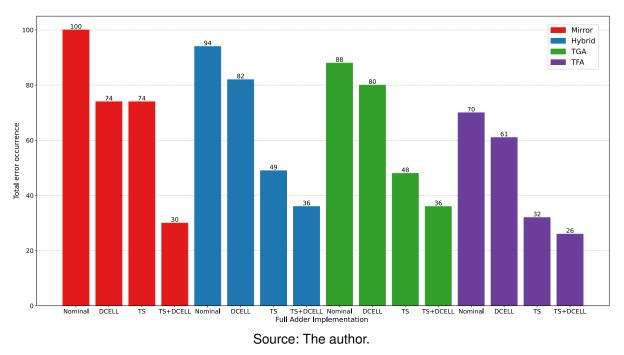

| Figure 18 – TFA Full Adder critical nodes at NTV                    | 52 |

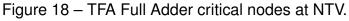

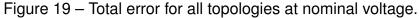

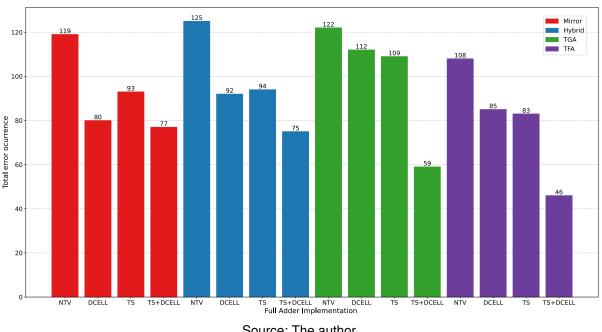

| Figure 19 – Total error for all topologies at nominal voltage       | 58 |

| Figure 20 – Total error for all topologies at NTV                   | 59 |

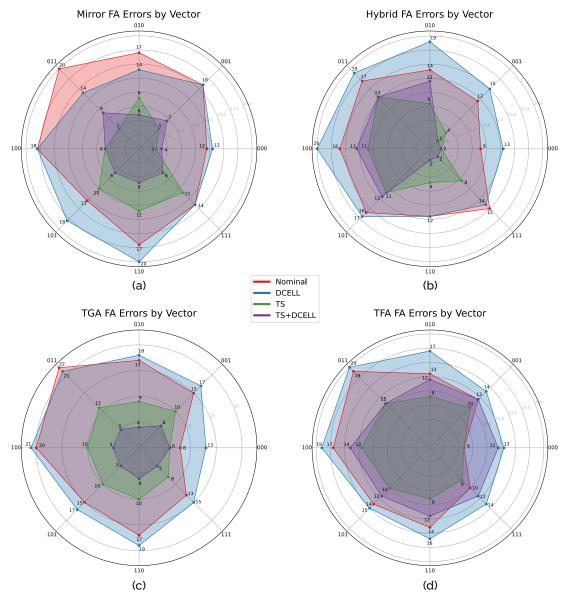

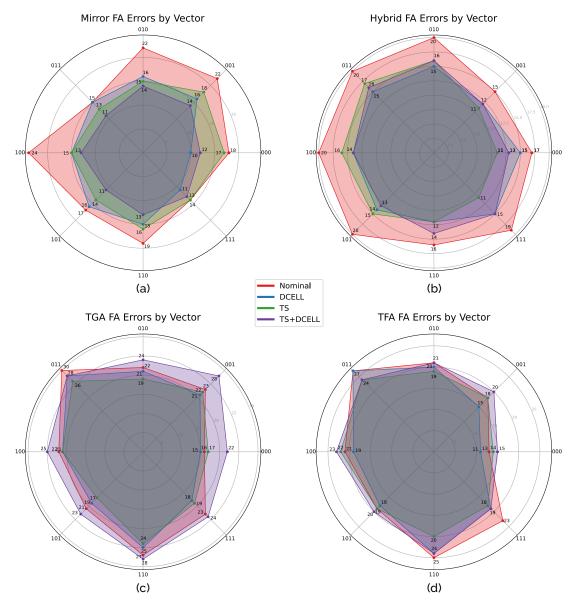

| Figure 21 – Error by Input Vectors at Nominal Voltage               | 61 |

| Figure 22 – Error by Input Vectors at NTV                           | 62 |

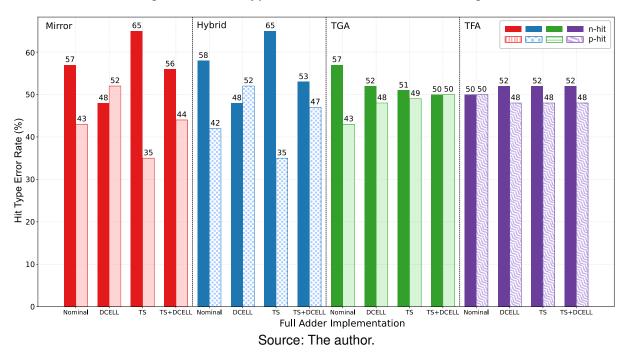

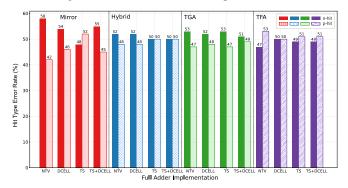

| Figure 23 – Hit type Error Rate at Nominal Voltage                  | 63 |

| Figure 24 – Hit type Error Rate at NTV.                             | 64 |

| Figure 25 – LETth Normalized by Mirror FA at Nominal Implementation | 65 |

|                                                                     |    |

## LIST OF TABLES

| Table 1 – Truth table for Full Adder.                                                             | 18 |

|---------------------------------------------------------------------------------------------------|----|

| Table 2 – Related work summary.                                                                   | 27 |

| Table 3 – LETth for all nodes of Mirror FA at Nominal Voltage ( $MeVcm^2/mg$ ).                   | 35 |

| Table 4 – LETth for all nodes of Hybrid FA considering worst fault propagation                    |    |

| at Nominal Voltage( <i>MeVcm<sup>2</sup>/mg</i> )                                                 | 36 |

| Table 5 – LETth for all nodes of TGA FA considering worst fault propagation at                    |    |

| Nominal voltage ( <i>MeVcm<sup>2</sup>/mg</i> )                                                   | 37 |

| Table 6 – LETth for all nodes of TFA FA considering worst fault propagation at                    |    |

| Nominal voltage ( <i>MeVcm<sup>2</sup>/mg</i> )                                                   | 38 |

| Table 7 – Error rate analysis for each FA topology                                                | 38 |

| Table 8 – Input vector sensitivity analysis for each FA topology                                  | 40 |

| Table 9 – Hit type percentage for each FA topology.                                               | 41 |

| Table 10 – Critical Nodes for Each FA Topology Based on Lowest LETth Values .                     | 45 |

| Table 11 – LETth for all nodes of Mirror FA considering worst fault propagation at                |    |

| NTV ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                              | 47 |

| Table 12 – LETth for all nodes of Hybrid FA considering worst fault propagation                   |    |

| at NTV ( <i>MeVcm<sup>2</sup>/mg</i> )                                                            | 47 |

| Table 13 – LETth for all nodes of TGA FA considering worst fault propagation at                   |    |

| NTV ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                              | 48 |

| Table 14 – LETth for all nodes of TFA FA considering worst fault propagation at                   |    |

| NTV ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                              | 49 |

| Table 15 – Comparison of sensitive nodes, critical nodes, critical input vectors,                 |    |

| and critical hit types for each FA topology under nominal and NTV                                 |    |

| operations                                                                                        | 56 |

| Table 16 – Summary of mitigation scenarios for nominal and NTV operations                         | 57 |

| Table 17 – LETth for all nodes of Mirror FA considering worst fault propagation at                |    |

| Nominal voltage ( <i>MeVcm<sup>2</sup>/mg</i> )                                                   | 79 |

| Table 18 – Total error for input vectors of Mirror FA at Nominal voltage ( $MeVcm^2/mg$ ).        |    |

|                                                                                                   | 79 |

| Table 19 – LETth for all nodes of Hybrid FA considering worst fault propagation                   |    |

| at Nominal voltage ( <i>MeVcm<sup>2</sup>/mg</i> ).                                               | 80 |

| Table 20 – Total error for input vectors of Hybrid FA at Nominal voltage (MeVcm <sup>2</sup> /mg) |    |

|                                                                                                   | 80 |

| Table 21 – LETth for all nodes of TGA FA considering worst fault propagation at                   |    |

| Nominal voltage ( <i>MeVcm<sup>2</sup>/mg</i> )                                                   | 81 |

| Table 22 – Total error for input vectors of TGA FA at Nominal voltage ( $MeVcm^2/mg$ ).           |    |

|                                                                                                   | 81 |

| Table 23 – LETth for all nodes of TFA FA considering worst fault propagation at                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Nominal voltage ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                    | 82 |

| Table 24 – Total error for input vectors of TFA FA at Nominal voltage ( $MeVcm^2/mg$ ).             |    |

|                                                                                                     | 82 |

| Table 25 – LETth for all nodes of Mirror FA considering worst fault propagation at                  |    |

| NTV ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                                | 83 |

| Table 26 – Total error for input vectors of Mirror FA at NTV ( $MeVcm^2/mg$ )                       | 83 |

| Table 27 – LETth for all nodes of Hybrid FA considering worst fault propagation                     |    |

| at NTV ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                             | 84 |

| Table 28 – Total error for input vectors of Hybrid FA at NTV ( <i>MeVcm<sup>2</sup>/mg</i> )        | 84 |

| Table 29 – LETth for all nodes of TGA FA considering worst fault propagation at                     |    |

| NTV ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                                | 85 |

| Table 30 – Total error for input vectors of TGA FA at NTV ( <i>MeVcm<sup>2</sup>/mg</i> )           | 85 |

| Table 31 – LETth for all nodes of TFA FA considering worst fault propagation at                     |    |

| NTV ( <i>MeVcm<sup>2</sup>/mg</i> ).                                                                | 86 |

| Table 32 – Total error for input vectors of TFA FA at NTV ( <i>MeVcm</i> <sup>2</sup> / <i>mg</i> ) | 86 |

## LIST OF ABBREVIATIONS AND ACRONYMS

| ALU    | Arithmetic and Logic Unit                           |

|--------|-----------------------------------------------------|

| ASAP7  | 7 nm Predictive Process Design Kit                  |

| CMOS   | Complementary Metal-Oxide-Semiconductor             |

| DCELL  | Decoupling Cell                                     |

| FA     | Full Adder                                          |

| FinFET | Fin Field-Effect Transistor                         |

| IC     | Integrated Circuit                                  |

| LET    | Linear Energy Transfer                              |

| LETth  | Linear Energy Transfer Threshold                    |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| MSB    | Most Significant Bit                                |

| NTV    | Near-threshold Voltage                              |

| NV     | Nominal Voltage                                     |

| PTM    | Predictive Technology Model                         |

| RHBD   | Radiation-Hardening by Design                       |

| RVT    | Regular Voltage Technology                          |

| SBU    | Single Bit Upset                                    |

| SE     | Soft Error                                          |

| SEE    | Single Event Effect                                 |

| SEFI   | Single Event Functional Interrupt                   |

| SET    | Single Event Transient                              |

| SEU    | Single Event Upset                                  |

| SOI    | Silicon-On-Insulator                                |

| SPICE  | Simulation Program with Integrated Circuit Emphasis |

| TFA    | Transmission Function Full Adder                    |

| TGA    | Transmission-Gate Adder                             |

| TS     | Transistor Sizing                                   |

| VLSI   | Very Large Scale Integration                        |

## CONTENTS

| 1     |                                              | 12 |

|-------|----------------------------------------------|----|

| 1.1   | ΜΟΤΙVΑΤΙΟΝ                                   | 13 |

| 1.2   | OBJECTIVE                                    | 13 |

| 1.3   | WORK ORGANIZATION                            | 14 |

| 2     | THEORETICAL FOUNDATION                       | 16 |

| 2.1   | FINFET DEVICES                               | 16 |

| 2.2   | VOLTAGE OPERATION                            | 17 |

| 2.3   | FULL ADDER CIRCUIT                           | 18 |

| 2.4   | COSMIC RADIATION AND INTEGRATED CIRCUITS     | 20 |

| 2.4.1 | Radiation effects on transistors             | 20 |

| 2.4.2 | Classification of radiation effects          | 22 |

| 2.5   | RADIATION-HARDENED-BY-DESIGN TECHNIQUES      | 23 |

| 3     | RELATED WORK                                 | 26 |

| 4     | METHODOLOGY                                  | 28 |

| 4.1   | ELECTRICAL SIMULATION                        | 30 |

| 4.2   | RADIATION EFFECTS EVALUATION                 | 30 |

| 4.3   | RESULTS EVALUATION                           | 32 |

| 4.4   | SET MITIGATION TECHNIQUES INSERTION          | 33 |

| 5     | RESULTS ANALYSIS                             | 34 |

| 5.1   | NOMINAL VOLTAGE                              | 34 |

| 5.1.1 | Error Rate                                   | 34 |

| 5.1.2 | Input Vectors                                | 38 |

| 5.1.3 | Ніт Туре                                     | 39 |

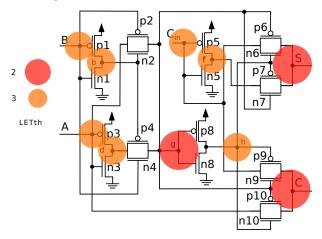

| 5.1.4 | Critical Nodes                               | 41 |

| 5.1.5 | Nominal Voltage Comparison                   | 45 |

| 5.2   | NEAR THRESHOLD VOLTAGE                       | 46 |

| 5.2.1 | Error Rate                                   | 46 |

| 5.2.2 | Input Vectors                                | 48 |

| 5.2.3 | Ніт Туре                                     | 49 |

| 5.2.4 | Critical Nodes                               | 50 |

| 5.3   | NEAR-THRESHOLD VOLTAGE COMPARISON            | 53 |

| 5.4   | NOMINAL VS NEAR-THRESHOLD VOLTAGE COMPARISON | 54 |

| 6     | SET MITIGATION TECHNIQUES                    | 57 |

| 6.1   | RESULTS ANALYSIS                             | 57 |

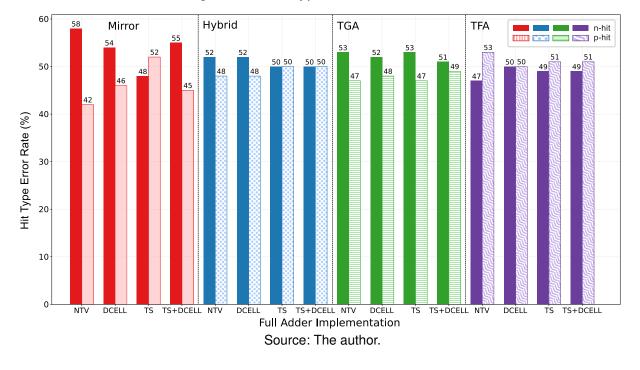

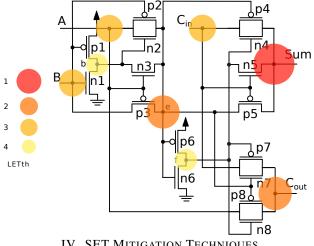

| 6.1.1 | Error Rate                                   | 58 |

| 6.1.2 | Input Vectors                                | 60 |

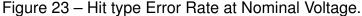

| 6.1.3 | Ніт Туре                                     | 62 |

| 6.1.4 | Critical Nodes                        | 65 |

|-------|---------------------------------------|----|

| 6.2   | DISCUSSION ON THE VOLTAGE OPERATION   | 67 |

| 7     | CONCLUSIONS                           | 69 |

| 7.1   | PUBLICATIONS                          | 70 |

|       | REFERENCES                            | 72 |

|       | APPENDIX A – SIMULATION RESULT TABLES | 79 |

|       | APPENDIX B – PUBLICATION              | 87 |

## **1 INTRODUCTION**

The advancement of technology scaling has made possible the development of more efficient and sophisticated electronic devices (JANSSON et al., 2017). This progression in technology has enabled the integration of a larger number of transistors into a single die. As a result, it has led to an increase in computational capability while reducing the overall area, consequently driving down the costs associated with integrated circuits.

The Fin Field-Effect Transistor (FinFET) structure is a 3D device with a vertical fin-like structure that allows better control of electrical current flow. FinFETs have replaced traditional planar transistors in modern integrated circuits, as they offer improved performance, lower power consumption, and reduced leakage current. This technology is a key enabler for the development of smaller, faster, and more energy-efficient electronic devices, making it widely used for advanced nodes process in the semiconductor industry.

In conjunction with these technological developments, voltage operation conditions have also played a pivotal role. By reducing the operating voltage, electronic devices have achieved remarkable gains in power efficiency. Lower voltage operation has not only reduced power consumption but has also significantly contributed to enhancing the cost-effectiveness of integrated circuits with penalties on overall performance (DE; VANGAL; KRISHNAMURTHY, 2017).

However, as voltage operation and devices size are scaled down, electronic components become increasingly vulnerable to radiation-induced interference, a phenomenon that significantly impacts their reliability and performance in electronic systems (DODD et al., 2010). This susceptibility to radiation is particularly relevant when considering Single Event Effects (SEE), which is caused by the interaction of energetic particles coming from space or terrestrial noise with silicon. With the advent of nanometer technologies, the minimum charge required to induce a Soft Error (SE) decreases. This reduction can be attributed to factors such as decreased nodal capacitances, lower supply voltages, and higher-frequency operations. Consequently, these technological advancements elevate the probability of a memory element latching onto a SE pulse generated within the combinational logic (DODD et al., 2010).

The Full Adder (FA) is one of the primary combinational cells of the Arithmetic and Logic Unit (ALU) and one of the most crucial component on computer systems (NAVI et al., 2009). Moreover, FA is generally part of the critical path in most systems making this digital component strongly affects the overall performance of the whole system.

While FinFET devices offer attractive attributes for mitigating radiation-induced soft errors, it is essential to recognize that Single Events Effects, still have the potential

to deposit sufficient amount of energy, quantified by the Linear Energy Transfer (LET) required to induce a SE. This underscores the importance of examining Single Event Transient (SET) effects on FA circuits for radiation-sensitive applications.

## 1.1 MOTIVATION

In the contemporary landscape of integrated circuits, the miniaturization and increasing complexity of electronic systems have led to a growing concern regarding the susceptibility of circuits to SETs, particularly in the context of FA circuits. As these circuits play a fundamental role in arithmetic and logic operations, any vulnerability to soft errors can have cascading effects on the reliability of larger systems.

The motivation for this research is rooted in the critical need to address the impact of SETs on the robustness and reliability of FinFET combinational cells, which are prevalent in modern integrated circuits. The reduction in supply voltages, coupled with the escalating usage of microelectronics in diverse applications, has amplified the importance of understanding and mitigating the effects of SETs, even in scenarios not traditionally associated with radiation-induced errors.

The proposed solution aims to fill a crucial gap in current knowledge by systematically analyzing various circuit-level methods to mitigate the effects of SETs in a specific group of FA circuits. The chosen focus on FinFET logic cells is particularly relevant given their widespread use in advanced integrated circuits.

## 1.2 OBJECTIVE

The main goal of this work is analyze two circuit-level methods in three approaches aimed at mitigating the effects of SET for a group of four FA circuits. Additionally, this work will provide information about the robustness to radiation and the susceptibility of SET for the selected circuit topologies. It will consider how input vectors and different current pulse types influence these aspects across different voltage operations.

In this way, the objective of this work is devised in:

- To explore radiation sensitivity across two voltage operation scenarios.

- To assess the efficacy of two circuit-level techniques in three distinct scenarios for mitigating the effects of SETs.

- To demonstrate the mitigation tendency when different radiation particle characteristics are integrated into circuit-level design.

- To present a comprehensive trade-off analysis, weighing the advantages and drawbacks of each mitigation approach concerning area, performance, and power consumption.

To provide an overall comparison between all techniques employed in the study.

In this study, we delve into two circuit-level techniques in three approaches designed to enhance the robustness of FinFET logic cells to soft errors. The first approach is the integration of decoupling cells, which act as reservoirs of charge to stabilize voltage levels, mitigate noise, and reduce power supply voltage fluctuations. Decoupling cells serve to enhance the overall performance and reliability of the circuit by minimizing electrical interference, providing a stable voltage supply, and ultimately, improving the circuit's resilience to soft errors (ZIMPECK et al., 2021).

The approach explored is Transistor sizing, a process that involves determining the physical dimensions of transistors within an integrated circuit. This includes selecting the appropriate width and length of transistors to optimize their functionality in terms of speed, power consumption, and area usage. For FinFETs, this sizing is primarily achieved by increasing the number of fins. By carefully adjusting transistor sizes, designers can fine-tune the performance of the circuit to meet specific requirements, thus contributing to the circuit's ability to withstand soft errors.

The final approach involves using both DCELL and Transistor Sizing to investigate the impact of combining these techniques. This method examines how the dual application affects overall performance and error resilience, despite the potential penalties in area and power consumption.

To evaluate the impact of the mitigation strategies, we compare the performance of FinFET logic cells with and without the application of these techniques. This comparison is based on a set of predefined metrics that serve as quantifiable indicators of the improvements achieved by incorporating Decoupling cells, Transistor sizing and combining both of them. These metrics help us evaluate the effectiveness of each technique in making FinFET logic cells more robust to soft errors, providing insights into the potential advantages and trade-offs associated with these circuit-level methods.

## 1.3 WORK ORGANIZATION

The organization of this work is structured as follows. It is divided into seven chapters, each with its own distinct focus. The Chapter 2 delves into the theoretical foundation of multigate devices, with a specific emphasis on FinFET transistors. This chapter provides a comprehensive exploration of FinFET operations, the evolution of manufacturing technology, layout design, predictive models, voltage operation, including both nominal and near-threshold operation modes, and an in-depth analysis of combinational cells, with a special emphasis on Full-Adder Circuits. It also explores (SEE), particularly SET, and concludes with a detailed definition of Radiation-Hardening by Design RHBD Schematic techniques.

Chapter 3, undertake a comprehensive review of relevant prior research within

the field. This examination of related literature establish a contextual foundation for the current research, offering insights and perspectives that contribute to a deeper understanding of the subject matter at hand. Within Chapter 4, it is provide a detailed account of the methodology used for modeling SET in the selected FA topologies, as well as the application of RHBD techniques. Additionally, we will discuss the tools and model devices utilized in our research.

Chapters 5 and 6 presents the results of the experiments, showcasing the potential of each circuit-level mitigation technique applied in the selected FA topologies and discussing the technical drawbacks of each approach. Furthermore, this chapter facilitates a comprehensive comparison of the proposed techniques, both internally and with related works.

The final chapter, Chapter 7, offers the research preliminary findings, reinforcing the initial contributions made throughout this work and outlining potential avenues for the conclusion of this research.

## **2 THEORETICAL FOUNDATION**

This research addresses a set of different subjects, encompassing the emerging device technologies and radiation effects. Within this chapter, we initiate a preliminary exploration of fundamental concepts crucial to our investigation. These include the landscape of multigate devices, the nuanced of different voltage operation, the role of full adder circuits in digital computation, and the strategic application of RHBD techniques. Each of these concepts lays the groundwork for a comprehensive understanding of the challenges at the intersection of radiation resilience and cutting-edge electronic systems.

## 2.1 FINFET DEVICES

Due to the ongoing efforts to enhance current drive and improve control over short-channel effects, MOS transistors have progressed from classical, planar, single-gate devices into three-dimensional structures with a multi-gate design. A FinFET is a type of transistor architecture used in the design and manufacturing of integrated circuits. It is a three-dimensional structure that improves upon the traditional planar Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) design.

In a FinFET, the channel is raised above the substrate, allowing better control over the flow of current. This vertical fin structure helps mitigate issues associated with traditional planar transistors, such as leakage current and power consumption. The increased control over the channel also enables more efficient use of space, allowing for the integration of a larger number of transistors on a chip. The adoption of FinFETs has contributed to improved performance, energy efficiency, and overall transistor density in integrated circuits (COLINGE, 2007). FinFET technology has become a standard in modern semiconductor manufacturing processes, especially as chip features have shrunk to smaller nanometer scales.

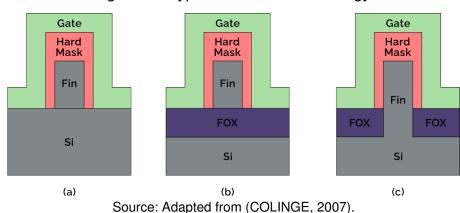

Various manufacturing methods exist for FinFET devices, including Silicon-On-Insulator SOI FinFET and bulk FinFET. Figure 1 illustrates the comparison between FinFETs implemented on conventional wafers, SOI and bulk with insulator.

Bulk FinFET, introduced and adopted by Intel starting at the 22 nm node in 2012, utilizes the triple gate model (AUTH, 2012). In this design, the fin share the same silicon substrate, as illustrated in Figure 1 (a). The decision to employ bulk FinFETs was motivated by lower manufacturing costs and the application of the planar CMOS fabrication model, despite having slightly lower electrical characteristics compared to SOI FinFETs. In contrast, SOI FinFETs feature physically isolated fins achieved by an oxide layer, as seen in Figure 1 (b). Additionally, bulk FinFETs can be constructed with a dense insulator to prevent inversion between the fins, as shown in Figure 1 (c).

#### Figure 1 – Types of FinFET Technology.

#### 2.2 VOLTAGE OPERATION

Nominal voltage operation and near-threshold voltage operation in Very Large Scale Integration (VLSI) circuits represent distinct approaches to designing circuits with different considerations for power consumption, performance, and energy efficiency.

Nominal voltage operation is the conventional and standard approach in VLSI circuit design. In this mode, circuits are designed to operate at a standard voltage level that ensures reliable and high-performance functioning. The emphasis is on achieving a balanced performance with considerations for speed, power consumption, and overall efficiency. Circuits designed for nominal voltage provide a reference point for achieving optimal processing speeds and are suitable for applications where performance is a primary concern.

On the other hand, near-threshold voltage operation involves running circuits at voltage levels close to the threshold voltage of the transistors. This approach is chosen to minimize power consumption, making it particularly suitable for applications with stringent power constraints. Operating at lower voltage levels offers the potential for improve energy efficiency by an order of magnitude (KAUL et al., 2012). However, this comes with challenges related to maintaining reliability, avoiding errors, and ensuring the circuit meets performance requirements under lower voltage conditions.

The key usage difference lies in the trade-off between power consumption and performance. Nominal voltage operation prioritizes speed and overall performance, making it more appropriate for applications where high processing speeds are crucial, even at the cost of increased power consumption. Near-threshold voltage operation, on the other hand, prioritize energy efficiency with some degradation on delay, making it suitable for applications where minimizing power consumption is a critical requirement.

## 2.3 FULL ADDER CIRCUIT

The addition operation holds significant importance in computational systems, serving as the foundation not only for ALU operations but also for tasks like multiplication, address generation, and various filtering purposes (WESTE; HARRIS, 2010). Given the critical role of this circuit, numerous FA architectures have been proposed in the literature, aiming to meet diverse constraints related to speed, power, and area (WESTE; HARRIS, 2010; ZHUANG; WU, 1992; CHANG; GU; ZHANG, 2005).

The FA circuit consists of two outputs and three inputs: Sum, which propagates the addition result after computation; Cout, which carries the most significant bit of the addition result to the next stage of the sum; and inputs A and B, which receive the operands for the addition operation. Cin is responsible for receiving the Most Significant Bit (MSB) value propagated from the Cout. Table 1 presents the truth table for the Full Adder circuit.

|                     | Inpu | its | Outputs |      |  |  |  |

|---------------------|------|-----|---------|------|--|--|--|

| Α                   | В    | Cin | Sum     | Cout |  |  |  |

| 0                   | 0    | 0   | 0       | 0    |  |  |  |

| 0                   | 0    | 1   | 1       | 0    |  |  |  |

| 0                   | 1    | 1 0 |         | 0    |  |  |  |

| 0                   | 1    | 1   | 0       | 1    |  |  |  |

| 1                   | 0    | 0   | 1       | 0    |  |  |  |

| 1                   | 0    | 1   | 0       | 1    |  |  |  |

| 1                   | 1    | 0   | 0       | 1    |  |  |  |

| 1                   | 1    | 1   | 1 1     |      |  |  |  |

| Source: The author. |      |     |         |      |  |  |  |

Table 1 – Truth table for Full Adder.

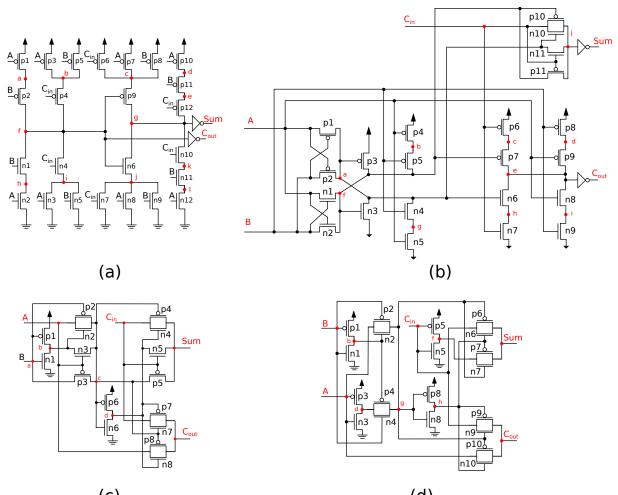

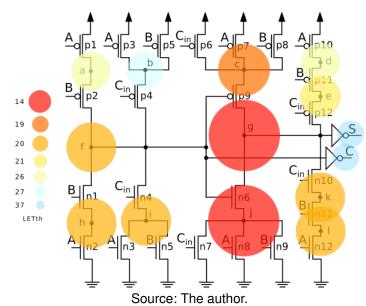

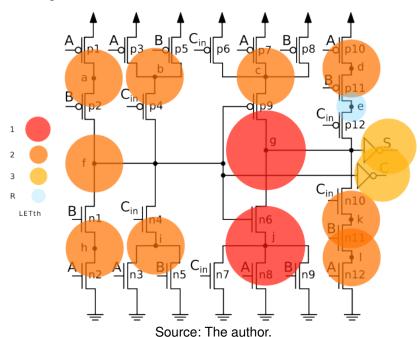

This work adopts four FA topologies, highlighting all internal target nodes for SET insertion, as shown in Figure 2 (a)-(d). The complementary CMOS full adder, Figure 2 (a) known as Mirror FA, utilizes the conventional CMOS structure featuring pMOS pull-up and nMOS pull-down network of transistors (CHANG; GU; ZHANG, 2005). The output stage incorporates series transistors forming a weak driver, necessitating additional buffers at the final stage to ensure sufficient driving power for cascaded cells. The complementary CMOS style offers robustness against voltage scaling and transistor sizing, crucial for reliable operation at low voltage and various transistor sizes. Furthermore, the layout of the Mirror FA circuit is straightforward and area-efficient, attributed to complementary transistor pairs and a reduced number of interconnecting wires.

The topology in Figure 2 (b) is the Hybrid Full Adder. This FA encompass a XOR/XNOR, sum, and carry-out subcircuits, adopting a pass logic design style for simultaneous and efficient generation of XOR and XNOR functions used (CHANG;

GU; ZHANG, 2005). A well-driven carry-out is achieved through the complementary CMOS-style circuit. Additionally, the last-stage inverter decouples the output and input to enhance driving capability. Despite a higher transistor count compared to other designs, the Hybrid circuit demonstrates high energy efficiency across a broad supply voltage range.

Figure 2 – Full Adders topologies.

(C) (d) Source: Mirror (a) and Hybrid (b) from (CHANG; GU; ZHANG, 2005), TFA (c) from (ZHUANG; WU, 1992), and TGA (d) from (WESTE; HARRIS, 2010).

A transmission function full adder (TFA) is a CMOS full adder designed based on the transmission function theory (ZHUANG; WU, 1992). It has simpler circuit with less transistors being used in the design to perform the FA Boolean expression, the topology is shown in Figure 2 (c).

A transmission-gate adder (TGA), shown in Figure 2 (d), is a different full adder design that uses transmission gates to form multiplexers and XORs. This topology has the advantage of using fewer transistors and having equal Sum and Cout delay time (WESTE; HARRIS, 2010).

The four full adder topologies were chosen for this work because they are among the most commonly found in the literature, providing a comprehensive set for analyzing radiation robustness. Additionally, these topologies represent a diverse range of design approaches, including complementary logic, pass transistor logic, and a hybrid implementation that combines both methods. This multidisciplinary selection ensures a thorough evaluation of the different techniques and their effectiveness in enhancing the robustness of FinFET-based processors in radiation environments.

## 2.4 COSMIC RADIATION AND INTEGRATED CIRCUITS

Cosmic rays are high energy particles created in space by nuclear reactions in stars, in supernovas, and explosions in the galactic nucleus (ZIEGLER, 1996). There are different types of cosmic rays and they are categorized as follow:

- Primary cosmic rays: galactic particles that enter the solar system and can hit the Earth. Solar cosmic rays, the particles generated by the Sun and contained in the solar wind, are also considered as primary cosmic rays (AUTRAN; MUNTEANU, 2015).

- Secondary cosmic rays: particles in the Earth's upper atmosphere produced by the collision between primary cosmic rays and the atoms in the air. Those interactions create cascade reactions and generate more particles (e.g. neutrons, neutrinos, electrons) (AUTRAN; MUNTEANU, 2015).

- Terrestrial cosmic rays: Particles that finally hit the Earth. Less than 1% of the terrestrial particles are primary cosmic rays. The other 99% of particles is mostly composed of third to seventh generation particles (ZIEGLER, 1996).

In the semiconductor industry, this energetic particles hitting integrated circuits circuit can lead to Single Event Effects, so they have to be cared about due the affect the reliability of the systems. In addition, with the transistor size reduction and increase integration, following Moore's law, circuit reliability to radiation is diminishing. Where only one transistor was affected by a radiation strike, now several transistors can suffer from one single strike.

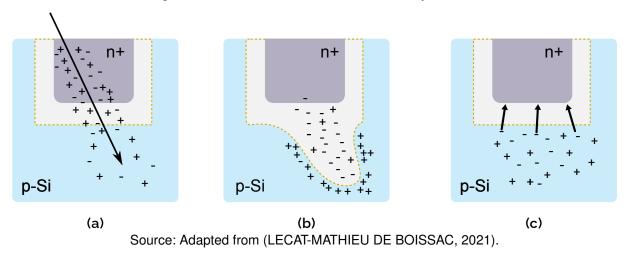

#### 2.4.1 Radiation effects on transistors

When an energetic particle hits a transistor junction, the impact triggers the charge collection mechanism of the device, collecting charge while the particle tracks into the depletion region (LEE et al., 2015). Figure 3 illustrates the three steps in the interaction between alpha particles and a PN junction. When an electrical charged particles penetrate silicon, they create an ionization track of electron-hole pairs, known as direct ionization Figure 3 (a). This process generates a parasitic current and causes

funneling in the space charge region Figure 3 (b). Finally, the remaining charges diffuse, producing a diffusion current Figure 3 (c). This current is the source of a soft error.

Figure 3 – Effects of radiation on a PN junction.

The energy transferred by ionization can be calculated using the Linear Energy Transfer. The LET represents an estimation of the energy collected by the material during the ionization process by an incident particle. It is defined as the energy loss per unit distance for a particle with a given density. The  $Q_{coll}$ , defined by the Eq. (2), is the amount of charge collected due to an ion strike in the junction.  $I_o$  is the minimum current to cause a fault, obtained by simulations. The term  $\tau_{\alpha}$  is the collection time constant of the junction, and  $\tau_{\beta}$  is the time constant for the initially establishing the track. The term Q is the constant charge that the particle deposits along its track and L is the charge collection depth.

$$LET = \frac{Q_{coll}}{Q \times L} \tag{1}$$

$$Q_{coll} = I_0 \times (\tau_\alpha - \tau_\beta) \tag{2}$$

The LET can also be expressed in terms of charged deposited by the particle to the material per unit path length, typically in MeV/cm (mega-electron volts per centimeter). It provides information about the density of ionization events along the path of a charged particle as it travels through a material. High-LET radiation tends to deposit more energy in a smaller volume, leading to a higher probability of causing ionization and potentially affecting the operation of electronic devices. For silicon the conversion factor is (GOMEZ TORO, 2014) :

$$1 fC/\mu = 0.0969 MeV/(cm^2/mg)$$

(3)

Linear Energy Transfer is often used to characterize the impact of ionizing radiation, such as cosmic rays or particles from radioactive decay, on the performance and reliability of electronic components (SCHRIMPF et al., 2012).

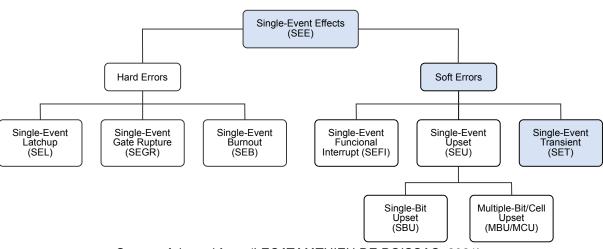

#### 2.4.2 Classification of radiation effects

The parasitic current caused by ionization is the main phenomenon affecting transistors. Transistors respond differently to this ionization, resulting in induced errors that can degrade their performance either permanently or temporarily. Single Event Effects is a broader term that classifying these errors and is crucial for focusing research efforts on finding effective solutions. As shown in Figure 4, SEEs can be categorized into two main types: soft errors and hard errors. Soft errors are nondestructive and reversible corruptions of a signal or data, whereas hard errors are permanent damages to the device or circuit. This work will focus on soft errors, as hard errors are beyond its scope.

Figure 4 – Classification of Single Event Effects.

Source: Adapted from (LECAT-MATHIEU DE BOISSAC, 2021).

Soft Errors is a broader term that encompasses various errors, including Single Event Upset (SEU), Single Event Functional Interrupt (SEFI), Single Bit Upset (SBU), and Single Event Transient.

A Single Event Upset is a type of error in a digital circuit caused by a single ionizing particle striking a sensitive node results in a transient voltage spike, which can flip a bit in memory or disrupt the operation of logic circuits. An SEU occurs in a memory element (such as a latch, flip-flop, RAM cell, or asynchronous memory logic) as a result of either latching an SET or a direct ionizing strike on the memory element. Single Event Upsets are the most common type of soft errors in memories and sequential logic. SEUs do not cause permanent damage to the device, but they can lead to temporary data corruption or malfunction until the system is reset or the error is corrected. Since an SEU is stored in a memory element, the error is not transient. It can persist for several clock cycles in synchronous logic or until the next transition edge of an input signal in asynchronous logic. This prolonged presence of the error makes SEUs a significant concern in maintaining the reliability of electronic systems.

SEUs are primarily a concern in environments with high levels of radiation, such as space, where cosmic rays and other high-energy particles are prevalent. However, they can also occur at ground level due to particles from cosmic rays and radioactive decay in the materials used in the device. The increasing density and miniaturization of integrated circuits make them more susceptible to SEUs, necessitating robust error detection and correction mechanisms to ensure the reliability of electronic systems.

On the other hand, Single Event Transient is also a class of non-destructive errors caused due to a single ionizing particle strike in a device silicon however on combinational circuits. Because the non-sequential circuits outputs are based on the logical relationship to the input without retention capabilities any voltage glitch in the transistor may cause a temporary change in the output. When a charged particle interacts with a semiconductor device, it can deposit energy and generate electron-hole pairs. This can lead to a transient voltage glitch in the affected circuit, potentially causing incorrect operation.

The SET can affect the combinational cells resulting in wrong output values that, if held in the memory elements, can compromise the system's correctness (FERLET-CAVROIS; MASSENGILL; GOUKER, 2013). The SET effects on over 180 nm technologies are not noticed mainly due to electrical and logical masking (SHIVAKUMAR et al., 2002). However, with the advance to sub-90 nm nodes, the effects of charge collection has increased, show the need to understand and consider the SET effects during IC design steps in order to enhance reliability (REJIMON, 2006).

## 2.5 RADIATION-HARDENED-BY-DESIGN TECHNIQUES

At advanced technology nodes, a significant reliability concern arises from the circuits vulnerability to environments noise. While radiation effects in electronic systems were initially predominantly associated with avionic or space applications, the electronic devices scaling and the use of low supply voltages have extended the relevance of these concerns to terrestrial applications (DODD et al., 2010).

Enhancing the reliability of integrated circuits involves radiation hardening strategies that can be explored from fabrication process modifications to different circuit design implementations. Because Radiation-Hardening-by-Process (RHBP) techniques has high costs and low-grade performances Radiation-Hardening-by-Design (RHBD) techniques are alternatives that have proven effective in ensuring resilience against radiation effects, particularly in highly-integrated technologies (LACOE et al., 2000). Complete mitigation or some level of hardness against radiation effects can be achieved through circuit-based techniques. Circuit design modifications may lead to the incorporation of components or filtering elements, experimentation with different transistor arrangements, gate sizing, transistor folding, hardware redundancy, increase of the capacitance in vulnerable nodes, and other strategies (CHEN et al., 2017; LACOE et al., 2000; LILJA et al., 2013).

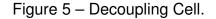

The circuit-level mitigation techniques of SET effects chosen for this work are the use of Decoupling Cell (DCELL) and exploring different transistor sizing (TS). DCELLs are composed of two transistors arranged in the cross-coupled mode, showed in Figure 5. Using two Decoupling Cells are recommended to achieve a more robust design for filtering positive and negative hit particles. DCELLs are responsible for increasing the total capacitance in the node applied, ensuring higher noise immunity in logic gates (REIS, R. et al., 2020). Generally, DCELLs are applied only to the output of the circuit to minimize noise interference. However, we opt to extend the traditional approach to observe the effects of the DCELL insertion on the internal node under evaluation, i.e, where the particle collision is happening.

Source: Adapted from (ZIMPECK et al., 2021).

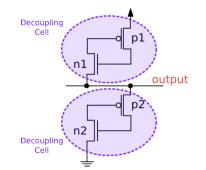

Sizing the transistors in FinFET technologies is related to the increase in the number of fins, as Figure 6 shows. When the number of fins is increased, the drive current of the transistor rises because the effective channel width is expanded. This improvement in drive current allows the transistor to switch faster, enhancing the overall performance and speed of the circuit (CLARK et al., 2016).

In the radiation scenario sizing the transistor leads to an increase in the amount of charge a particle must deposit in the depletion region to generate a SET. The TS was applied to all transistors of the FAs circuits, increasing the number of fins from one to three. Despite the area increase of TS, the design rules of the 7 nm ASAP7 technology recommends the adoption of the three fins to ensure the best routability of the circuits (CLARK et al., 2016). Thus, the area increase of TS strategy in the experiment is in an acceptable range for FinFET designs.

## **3 RELATED WORK**

Some works have presented discussions about a variety of FAs using different logic styles (NAVI et al., 2009; DA SILVA; MEINHARDT; REIS, R., 2019). The key focus of these works is on reducing average power consumption and delay. The effects of nanometer variability is also a current research topic, mainly process variability on FAs (DOKANIA; IMRAN; ISLAM, 2013; AMES et al., 2016).

Other mitigation techniques are proposed to reduce the impact of process variability on these circuits (DOKANIA; ISLAM, 2015; MORAES et al., 2018; ZIMPECK et al., 2021). In (ZIMPECK et al., 2021), it is explored the influence of process variations and radiation-induced soft errors on FinFET logic cells, using the 7 nm technological node as a case study. The authors utilize the MUSCA SEP3 (HUBERT et al., 2009) radiation event generator for accurate soft error estimation and investigate four circuit-level mitigation techniques: transistor reordering (BUTZEN et al., 2010), decoupling cells (ANDJELKOVIC, M. et al., 2018), Schmitt Trigger (MORAES et al., 2018), and sleep transistors (RICARDO REIS YU CAO, 2014). The study evaluates the effectiveness of these techniques against various levels of process variation and radiation characteristics, offering a comprehensive trade-off analysis regarding reliability gains and design costs in terms of area, performance, power consumption, and SET resilience.

SET effects have been studied for different circuits, for example XOR (DE AGUIAR; MEINHARDT; REIS, R. A. L., 2017) and majority voters (OLIVEIRA, I. F. V. et al., 2022; AGUIAR, Y. de et al., 2017; BRENDLER et al., 2020). The authors at (OLIVEIRA, I. F. V. et al., 2022) evaluates various majority voter designs to determine their effectiveness in fault tolerance, particularly in radiation-prone environments. The study focuses on the resilience of these designs against SEUs and single-event SETs, which are critical for ensuring reliable operations in electronic circuits used in space and other high-radiation environments. The research compares the performance of different majority voter circuits, analyzing their ability to mitigate faults and maintain operational integrity. The evaluation is based on metrics such as error rate, power consumption, and area overhead. The results highlight the trade-offs between robustness and resource efficiency, providing valuable insights for designing more reliable digital systems. The findings underscore the importance of selecting appropriate majority voter designs to enhance fault tolerance in critical applications.

The authors of (AGUIAR, Y. Q. et al., 2020) presents transistor folding as layout technique for RHBD logic gates. This approach aims to mitigate the effects of SETs in integrated circuits, which are critical for ensuring the reliability of electronic devices in radiation-prone environments. The study emphasizes the effectiveness of transistor folding in enhancing circuit robustness without significantly impacting performance metrics like area, power, and speed. By employing Monte Carlo simulations, the researchers demonstrate the improved resilience of circuits using this technique compared to conventional designs.

In (AZIMI; DE SIO; STERPONE, 2021), it is discussed a design for a radiationhardened full-adder cell implemented in 45-nm technology. This design improves resilience against SETs through selective duplication of sensitive transistors based on radiation sensitivity analysis. Experimental results indicate a 62% reduction in SET sensitivity compared to the standard design, with improvements in performance and power overhead, and no increase in area overhead for the specific topology evaluated.

However, as far as we could investigate, there is a lack of more studies evaluating the radiation robustness FAs in multigate technologies considering different voltage scenarios and different full adder topologies.

| Authors           | Focus                   | Key Findings                            |  |

|-------------------|-------------------------|-----------------------------------------|--|

| Navi et al., 2009 | Power consumption       | Reduction on average power              |  |

|                   | on FAs                  | consumption and delay.                  |  |

| Da Silva et al.,  | Variability on FAs      | Reduction on average power              |  |

| 2019              |                         | consumption and delay.                  |  |

| Dokania et al.,   | Variability on FAs      | Comparative analysis for FAs designs    |  |

| 2013              |                         | offering minimum variabilities.         |  |

| Ames et al.,      | Variability on FAs      | Process variability is the main         |  |

| 2016              |                         | responsible for the high delay and      |  |

|                   |                         | power.                                  |  |

| Dokania et al.,   | Mitigation techniques   | Circuit-level technique to mitigate the |  |

| 2015;             | for variability on FAs  | adverse effects of PVT variations.      |  |

| Moraes et al.,    | Mitigation techniques   | Improvement in average delay and        |  |

| 2018;             | for variability         | power consumption.                      |  |

| Zimpeck et al.,   | Mitigation techniques   | Provides a trade-off analysis on        |  |

| 2021              | for process variability | reliability gains and design costs.     |  |

| Oliveira et al.,  | SET effects on          | Comparative analysis of radiation       |  |

| 2022;             | majority voters         | sensitivity.                            |  |

| Brendler et al.,  | SET effects and         | Comparative analysis of radiation       |  |

| 2020              | variability on majority | sensitivity.                            |  |

|                   | voters                  |                                         |  |

| Aguiar, Y. de et  | SET effects on          | Comparative analysis of radiation       |  |

| al., 2020         | majority voters         | sensitivity.                            |  |

| Azimi et al.,     | Radiation-hardened      | Reduction in the SET sensitivity.       |  |

| 2021              | FAs design              |                                         |  |

Table 2 – Related work summary.

### 4 METHODOLOGY

The goal of this work is to evaluate the sensitivity of full adder circuits, observing the impact of SET faults. For this purpose, this study presents comparison results for a subset of common full adder topologies found in the literature operating under nominal voltage (NV) conditions and near-threshold voltage (NTV). Subsequently, this work defines a comparative methodology based on electrical simulations in order to estimate the robustness of different topologies, identifying their critical points. Finally, fault mitigation techniques are inserted at the circuit level, and their effectiveness in enhancing radiation robustness is also evaluated using electrical simulations.

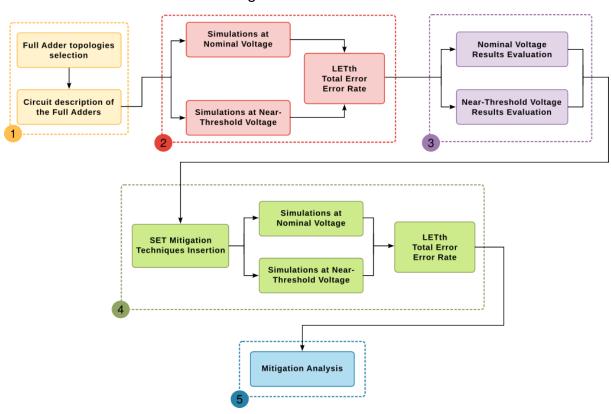

Figure 7 – Workflow.

Source: The author.

Currently, the workflow consists of five different steps, as shown in Figure 7: (1) a pre-study, (2) nominal and NTV simulation, (3) sensitivity results evaluation, (4) mitigation techniques insertion and lastly, (5) mitigation results analysis.

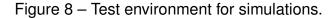

The first step involves selecting a subset of the most common full adder topologies. These topologies were described in Simulation Program with Integrated Circuit Emphasis (SPICE) to perform electrical simulations using the 7nm FinFET Predictive Technology Model (PTM) by (CLARK et al., 2016). All transistors on all circuits were set to the minimum size of 1-fin to represent a critical scenario for robustness tests. Two inverters were inserted in the input signals to emulate a realistic input slope, and the load capacitance was adjusted to correspond to a fanout of 4.

The second step is the core of the proposed workflow. In this step, electrical simulations are conducted to obtain important metrics such as LET threshold (LETth), total error propagated, and error rate for each node. The nominal and near-threshold voltage for the devices was set to 0.7 V and 0.35 V, respectively. Fault simulation is conducted at the circuit level using HSPICE. Each internal node is tested individually to simulate the impact of a particle hit. In our work, we define the SET pulse as the voltage glitch occurring at the output of a logic gate, influenced by the deposited charge in any internal device. The radiation pulse is introduced as an independent current source at the target junction of the device, represented by the circuit node in the simulation and evaluation (SAYIL, 2016). Depending on the location of the ion impact, there are two types of single-event hits: n-hit and p-hit. An n-hit causes a high-to-low transition at the sensitive node, while a p-hit results in a low-to-high transition (DUAN; WANG, L.; LAI, 2011). The experiments involve determining the minimum current required to induce an output flip in the circuit, followed by calculating the minimum LETth based on the equation in (WANG, F.; AGRAWAL, 2008). The experiment concludes when the simulation requires a LETth value exceeding 100 MeVcm<sup>2</sup>/mg. The current value is increased at 0.5  $\mu$ A step to determine the minimum current to provoke the unexpected behavior on one of the FA outputs. The second step is essential for evaluating and identifying the critical parts of each circuit.

Step 3 comprises all the result evaluation that will guide the SET mitigation strategies. The focus is on evaluating and interpreting the results obtained from the default conditions simulations in stage (2) in order to find the critical internal nodes for each topology and also critical current to generate a SET.

Mitigation techniques, specifically DCELL and Transistor sizing, are introduced to address Single Event Transient effects, in the fourth stage of the workflow. The DCELL is inserted only to the target node that will receive the pulse strike, and the transistor fins are sized according to the sizing strategy of the circuit being simulated. Subsequently, another round of SPICE simulation using the HSPICE tool is conducted for the modified circuits, operating at both nominal voltage and near-threshold voltage. The same metrics (LETth, Total error occurrence, and Error rate) are captured.

In step four, the mitigation techniques are applied to the same circuits and the results are collected. Finally, in the last step, the same metrics from step two are analyzed to understand the improvements in radiation robustness provided by each chosen technique.

## 4.1 ELECTRICAL SIMULATION

The circuits were simulated using the 7 nm ASAP7 Regular Voltage Technology (RVT) model (CLARK et al., 2016). The nominal operation adopts the nominal voltage for the RVT devices (0.7 V), and the near-threshold voltage is defined as half of the nominal voltage (0.35 V). Despite the recommendation of using 3-fin transistors (CLARK et al., 2016), in order to represent the critical scenario for robustness tests, all transistors on both circuits adopt the minimum size of 1-fin. Figure 8 illustrate the simulation environment used for the experiments in this work. To emulate a realistic input slope, we insert two inverters in the input signals. The load capacitance is set up to correspond to a fanout of 4.

## 4.2 RADIATION EFFECTS EVALUATION

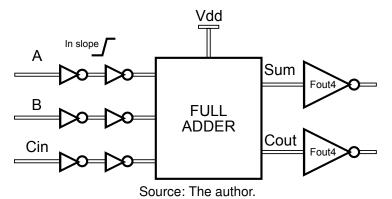

When an energetic particle hits a transistor junction, the impact triggers the charge collection mechanism of the device, collecting charge while the particle tracks into the depletion region (LEE et al., 2015), as illustrated in Figure 9 (a). The Linear Energy Transfer estimates this collected charge, thus, this metric is adopted to evaluate the robustness of an under-evaluation cell.

This work adopted the equation model defined in (SAYIL, 2016). The LETth is calculated for the FAs topologies using the Eq. (1).

In this work, the collection time constant is set to 200 ps, the initially constant time is set to 10 ps (SAYIL, 2016). The value of the Q and L constants on Eq. (1) for the FinFET devices used are 10.8 fC/ $\mu$ m and 21 nm (FANG; OATES, 2011), respectively.

In our work, we define the SET pulse as the voltage glitch occurring at the output of a logic gate, which is influenced by the quantity of deposited charge. Within our analyzed circuits, the transistor demonstrates sensitivity to charge collection when it is reverse biased and when there exists a low-resistance path between the affected node and the output. Depending on the location of impact from the incident ion, there are two

#### Figure 9 – Charge collection mechanism.

Source: Adapted from (LEE et al., 2015).

types of single-event hits: n-hit and p-hit. An n-hit results in a high-to-low transition at the sensitive node, whereas a p-hit causes a low-to-high transition (DUAN; WANG, L.; LAI, 2011). Thus, the radiation effect of a particle hitting at the junction of a device is described as a double exponential transient pulse shown in Figure 9 (b). The pulse can be modeled as a low-to-high (010) to reflect p-hits or a high-to-low (101) to n-hits. This work adopted the equation model defined in (SAYIL, 2016). The fault simulation is carried out at the circuit level using HSPICE and the radiation pulse is introduced as an independent current source at the target junction of the device, represented by the circuit node in the simulation and evaluation. The current value is increased at 0.5  $\mu$ A step to determine the minimum current to provoke the unexpected behavior on one of the FA outputs. The simulations were performed in parallel using a Python script in order to automate and speed up the experiments results.

The experiments consist of finding the minimum current necessary to provoke an output flip of the circuit to them calculate the minimum LET, i.e., the LET threshold based on the equation in (WANG, F.; AGRAWAL, 2008). The experiment defines as a limit to be considered a robust a node (i.e. a robust junction) when the simulation requires a LETth value over 100 *MeVcm*<sup>2</sup>/*mg* since most particles encountered in space have lower LET (ANDJELKOVIC, Marko; KRSTIC, 2024). The circuit-level abstraction with electrical simulations allows us to evaluate all internal nodes, highlighted in red in Figure 2, and all input vectors, observing the fault propagation to each output function of the FA. This experiment was carried out for nominal voltage and NTV operation. The error susceptibility rate is the relation between the number of errors per node (or vector) and the total errors observed on the circuit.

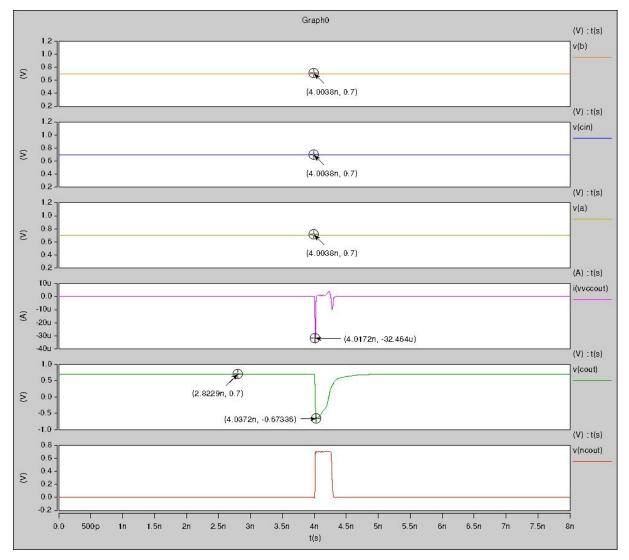

Figure 10 illustrates the radiation glitch for a given pulse under the input combination 111 during a n-type hit. The current source i(vvccout), representing the charge collected of -32.454  $\mu$ A, generates a voltage drop in V(cout) from 0.7 V to 0.67336 V. This voltage drop is then propagated through V(ncout), demonstrating that a fault was captured by the charged circuit at the output.

Source: The author.

## 4.3 RESULTS EVALUATION

In our investigation of SETs in FA circuits, understanding the distribution of errors across different nodes is vital for pinpointing vulnerable areas and devising effective mitigation strategies. The formula used to calculate the error rate is presented in (4). This expression involves two key variables:  $E_n$ , which represents the total errors found for a specific node, and  $E_{total}$ , which signifies the total errors observed in the entire topology. The formula calculates the ratio of errors at the specific node. This ratio is then multiplied by 100 to express the result as a percentage. The resulting  $E_r$  represents the

proportion of errors attributed to the specific node in relation to the total errors observed in the topology.

$$E_r = \frac{E_n}{E_{total}} \times 100 \tag{4}$$

Also, the influence of the input vector must be consider in the radiation evaluation. Different input vectors can lead to variations in the occurrence of errors within a circuit. By analyzing the impact of each input vector, it becomes possible to identify specific combinations that are more prone to propagating failures. This information is invaluable for localizing and understanding the sources of errors within the circuit.

Analyzing different radiation pulse types is crucial for understanding how specific environmental conditions, represented by distinct pulse patterns, impact the performance and reliability of integrated circuits. Each pulse type represents a unique set of challenges and stressors on the circuit components, influencing their response to radiation-induced effects.

## 4.4 SET MITIGATION TECHNIQUES INSERTION

To mitigate the impact of radiation, three distinct approaches are employed: DCELL, TS, and a combined strategy utilizing both DCELL and TS. The implementation of these techniques involves incorporating specific modifications into the SPICE descriptions of the transistor network constituting the evaluated FA circuit. In the DCELL technique, the extra cross-coupled circuit is inserted into each internal target node, ensuring that DCELL is applied to every node in the circuit under test. In the transistor sizing approach, all internal transistors of the topology under test are resized from 1-fin to 3-fin, including in the DCELL when combining both techniques. These tailored modifications precede the rerun of simulations to assess the effectiveness of each mitigation technique. Subsequently, the results derived from the application of these techniques are meticulously examined and discussed to evaluate their impact on enhancing the circuit's resilience against radiation-induced effects.

## **5 RESULTS ANALYSIS**

The evaluation of the radiation sensitivity begins with testing the circuits while operating at their nominal voltage and then at NTV. This allows us to understand the impact of radiation in both typical and non-typical operating conditions. Throughout the evaluation process, reference values of absolute LETth are available for each result table. The complete result simulations can be checked in the Apendix A. LETth values greater than 100 MeVcm2/mg indicate nodes that are not sensitive to SET (AND-JELKOVIC, Marko; KRSTIC, 2024) and this condition where the circuit remains robust are denoted by a "-" in the results tables. To identify critical cases that are more susceptible to radiation-induced errors, we highlight them in red within the tables. By focusing attention on these critical cases, significant insights can help to highlight potential weaknesses within the circuit's radiation tolerance and develop targeted mitigation strategies to enhance overall reliability.

The presentation of results will follow a structured format. Initially, findings for the nominal voltage operation will be presented, covering the error rate, critical nodes, critical input vectors, and the critical hit type. Subsequently, a similar set of results will be provided for the NTV operation. Finally, an overall comparison between the two voltage operations will be outlined.

## 5.1 NOMINAL VOLTAGE

The nominal voltage denotes the predetermined standard operating voltage level at which a digital circuit is engineered to achieve optimal functionality. It represents the voltage necessary to uphold the performance of the circuit under typical operational circumstances. This particular voltage typically derives from the precise specifications of the process technology employed in the production of integrated circuits. The utilization of a circuit at its nominal voltage is fundamental in satisfying the stipulated requirements for performance, speed, and reliability, all while maintaining a reasonable power consumption. Within the context of the technology applied in this research, the nominal voltage is defined as 0.7 V.

## 5.1.1 Error Rate

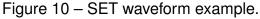

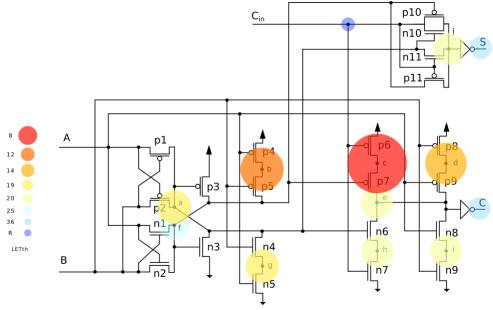

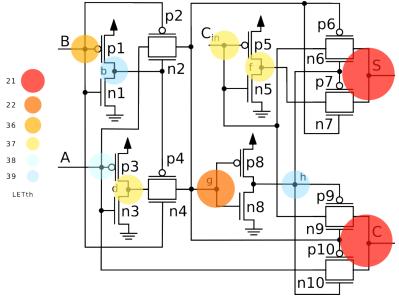

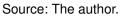

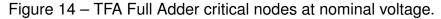

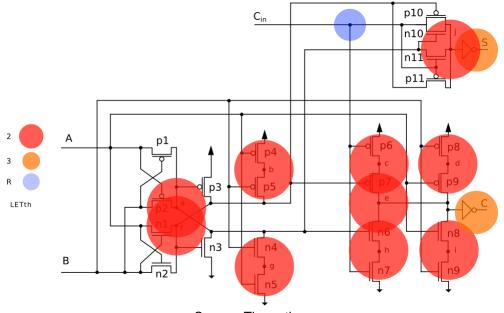

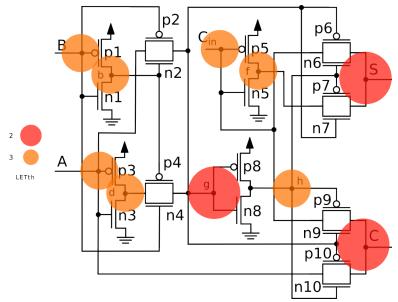

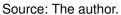

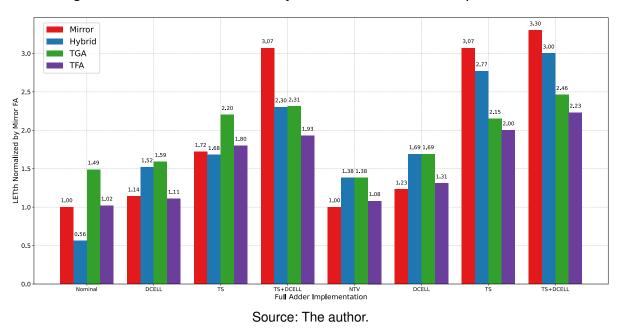

Based on the total error analysis for each node we can identify the most and least sensitive nodes, highlighted in Figure 11, 12, 13, and 14. The total error is indicative of the robustness of each node in the face of faults, with lower values signifying less sensitivity. Also the finds in this sections is summarized in Table 7.

The analysis of LETth in Table 3 for the Mirror FA at nominal voltage sheds light on node k, which exhibit a higher probability to generate transient errors in this

topology. Node k collectively contribute to nearly 13% of all error occurrences observed in our experiments, emphasizing its significance in the error rate landscape. Nodes e, f, g, l, Sum and Cout also demonstrate notable error rates, although these values vary depending on the input pulses. These nodes can be considered moderately sensitive, as their error rates range from 9% to 10% of the total error occurrence. Nodes that are farther from the output in the Mirror FA topology exhibit greater resilience to noise interference. This increased resilience is attributed to the the capability of the transistor network to mask potential glitches in the signal. Specifically, nodes driven by more than one transistor, such as nodes b, c, i, and j, have shown a higher resistance to error propagation.

To summarize, node k emerges as the most sensitive components in the Mirror FA topology, while nodes e, f, g, l, Sum and Cout exhibit moderate sensitivity. Nodes b, c, i, and j demonstrate relatively lower sensitivity to faults, highlighting their robustness.

| Pulse  | Input |    |    |    |    |    |    | No | minal |    |    |    |    |     |      |

|--------|-------|----|----|----|----|----|----|----|-------|----|----|----|----|-----|------|

| i uise | Input | а  | b  | С  | d  | е  | f  | g  | h     | i  | j  | k  |    | Sum | Cout |

|        | 000   | -  | -  | -  | -  | -  | -  | -  | -     | -  | -  | 97 | -  | 45  | 45   |

|        | 001   | -  | -  | -  | -  | -  | -  | -  | 96    | -  | -  | 67 | 97 | -   | 45   |

|        | 010   | -  | -  | -  | -  | -  | -  | -  | -     | -  | -  | 52 | 59 | -   | 45   |

| 010    | 011   | -  | -  | -  | -  | -  | 27 | -  | -     | 47 | -  | -  | -  | 45  | -    |

|        | 100   | -  | -  | -  | -  | 26 | -  | -  | -     | -  | -  | 98 | -  | -   | 45   |

|        | 101   | 27 | -  | -  | -  | -  | 27 | -  | -     | 48 | -  | -  | -  | 45  | -    |

|        | 110   | 51 | 27 | -  | -  | -  | 27 | -  | 48    | -  | -  | -  | -  | 45  | -    |

|        | 111   | -  | -  | -  | -  | -  | 60 | -  | -     | -  | -  | -  | -  | -   | -    |

|        | 000   | -  | -  | -  | 42 | 21 | 46 | 14 | 89    | -  | 14 | 20 | 40 | -   | -    |

|        | 001   | -  | 41 | -  | -  | 26 | 20 | 27 | 20    | -  | 47 | 52 | 59 | 37  | -    |

|        | 010   | -  | 41 | -  | 26 | 26 | 20 | 27 | 97    | -  | 47 | 97 | -  | 37  | -    |

| 101    | 011   | 83 | -  | 39 | 85 | 53 | -  | 20 | -     | -  | -  | 71 | -  | -   | 37   |

|        | 100   | 41 | -  | -  | -  | 78 | 21 | 27 | 96    | 20 | 47 | 66 | 97 | 37  | -    |

|        | 101   | -  | -  | 40 | -  | 83 | -  | 20 | -     | -  | -  | 20 | 20 | -   | 37   |

|        | 110   | -  | -  | 39 | 55 | 43 | -  | 20 | -     | -  | -  | 20 | -  | -   | 37   |

|        | 111   | -  | -  | 19 | -  | 80 | -  | 19 | -     | -  | -  | 27 | 48 | 37  | 37   |

| Table 3 – LETth for all nodes of Mirror FA at Nomina | I Voltage ( $MeVcm^2/mg$ ). |

|------------------------------------------------------|-----------------------------|

|------------------------------------------------------|-----------------------------|

\*Robust results are indicated by (-) on the table, representing the cases where the LETth values are over 100*MeVcm<sup>2</sup>/mg*.

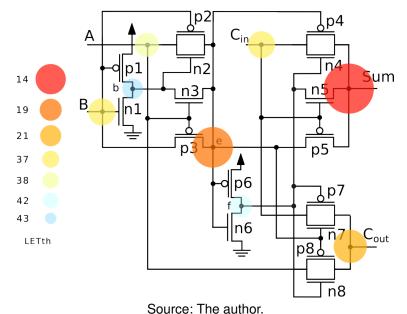

Turning our attention to the Hybrid FA, Table 4 reveals that nodes *c* and *d* stand out with the highest error rates. This consistency suggests that these nodes emerge as the most susceptible to error generation, experiencing significant disruptions under fault conditions. Together they represent approximately 20% of the total error occurrences observed at nominal voltage. Nodes *a*, *e*, *f*, *h*, *i*, *j*, *Sum* and *Cout* display moderate levels of sensitivity very similar to the critical ones, as indicated by their error rate, which is close to 9% each. These nodes are moderately susceptible to faults, with their performance affected to a noticeable extent. Node *Cin* consistently exhibits a robust performance across diverse fault propagation scenarios, as indicated by the absence of errors in the simulations. The consistent stability of *Cin* emphasizes its robust behavior against faults, highlighting its capacity to maintain functionality without notable disruptions. This resilience can be attributed to the signal path of *Cin* being

associated with either a pass transistor logic or a complementary logic circuit subpart, which effectively filters out potential SET error glitches.

In summary, nodes *c* and *d* emerge as the most sensitive components in the Hybrid FA topology, while nodes *a*, *e*, *f*, *h*, *i*, *j*, *Sum* and *Cout* exhibit similar degrees of sensitivity. Node *Cin* exhibits a sensitivity that is not context-dependent, demonstrating an absence of errors even across different pulse scenarios. This analysis provides insights into the robustness of each node in the Hybrid FA topology under worst-case fault propagation conditions. This insight into the error rate distribution provides a foundation for exploring targeted mitigation techniques, aiming to fortify these vulnerable nodes and enhance the overall robustness for this topology.

Table 4 – LETth for all nodes of Hybrid FA considering worst fault propagation at Nominal Voltage(*MeVcm*<sup>2</sup>/*mg*).

| Pulse | Input |    |    |    |    |    |    | Nomin | al |    |    |     |     |      |

|-------|-------|----|----|----|----|----|----|-------|----|----|----|-----|-----|------|

| Fuise | Input | а  | b  | С  | d  | е  | f  | g     | h  | i  | j  | Cin | Sum | Cout |

|       | 000   | 51 | -  | -  | -  | -  | -  | -     | -  | -  | -  | -   | 45  | 45   |

|       | 001   | 78 | -  | -  | -  | -  | -  | -     | -  | -  | 26 | -   | -   | 45   |

|       | 010   | -  | -  | -  | -  | -  | 29 | 62    | 59 | -  | 64 | -   | -   | 45   |

| 010   | 011   | -  | 96 | 26 | 26 | 27 | 25 | 66    | 47 | -  | -  | -   | 45  | -    |

|       | 100   | -  | 29 | -  | -  | -  | 30 | -     | 59 | 54 | 65 | -   | -   | 45   |

|       | 101   | -  | 25 | 26 | -  | 27 | 25 | -     | 47 | 69 | -  | -   | 45  | -    |