# UNIVERSIDADE FEDERAL DE SANTA CATARINA SANTA CATARINA CENTRO TECNOLÓGICO DE JOINVILLE PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA DE SISTEMAS ELETRÔNICOS

BRUNA ARRUDA ARAUJO

# ANALYSIS AND OPTIMIZATION OF CACHE-RELATED PARAMETERS FOR REAL-TIME SYSTEMS

# DISSERTATION OF DEGREE OF MASTER

Joinville 2023

Bruna Arruda Araujo

# ANALYSIS AND OPTIMIZATION OF CACHE-RELATED PARAMETERS FOR REAL-TIME SYSTEMS

Dissertation presented to Programa de Pós-Graduação em Engenharia de Sistemas Eletrônicos of Universidade Federal de Santa Catarina Santa Catarina in partial fulfillment of the requirements for the degree of Master in Eletronic Systems Engineering.

Supervisor:: Dr. Giovani Gracioli Co-supervisor:: Dr. Tomasz Kloda

Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

```

Araujo, Bruna

Analysis and Optimization of Cache-Related Parameters

for Real-time Systems / Bruna Araujo ; orientador, Giovani

Gracioli, coorientador, Tomasz Kloda, 2023.

114 p.

Dissertação (mestrado) - Universidade Federal de Santa

Catarina, Campus Joinville, Programa de Pós-Graduação em

```

Engenharia de Sistemas Eletrônicos, Joinville, 2023.

Inclui referências.

1. Engenharia de Sistemas Eletrônicos. 2. Cache optimization. 3. Real-time systems. 4. Cache replacement policies. I. Gracioli, Giovani. II. Kloda, Tomasz. III. Universidade Federal de Santa Catarina. Programa de Pós Graduação em Engenharia de Sistemas Eletrônicos. IV. Título. Bruna Arruda Araujo

# Analysis and Optimization of Cache-Related Parameters for Real-Time Systems

The present work in degree of Master was evaluated and approved by the committee composed by the following members:

Dr. Anderson Spengler PPGESE - Universidade Federal de Santa Catarina

Dr. Alex Sandro Roschildt Pinto PPGCC - Universidade Federal de Santa Catarina

We certify that this is the **original and final version** of the conclusion work that was deemed suitable for obtaining the title of Master in Eletronic Systems Engineering.

> Dr. Lucas Weihmann Program Coordinator

Dr. Giovani Gracioli Advisor

To those who are, in some way, my family.

### ACKNOWLEDGEMENTS

My heartfelt acknowledgments begin with my family. I want to express my gratitude to my parents, Adriane and Sandro, for their tireless dedication to me and my education. To my stepfather, Reginaldo, who has always treated me as a daughter and supported all my choices, encouraging me to go further. And to my stepmother, Laudeci, who has consistently aided my time away from home. I'd also like to extend my thanks to the Schnorr family, especially Jane, Paulo and Ezequiel, who welcomed me since my undergraduate years and became my pillar of support in various places.

A special thanks goes to my advisor, Giovani Gracioli, for providing me with such an engaging topic and for their unwavering patience during the completion of this work. I'd also like to express my gratitude to Tomasz Kloda, Dennis Hoornaert, Sergio Arribas and Lucas Santos for their immense contributions throughout the research. The academic and administrative support and the scientific environment at LISHA were pivotal in achieving the results of this thesis. Many thanks also to all my colleagues at LISHA.

I must also acknowledge some friends who played a crucial role during this period. Firstly, Vanessa Prediger, who was always ready to listen, share experiences, and assist me on countless occasions. I'd also like to extend my gratitude to individuals who were instrumental in helping me regain my self-confidence in the last year: Isaac Vianna, Renato Junk, Marcio Montibeler, Carmen Gaulke, Denis Dalpiaz, Éder Guber, Thais Musika, João Paulo Frotscher, Vivian Oliveira, Bianca Acuna, Johannes Sell and Manuela Rothbarth.

Finally, I'd like to thank the Federal University of Santa Catarina for enabling my academic journey. Last but not least, I'm deeply grateful to CAPES for their financial support during my years in the graduate program, which was essential for my life in Joinville.

" We ourselves feel that what we are doing is just a drop in the ocean. But the ocean would be less because of that missing drop. " (Mother Teresa of Calcutta, 1910 - 1997)

#### RESUMO

As memórias cache são fundamentais nos sistemas ciberfísicos contemporâneos devido às penalidades temporais incorridas por falhas da cache. Pesquisas anteriores se concentraram principalmente em políticas de substituição de linha e particionamento da cache em sistemas em tempo real para mitigar o impacto das falhas no Pior Tempo de Execução (*Worst Case Execution Time* - WCET).

Esta dissertação explora extensivamente várias políticas de substituição de linhas da cache em sistemas de tempo real, com o objetivo central de avaliar de forma abrangente o seu desempenho em termos de falhas e escalonabilidade – duas métricas cruciais na otimização de sistemas de tempo real. Os resultados da pesquisa confirmam que o tamanho da partição da cache e o número *ways* da cache exercem uma influência profunda no desempenho e na escalonabilidade da aplicação.

O impacto do tamanho da partição da cache nas políticas de substituição de linha é particularmente significativo. Os resultados experimentais ilustram que a modificação do tamanho da partição da cache pode levar a melhorias significativas no tempo de execução em aplicações específicas. Por exemplo, a aplicação pca-small obteve uma melhoria impressionante de 40% no tempo de execução com uma partição de 128 KB simplesmente alterando a política de substituição, destacando o papel crítico de otimizar políticas de substituição de linhas da cache e tamanhos de partição adaptados a tarefas específicas.

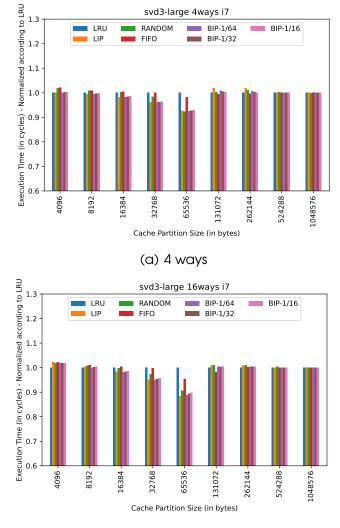

O número de formas da cache também desempenha um papel crucial nas políticas de substituição da cache. A transição de um número menor para um número maior de *ways* pode resultar em aumentos substanciais de desempenho em determinados cenários. Por exemplo, a aplicação svd3-large obteve uma melhoria de desempenho de aproximadamente 12% ao passar de quatro *ways* para 16 *ways*, atribuída principalmente à adoção da política LIP e de uma partição da cache de 64 KB. Essas observações enfatizam a influência significativa do número de *ways* da cache no comportamento e no desempenho da política de substituição de cache.

A escalonabilidade, uma consideração importante em sistemas de tempo real, é profundamente influenciada por essas otimizações da cache. Mesmo em cenários moderados de aceleração da cache, melhorias de escalonamento de até 5% podem ser alcançadas para casos não preemptivos. Em cenários com as maiores acelerações da cache, as melhorias na capacidade de escalonamento chegam a mais de 40% para casos não preemptivos em conjuntos de tarefas de alta utilização. A contribuição central da dissertação reside no desenvolvimento de um algoritmo projetado para otimizar a utilização e escalonabilidade da cache em sistemas de tempo real, alocando dinamicamente partições da cache. Este algoritmo supera consistentemente o algoritimo de particionamento da cache ideal (*Optimal Cache Partitioning Algorithm* - OCPA) alcançando ganhos de até 2%.

Concluindo, esta pesquisa ressalta a importância dos parâmetros da cache no aumento da previsibilidade, eficiência e desempenho geral em sistemas de tempo real, ao mesmo tempo em que destaca o potencial para melhorias substanciais na escalonabilidade. Essas descobertas estabelecem as bases para futuras explorações e inovações no campo da otimização da cache em sistemas de tempo real.

**Palavras-chave**: Otimização da cache, sistemas de tempo real, políticas de substituição de linhas da cache, particionamento da cache, previsibilidade, escalonabilidade.

# ABSTRACT

Cache memories are pivotal in contemporary cyber-physical systems due to the temporal penalties incurred from cache failures. Previous research has primarily focused on cache line replacement policies and cache partitioning in real-time systems to mitigate cache failures' impact on Worst Case Execution Time (WCET). However, the broader implications of cache parameters on these policies, especially in the context of cache partitions, have received limited attention.

This dissertation extensively explores various cache line replacement policies in real-time systems, with a central objective to comprehensively assess their performance in terms of cache misses and schedulability—two crucial metrics in optimizing real-time systems. The research findings confirm that cache partition size and the number of cache ways exert a profound influence on both application performance and schedulability.

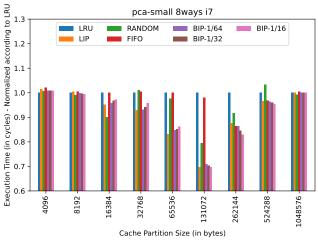

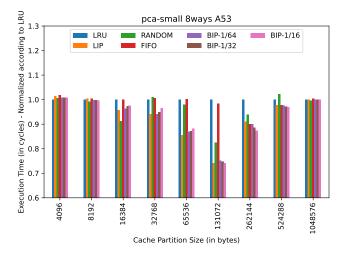

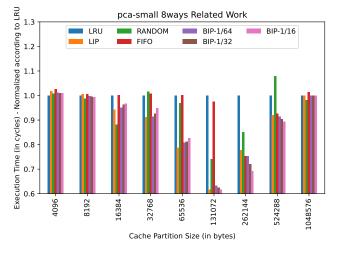

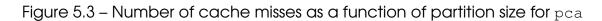

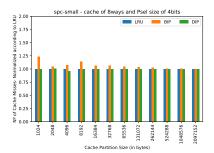

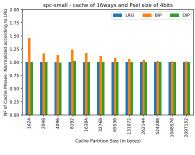

Cache partition size's impact on cache policies is particularly significant. Experimental results illustrate that modifying the cache partition size can lead to significant runtime improvements in specific applications. For instance, the pca-small application achieved an impressive 40% runtime improvement with a 128 KB cache partition simply by changing the replacement policy, highlighting the critical role of optimizing cache replacement policies and partition sizes tailored to specific tasks.

The number of cache ways also plays a crucial role in cache replacement policies. Transitioning from a lower to a higher number of cache ways can result in substantial performance boosts in certain scenarios. For example, the svd3-large application saw a performance improvement of approximately 12% when moving from four cache ways to 16 cache ways, primarily attributed to adopting the LIP policy and a 64 KB cache partition. These observations emphasize the significant influence of the number of cache ways on cache replacement policy behavior and performance.

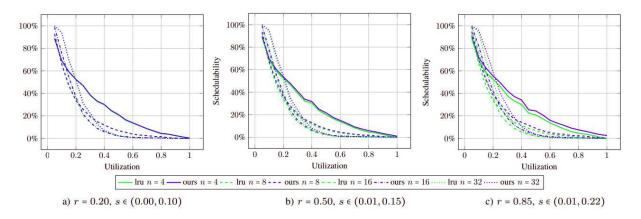

Schedulability, a key consideration in real-time systems, is profoundly influenced by these cache optimizations. Even under moderate cache acceleration scenarios, schedulability improvements of up to 5% can be achieved for nonpreemptive cases. In scenarios with the highest cache accelerations, schedulability improvements soar to over 40% for non-preemptive cases in high-utilization task sets.

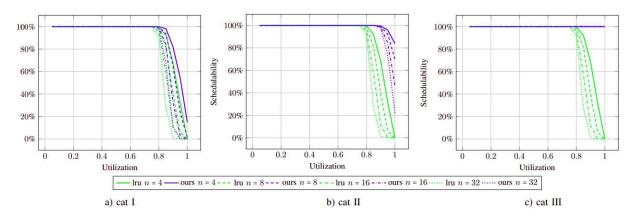

The dissertation's central contribution lies in the development of an algorithm designed to optimize cache utilization and schedulability in real-time systems by dynamically allocating cache partitions. This algorithm consistently outperforms the Optimal Cache Partitioning Algorithm (OCPA) achieving gains of up to 2%.

In conclusion, this research underscores the significance of cache parameters in enhancing predictability, efficiency, and overall performance in real-time systems while highlighting the potential for substantial schedulability improvements. These findings lay the foundation for future exploration and innovation in the field of cache optimization within real-time systems.

**Keywords**: Cache optimization, real-time systems, cache line replacement policies, cache partitioning, predictability, schedulability.

### **RESUMO EXPANDIDO**

### Introdução

Na era da Indústria 4.0 e da proliferação da Internet das Coisas (IoT), os Sistemas Ciberfísicos (CPS) tornaram-se a espinha dorsal das tecnologias modernas. Esses sistemas, também conhecidos como CPS críticos, são essenciais em setores cruciais, como aviação, energia nuclear, satélites, estações espaciais, veículos autônomos e cirurgia robótica. A evolução tecnológica trouxe um desafio significativo para esses sistemas: a crescente inteligência exigida, especialmente no contexto de Inteligência Artificial (IA). Contudo, essa complexidade crescente traz consigo um problema crítico: a previsibilidade limitada do comportamento dos CPS.

Nesse cenário, a memória cache, um componente central dos sistemas computacionais, desempenha um papel fundamental. As políticas de substituição de linha da cache têm um impacto direto na previsibilidade da cache, influenciando diretamente o Tempo de Execução do Pior Caso (WCET) e a capacidade de escalonamento dos sistemas em tempo real. Falhas de cache e as penalidades associadas podem causar sérios problemas, especialmente em sistemas críticos, onde a previsibilidade é essencial.

## Objetivos

O principal objetivo desta pesquisa é analisar e otimizar os parâmetros relacionados à cache, como tamanho da partição, número de ways, tamanho da linha da cache e a política de substituição para cada partição, a fim de aprimorar a capacidade de escalonamento de sistemas críticos em tempo real. Para alcançar esse objetivo abrangente, os seguintes objetivos específicos foram definidos: conduzir uma revisão bibliográfica abrangente das pesquisas relacionadas para reunir conhecimento no campo das políticas de substituição de linha da cache e seu impacto nos sistemas em tempo real. Além disso, avaliar o desempenho das políticas de substituição populares, incluindo LRU, FIFO, RANDOM, LIP e BIP, em termos de falhas da cache e escalonabilidade de tarefas em tempo real, usando um conjunto diversificado de benchmarks. A pesquisa também visa implementar e avaliar o desempenho da Política de Inserção Dinâmica (DIP) em um simulador de cache, especificamente cachegrind, para determinar sua eficácia na redução de falhas de cache. Além disso, investigar e analisar os efeitos de diferentes configurações da cache no desempenho das políticas de substituição de linha da cache, com foco em seu impacto nos sistemas críticos em tempo real. Por fim, desenvolver um algoritmo que otimize os parâmetros da cache e as políticas de substituição, considerando a abordagem de particionamento da

cache para tarefas em um sistema em tempo real. Ao abordar esses objetivos específicos, esta pesquisa visa contribuir para o avanço das técnicas de otimização da cache para sistemas críticos em tempo real, visando melhorar a escalonabilidade do sistema e o desempenho geral.

## Metodologia

Esta pesquisa adota uma abordagem sistemática para atingir seus objetivos. Inicialmente, é realizada uma revisão bibliográfica abrangente para estabelecer uma base teórica sólida. Em seguida, uma série de experimentos é conduzida, implementando e avaliando diversas políticas de substituição de linha da cache, como LRU, FIFO, RANDOM, LIP e BIP, usando benchmarks variados para representar cenários do mundo real.

Além disso, a eficácia da Política de Inserção Dinâmica (DIP) é analisada em um simulador de mémoria cache. Investigações detalhadas sobre diferentes configurações da cache são realizadas, com foco especial em seu impacto nos sistemas críticos de tempo real. Por fim, um algoritmo inovador é desenvolvido e testado em simulações controladas e cenários do mundo real para validar sua aplicabilidade.

## Resultados e Discussões

Os resultados experimentais destacaram a influência significativa do tamanho da partição de cache nas políticas de substituição de linha. Modificar o tamanho da partição da cache teve um impacto notável no tempo de execução de aplicações específicas. Por exemplo, a aplicação pca-small alcançou uma impressionante melhoria de 40% no tempo de execução com uma partição de cache de 128 KB, simplesmente alterando a política de substituição, evidenciando o papel crítico da otimização das políticas de substituição de linha de cache e dos tamanhos de partição adaptados a tarefas específicas. Além disso, o número de *ways* da cache também desempenhou um papel crucial nas políticas de substituição de linha. A transição de um número menor para um número maior de ways da cache resultou em aumentos substanciais de desempenho em cenários específicos. Por exemplo, a aplicação svd3-large obteve uma melhoria de desempenho de aproximadamente 12% ao passar de quatro para 16 vias da cache, atribuída principalmente à adoção da política LIP e a uma partição da cache de 64 KB. Essas observações enfatizam a influência significativa do número de ways da cache no comportamento e no desempenho da política de substituição de linhas da cache. A escalonabilidade, uma consideração crucial em sistemas em tempo real, foi profundamente influenciada por essas otimizações. Mesmo em cenários

moderados de aceleração da cache, melhorias de escalonabilidade de até 5% foram alcançadas para casos não preemptivos. Em cenários com as maiores acelerações, as melhorias na capacidade de escalonamento chegaram a mais de 40% para casos não preemptivos em conjuntos de tarefas de alta utilização.

A contribuição central da dissertação reside no desenvolvimento de um algoritmo projetado para otimizar a utilização e escalonabilidade da cache em sistemas em tempo real, alocando dinamicamente partições da cache. Este algoritmo supera consistentemente o algoritmo de particionamento da cache ideal (OCPA), alcançando ganhos de até 2%. Esses resultados reais validam a eficácia do algoritmo proposto, demonstrando melhorias tangíveis na previsibilidade e na capacidade de escalonamento dos sistemas em tempo real, estabelecendo assim um novo padrão na otimização de cache para esses ambientes críticos.

# **Considerações Finais**

Em resumo, esta pesquisa ressalta a influência fundamental dos parâmetros da cache na previsibilidade, eficiência e desempenho geral de sistemas de tempo real. Além disso, demonstra o potencial para melhorias substanciais na escalonabilidade. As percepções obtidas a partir dos estudos sobre partição da cache e minimização do uso da cache em sistemas em tempo real enriquecem ainda mais nossa compreensão das estratégias de gerenciamento da cache. Essas descobertas estabelecem as bases para futuras explorações e inovações no campo da otimização da cache em sistemas de tempo real.

**Palavras-Chaves**: Otimização da cache, sistemas de tempo real, políticas de substituição de linhas da cache, particionamento da cache, previsibilidade, escalonabilidade.

# LIST OF FIGURES

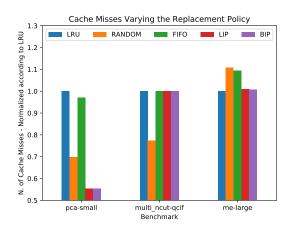

| Figure 1.1 –  | Number of cache misses from different benchmarks varying                                                     |     |

|---------------|--------------------------------------------------------------------------------------------------------------|-----|

|               | cache override policy. Normalized according to LRU. 128 KB                                                   |     |

|               | cache size with 8 ways                                                                                       | 31  |

| Figure 2.1 –  | Memory hierarchy structure.                                                                                  | 37  |

| Figure 2.2 –  | Multicore system architecture with dedicated L1 and L2                                                       |     |

|               | caches and shared LLC (L3)                                                                                   | 40  |

| Figure 2.3 –  | Direct mapping of a memory with 32 blocks into an eight-                                                     |     |

|               | word cache                                                                                                   | 42  |

| Figure 2.4 –  | Associative mapping of a block of main memory                                                                | 43  |

| Figure 2.5 –  | Associative mapping per set.                                                                                 | 44  |

| Figure 2.6 –  | $FIFO \text{ replacement policy.}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 47  |

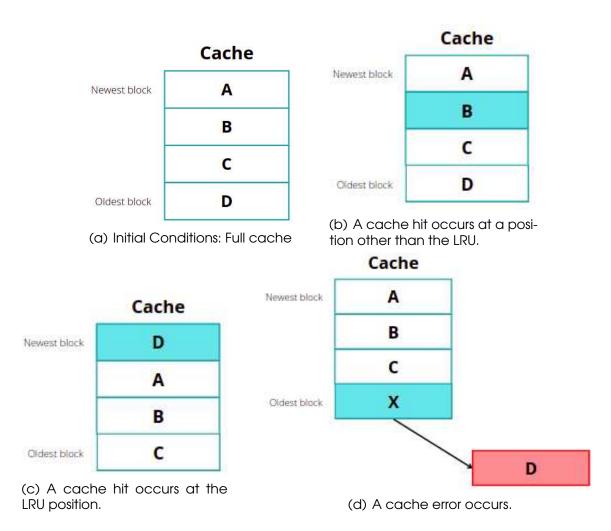

| Figure 2.7 –  | LRU replacement policy.                                                                                      | 48  |

| Figure 2.8 –  | How the PLRU policy works when a hit occurs                                                                  | 50  |

| Figure 2.9 –  | How the PLRU policy works when a cache miss occurs                                                           | 50  |

| Figure 2.10 – | LIP adaptive insertion policy                                                                                | 52  |

| Figure 4.1 –  | Impact of cache misses on execution time per processor,                                                      |     |

|               | varying the size of the cache partition in 8 ways                                                            | 78  |

| Figure 4.2 –  | Impact of number of ways on execution time, varying cache                                                    |     |

|               | partition size.                                                                                              | 79  |

| Figure 4.3 –  | Schedulability rate of non-preemptive fixed-priority algorithms.                                             | 81  |

| Figure 4.4 –  | Schedulability rate of preemptive fixed-priority algorithms                                                  | 81  |

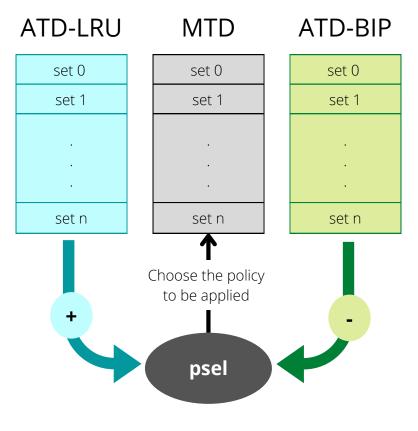

| Figure 5.1 –  | Global Mechanism of DIP                                                                                      | 84  |

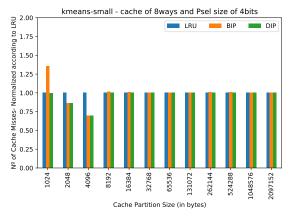

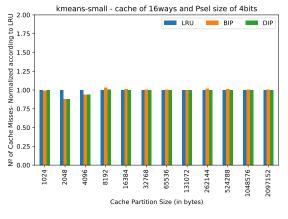

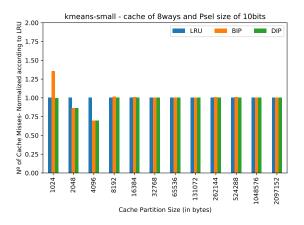

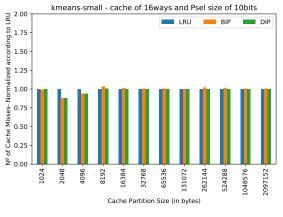

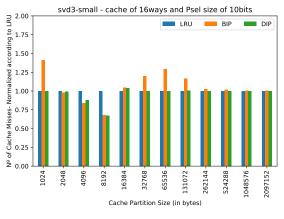

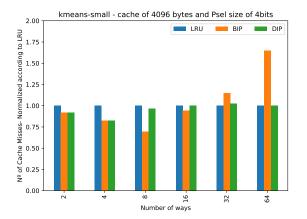

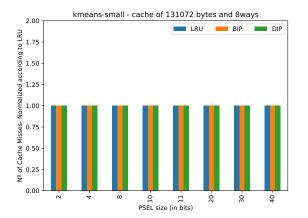

| Figure 5.2 –  | Number of cache misses as a function of partition size for                                                   |     |

|               | kmeans                                                                                                       | 88  |

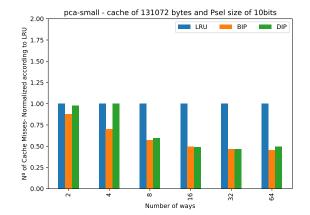

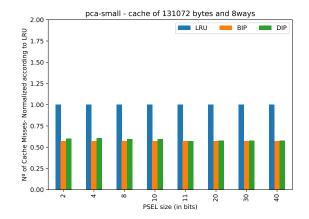

| Figure 5.3 –  | Number of cache misses as a function of partition size for ${\tt pca}$                                       | 89  |

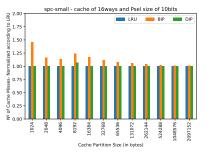

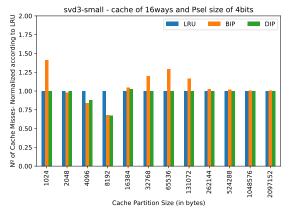

| Figure 5.4 –  | Number of cache misses as a function of partition size for ${\tt spc}$                                       | 89  |

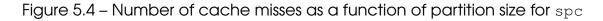

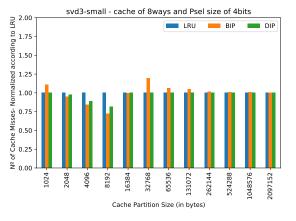

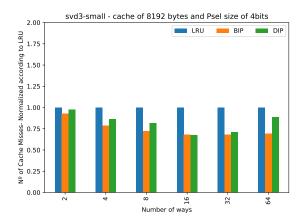

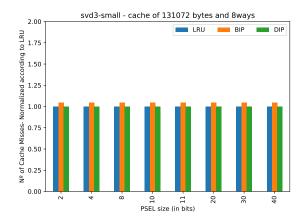

| Figure 5.5 –  | Number of cache misses as a function of partition size for ${\tt svd3}$                                      | 90  |

| Figure 5.6 –  | Number of cache misses as a function of the number of ways                                                   | 91  |

| Figure 5.7 –  | Variation of the value of <i>psel</i> during execution                                                       | 92  |

| Figure 5.8 –  | Number of cache misses as a function of the size of <i>psel</i>                                              | 93  |

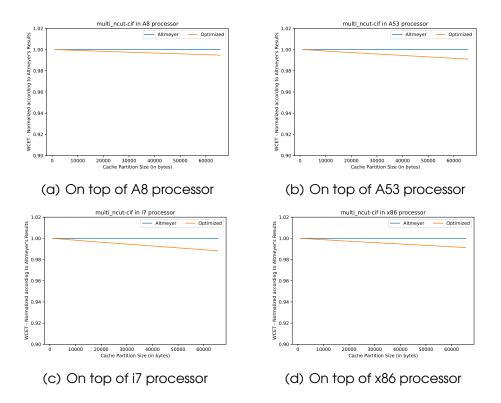

| Figure 6.1 –  | Relation of WCET and cache partition size for multi_ncut                                                     | 100 |

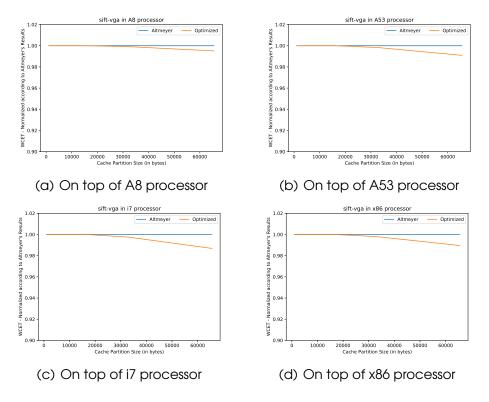

| Figure 6.2 –  | Relation of WCET and cache partition size for sift                                                           | 100 |

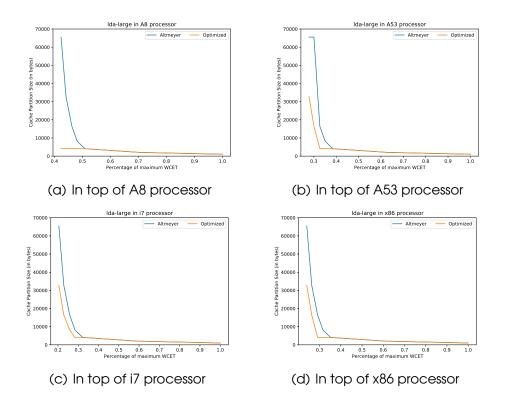

| Figure 6.3 –  | Relation of cache partition size and maximum WCET for ${\tt lda}$                                            | 101 |

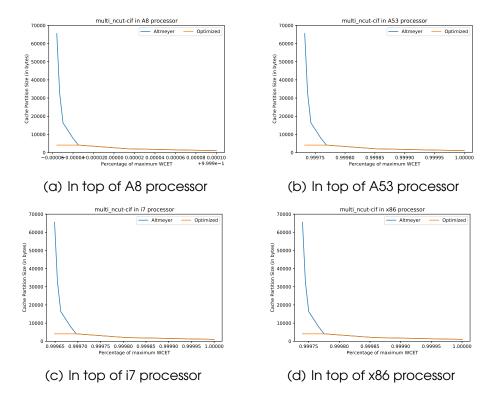

| Figure 6.4 –  | Relation of cache partition size and maximum WCET for lda.                                                   | 102 |

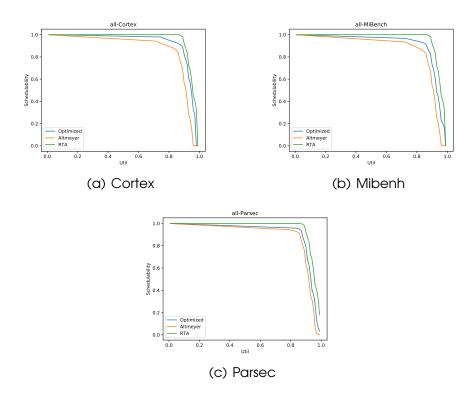

| Figure 6.5 –  | Schedulability analysis for all benchmarks.                                                                  | 103 |

# LIST OF TABLES

| Table 2.1 – Summary of notations related to periodic real-time task model | 56 |

|---------------------------------------------------------------------------|----|

| Table 4.1 – Benchmark categorization considering the percentage of        |    |

| cache misses                                                              | 76 |

| Table 4.2 – Parameters of the considered processors.                      | 76 |

| Table 4.3 – Parameters of schedulability experiments.                     | 80 |

| Table 5.1 – Benchmarks used in the experiments                            | 86 |

| Table 5.2 – Cache parameters applied in the experiments.                  | 87 |

| Table 6.1 – Benchmarks used in the experiments                            | 98 |

| Table 6.2 – Cache parameters applied in the experiments                   | 99 |

|                                                                           |    |

# LIST OF ABBERVIATIONS

| AI   | Artificial Inteligence               |

|------|--------------------------------------|

| BIP  | Bimodal Insertion Policy             |

| CPS  | Cyber-Physical System                |

| DIP  | Dynamic Insertion Policy             |

| DM   | Deadline Monotonic                   |

| EDF  | Earliest Deadline First              |

| FIFO | First-In First-Out                   |

| HD   | Hard Drive                           |

| HRT  | Hard Real-Time                       |

| loT  | Internet of Things                   |

| LIP  | LRU Insertion Policy                 |

| LLC  | Last Level of Cache                  |

| LRU  | Least Recently Used                  |

| MRU  | Most Recntly Used                    |

| OCPA | Optimal Cache Partitioning Algorithm |

| PLRU | Pseudo Least Recently Used           |

| RAM  | Random Access Memory                 |

| RM   | Rate Monotonic                       |

| RMS  | Rate Monotinic Server                |

| RTS  | Real-Time System                     |

| SoC  | System-on-Chip                       |

| SRT  | Soft Real-Time                       |

| UAV  | Unmanned Aerial Vehicles             |

| WCET | Worst Case Execution Time            |

# LIST OF SYMBOLS

- A task set au

- $T_i$

- $J_{i,j}$

- The  $i^{th}$  task of  $\tau$ The  $j^{th}$  job of the task  $T_i$ The execution time of  $T_i$  $e_i$

- $p_i$

- The period of  $T_i$ The relative deadline of  $T_i$ The relative deadline of  $T_i$  $d_i$

- $r_{i,j}$

# CONTENTS

| 1     |                                                  | 29 |

|-------|--------------------------------------------------|----|

| 1.1   | PROBLEM OVERVIEW                                 | 31 |

| 1.2   | GOALS                                            | 33 |

| 1.3   |                                                  | 34 |

| 2     | BACKGROUND                                       | 35 |

| 2.1   |                                                  | 35 |

| 2.1.  | 1 Memory Hierarchy                               | 36 |

| 2.1.  | 2 Temporal and Spatial Locality                  | 37 |

| 2.1.  | 3 Cache Memory Organization                      | 38 |

| 2.1.3 | 3.1 Levels of Cache Memory                       | 39 |

| 2.1.3 | 3.2 Performance                                  | 40 |

| 2.1.3 | 3.3 Mapping                                      | 41 |

| 2.1.3 | 3.4 Cache Partitioning                           | 44 |

| 2.1.4 | 4 Cache Replacement Policies                     | 45 |

| 2.1.4 | 4.1 RANDOM                                       | 45 |

| 2.1.4 | 4.2 First-In, First-Out (FIFO)                   | 46 |

| 2.1.4 | 4.3 Lest Recently Used (LRU)                     | 46 |

| 2.1.4 | 4.4 Pseudo-LRU (PLRU)                            | 49 |

| 2.1.  | 5 Adaptive Insertion Policies                    | 49 |

| 2.1.  | 5.1 LRU Insertion Policy (LIP)                   | 51 |

| 2.1.  | 5.2 Bimodal Insertion Policy (BIP)               | 51 |

| 2.1.  | 5.3 Dynamic Insertion Policy (DIP)               | 53 |

| 2.2   | REAL-TIME SYSTEM                                 | 53 |

| 2.2.  | 1 Real-Time Systems Classification               | 55 |

| 2.2.2 | 2 Notations Definitions and Task Models          | 55 |

| 2.2.  | 3 Real-Time Scheduling Algorithm                 | 56 |

| 2.2.3 | 3.1 Fixed-Priority Scheduling                    | 58 |

| 2.2.3 | 3.2 Dynamic-Priority Scheduling                  | 59 |

| 2.2.3 | 3.3 Resource Reservation-based Scheduling        | 61 |

| 2.2.4 | 4 Real-Time Systems and Cache-Related Parameters | 61 |

| 2.3   | SUMMARY                                          | 62 |

| 3     | RELATED WORK                                     | 65 |

| 3.1   | CACHE REPLACEMENT POLICIES FOR REAL TIME SYSTEMS | 65 |

| 3.2   | CACHE PARTITIONING                               | 68 |

| 3.3   | SCRATCHPAD MEMORIES IN HARD REAL-TIME SYSTEMS    | 69 |

| 3.4   | PARTIAL CONSIDERATIONS                           | 71 |

| 4     | EVALUATION OF CACHE REPLACEMENT POLICIES         | 73 |

| 4.1    | CACHEGRIND: PROFILING CACHE BEHAVIOR IN DYNAMIC ANALYSIS .    | 73  |

|--------|---------------------------------------------------------------|-----|

| 4.2    | CATEGORIZATION OF BENCHMARKS AND EVALUATION OF REPLACE-       |     |

|        |                                                               | 74  |

| 4.3    | SCHEDULABILITY IMPACT ASSESSMENT                              | 77  |

| 4.4    | PARTIAL CONSIDERATIONS                                        | 81  |

| 5 II   | MPLEMENTATION AND EVALUATION OF THE DIP POLICY IN CACHEGRIND  | 83  |

| 5.1    | IMPLEMENTATION OF DIP                                         | 83  |

| 5.2    | PARAMETERS OF EXPERIMENTS                                     | 86  |

| 5.3    | ASSESSMENT OF THE DIP POLICY IMPLEMENTED IN CACHEGRIND        | 86  |

| 5.4    | PARTIAL CONSIDERATIONS                                        | 91  |

| 6 (    |                                                               | 95  |

| 6.1    | OVERVIEW OF OPTIMAL CACHE PARTITION ALGORITHM                 | 96  |

| 6.2    | THE PROPOSED ALGORITHM                                        | 96  |

| 6.3    | EXPERIMENTAL COMPARISON                                       | 98  |

| 6.3.1  | First Experiment: WCET x Cache Partition Size                 | 99  |

| 6.3.2  | Second Experiment: cache partition size x maximum WCET        | 101 |

| 6.3.3  | Third Experiment: Schedulability                              | 101 |

| 6.4    |                                                               | 103 |

| 7 (    |                                                               | 105 |

| 7.1    |                                                               | 105 |

| 7.1.1  | Evaluation of Cache Replacement Policies                      | 105 |

| 7.1.2  | Implementation and Evaluation of the DIP Policy in Cachegrind | 106 |

| 7.1.3  |                                                               | 106 |

| 7.2    | CLOSING REMARKS                                               | 107 |

| 7.3    |                                                               | 108 |

| BIBLIC | OGRAPHY                                                       | 109 |

### **1 INTRODUCTION**

In the era of Industry 4.0 and the widespread adoption of the Internet of Things (IoT), Cyber-Physical Systems (CPS) have become increasingly prevalent in modern society. These systems, known as hard CPS, are characterized by their strict constraints on predictability and confidentiality (AYDIN; JOHANS-SON; SASTRY, 2018). They find extensive application in critical domains such as avionics systems, supervisory systems for nuclear power plants, satellite orbit controllers, life support devices in space stations, unmanned aerial vehicles (UAVs), flight controllers, surgeon-machine interfaces in robotic surgery devices, and autonomous vehicles, among others.

As technology advances, CPS is entering a new phase with high expectations for their capabilities, particularly in the realm of artificial intelligence (Al). Modern CPS are becoming more intelligent, which demands greater computational power and increased complexity in both software and hardware. However, this complexity comes at a cost — a fundamental lack of predictability in CPS behavior has emerged as a significant challenge. (LIU, 2000; BUTTAZZO, 2011; GRACIOLI et al., 2019)

To improve system performance in typical scenarios, hardware designers have adopted various techniques such as caches, multilevel and superscalar pipelines, and prefetchers. While these techniques have demonstrated performance enhancements, they have also introduced variability in instruction execution times due to potential accidents and associated time penalties (REINEKE et al., 2007). Among these hardware components, cache memory architecture plays a pivotal role in determining medium and worst-case performance, primarily due to the substantial penalties associated with cache misses (GRA-CIOLI et al., 2015). In cases where a cache line needs to be replaced and returned to the main memory before being filled, cache misses can result in cycles exceeding 50 or more, presenting a hundredfold increase compared to cache hits (Liedtke; Hartig; Hohmuth, 1997). Several properties of cache memories, including associativity and replacement policies, significantly influence predictability, with the replacement policy emerging as one of the key factors impacting cache memory behavior predictability. (Heckmann et al., 2003)

Traditionally, the Least Recently Used (LRU) policy and its approximations have been the preferred choice for line replacement policies in processor chip caches for several decades (QURESHI et al., 2006; MANCUSO; YUN; PUAUT, 2019). While LRU performs well in workloads with high locality, it can exhibit pathological behavior when confronted with high memory demands that surpass the available cache size (QURESHI et al., 2007). In cases where a real-time application's working set slightly exceeds the cache size, alternative policies such as RANDOM may experience fewer cache misses compared to LRU (AL-ZOUBI; MILENKOVIC; MILENKOVIC, 2004; REINEKE et al., 2007; QURESHI; SRINIVASAN; RIVERS, 2007).

The diverse range of critical modern real-time systems mentioned earlier exhibits varying and often conflicting memory requirements (GRACIOLI et al., 2019). For instance, in autonomous vehicles, simple control tasks like airbags and ABS braking systems have low memory demands, while more complex tasks like pedestrian detection and sensory fusion necessitate substantial processing power and memory resources. In such scenarios, each task's performance can be maximized by selecting the most appropriate cache line replacement policy—one that minimizes cache misses—for each specific case. The integration of a cache architecture with a partitioning mechanism, isolating individual tasks at the cache level (GRACIOLI et al., 2015), and dynamically selecting the most suitable replacement policy within each partition holds the potential to reduce the system's worst-case execution time (WCET) and increase schedulability.

Several research studies have explored the benefits of varying cache line replacement policies. Quereshi et al. introduced the Bimodal Insertion Policy (BIP) as an alternative to LRU, demonstrating its superior performance. They further proposed the Dynamic Insertion Policy (DIP), which dynamically selects between BIP and LRU based on the lowest number of cache misses for a given task, resulting in a 21% reduction in cache misses compared to the secondbest policy (QURESHI et al., 2007). Subramanian, Smaragdakis, and Loh (2006) proposed a hybrid cache line replacement scheme that dynamically selects between LRU and other policies in hardware without software interference (SUB-RAMANIAN; SMARAGDAKIS; LOH, 2006). Mancuso, Yun, and Puaut (2019) introduced DM-LRU (Deterministic Memory - Least Recently Used), applying LRU to deterministic-classified memory regions evaluated through a simulated environment (MANCUSO; YUN; PUAUT, 2019). The DIP policy (QURESHI et al., 2007) opened the door to dynamic approaches for selecting the best cache line replacement policy at runtime (QURESHI et al., 2007).

Additionally, the papers by (ALTMEYER et al., 2014) and (SUN et al., 2023) have made significant contributions to the field. These studies have investigated cache partitioning techniques and cache usage optimization in the context of real-time systems. By applying fixed-priority scheduling and cache partitioning, these papers address the challenges of ensuring mixed-criticality tasks meet their timing requirements while efficiently utilizing cache resources. The outcomes of these studies provide valuable insights into cache management strategies for real-time systems, complementing the research efforts in cache line replacement policy optimization.

Building upon these foundations, the present research aims to address the challenge of optimizing cache line replacement policies and configuration parameters for different tasks in real-time CPS. We propose a novel algorithm that systematically explores the design space to determine the optimal cache settings for each task, taking into account their specific memory requirements and performance objectives. Leveraging the cache partitioning mechanism, our algorithm dynamically selects the most appropriate replacement policy within each partition, with the primary objective of reducing WCET and enhancing the system's schedulability.

In summary, this dissertation aims to bridge the existing gap in the literature by providing an algorithm that explores the design space to determine optimal cache settings for each task in critical CPS. By optimizing cache line replacement policies and configuration parameters, our research endeavors to improve predictability, reduce WCET, and enhance the schedulability of these critical systems. The insights gained from the studies on cache partitioning and cache usage minimization in real-time systems further enrich our understanding of cache management strategies.

### 1.1 PROBLEM OVERVIEW

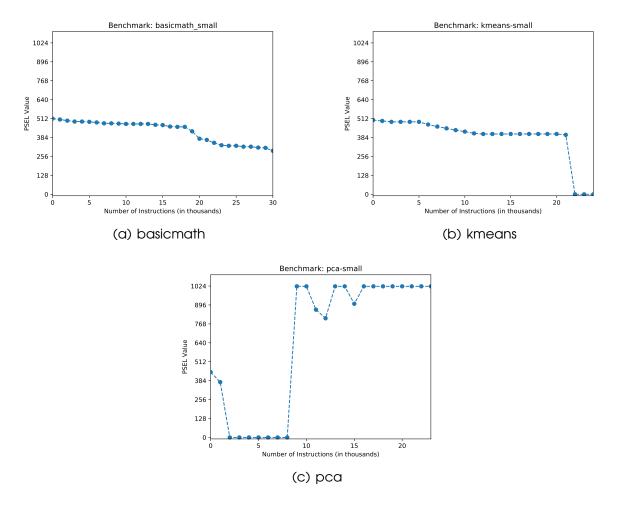

Tasks and algorithms exhibit different memory access patterns depending on the organization of their data. However, modern caches typically have a single line replacement policy predetermined during the System-on-Chip (SoC) design phase. This one-size-fits-all policy is often determined based on average performance metrics. However, as depicted in Figure 1.1, independent tasks demonstrate varying behavior depending on the chosen replacement policy.

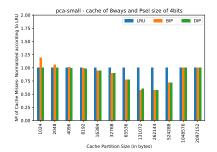

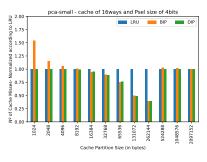

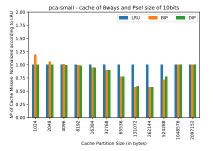

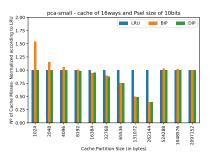

Figure 1.1 – Number of cache misses from different benchmarks varying cache override policy. Normalized according to LRU. 128 KB cache size with 8 ways. Figure 1.1 showcases the cache miss counts for five different cache line replacement policies (LRU, RANDOM, FIFO - First-In First-Out, LIP - LRU Insertion Policy and BIP) obtained by running three benchmarks from the Cortex Benchmark Suite (THOMAS et al., 2014) on top of cachegrind, a cache profiling tool. The cache configuration used in this scenario includes a size of 128 KB, 8 ways, and a cache line of 64 bytes. The results are normalized with respect to LRU performance, meaning that a bar lower than the LRU bar indicates fewer cache misses for that policy.

For instance, the pca benchmark exhibits significantly fewer cache misses under the RANDOM, LIP, and BIP policies compared to LRU and FIFO. However, when running the me benchmark, these policies result in a higher number of cache misses compared to LRU. Figure 1.1 demonstrates that in this case, the LRU policy is preferable. Even the performance benefits offered by each policy may vary depending on the benchmark. This is evident in the multi\_ncut-qcif benchmark, where RANDOM is the only policy with better performance than LRU, albeit with a smaller gain than in the pca benchmark.

This example, while simple, highlights the sub-optimality of selecting a single line replacement policy for all cases, as it can lead to increased task execution time. Therefore, it is believed that a unique and flexible architecture, allowing the selection of the replacement policy per task, as well as a mechanism for choosing the best cache parameters, can reduce the execution time of each task and improve the schedulability of the entire system.

In a recent collaboration between the Laboratory of Software/Hardware Integration (LISHA) at UFSC and the cyber-physical systems group at the Technical University of Munich, Germany, a modular and configurable cache architecture was proposed for a RISC-V processor (HOORNAERT et al., 2021). This architecture enables cache partitioning on a per-task basis and the application of different line replacement policies within each partition. Additionally, it allows the selection of cache parameters, such as line length and the number of ways, at compile time. However, existing literature lacks a mechanism that chooses the best cache configuration parameters for each real-time task.

The absence of a mechanism for selecting the optimal cache configuration parameters hinders the full potential of cache performance optimization in real-time systems. Addressing this gap is the objective of the present research, aiming to provide a solution that determines the most suitable cache configuration parameters for each real-time task, considering their unique memory requirements and performance goals. By integrating this mechanism with the modular and configurable cache architecture, we strive to enhance the overall efficiency and schedulability of real-time systems.

# 1.2 GOALS

Cache line replacement policies play a critical role in ensuring cache predictability and complying with time constraints, as cache misses and miss penalties significantly impact system performance. However, the effectiveness of each policy varies depending on the specific task it is applied to. Therefore, a cache architecture that allows the selection of the most suitable policy at runtime, resulting in fewer cache misses, can greatly improve worst-case execution time (WCET) and schedulability in critical real-time systems.

The main objective of this research is to analyze and optimize cacherelated parameters, such as partition size, number of ways, cache line size, and the replacement policy for each partition, in order to enhance the schedulability of critical real-time systems. To achieve this overarching objective, the following specific objectives have been defined:

- 1. Conduct a comprehensive literature review of related works to gather insights and knowledge in the field of cache line replacement policies and their impact on real-time systems.

- 2. Evaluate the performance of popular cache line replacement policies, namely LRU, FIFO, RANDOM, LIP, and BIP, in terms of cache misses and the scalability of real-time tasks using a diverse set of benchmarks.

- 3. Implement and assess the performance of the Dynamic Insertion Policy (DIP) in a cache simulator, specifically cachegrind, to determine its effectiveness in reducing cache misses.

- 4. Investigate and analyze the effects of different cache settings on the performance of cache line replacement policies, with a focus on their impact on critical real-time systems.

- 5. Develop an algorithm that optimizes cache parameters and replacement policies, considering the cache partitioning approach for tasks in a realtime system.

By addressing these specific objectives, this research aims to contribute to the advancement of cache optimization techniques for critical real-time systems. The ultimate goal is to propose an algorithm that selects the most suitable cache parameters and replacement policies for each task, considering their individual requirements, in order to improve system schedulability and overall performance.

#### 1.3 DOCUMENT ORGANIZATION

The remainder of this document is structured as follows:

**Chapter 2** provides the necessary theoretical background for the development of this research. It covers key concepts and metrics related to cache memory organization and performance 2.1.3, as well as the definition, classification, and mechanisms of Real-Time Systems 2.2.

In **Chapter 3**, a comprehensive survey is conducted on relevant works in the field that align with the scope of this research. This chapter is divided into three main topics: Cache Partitioning Mechanisms 3.2, Cache Line Replacement Policies for Real-Time Systems 3.1, and Memories Scratchpads 3.3.

**Chapter 4** focuses on analyzing the impact of different cache line replacement policies, namely LRU, FIFO, RANDOM, LIP, and BIP, in terms of cache misses and the schedulability of real-time tasks. This analysis is performed using a set of benchmarks on a cache architecture that supports per-task partitioning.

In **Chapter 5**, the Dynamic Insertion Policy (DIP) mechanism implemented in the cachegrind simulator is presented. This chapter discusses the simulations conducted, the benchmarks utilized, and provides a detailed discussion of the obtained results.

**Chapter 6** introduces an algorithm inspired at (ALTMEYER et al., 2014). The proposed algorithm aims to select the optimal cache line replacement policy for task partitioned caches. The evaluation of this algorithm involves comparing the reduction of WCET, improvement of partition costs, and enhancement of schedulability.

Finally, **Chapter 7** concludes the research, summarizing the main findings, discussing their implications, and highlighting potential avenues for future work in this field.

# 2 BACKGROUND

This chapter provides a concise overview of the essential background knowledge required for this research. It begins by presenting the fundamental concepts of memory architecture, hierarchy and performance. This includes an exploration of cache memory and its role in improving system performance by reducing memory access latency. The chapter specifically focuses on cache line replacement policies and their behaviors in different scenarios. The aim is to understand how these policies impact cache performance and predictability.

The next section delves into the Real-Time Systems (RTS). It discusses the definition and classification of RTS and highlights their unique characteristics and requirements. The chapter examines the challenges and considerations involved in designing and analyzing RTS, such as meeting strict timing constraints and ensuring deterministic behavior.

By providing this foundational knowledge, the chapter sets the stage for the subsequent chapters, which explore cache partitioning mechanisms, cache line replacement policies for real-time systems, and other related topics. This background understanding is crucial for comprehending the research's objectives and methodology, and for grasping the significance of the findings and recommendations presented throughout the document.

## 2.1 MEMORY ARCHITECTURE

Over the years, computer systems have made significant advancements, particularly in the field of processors, leading to improved efficiency. However, the same level of progress has not been achieved in memory technology, especially concerning speed (PATTERSON; HENNESSY, 2013). This discrepancy has resulted in a performance gap, where high-speed processors encounter delays when accessing and transferring data to or from main memory.

As computerized systems are applied to increasingly complex projects, the demands for memory performance and size have also grown. This has led to the emergence of different memory specifications with varying construction technologies, often associated with higher production costs (STALLINGS, 2009). These memory-related requirements pose complex challenges in the design of practical systems. While larger and faster memory may be desired, the cost implications must also be taken into account (TANENBAUM, 2006).

Consequently, the development of a memory hierarchy has become imperative. This hierarchy employs multiple components or technologies to meet the diverse performance needs of systems (HENNESSY; PATTERSON, 2011).

This section provides an overview of the memory hierarchy, with a spe-

cific focus on cache memory and cache replacement policies. Understanding these concepts is essential for the development of this research. The memory hierarchy plays a crucial role in bridging the speed gap between processors and main memory, improving overall system performance. Cache memory, as a key component of the memory hierarchy, operates as a high-speed buffer between the processor and main memory, storing frequently accessed data to minimize access latency. Cache replacement policies determine which cache lines are evicted when new data is fetched, and different policies exhibit varying behaviors in different scenarios. A comprehensive understanding of these concepts is necessary for investigating cache partitioning mechanisms and optimizing cache parameters to enhance the schedulability of real-time systems.

#### 2.1.1 Memory Hierarchy

In 1946, Arthur Burks, Herman Goldstine and John von Neumann published preliminary discussions on the logical design of an electronic computing instrument. Even at that early stage, they recognized the critical role of memory capacity in the design of general-purpose systems and concluded that the use of different types of memories to meet varying usage demands was becoming increasingly necessary (BURKS; GOLDSTINE; NEUMANN, 1946).

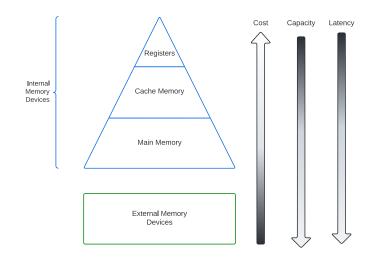

The memory hierarchy was subsequently devised as a mechanism to address system resource requirements by incorporating memory levels, each of which is smaller, faster, and more expensive than the next level, moving farther away from the processor. Figure 2.1 illustrates the organization of the memory hierarchy. At the top of the hierarchy, within the triangle, are the registers and caches, which are implemented in closer proximity to the processor. Below the triangle, in the box, are external memory devices such as USB drives and hard disks (HD). As we move up the hierarchy, the devices take less time to access information (lower latency), but they come at a higher cost and offer a smaller storage capacity. Conversely, devices lower in the memory hierarchy are more cost-effective, provide larger storage capacity, but exhibit higher latency.

The memory hierarchy's goal is to optimize the overall performance of computer systems by strategically utilizing different memory levels. The registers, which are the fastest and most expensive memory units, are located directly within the processor and provide rapid access to data. Caches, which are smaller and faster than main memory, serve as intermediate storage between the registers and the main memory. Caches aim to store frequently accessed data to minimize the latency associated with accessing data from the larger and slower main memory. Main memory, also known as RAM (Random Access Memory), serves as a larger storage unit but has a higher latency compared

Figure 2.1 – Memory hierarchy structure. Adapted from (STALLINGS, 2009)

to caches. External memory devices, such as pen drives and external HDs, are even larger in capacity but come with longer access times.

By employing the memory hierarchy, computer systems can optimize the use of resources, balancing speed, capacity, and cost, to deliver efficient and cost-effective performance. The hierarchical arrangement ensures that frequently accessed data is readily available in the faster memory levels, reducing the overall latency of memory operations.

# 2.1.2 Temporal and Spatial Locality

In the 1960s, IBM researchers made a significant discovery that revolutionized computer performance. They observed that a large portion of code exhibits repetitive patterns, which can be leveraged to enhance system efficiency. By storing frequently accessed sections of code in a small, high-speed memory, the impact of wait states can be minimized, relegating slower and less expensive memory to the less repetitive parts of the program (HANDY, 1998). This principle forms the basis of cache memory operation, which will be discussed in detail in Section 2.1.3. The concept of code repetition can be viewed from two perspectives: time locality and spatial locality.

**Time locality**, also known as temporal locality, refers to the tendency of instructions or data to be accessed in close temporal proximity. In other words, recently accessed memory locations are more likely to be accessed again in the near future, compared to those accessed a long time ago. For example, a processor is more likely to revisit a memory location accessed ten cycles ago rather than one accessed ten thousand cycles ago. Exploiting time locality allows for efficient caching and reduces the latency associated with memory

accesses (HANDY, 1998).

**Spatial locality**, on the other hand, relates to the observation that computer code frequently executes within a small area of memory. This area is not necessarily confined to a single range of main memory addresses; it can be distributed throughout the memory system. In simpler terms, if a particular memory location is accessed, it is highly likely that data stored in nearby memory locations will also be accessed in the near future. By capitalizing on spatial locality, cache systems can prefetch and store adjacent data, reducing the time needed to retrieve it when required (HANDY, 1998).

Both time and spatial locality are fundamental properties of program execution that can significantly impact memory access patterns. Caching mechanisms exploit these locality principles to deliver faster access times and improved overall system performance. By storing frequently used instructions and data closer to the processor, caches minimize the latency associated with retrieving information from slower, larger, and more distant memory levels.

#### 2.1.3 Cache Memory Organization

Cache memories are specialized high-speed storage devices that play a crucial role in improving data transfer between the processor and main memory, as well as other cache levels (JACOB; WANG; NG, 2010). The primary objective of a cache is to enhance system performance by exploiting the principle of temporal locality. By storing recently accessed data, the cache enables quick retrieval when the processor requires it. As a result, the processor first checks the cache for the requested data, and only if it is not found there, does it search for the data in the main memory. By keeping a significant portion of frequently used data in the cache, the average access time can be substantially reduced (TANENBAUM, 2006).

The cache operates based on the principle of a memory hierarchy, as discussed earlier. It consists of a hierarchy of cache levels, with each level being closer to the processor and faster but smaller compared to the levels below it. The cache works by dividing memory into fixed-size blocks, known as cache lines or cache blocks, which are used as the basic unit of data transfer between the cache and main memory. When the processor requests data, the cache checks if the desired data is present in one of its cache lines. If a cache hit occurs, indicating that the data is already in the cache, it is quickly accessed and provided to the processor. On the other hand, if a cache miss occurs, meaning the data is not present in the cache, the cache needs to retrieve the data from the main memory, resulting in higher latency (JACOB; WANG; NG, 2010).

The efficiency of a cache memory is determined by its hit rate, which represents the percentage of data accesses that result in a cache hit. A higher hit rate indicates better cache utilization and overall system performance. Caches employ various techniques, such as associative mapping and replacement policies, to manage the cache lines and optimize the hit rate. These techniques ensure that the most frequently accessed data is retained in the cache, while less frequently used data is replaced to make room for new data (TANENBAUM, 2006).

In summary, cache memories act as high-speed intermediaries between the processor and main memory, leveraging temporal locality to store recently accessed data and minimize the latency associated with accessing the slower main memory. By keeping frequently used data closer to the processor, caches enhance overall system performance and reduce average access times.

### 2.1.3.1 Levels of Cache Memory

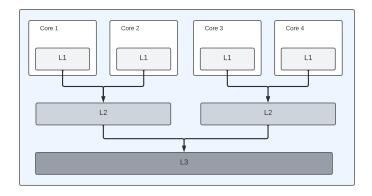

Multilevel caches have become commonplace in modern computer systems to optimize data transfer and improve performance. The cache hierarchy typically consists of three levels: L1, L2, and LLC (Last Level of Cache), each with different capacities and characteristics (STALLINGS, 2009).

The L1 cache, also known as the primary cache, is the fastest but smallest cache level. It is usually integrated into the processor chip and divided into separate data and instruction caches. The L1 cache stores frequently accessed data and instructions to provide quick access for the CPU. Different processors have different sizes of L1 cache, ranging from 8 KB in early Intel processors like the i486 to larger sizes like 32 KB in Intel i7 and even 64 KB in ARM Cortex-A53.

To compensate for the limited capacity of the L1 cache, the L2 cache, or secondary cache, was introduced. The L2 cache has a larger storage capacity compared to the L1 cache. It acts as an intermediary between the L1 cache and the main memory, storing additional data to reduce the need for accessing the slower main memory. The size of the L2 cache varies depending on the processor architecture. For example, Intel i7 processors provide an L2 cache of 256 KB, while ARM processors offer configurable L2 cache sizes of up to 2 MB.

In some systems, an additional cache level, LLC, is implemented. The LLC is a specialized memory designed to improve the performance of the previous cache levels. It serves as a buffer between the processor cores and the main memory, helping to mask the latency associated with main memory access. The LLC is typically larger than the L2 cache and has a significant impact on overall system runtime performance. Its size and configuration vary depending on the specific system design and requirements.

In multicore processors, each core may have its dedicated L1 cache integrated into the processor chip. However, the higher-level caches, such as L2 and LLC, are often shared among multiple cores. To ensure efficient data transfer, these shared caches are connected to the CPU through high-speed alternate system buses, separate from the main system bus. This design allows the shared caches to handle cache traffic without being affected by congestion on the main bus.

Figure 2.2 provides an illustration of a possible memory configuration in a multicore system with four cores and a three-level cache hierarchy. Each core has its dedicated L1 cache. The L2 cache levels are shared, with cores 1 and 2 sharing one L2 cache and cores 3 and 4 sharing the other. Finally, there is an external LLC cache that is shared among all the cores, in this example the LLC is shown as a third level L3. This configuration demonstrates the hierarchical structure of cache memory in a multicore system.

Overall, the multilevel cache architecture with dedicated and shared caches improves system performance by reducing the latency associated with main memory access and providing fast data retrieval for the processor cores.

Figure 2.2 – Multicore system architecture with dedicated L1 and L2 caches and shared LLC (L3).

Source: Adapted from (STALLINGS, 2009)

### 2.1.3.2 Performance

The performance of cache memory can be evaluated based on two key metrics: cache hit ratio and cache miss ratio. Additionally, the miss penalty is another important factor to consider.

A cache hit occurs when the processor successfully finds the required data in the cache. It indicates that the cache memory is functioning effectively, allowing for fast access to frequently accessed data. On the other hand, a cache miss happens when the required data is not found in the cache. In such cases, the cache needs to fetch the required block from the main memory, resulting in increased latency and performance degradation.

To assess cache performance, two ratios are commonly used:

- Hit ratio: This is the ratio between the number of cache hits and the total number of cache accesses. It provides a measure of how often the cache is able to satisfy data requests without accessing the main memory. A higher hit ratio indicates a more efficient cache, as a larger proportion of data requests are fulfilled from the cache itself (HENNESSY; PATTERSON, 2011).

- 2. Miss ratio: This is the ratio between the number of cache misses and the total number of cache accesses. It represents the frequency at which the cache fails to find the required data and needs to fetch it from the main memory. A lower miss ratio indicates better cache performance, as fewer cache accesses result in cache misses (HENNESSY; PATTERSON, 2011).

In addition to hit and miss ratios, the miss penalty is a critical factor in cache performance evaluation. The miss penalty refers to the cost incurred when a cache miss occurs and a cache line needs to be replaced. It includes the time taken to retrieve the required block from the main memory and the subsequent cache line replacement. Minimizing the miss penalty is crucial for improving cache efficiency and reducing overall system latency (PATTERSON; HENNESSY, 2013).

By analyzing the hit ratio, miss ratio, and miss penalty, the performance of a cache can be evaluated, and appropriate optimizations can be applied to enhance cache efficiency and reduce access latency.

# 2.1.3.3 Mapping

Cache mapping determines the mapping scheme used to allocate memory blocks from the main memory to cache lines. It defines how the cache index is computed from the memory address and how cache lines are selected for replacement in case of a cache miss.

There are three commonly used cache mapping techniques, according to (PATTERSON; HENNESSY, 2013). They are:

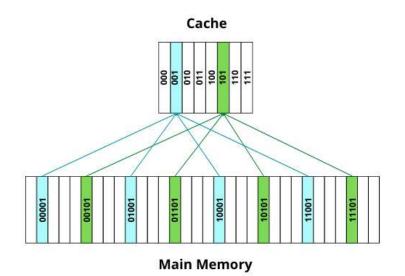

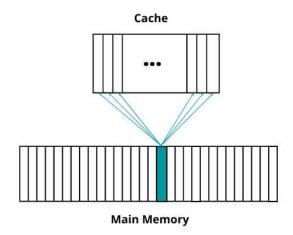

Direct Mapping: In this mapping scheme, each memory block is mapped to a specific cache line based on its memory address. The cache index is calculated using a subset of the address bits. For example, if the cache has 2<sup>n</sup> lines, the lower n bits of the memory address are used to determine the cache index. Direct mapping provides a simple and efficient mapping strategy, but it can lead to a high collision rate when multiple memory blocks are mapped to the same cache line, resulting in frequent cache misses.

Figure 2.3 – Direct mapping of a memory with 32 blocks into an eight-word cache.

Source: Adapted from (PATTERSON; HENNESSY, 2013)

In Figure 2.3, the least significant 3 bits of the main memory blocks are used as the cache index. Thus, addresses  $00001_{bin}$ ,  $01001_{bin}$ ,  $10001_{bin}$  and  $11001_{bin}$  are all mapped to cache entry  $001_{bin}$ , while addresses  $00101_{bin}$ ,  $01101_{bin}$ ,  $10101_{bin}$  and  $11101_{bin}$  are all mapped to the cache entry  $101_{bin}$ .

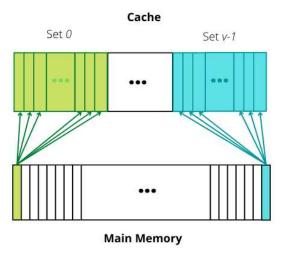

2. Set-Associative Mapping: Set-associative mapping combines the advantages of direct mapping and fully associative mapping. It divides the cache into a set of smaller groups or sets, where each set contains a fixed number of cache lines. Memory blocks can be mapped to any cache line within a specific set. The cache index is calculated using a subset of the address bits that identifies the set. Set-associative mapping reduces the collision rate compared to direct mapping by allowing more flexibility in cache line selection. Common examples include 2-way, 4-way, and 8-way set-associative mapping, where each set contains two, four, or eight cache lines, respectively.

In Figure 2.4, any memory block can be allocated on any line in the cache memory without any restrictions. The cache index is not derived from the

Figure 2.4 – Associative mapping of a block of main memory Source: Adapted from (PATTERSON; HENNESSY, 2013)

memory address, and the cache controller searches the entire cache to find the requested block.

3. Fully Associative Mapping: In fully associative mapping, any memory block can be mapped to any cache line, without any restrictions. This means that the cache index is not derived from the memory address. Instead, the cache controller searches the entire cache to find the requested block. Fully associative mapping provides the highest flexibility and lowest collision rate among all mapping techniques. However, it requires more complex hardware and incurs higher access latency due to the need for a full cache search. Consequently, fully associative mapping is typically used in smaller cache configurations or as an LLC in multilevel cache systems.

In Figure 2.5, the cache memory is divided into v sets. The main memory block  $B_0$  must be mapped to set 0 and can be allocated to any line in that set. The block  $B_{v-1}$  of main memory must be mapped in any line of the set v - 1 of the cache.

The choice of cache mapping technique greatly influences cache performance, hit rate, and access latency. Different applications and memory access patterns may benefit from different mapping schemes. The selection of an appropriate cache mapping technique involves considering factors such as cache size, associativity, access patterns, and the trade-off between cache hit rate and hardware complexity. Optimizing cache mapping is an important

Figure 2.5 – Associative mapping per set. Source: Adapted from (STALLINGS, 2009)

aspect of cache design and can significantly impact the overall system performance.

# 2.1.3.4 Cache Partitioning

Cache partitioning is a technique used in real-time systems to allocate a specific portion of the cache to a particular task or core. This helps in isolating task workloads, reducing interference between cores (in multicore systems), improving system predictability, and facilitating Worst-Case Execution Time (WCET) estimation (SANCHEZ; KOZYRAKIS, 2011).

Cache partitioning involves dividing the cache into private and shared spaces. Each task or core is allocated a private space in the cache where it can store its most recently accessed memory blocks. This private space is virtual, meaning that it consists of the N most recently used blocks accessed by the task in each cache set, regardless of their physical location. The actual storage location of these blocks may vary while the task is running. Once the task is completed, the associated private space is released (LESAGE; PUAUT; SEZNEC, 2012).

The shared space in the cache holds blocks that are accessed by all cache-accessing tasks, regardless of whether they have a dedicated private space. It contains the least accessed memory blocks of tasks. The shared space dynamically consists of cache lines that do not belong to any private space. This includes cache lines occupied by task blocks that have no private cache space and cache lines used by a task beyond its allocated capacity of private

space (LESAGE; PUAUT; SEZNEC, 2012).

There are two forms of cache partitioning: index-based and way-based partitioning. In index-based partitioning, partitions are formed by aggregating associative sets in the cache. Each partition consists of multiple cache sets. In way-based partitioning, partitions are formed by aggregating individual cache ways. Each partition consists of multiple cache ways (GRACIOLI et al., 2015).

Different cache partitioning mechanisms have been proposed in the literature to address both types of partitioning. These mechanisms aim to efficiently allocate cache space to tasks, optimize cache utilization, and manage the sharing of cache resources among tasks. The details of cache partitioning mechanisms will be discussed in Section 3.2.

# 2.1.4 Cache Replacement Policies

Cache replacement policies play a critical role in managing cache utilization and performance. When a cache miss occurs, requiring the retrieval of a block of memory into the cache, a cache line needs to be selected for replacement. This decision becomes particularly important in caches that utilize associative or set associative mapping techniques. The cache line replacement policy dictates which block will be evicted from the cache and where the incoming block will be placed.

Choosing an effective cache replacement policy is essential to maximize cache hit rates, reduce cache thrashing, and improve overall system performance. Various cache replacement policies have been developed, each with its own advantages and trade-offs. In the following subsection, we explore some commonly used cache replacement policies, delve into their characteristics, and examine their impact on cache performance

### 2.1.4.1 RANDOM

The RANDOM cache replacement policy is the simplest and most straightforward approach among cache line replacement policies. It operates by randomly selecting a cache line for eviction whenever a new block needs to be inserted into the cache. The existing block occupying the randomly chosen position is replaced with the new block.

The RANDOM policy is easy to implement since it does not require any complex tracking or decision-making mechanisms. However, its simplicity comes at the cost of performance. Since the replacement decision is purely random, it disregards the principle of temporal locality, which states that recently accessed blocks are more likely to be accessed again in the near future. As a result, the RANDOM policy tends to lead to suboptimal cache performance. Empirical studies have demonstrated that the RANDOM policy performs, on average, approximately 22% worse than more advanced policies like LRU in the context of data caches (AL-ZOUBI; MILENKOVIC; MILENKOVIC, 2004). Despite its inferior performance, the RANDOM policy is still employed in certain processors, such as the Cortex A-53. In cases where simplicity and low implementation overhead outweigh the potential performance gains of more sophisticated policies, the RANDOM policy may be a viable choice.

### 2.1.4.2 First-In, First-Out (FIFO)

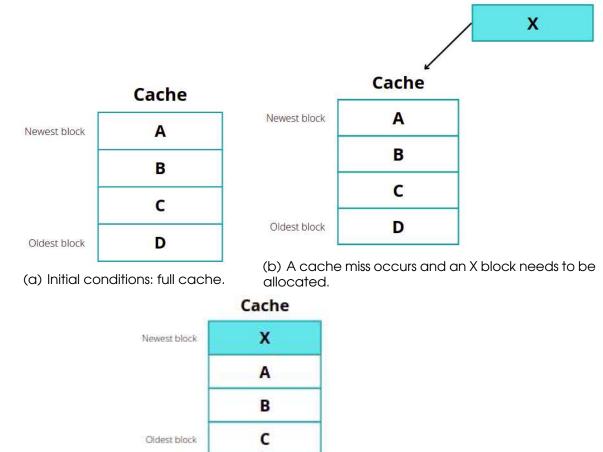

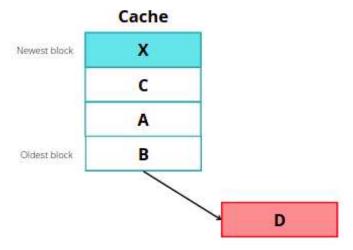

The FIFO cache replacement policy operates based on the order of entry of blocks into the cache. Each block is assigned a position in the cache based on the time it was brought in, with the oldest block occupying the LRU position. When a cache miss occurs and a new block needs to be inserted, it is placed in the first position of the cache, pushing all existing blocks toward the LRU position. As a result, the oldest block, which is located in the LRU position, is evicted from the cache.

In Figure 2.6, an example of a cache employing the FIFO policy is illustrated. The cache initially contains blocks A, B, C, and D (Figure 2.6(a)). When a cache miss occurs and a new block X is brought in, it is allocated in the most recently used (MRU) position, displacing the existing blocks towards the LRU position. Consequently, the oldest block D, which occupied the LRU position, is evicted from the cache (Figure 2.6(b)).

The FIFO policy ensures a fair and deterministic replacement strategy, as blocks are evicted in the order in which they entered the cache. However, it suffers from the drawback of not considering the access frequency or recency of the blocks. This can lead to poor cache performance in scenarios where certain blocks are repeatedly accessed, while others are rarely used. Despite its simplicity and fairness, the FIFO policy is generally outperformed by more advanced replacement policies, such as LRU, in terms of cache hit rate and overall system performance.

### 2.1.4.3 Lest Recently Used (LRU)

The Least Recently Used cache replacement policy is a popular and effective strategy for managing cache memory. It is based on the principle of temporal locality, which states that recently accessed data is more likely to be accessed again in the near future. The LRU policy aims to maximize cache hit rates by prioritizing cache lines that have been accessed most recently.

In the LRU policy, each cache line is associated with a timestamp or counter that indicates the order of its access. Whenever a cache hit occurs,

(c) Block X assumes the position of the newest block pushing all others in the queue. Block D leaves the cache.

D

Figure 2.6 - FIFO replacement policy.

Source: Adapted from (HANDY, 1998)

indicating that a requested block is found in the cache, the corresponding cache line's timestamp is updated to the current time, marking it as the most recently used. This ensures that frequently accessed data remains in the cache and can be quickly retrieved when needed.

When a cache miss occurs and a new block needs to be brought into the cache, the cache line with the oldest timestamp, representing the least recently used block, is selected for replacement. The new block is then inserted into the cache at the position of the evicted block.

The significance of the LRU policy lies in its ability to exploit the temporal locality exhibited by many programs. By giving priority to recently accessed data, it maximizes the chances of keeping frequently used data in the cache,

reducing the frequency of cache misses and improving overall system performance. (SMITH, 1982)

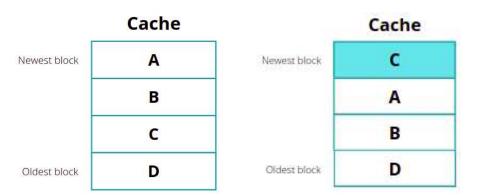

Figure 2.7 provides a visual representation of the LRU policy. In Figure 2.7(a), the cache initially contains blocks A, B, C and D, with their corresponding timestamps indicating their order of access, from the most recent to the least recent. In Figure 2.7(b), a cache hit occurs when block C is accessed. As a result, block C's timestamp is updated, moving it to the most recent position. Blocks A and B retain their relative positions. In Figure 2.7(c), a cache miss occurs when block X is requested and not found in the cache. Block X is brought in from main memory and replaces the block with the oldest timestamp, which is block D in this case. The timestamps of blocks A, B and C are updated accordingly.

(a) Initial conditions. Cache full.

(b) A cache hit occurs.

(c) A cache miss occurs.

The LRU policy has proven to be highly effective in improving cache performance and reducing cache thrashing. Its ability to prioritize frequently accessed data aligns well with the behavior of many programs, resulting in higher cache hit rates and overall system efficiency. As a result, the LRU policy is widely used in various computer architectures and systems.

# 2.1.4.4 Pseudo-LRU (PLRU)

The Pseudo Least Recently Used (Pseudo-LRU or PLRU), also known as tree-LRU, is a widely adopted cache line replacement policy in modern cache memory designs. It has gained popularity and is extensively utilized in commercial products by leading companies like AMD and Intel (Abel; Reineke, 2013).

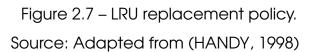

The Pseudo-LRU algorithm employs a binary tree data structure to track the cache memory state. In this tree, each node represents a cache line and is associated with a bit that can be interpreted as an arrow. The tree's structure allows for efficient determination of the least recently used cache line.

When a cache hit occurs, indicating that the requested data is already present in the cache, the corresponding bits pointing to that memory location are inverted. This inversion ensures that the recently accessed cache line moves closer to the root of the binary tree, indicating its updated usage.

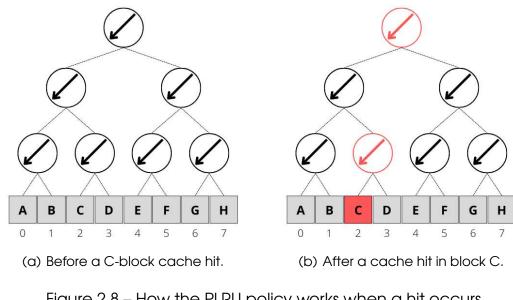

On the other hand, when a cache miss happens and new data needs to be brought into the cache, the line pointed to by the bits is selected for replacement. The new data replaces this line, and the corresponding bits are then inverted, indicating its recent usage.

The Pseudo LRU policy leverages the tree-like structure and the bit inversions to approximate the least recently used cache line efficiently. By keeping track of the cache lines' relative recency of use, the Pseudo LRU policy aims to minimize cache misses and maximize cache hit rates, leading to improved performance.

Figure 2.9 provides an illustration of the Pseudo LRU policy in action. In this example, a cache miss occurs when a requested block is not found in the cache. The new data replaces the cache line pointed to by the bits, and the corresponding bits are inverted, indicating the updated cache line usage.

The Pseudo LRU policy has become prevalent due to its effectiveness in managing cache memory and its utilization by major industry players. Its ability to efficiently approximate the least recently used cache line makes it a valuable tool for improving cache performance in a variety of computing systems.

# 2.1.5 Adaptive Insertion Policies

This subsection introduces three adaptive insertion policies, namely LIP (LRU Insertion Policy), BIP (Bimodal Insertion Policy), and DIP (Dynamic Insertion Policy), proposed by Qureshi et al. (QURESHI et al., 2007). These policies are

Figure 2.8 – How the PLRU policy works when a hit occurs. Source: Adapted from (HANDY, 1998)

(a) Before a cache miss on block C.

(b) After a cache miss on block CC.

Figure 2.9 – How the PLRU policy works when a cache miss occurs. Source: Adapted from (HANDY, 1998)

based on LRU policy, but aim to reduce cache misses for memory-intensive workloads.

The LRU policy, while widely used, may not be optimal for all workload patterns. The adaptive insertion policies offer greater flexibility and adaptability to improve cache performance in such scenarios.

The LIP, BIP and DIP policies proposed by Qureshi et al. demonstrate their potential in enhancing cache performance for memory-intensive workloads. By deviating from strict LRU ordering and considering factors like insertion time and age ranges, these adaptive insertion policies improve cache hit rates and effectively reduce the number of cache misses.

# 2.1.5.1 LRU Insertion Policy (LIP)

The LIP is an adaptive insertion policy that enhances cache performance by allocating all input lines at the LRU position in the cache. Unlike traditional LRU, where cache lines are reordered only based on their access history, LIP introduces the concept of promoting lines from the LRU position to the MRU position when new lines are brought in from the main memory. This adaptive approach aims to address the limitations of LRU and optimize cache performance for memory-intensive workloads.

The key advantage of LIP is its ability to avoid thrashing for workloads with a working set larger than the cache size. By initially placing all input lines at the LRU position, LIP ensures that frequently accessed lines remain in the cache while infrequently accessed lines are more likely to be evicted. This strategy helps maintain a balanced cache content and mitigates the negative impact of excessive cache misses. (QURESHI; SRINIVASAN; RIVERS, 2007)

Furthermore, LIP exhibits excellent performance for workloads that exhibit a cyclic access pattern. By promoting recently accessed lines from the LRU position to the MRU position, LIP adapts to the cyclic nature of these workloads and achieves near-optimal hit rates. This adaptive behavior allows LIP to effectively exploit temporal locality and improve cache efficiency.