# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO DEPARTAMENTO DE ENGENHARIA ELÉTRICA E ELETRÔNICA CURSO DE ENGENHARIA ELETRÔNICA

Julio Ribeiro Martins

Oscilador CMOS controlado por temperatura

| Julio Ribeiro Martins |

|-----------------------|

|                       |

# Oscilador CMOS controlado por temperatura

Trabalho Conclusão do Curso de Graduação em Engenharia Eletrônica do Centro Tecnológico da Universidade Federal de Santa Catarina como requisito para a obtenção do título de Bacharel em Engenharia Eletrônica.

Orientador: Prof. Marcio Cherem Schneider, Dr.

Florianópolis

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Martins, Julio Ribeiro Oscilador CMOS controlado por temperatura / Julio Ribeiro Martins; orientador, Marcio Cherem Schneider, 2021. 58 p.

Trabalho de Conclusão de Curso (graduação) - Universidade Federal de Santa Catarina, Centro Tecnológico, Graduação em Engenharia Eletrônica, Florianópolis, 2021.

Inclui referências.

1. Engenharia Eletrônica. 2. Oscilador controlado por temperatura. 3. Fonte de corrente autopolarizada. 4. Oscilador em anel. 5. Independência da fonte de alimentação. I. Schneider, Marcio Cherem Schneider. II. Universidade Federal de Santa Catarina. Graduação em Engenharia Eletrônica. III. Título.

#### Julio Ribeiro Martins

# Oscilador CMOS controlado por temperatura

Este Trabalho de Conclusão de Curso foi julgado adequado para obtenção do Título de Bacharel em Engenharia Eletrônica e aprovado em sua forma final pelo Curso de Engenharia Eletrônica.

| Florianópolis, 30 de junho de 2021.                                     |

|-------------------------------------------------------------------------|

| Prof. Fernando Rangel de Sousa, Dr. Coordenador do Curso                |

| Prof. Marcio Cherem Schneider, Dr., UFSC Orientador  Banca Examinadora: |

| Banca Examinadora:                                                      |

| Prof. Carlos Galup-Montoro, Dr., UFSC<br>Avaliador                      |

| Prof. Cesar Ramos Rodrigues, Dr., UFSC<br>Avaliador                     |

| Eng. Rodrigo Eduardo Rottava, Me., Chipus Microeletrônica Avaliador     |

#### **AGRADECIMENTOS**

Em primeiro lugar, agradeço aos meus pais, Rosilene e Altino, por sempre acreditarem em mim e por todo apoio e incentivo nestes anos de graduação, sem os quais eu não teria a possibilidade de continuar minha formação.

Agradeço imensamente ao Prof. Marcio C. Schneider, Dr. por ter sido meu orientador e ter desempenhado tal função com dedicação e amizade. Também pelas correções e ensinamentos que me permitiram apresentar um melhor desempenho nas atividades desenvolvidas e guiaram o meu aprendizado.

Agradeço aos colegas do Laboratório de Circuitos Integrados pela oportunidade de fazer parte da equipe, pela confiança no compartilhamento de informações e pela receptividade e ajuda no desenvolvimento deste trabalho, em especial ao Thiago e Evandro.

Agradeço a Universidade Federal de Santa Catarina, todos os professores e servidores, pela oportunidade de ensino público de qualidade.

Agradeço aos meus colegas de classe, por compartilharem comigo momentos de aprendizado e pela troca de experiências que me permitiram crescer não só como pessoa, mas também como formando.

E por último, mas não menos importante, agradeço aos meus grandes amigos, Jéssica, João e Nathália, por todos os momentos de incentivo, compreensão e amizade que me apoiaram durante toda a graduação.

#### **RESUMO**

Neste projeto, é desenvolvido um oscilador controlado por temperatura com baixa dependência da tensão de alimentação. Para isso, uma fonte de corrente proporcional à temperatura absoluta (PTAT) foi projetada para alimentar um oscilador em anel. Como resultado, a frequência de oscilação é aproximadamente PTAT. Além disso, um circuito para inicializar a fonte de corrente em um curto período de tempo, um deslocador de nível para maior excursão do sinal oscilatório e, finalmente, um *buffer* para transferir o sinal oscilatório a uma sonda para medições foram projetados. Ferramentas da Cadence foram empregadas para o leiaute e extração de capacitâncias e resistências parasitas, visando a uma possível integração na tecnologia CMOS 0.18 μm. A frequência de oscilação é de 1 MHz a 40 °C, com sensibilidade à temperatura de 4000 ppm/°C e erro máximo de ±0.3 °C na faixa de 0 a 80 °C. O oscilador consome aproximadamente 1 μA (sem considerar o buffer), apresenta sensibilidade à fonte de alimentação de 1000 ppm/V para uma tensão de alimentação entre 1.6 V e 2 V. A área total é de 1500 μm².

Palavras-chave: Tecnologia CMOS. Oscilador em anel. Fone de corrente PTAT. Oscilador controlado por temperatura.

#### **ABSTRACT**

In this project, a temperature-controlled oscillator with a low frequency dependence on the power supply voltage is developed. For this, a proportional to absolute temperature (PTAT) current source was designed to feed a current-starved ring oscillator. As a result, the oscillation frequency is approximately PTAT. Additionally, a circuit for starting up the current source in a short period of time, a level shifter for increased excursion of the oscillatory signal and, finally, a buffer for carrying the oscillatory signal to a probe for measurements were designed. Cadence tools were employed for the layout and extraction of parasitic capacitances and resistances, aiming at a possible integration in 0.18  $\mu m$  CMOS technology. The oscillation frequency is 1 MHz at 40 °C, with temperature sensitivity of 4000 ppm/°C and maximum error of  $\pm 0.3$  °C in the range of 0 to 80 °C. The oscillator consumes approximately 1  $\mu A$  (not considering the buffer), presents supply sensitivity of 1000 ppm/V for a supply voltage between 1.6 V to 2 V and a total area of 1500  $\mu m^2$ .

**Keywords:** CMOS technology. Current-starved ring oscillator. PTAT current source. Temperature-controlled oscillator.

# LISTA DE FIGURAS

|          | Figura 1 Comparação de tecnologias para detecção de temperatura                     | 16  |

|----------|-------------------------------------------------------------------------------------|-----|

|          | Figura 2 Diagrama de Blocos do TCO                                                  | 18  |

|          | Figura 3 Diagrama esquemático do TCO                                                | 18  |

|          | Figura 4 Fonte de corrente simples                                                  | 19  |

|          | Figura 5 Esquemático simplificado da SBCS                                           | 19  |

|          | Figura 6 Variação do resistor compósito com a temperatura                           | 22  |

|          | Figura 7 Variação da corrente com a temperatura para diferentes tipos de resistores | 23  |

|          | Figura 8 Características de transferência dos espelhos de corrente                  | 23  |

|          | Figura 9 Correntes e tensões na inicialização                                       | 24  |

|          | Figura 10 Tempo de estabilização da corrente em função do tempo de subida da for    | nte |

| de alime | ntação                                                                              | 25  |

|          | Figura 11 Variação da corrente de saída com a temperatura (a) e com a fonte         | de  |

| alimenta | ção (b)                                                                             | 28  |

|          | Figura 12 - Sensibilidade da corrente de saída com a tensão de alimentação em funç  | ão  |

| da tempe | eratura                                                                             | 28  |

|          | Figura 13 Variação da corrente de saída com a temperatura para os corners           | da  |

| tecnolog | ria                                                                                 | 30  |

|          | Figura 14 Sensibilidade da corrente de saída com a fonte de alimentação nos corre   | ers |

| da tecno | logia                                                                               | 30  |

|          | Figura 15 Simulação de Monte Carlo da corrente de saída                             | 31  |

|          | Figura 16 Leiaute desenvolvido da fonte de corrente autopolarizada                  | 32  |

|          | Figura 17 Diagrama simplificado do Oscilador em anel                                | 33  |

|          | Figura 18 Propagação do sinal no oscilador em anel                                  | 33  |

|          | Figura 19 Esquemático simplificado do CSRO proposto                                 | 34  |

|          | Figura 20 Esquemático simplificado de um estágio estático do inversor               | 35  |

|          | Figura 21 Capacitâncias associadas a dois inversores cascateados                    | 36  |

|          | Figura 22 Esquematico do Level Shifter com espelho de corrente                      | 38  |

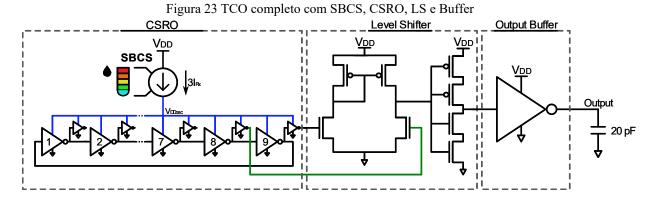

|          | Figura 23 TCO completo com SBCS, CSRO, LS e Buffer                                  | 39  |

|          | Figura 24 Tensões na saída de um inversor do CSRO e na capacitância de carga        | 40  |

|          | Figura 25 Variação da frequência com a temperatura (a) e inclinação para VDD        | =   |

| 1.8 V (b | )                                                                                   | 41  |

| Figura 26 Variação da frequência com a alimentação em 1.6 V e 2.0 V relativo à       |

|--------------------------------------------------------------------------------------|

| alimentação de 1.8 V41                                                               |

| Figura 27 Variação da sensibilidade do coeficiente de temperatura em função de VDD   |

| (a) e sensibilidade à tensão de alimentação (b)                                      |

| Figura 28 Variação da frequência com a temperatura nos corners do processo43         |

| Figura 29 Sensibilidade da frequência com a alimentação em 0, 40, 80°C nos corners   |

| do processo                                                                          |

| Figura 30 Erro da temperatura em relação ao modelo linear                            |

| Figura 31 Corrente consumida em função da temperatura no buffer (a) e no restante do |

| TCO (b)                                                                              |

| Figura 32 Histograma da variação da frequência com o descasamento dos dispositivos   |

| 46                                                                                   |

| Figura 33 Leiaute completo do TCO                                                    |

| Figura 34 Tensões de saída no circuito extraído para diferentes VDD48                |

| Figura 35 Variação da frequência extraída com a temperatura para diferentes valores  |

| de VDD (a) e erro relativo ao modelo linear (b)                                      |

| Figura 36 Sensibilidade da frequência com a tensão de alimentação para diferentes    |

| temperaturas                                                                         |

| Figura 37 Erro da temperatura extraída em relação ao modelo linear50                 |

| Figura 38 Rejeição de <i>VDDosc</i> à fonte de alimentação51                         |

|                                                                                      |

# LISTA DE TABELAS

| Tabela 1 Parâmetros dos resistores                | 21 |

|---------------------------------------------------|----|

| Tabela 2 Dimensionamento dos transistores da SBCS | 27 |

| Tabela 3 Modelos dos corners da tecnologia        | 29 |

| Tabela 4 Dimensionamento do CSRO                  | 40 |

#### LISTA DE ABREVIATURAS E SIGLAS

CMOS - Complementary Metal-Oxide-Semiconductor

CSRO - Current-Starved Ring Oscillator

DRC - Design Rule Checking

LS - Level Shifter

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

NMOS - N-channel Metal-Oxide Semiconductor

PMOS - P-channel Metal-Oxide Semiconductor

PTAT - Proportional to Absolute Temperature

RTD - Resistance Temperature Detector

SBCS - Self-Biased Current Source

TC - Temperature Coefficient

TCO - Temperature Controlled Oscillator

UICM - Unified Current-Control Model

## LISTA DE SÍMBOLOS

$V_P$  Tensão de *pinch-off*

$V_{S(D)}$  Tensão de fonte (dreno) do transistor  $I_D$  Corrente do dreno do transistor

$R_X$  Resistor da SBCS  $I_{Rx}$  Corrente no resistor

$I_S$  Corrente específica do transistor  $I_{F(R)}$  Corrente direta (reversa) do transistor

$\phi_t$  Tensão térmica

KFator de espelhamento dos NMOS da SBCSMFator de espelhamento dos PMOS da SBCS

$k_B$  Constante de Boltzmann

q Carga do elétronT Temperatura

$TC_{I_{R_{x}}}$  Coeficiente de temperatura da corrente no resistor  $TC_{S\acute{e}rie}$  Coeficiente de temperatura do resistor compósito

L Comprimento do canal do transistor W Largura do canal do transistor  $\sigma^2(I_D)$  Variância da corrente do transistor

$A_{I_{SH}}$  Parâmetro de descasamento da corrente específica de folha

$A_{V_{\tau}}$  Coeficiente de descasamento da tensão de limiar

$i_f$  Nível de inversão direto normalizado pela corrente específica

*n* Fator de inclinação do transistor

$V_{DS_{sat}}$  Tensão entre dreno e fonte de saturação do transistor

$I_{SH}$  Corrente específica de folha

$T_D$  Tempo de atraso médio do inversor

C<sub>L</sub> Capacitância associada a cada estágio do CSRO

$f_{osc}$  Frequência de oscilação

$V_{DD}$  Tensão da fonte de alimentação

$V_{DDosc}$  Tensão de alimentação local dos estágios inversores do CSRO

Número de estágios inversores

$V_{T0}$  Tensão de limiar em polarização nula

$C_{gd}$  Capacitância entre porta e dreno do transistor  $C_{db}$  Capacitância entre dreno e substrato do transistor

$C_g$  Capacitância na porta do transistor  $C_w$  Capacitância de interconexão  $C_J$  Capacitância de junção por área  $C_{JSW}$  Capacitância de junção por perímetro

$C_{ox}$  Capacitância do óxido por área de porta  $C_o$  Capacitância de sobreposição de porta

# SUMÁRIO

| 1   | INTRODUÇÃO                               | 15 |

|-----|------------------------------------------|----|

| 1.1 | ESTADO DA ARTE                           | 15 |

| 1.2 | OBJETIVOS E METODOLOGIA                  | 17 |

| 1.3 | ESTRUTURA PROPOSTA                       | 17 |

| 2   | FONTE DE CORRENTE AUTOPOLARIZADA         | 19 |

| 2.1 | TOPOLOGIA                                | 19 |

| 2.2 | SENSIBILIDADE À TEMPERATURA              | 21 |

| 2.3 | STARTUP                                  | 23 |

| 2.4 | DIMENSIONAMENTO                          | 25 |

| 2.5 | SIMULAÇÕES DA SBCS                       | 27 |

| 2.6 | LEIAUTE                                  | 31 |

| 3   | OSCILADOR EM ANEL                        | 33 |

| 3.1 | TOPOLOGIA                                | 33 |

| 3.2 | DIMENSIONAMENTO                          | 34 |

| 3.3 | LEVEL SHIFTER                            | 37 |

| 3.4 | BUFFER                                   | 39 |

| 3.5 | SIMULAÇÕES DO CSRO                       | 40 |

| 3.6 | LEIAUTE                                  | 47 |

| 4   | RESULTADOS OBTIDOS APÓS O LEIAUTE        | 48 |

| 5   | CONSIDERAÇÕES FINAIS E TRABALHOS FUTUROS | 52 |

|     | REFERÊNCIAS                              | 54 |

# 1 INTRODUÇÃO

Sensores de temperatura são amplamente aplicados em sistemas de controle, medida e instrumentação. Tornam-se necessários tanto para o monitoramento da temperatura interna ou externa ao dispositivo, quanto para garantir a proteção e evitar danos nos sistemas ou também para compensação de componentes críticos, mantendo o sistema robusto às variações dos dispositivos com a temperatura. Com essas necessidades, faz sentido fabricar sensores de temperatura integrados em tecnologia CMOS, que possibilitam baixo custo, grande volume de produção e de integração dos dispositivos. Microprocessadores e memórias, com bilhões de transistores, são exemplos de sistemas que necessitam de um gerenciamento térmico para fornecer informações sobre gradientes de temperatura e pontos de aquecimento, usando a maior densidade de sensores possível [1].

Um TCO (*Temperature Controlled Oscillator*) é um circuito que produz um sinal oscilatório controlado por temperatura. Em geral, é implementado com um oscilador em anel que recebe uma corrente proporcional à temperatura absoluta (PTAT). Osciladores em anel alimentados pela tensão de alimentação são diretamente dependentes da tensão da fonte de alimentação local. Para reduzir significativamente tal dependência, os osciladores em anel são alimentados por uma fonte de corrente. Se, adicionalmente, a fonte de corrente é PTAT, à medida que a temperatura aumenta, a variação da corrente resulta em um aumento da frequência de oscilação de forma aproximadamente linear.

#### 1.1 ESTADO DA ARTE

Devido à importância do monitoramento da temperatura, as considerações principais para o projeto são referentes à precisão, faixa de temperatura, tamanho (área de silício), potência e posicionamento do sensor de temperatura.

As tecnologias comumente usadas no monitoramento da temperatura incluem o uso de termistores, termorresistências (RTDs), termopares e circuitos integrados, este último sendo o foco deste trabalho. Na Figura 1 a seguir, disponibilizada pela Texas Instruments [1], vemos uma tabela comparativa de tecnologias usadas na detecção de temperatura, evidenciando os benefícios e desvantagens de cada uma. Nela vemos que o uso de circuitos integrados pode oferecer a melhor precisão, menor tamanho, baixa complexidade, melhor linearidade, preço baixo e cobrir temperaturas de -55 até +200 °C.

IC sensors **Thermistors** RTDs **Thermocouples** -55°C to +200°C -100°C to +500°C -240°C to 600°C -260°C to +2,300°C Range Accuracy Good/best Calibration-dependent Rest Retter Footprint/size Smallest Small Moderate Large Complexity Moderate Complex Complex Easy Linearity Best Low Best Better Topology Point-to-point, multidrop, daisy chain Point-to-point Point-to-point Point-to-point Price Low to moderate Low to moderate Expensive Expensive

Figura 1 Comparação de tecnologias para detecção de temperatura

Fonte: Texas Instruments [1].

Analisando o histórico do uso de osciladores controlados por temperatura vemos que, em 1975, foi desenvolvido um TCO utilizando um circuito multivibrador astável com uma rede resistiva usando um termistor; porém, as capacitâncias parasitas introduziam erros consideráveis ao aumentar a constante de tempo do circuito [2].

Em 2006, foi implementado por Makinwa e Snoeij [3] um conversor de temperatura em frequência em tecnologia CMOS de 0.7 μm em que a frequência de saída é determinada pela mudança de fase de um filtro eletrotérmico. Apesar da complexidade, é relatado o avanço em relação às implementações que utilizavam transistores bipolares, que têm alta precisão, mas ocupam grande área e necessitam de calibração.

Em 2009, foi apresentado por Ueno, Asai e Amemiya <sup>[4]</sup> um TCO semelhante ao proposto neste trabalho. Consiste em um gerador de corrente PTAT e um frequency-locked loop que gera uma frequência PTAT. O gerador de corrente PTAT é construído usando as características do MOSFET na região do sublimiar, em tecnologia CMOS de 0.35 μm.

Em 2015 foi implementado um conversor de temperatura para frequência por Chouhan e Halonen <sup>[5]</sup> para medir temperaturas internas ao chip, usando um circuito multivibrador acoplado à fonte. E, por Chiang e Chang <sup>[6]</sup>, foi projetado um conversor de diferença de temperatura para frequência com objetivo de medir a temperatura ambiente utilizando tecnologia CMOS de 0.35 μm. A inovação desse trabalho vem da técnica de calibração e da saída já digitalizada. Contudo, são apontados como aspectos negativos a área ocupada e consumo elevado.

Mais recentemente, em 2018, foi apresentado por Li e Zhou um TCO que utiliza a variação da tensão de limiar dos MOSFETs com a temperatura para o sensoriamento, utilizando tecnologia CMOS de 0.18 μm <sup>[7]</sup>. A tensão obtida é complementar à temperatura absoluta e utilizada em um oscilador controlado por tensão que gera, assim, a saída em frequência.

Em aplicações mais recentes, sem ter a saída do sensoriamento de temperatura em frequência, torna-se frequente a busca da conversão de temperatura diretamente para o domínio digital<sup>[8] [9]</sup>, fornecendo maior modularidade para integração com outros sistemas.

#### 1.2 OBJETIVOS E METODOLOGIA

É objetivo deste trabalho projetar um oscilador cuja frequência seja proporcional à temperatura e que, adicionalmente, tenha baixa dependência da frequência com a tensão da fonte de alimentação, com frequência variando em torno de 1 MHz, para temperaturas no intervalo de 0 até 80 °C, com precisão de ±0.5 °C, rejeição à fonte de alimentação menor que 0.125 °C/V e tensão de alimentação de 1.6 até 2V. O objetivo final é integrar o projeto em tecnologia CMOS de 0.18 μm.

Para alcançar esses objetivos foram usados resultados teóricos disponíveis na literatura referentes aos blocos principais para obter o comportamento desejado. Então, foi analisado o funcionamento do sistema por meio de simulações elétricas para obter medidas do desempenho do TCO desenvolvido, buscando a menor sensibilidade da frequência de saída com a fonte de alimentação, maior sensibilidade com a temperatura e, adicionalmente, mantendo um compromisso entre o consumo de potência e área ocupada. Por fim, foi verificado o funcionamento do sistema após o desenho do leiaute, por meio de simulações com a extração de impedâncias parasitas, visando à fabricação do sistema na tecnologia CMOS de 0.18 μm para verificação do seu real funcionamento no futuro.

Seguindo a metodologia apresentada para o projeto, inicialmente são apresentados os dois blocos principais: a fonte de corrente PTAT e o oscilador em anel. Inicia-se com as previsões teóricas, seguido pelas considerações adotadas para o projeto, blocos adicionais necessários, simulações no nível esquemático, leiaute desenvolvido e, por fim, comparação das simulações pré e pós-leiaute.

#### 1.3 ESTRUTURA PROPOSTA

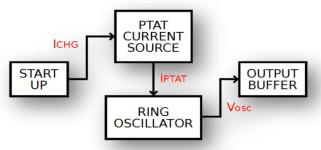

Dois blocos principais foram usados para implementar o TCO. Uma fonte de corrente PTAT autopolarizada (SBCS – *self-biased current source*) com *startup* e um oscilador em anel controlado por corrente (CSRO – *current-starved ring oscillator*) com buffer de saída. O diagrama de blocos do TCO é apresentado na Figura 2.

Figura 2 Diagrama de Blocos do TCO

O circuito de startup é responsável por inicializar o gerador de corrente no modo de operação apropriado. Uma vez estabelecida, a corrente do bloco SBCS polariza o oscilador em anel com uma corrente PTAT que produz um sinal oscilatório proporcional à temperatura que, para ser medido, necessita ser interfaceado ao circuito de medição através de um buffer.

Cada um desses blocos representa um circuito esquemático para realizar a função desejada. O diagrama esquemático proposto para o TCO é apresentado na Figura 3.

START CURRENT SOURCE OSCILLATOR BUFFER

Figura 3 Diagrama esquemático do TCO

Fonte: Elaborada pelo autor.

#### 2 FONTE DE CORRENTE AUTOPOLARIZADA

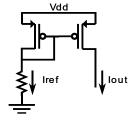

Usar uma fonte de corrente simples, como a representada na Figura 4 que usa um resistor para definir a corrente de polarização, pode resultar em correntes que são muito dependentes do valor da fonte de alimentação [10][11]. Uma forma de diminuir essa sensibilidade é utilizando uma fonte autopolarizada para garantir a polarização desejada.

Figura 4 Fonte de corrente simples

Fonte: Elaborada pelo autor.

#### 2.1 TOPOLOGIA

Uma fonte de corrente PTAT autopolarizada, independente da fonte de alimentação e com startup é apresentada em [10]. Adicionalmente, para suprimir os efeitos da modulação do comprimento do canal e aumentar a impedância de saída dos transistores, foram adicionados transistores  $N_3$ ,  $N_4$ ,  $P_3$  e  $P_4$  na configuração cascode. Seu esquemático completo com a relação das razões de aspecto entre os transistores é mostrado na Figura 5, juntamente com o símbolo que indica a variação da corrente com a temperatura.

Figura 5 Esquemático simplificado da SBCS

Startup

SBCS

Símbolo

Vod

PR

P1

1:1

P2

1:M

P6

NIRX

NIRX

NIRX

VSS

NIRX

VSS

VSS

VSS

Símbolo

Fonte: Elaborada pelo autor.

Para o projeto da SBCS, o transistor  $N_2$  é igual a K transistores  $N_1$  em paralelo e, portanto, como a corrente nesses transistores é mantida a mesma pelo espelho unitário  $P_1$ - $P_2$ , é aplicada ao resistor  $R_X$  a diferença de potencial  $V_{GS1}$  -  $V_{GS2}$ > 0, desde que K>1. Isto, por sua vez, gera a corrente PTAT através de  $R_X$ . Os transistores  $P_5$  e  $P_6$  espelham N vezes a corrente em  $R_X$  para a saída.

As equações de design para o SBCS PTAT são obtidas aplicando o UICM<sup>[10]</sup> seguindo a relação:

$$V_P - V_{S(D)} = \phi_t \left[ \sqrt{1 + \frac{I_{F(R)}}{I_S}} - 2 + \ln\left(\sqrt{1 + \frac{I_{F(R)}}{I_S}} - 1\right) \right]; V_P = \frac{V_G - V_{T0}}{n\phi_t}$$

(1)

onde  $V_P$  é a tensão de *pinch-off*,  $V_G$  é a tensão na porta,  $V_{S(D)}$  é a tensão de fonte(dreno), n é fator de inclinação,  $\phi_t$  é a tensão térmica,  $I_{F(S)}$  é a corrente direta(reversa),  $I_S$  é a corrente de saturação no transistor e  $V_{T0}$  é a tensão de limiar no equilíbrio.

Quando todos os transistores operam em saturação ( $I_F >> I_R$ ), aplicando UICM (1) aos transistores  $N_1$  e  $N_2$  obtemos, respectivamente, (2) e (3):

$$\frac{v_{P_{N_1}}}{\phi_t} = \sqrt{1 + \frac{I_{Rx}}{I_S}} - 2 + \ln\left(\sqrt{1 + \frac{I_{Rx}}{I_S}} - 1\right)$$

(2)

$$\frac{v_{P_{N_2}} - v_{S_{N_2}}}{\phi_t} = \sqrt{1 + \frac{I_{Rx}}{KI_S}} - 2 + \ln\left(\sqrt{1 + \frac{I_{Rx}}{KI_S}} - 1\right)$$

(3)

Como os transistores são iguais e têm a mesma tensão de porta,  $V_{P_{N_1}}=V_{P_{N_2}}$ . Subtraindo (3) de (2), temos:

$$\frac{V_{S_{N_2}}}{\phi_t} = \sqrt{1 + \frac{I_{Rx}}{I_S}} - \sqrt{1 + \frac{I_{Rx}}{KI_S}} + \ln\left(\frac{\sqrt{1 + \frac{I_{Rx}}{I_S}} - 1}}{\sqrt{1 + \frac{I_{Rx}}{KI_S}} - 1}\right)$$

(4)

Como  $V_{S_{N_2}} = R_X I_{R_X}$ , a expressão (3) pode ser reescrita como:

$$I_{R_X} = \frac{\phi_t}{R_X} \left[ \sqrt{1 + \frac{I_{RX}}{I_S}} - \sqrt{1 + \frac{I_{RX}}{KI_S}} + \ln\left(\frac{\sqrt{1 + \frac{I_{RX}}{I_S}} - 1}{\sqrt{1 + \frac{I_{RX}}{KI_S}} - 1}\right) \right]$$

(5)

Por fim, considerando que os transistores  $N_1$  e  $N_2$  operam em inversão fraca  $(I_S \gg I_{R_X})$ , obtemos:

$$I_{R_X} \cong \frac{\phi_t}{R_X} \ln K \tag{6}$$

Assim, caso a resistência  $R_X$  seja independente da temperatura, a corrente nos transistores é diretamente proporcional à temperatura absoluta, pois a tensão térmica é  $\phi_t = (k_B/q)T$ , onde  $k_B$  é a constante de Boltzmann e q é a carga do elétron.

#### 2.2 SENSIBILIDADE À TEMPERATURA

É objetivo deste trabalho obter uma resposta do sensor aproximadamente linear com a temperatura. Segundo a aproximação obtida em (6), a corrente gerada varia com a temperatura e com a resistência  $R_X$ . O coeficiente de temperatura (TC) da corrente é obtido através da relação:

$$TC_{I_{R_{\mathcal{X}}}} = \frac{1}{I_{R_{\mathcal{X}}}} \frac{\partial I_{R_{\mathcal{X}}}}{\partial T} = \frac{1}{T} - \frac{1}{R_{\mathcal{X}}} \frac{\partial R_{\mathcal{X}}}{\partial T}$$

$$\tag{7}$$

Para obter, de fato, uma corrente proporcional à temperatura absoluta, é necessário diminuir a influência da resistência no  $TC_{I_{R_X}}$ , tornando o coeficiente de temperatura de  $R_X$  o menor possível. Para isso, podemos usar a técnica de resistores compósitos em série<sup>[12]</sup>. Ao introduzir dois resistores em série, o coeficiente de temperatura da composição é dado pela expressão:

$$TC_{S\acute{e}rie} = \frac{1}{R_1 + R_2} \left( \frac{\partial R_1}{\partial T} + \frac{\partial R_2}{\partial T} \right)$$

(8)

Considerando  $R_X$  como a associação série de  $R_1$  e  $R_2$ , para que a expressão (8) seja nula, é necessário que  $\frac{\partial R_1}{\partial T} = -\frac{\partial R_2}{\partial T}$ , ou seja, que os resistores tenham comportamentos complementares em relação à temperatura, resultando em uma resistência total aproximadamente independente da temperatura.

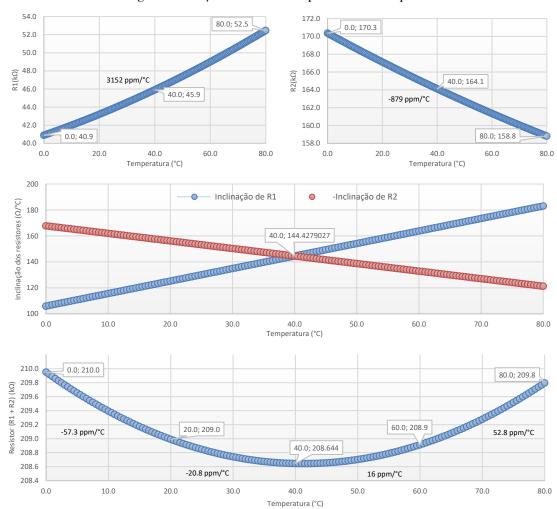

Na tecnologia utilizada são disponibilizados, dentre outros, resistores NWELL e Poly que têm coeficientes de temperatura complementares. Na Tabela 1 são mostrados os parâmetros medidos por simulação desses dispositivos para  $R_X=200~\mathrm{k}\Omega$  na temperatura de 40 °C, onde L é o comprimento dos resistores e ambos têm a largura de 2.1  $\mu$ m.

| Resistor                      | R1        | R2       |

|-------------------------------|-----------|----------|

| Material                      | STI NWELL | HRI Poly |

| TC [ppm/°C]                   | 3152      | -879     |

| Resistência de folha<br>[Ω/□] | 927       | 1037     |

| L [μm]                        | 86.5      | 314.2    |

| Resistência @40°C<br>[kΩ]     | 45.9      | 164.1    |

A variação das resistências com a temperatura, tanto separadamente quanto no resistor compósito, são mostradas na Figura 6. Com uma apropriada ponderação dos dois resistores, como na Tabela 1, a variação da resistência com a temperatura é bastante pequena no resistor compósito. Porém, devido à degradação da linearidade, quanto mais distante do ponto de calibragem (40 °C, no caso), maior a variação da resistência.

Figura 6 Variação do resistor compósito com a temperatura

Fonte: Elaborada pelo autor.

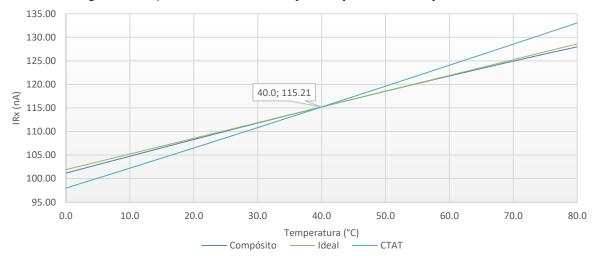

Por outro lado, observando a expressão (7), vemos que ao utilizar apenas um tipo de resistor com TC negativo, aumentaria ainda mais a sensibilidade da corrente com a temperatura e resultaria em melhor linearidade em relação ao resistor compósito. Estes resultados são mostrados na Figura 7. Vemos que a variação da corrente com a temperatura, no caso do resistor compósito, tem uma inclinação levemente menor que a de um resistor com coeficiente de temperatura próximo de zero. Já no caso do resistor com TC negativo, fica evidente o aumento da inclinação em relação aos demais, tornando-se a melhor escolha para este projeto.

Figura 7 Variação da corrente com a temperatura para diferentes tipos de resistores

#### 2.3 STARTUP

A SBCS tem dois blocos principais, um espelho de corrente unitário, formado pelos transistores  $P_1$  e  $P_2$ , e um espelho de corrente degenerado, formado por  $N_1$ ,  $N_2$  e  $R_X$ . Na Figura 8 são mostradas as características de transferência dos espelhos de corrente de cada um desses blocos.

Figura 8 Características de transferência dos espelhos de corrente

Fonte: Adaptado de [13]

O espelho formado por  $P_1$  e  $P_2$  tem ganho unitário e o espelho degenerado formado por  $N_1$ ,  $N_2$  e  $R_X$  tem uma relação não linear entre a corrente de saída e a de entrada. A corrente resultante é definida pela interseção dessas curvas, resultando em dois pontos de operação, o ponto A desejado e o ponto B onde a corrente é extremamente baixa.

Segundo a análise da estabilidade em [13], no caso do ponto A, vemos pela curva de transferência que o ganho do primeiro bloco é unitário, então um aumento na corrente em  $P_2$  reflete na mesma corrente em  $P_1$  e assim em  $N_1$ . Já no segundo bloco, vemos que o ganho de corrente como valor da corrente nominal (ponto A) é menor que a unidade, tornando o ponto de operação estável. Por outro lado, no ponto B, ocorre justamente o contrário. A inclinação no ponto B é maior que a unidade, tornando o ponto instável, como desejável.

Contudo, por operar com baixas correntes no ponto *B*, o ganho pode ser degradado abaixo da unidade, devido a correntes de fuga por exemplo, tornando a condição de corrente no ponto *B* estável por tempo indeterminado. Para evitar esta condição, é utilizado um circuito de startup para inicializar a corrente no ponto de operação desejado o quanto antes.

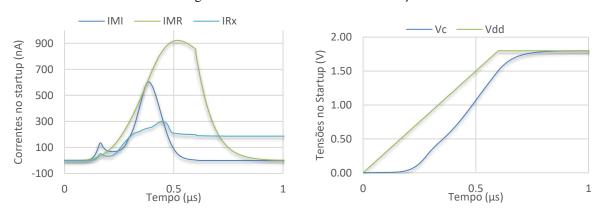

O circuito de startup apresentado em [10] é mostrado na Figura 5. Quando o sistema é ligado, a corrente no transistor  $P_I$  atinge seu valor máximo, fornecendo carga ao nó associado ao seu dreno. No entanto, a corrente começa a diminuir à medida que o transistor  $P_R$  carrega o capacitor formado pelo transistor  $N_C$  até atingir a tensão de alimentação, quando é interrompida a corrente em  $P_I$ . Este funcionamento é verificado por simulação através dos gráficos obtidos na Figura 9, aproximando o acionamento da fonte de alimentação por uma rampa com 600 ns de subida. Desta forma, assim que o circuito é acionado, os transistores  $N_3$  e  $N_I$  são polarizados no ponto estável e a corrente se estabiliza no ponto de operação desejado, em tempo relativamente curto, após ser acionada a alimentação.

Figura 9 Correntes e tensões na inicialização

Fonte: Elaborada pelo autor.

Por simulação, o tempo que a corrente demorou para se estabilizar no ponto de operação desejado, sem o startup, foi da ordem de 6 μs. Por outro lado, com o startup, para rampas de subida da ordem de no máximo nanossegundos, a corrente leva menos de cerca de 230 ns para se estabilizar, 26 vezes mais rápido. E, para rampas de subida mais lentas, a

corrente é acionada de forma aproximadamente linear com o tempo de subida da alimentação. Este resultado é mostrado na Figura 10.

Figura 10 Tempo de estabilização da corrente em função do tempo de subida da fonte de alimentação

Fonte: Elaborada pelo autor.

#### 2.4 DIMENSIONAMENTO

Em uma fonte de corrente, para diminuir a sensibilidade da corrente com a tensão de saída podemos utilizar empilhamento de transistores (configuração cascode) e aumentar o comprimento do canal dos transistores [10] [12]. Os transistores  $P_3$ ,  $P_4$ ,  $N_3$ , e  $N_4$  na Figura 5 foram adicionados com para aumentar a impedância de saída da fonte de corrente.

Para o funcionamento desejado da fonte de corrente, é necessário que os transistores  $N_1$  e  $N_2$  operem em inversão fraca. Segundo [14], para diminuir o descasamento entre os transistores da fonte de corrente, os transistores devem operar em inversão forte, suas áreas efetivas de porta não devem ser as mínimas disponíveis, devem ser decompostos em transistores unitários com a mesma geometria e orientação e, adicionalmente, devem ser intercalados em configuração de centroide comum. Conforme a relação (9) a seguir, as considerações de área e nível de inversão  $(i_f)$  podem ser verificadas pelo modelo de Pelgrom, adaptado em [10] para um espelho de corrente, onde  $\sigma^2(I_D)$  representa a variância da corrente de dreno, W é a largura do canal, L o comprimento do canal,  $A_{I_{SH}}$  é o parâmetro de descasamento da corrente específica de folha e  $A_{V_T}$  é o coeficiente de descasamento da tensão de limiar.

$$\frac{\sigma^2(I_D)}{I_D^2} \approx \frac{2}{WL} \left\{ A_{ISH}^2 + \left( \frac{A_{V_T}}{n \phi_t} \right)^2 \left[ \frac{2}{\sqrt{1 + i_f} + 1} \right]^2 \right\} \tag{9}$$

Contudo, como é desejado minimizar a variação da corrente com a fonte de alimentação, foram mantidos os transistores em inversão moderada para diminuir  $V_{DS_{sat}}$ , a

tensão entre dreno e fonte a partir da qual o transistor opera em saturação, dada pela relação (10), conforme [10] . Dessa forma, é possível garantir que, mesmo com a menor tensão de alimentação, os transistores continuem operando em saturação com a tensão entre dreno e fonte acima da mínima para saturação.

$$V_{DS_{sat}} = \phi_t \left( \sqrt{1 + i_f} + 3 \right) \tag{10}$$

O resistor Rx é responsável por converter a tensão PTAT na fonte de  $N_2$  em corrente. Algumas desvantagens no uso de resistores em circuitos integrados é que ocupam área considerável quando é necessário o uso de elevadas resistências para obter correntes reduzidas, além de poderem apresentar variações consideráveis com o processo de fabricação. Várias técnicas são usadas para substituir o resistor por um circuito equivalente, como a utilização de um transistor na região triodo, que implementa um resistor controlado por tensão<sup>[14]</sup>. Porém, neste projeto, como o objetivo é gerar uma corrente aproximadamente linear com a temperatura e com baixa dependência da alimentação, o uso da topologia com resistor foi capaz de obter a corrente desejada sem a necessidade de adicionar maior complexidade ao circuito e sem ocupar mais que o dobro da área utilizada pelos demais transistores da fonte de corrente.

Para o dimensionamento da fonte de corrente, como K representa o número de transistores  $N_I$  em paralelo e deve ser maior que um, foi adotado K igual a 5, resultando em:

$$I_{R_X}R_X = \phi_t \ln K = (k_B T/q) \ln 5 \approx 43 \text{ mV } @40^{\circ}\text{C}.$$

(11)

Como os transistores operam em saturação, a corrente no dreno é aproximadamente igual à corrente direta que é o produto do nível de inversão direto pela corrente especifica de folha ( $I_{SH}$ ) e pela razão entre W e  $L^{[10]}$ , conforme equacionado em (12).

$$I_D = I_F = i_f I_{SH} W / L \tag{12}$$

Através de (12), podemos dimensionar os transistores em função da corrente e nível de inversão desejados. Rearranjando os termos de (12), obtemos:

$$\frac{W}{L} = \frac{I_D}{i_f I_{SH}} \tag{13}$$

Para a tecnologia utilizada, o valor obtido de  $I_{SH}$  para o NMOS foi de aproximadamente 110 nA. Adotando  $I_D = I_{SH}$ , a relação de aspecto fica inversamente proporcional ao nível de inversão. De (11), obtemos  $R_X$  da ordem de 390 kΩ. Já para o PMOS, o valor obtido de  $I_{SH}$  é de aproximadamente 38 nA.

Na Tabela 2, estão as dimensões utilizadas para os dispositivos da fonte de corrente e o nível de inversão, a partir das considerações apresentadas. Para melhor ajuste do leiaute, o transistor  $N_C$  foi dividido em dois transistores ( $N_{C1}$  e  $N_{C2}$ ) para implementar a capacitância

necessária, considerando a capacitância como aproximadamente o produto da área de porta pela densidade de capacitância por área, com valor obtido de 8 fF/ $\mu$ m<sup>2</sup>, totalizando 187 fF. Também, para facilitar o ajuste no leiaute, o resistor  $R_X$  foi dividido em 16 resistores em série.

Tabela 2 Dimensionamento dos transistores da SBCS

| Transistor                                    | $W(\mu m)$ | $L(\mu m)$ | W/L  | <b>İ</b> f |

|-----------------------------------------------|------------|------------|------|------------|

| $N_1$ e $N_2$                                 | 10.8       | 1.62       | 60/9 | 0.15       |

| <i>N</i> <sub>3</sub> e <i>N</i> <sub>4</sub> | 1.44       | 1.62       | 8/9  | 1.13       |

| $P_1$ , $P_2$ e $P_5$                         | 1.44       | 2.16       | 8/12 | 4.34       |

| $P_3$ , $P_4$ e $P_6$                         | 1.44       | 1.62       | 8/9  | 3.26       |

| $P_R$                                         | 0.22       | 5.94       | 1/27 | -          |

| $P_{I}$                                       | 0.22       | 0.18       | 11/9 | -          |

| Nc1 e Nc2                                     | 1.62       | 7.20       | 9/40 | -          |

# 2.5 SIMULAÇÕES DA SBCS

Com o dimensionamento dos transistores indicado na Tabela 2 foi analisado o funcionamento da fonte de corrente PTAT por meio de simulações em corrente contínua no ambiente Cadence.

A corrente em  $R_X$  é multiplicada por 3 através do espelho formado por  $P_2$  e  $P_5$ , em que  $P_5$  equivale a 3 transistores  $P_2$  em paralelo, resultando em cerca de 330 nA como corrente de saída, que é utilizada para alimentar o oscilador em anel.

Neste projeto, o modelo utilizado para verificar a linearidade consiste em obter a reta que melhor se adapta aos pontos simulados através do método dos mínimos quadrados. O erro relativo  $(e_{relativo})$  é calculado entre os pontos estimados pela reta  $(X_{estimado})$  e os pontos medidos por simulação  $(X_{medido})$ , através da relação  $e_{relativo}(\%) = 1 - X_{estimado}/X_{medido}$ .

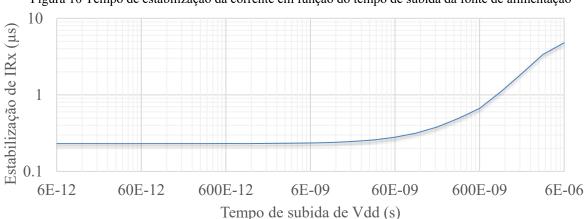

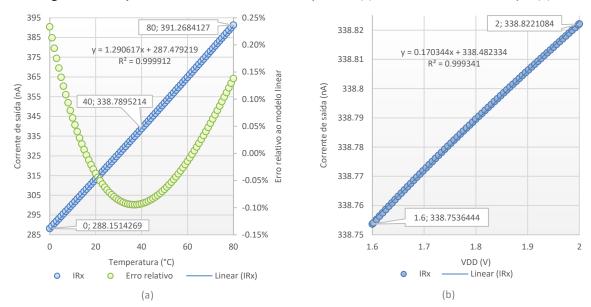

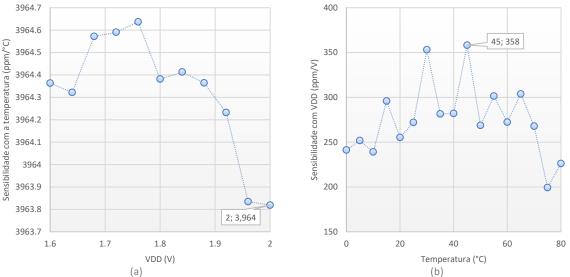

Na Figura 11, em (a) temos uma simulação onde vemos a variação da corrente de saída com a temperatura e, com o propósito de evidenciar a não linearidade, o erro relativo à aproximação linear desta curva. Esta simulação representa o caso típico, onde a fonte de alimentação é mantida em 1.8 V e os transistores e resistor utilizam o modelo típico de funcionamento. A corrente de saída, aos 40 °C, é de 338.79 nA com o coeficiente de temperatura de 3805 ppm/°C. Já em (b), é medida a mesma corrente, mas agora mantendo a temperatura fixa em 40°C e variando a fonte de alimentação de 1.6 até 2.0 V. Neste caso, a sensibilidade da corrente com a fonte de alimentação é de 505 ppm/V.

Figura 11 Variação da corrente de saída com a temperatura (a) e com a fonte de alimentação (b)

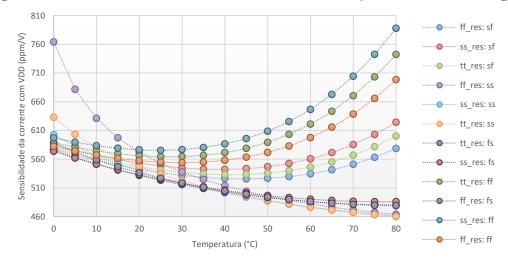

Para estimar o maior erro obtido no caso típico, na Figura 12 (a) foi simulada a sensibilidade da corrente de saída com a tensão de alimentação para a faixa de temperaturas do projeto. Vemos que quanto menor a temperatura, mais sensível é a corrente a variações da fonte de alimentação. O maior desvio da corrente é de 570 ppm/V. Também foi simulada a sensibilidade da corrente de saída com a temperatura em função da variação da tensão da fonte de alimentação. A sensibilidade com a temperatura se mantém aproximadamente constante, por volta de 3804 ppm/°C.

Figura 12 - Sensibilidade da corrente de saída com a tensão de alimentação em função da temperatura

Fonte: Elaborada pelo autor.

Para fornecer uma melhor representatividade das diferenças que podem ser observadas após a fabricação dos dispositivos, podem ser utilizados modelos que representam as variações no processo de fabricação, conhecidos como *corners* da tecnologia, que resultam em dispositivos com resposta mais lenta ou rápida que o caso típico. Na Tabela 3 são definidos os modelos utilizados para cada dispositivo.

| Tabela 3 | Modelos dos corners da tecnologia |

|----------|-----------------------------------|

| Modelo   | Descrição                         |

| tt       | NMOS típico e PMOS típico         |

| ss       | NMOS lento e PMOS lento           |

| sf       | NMOS lento e PMOS rápido          |

| fs       | NMOS rápido e PMOS lento          |

| ff       | NMOS rápido e PMOS rápido         |

| tt_res   | Resistor típico                   |

| ss_res   | Resistor lento                    |

| ff res   | Resistor rápido                   |

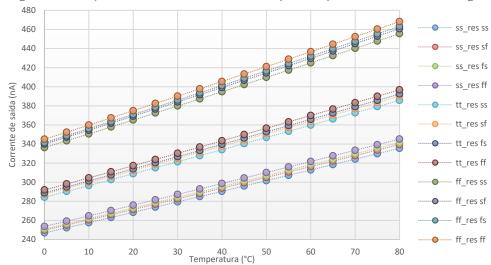

Nas curvas da Figura 13 foi simulada a variação da corrente de saída com a temperatura para cada *corner* do resistor e para os *corners* dos transistores com exceção do caso típico. Vemos que o dispositivo que causa a maior variação na corrente é o resistor, chegando a desviar 18.3 % em relação ao caso típico. Uma forma de corrigir pós-fabricação esta variação é através da utilização de chaves controladas por palavras lógicas que conectam ou desconectam pequenas resistências em série com *Rx* para corrigir a corrente, lembrando que as resistências das chaves incluídas afetarão o desempenho. Outra forma, como mostrado em [12], consiste em usar configurações que associam resistores com variações complementares resultando em um resistor compósito que apresenta baixa variação com o processo de fabricação. Contudo, como o objetivo é obter variação aproximadamente linear com a temperatura, vemos que todas as curvas cumprem esse requisito.

Figura 13 Variação da corrente de saída com a temperatura para os corners da tecnologia

A sensibilidade com a tensão da fonte de alimentação para cada variação do processo é mostrada na Figura 14. Vemos que as maiores variações ocorrem nos extremos da temperatura, com variação máxima de 788 ppm/V.

Figura 14 Sensibilidade da corrente de saída com a fonte de alimentação nos corners da tecnologia

Fonte: Elaborada pelo autor.

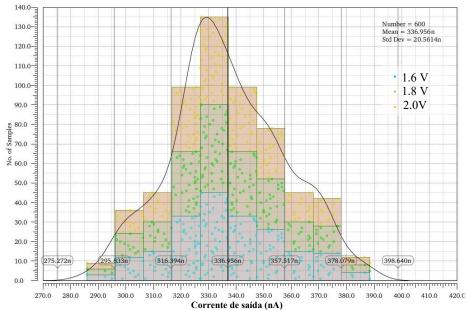

Para verificar os efeitos do descasamento entre os dispositivos, supondo processo típico, foi feita a simulação de Monte Carlo. Na Figura 15 está o histograma obtido, onde o eixo horizontal representa a corrente de saída e o vertical o número de amostras, após 200 iterações para cada tensão de alimentação de 1.6, 1.8 e 2.0 V. O valor médio da corrente é de 336.96 nA, com desvio padrão de 20.56 nA.

Figura 15 Simulação de Monte Carlo da corrente de saída

### 2.6 LEIAUTE

Para definir o leiaute a fim de reduzir o descasamento entre os dispositivos, em [15] são definidas algumas técnicas gerais. Dentre elas, para o leiaute da fonte de corrente, foram usadas para os dispositivos casados as técnicas de: manter transistores com a mesma largura e comprimento do canal; usar dimensões maiores que as mínimas; orientar os transistores na mesma direção; manter os dispositivos próximos e na forma mais compacta quanto for possível; além de não colocar contatos ou rotear metais sobre a área ativa na porta dos transistores; manter os dispositivos casados no mesmo eixo de simetria; dividir transistores em pares para arranjar os dispositivos de forma interdigitada e conectar as portas dos transistores com metal e não com polisilício.

Na Figura 16 é mostrado o leiaute desenvolvido, evidenciando os dispositivos que foram divididos parar melhorar a simetria vertical.

NC1 NC2 N2 N2 RX

Figura 16 Leiaute desenvolvido da fonte de corrente autopolarizada

#### **3 OSCILADOR EM ANEL**

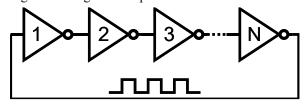

O oscilador em anel é geralmente composto por um número ímpar de inversores, conectados em série, como mostrado na Figura 17.

Figura 17 Diagrama simplificado do Oscilador em anel

Fonte: Elaborada pelo autor.

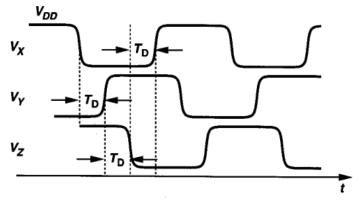

Quando a saída do inversor 1 fica em nível lógico alto, o inversor 2 recebe o nível alto na entrada e, após o atraso de propagação devido às capacitâncias associadas ao inversor, este apresenta nível lógico baixo na saída que é recebido pelo inversor 3 que por sua vez, após o atraso de propagação, apresenta nível alto na saída e assim o sinal vai se propaga no anel de inversores<sup>[16]</sup>. Este comportamento é mostrado na Figura 18, onde  $T_D$  é o tempo de propagação.

Figura 18 Propagação do sinal no oscilador em anel

Fonte: [16]

#### 3.1 TOPOLOGIA

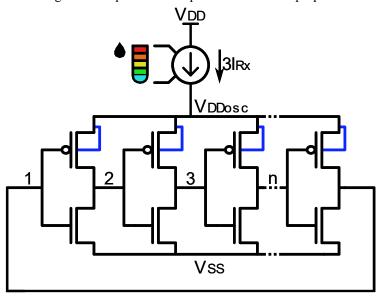

A partir do oscilador em anel convencional, com funcionamento amplamente conhecido na literatura<sup>[17]</sup> [18] [19], o diagrama do oscilador em anel proposto é mostrado na Figura 19. O substrato dos transistores PMOS dos inversores no oscilador em anel foi ligado ao terminal de fonte e não à fonte de alimentação, de forma que a amplitude de oscilação fica

limitada a esta tensão de alimentação local, com menor sensibilidade com a fonte de alimentação. A frequência de oscilação é dada pela expressão (14), onde N representa o número de estágios do inversor,  $C_L$  é a capacitância nodal,  $V_{DDosc}$  é a tensão de alimentação local e a corrente de polarização do oscilador é  $I_{bias} = 3I_{R_X}$ .

$$f_{osc} = \frac{I_{Bias}}{NC_L V_{DDosc}} \tag{14}$$

Figura 19 Esquemático simplificado do CSRO proposto

Fonte: Elaborada pelo autor.

Nesta topologia, ao fornecer a corrente da SBCS projetada com baixa dependência da fonte de alimentação e variação aproximadamente linear com a temperatura, obtemos a frequência de oscilação como função (quase) linear da temperatura. Substituindo a expressão (6) na expressão anterior, obtemos que

$$f_{osc} = \frac{3I_{Rx}}{NC_L V_{DDosc}} = \frac{3\phi_t lnK}{R_X NC_L V_{DDosc}} = \frac{3k_B lnK}{qR_X NC_L V_{DDosc}} T$$

(15)

onde *T* é a temperatura em graus kelvin.

#### 3.2 DIMENSIONAMENTO

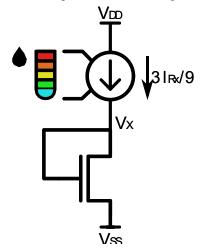

Como os parâmetros referentes à corrente na expressão (15) já foram definidos no projeto da SBCS, ainda é necessário estimar a capacitância  $C_L$  associada a cada estágio e a tensão  $V_{DDosc}$  que representa a alimentação atenuada do oscilador em anel e estimar o tamanho necessário dos transistores para obter esta capacitância.

Isolando  $C_L V_{DDosc}$  em (15), conforme mostrado em (16), obtemos que este produto deve ser igual a 37.7 fC aos 40 °C, utilizando 9 estágios para obter um compromisso entre o atraso médio e a área ocupada.

$$C_L V_{DDosc} = \frac{3I_{Rx}}{Nf_{osc}} = \frac{339 \text{ nA}}{9*1 \text{MHz}} = 37.7 \text{ fC}$$

(16)

Para estimar o valor de  $V_{DDosc}$ , consideramos que a corrente média em cada estágio é a corrente fornecida pela SBCS dividida pela quantidade de estágios, no caso, 9. Assim, podemos estimar qual a tensão entre porta e fonte que resulta nesta corrente média. Para isto, utilizamos o esquemático da Figura 20, onde a tensão  $V_X$ , considerando os transistores corretamente balanceados, é aproximadamente igual à metade de  $V_{DDosc}$ .

Figura 20 Esquemático simplificado de um estágio estático do inversor

Fonte: Elaborada pelo autor.

Aplicando UICM<sup>[10]</sup> para o transistor NMOS da Figura 20, conforme a expressão (1), obtemos:

$$V_P - 0 = n \,\phi_t \left[ \sqrt{1 + I_F/I_S} - 2 + \ln(\sqrt{1 + I_F/I_S} - 1) \right] \tag{17}$$

Para a tensão  $V_P$ , utilizamos a aproximação  $V_P\cong (V_X-V_{T0})/n$ , onde n é o fator de inclinação,  $V_X$  é a tensão entre a porta e o substrato e  $V_{T0}$  é a tensão de limiar no equilíbrio<sup>[10]</sup>.

Assumindo que o transistor opera em inversão fraca, com  $I_S \gg I_F$ , podemos utilizar a aproximação  $\sqrt{1+X} \approx 1 + \frac{X}{2}$  em (21), conforme é mostrado em (18), onde  $i_f = I_F/I_S$  é o nível de inversão direto normalizado pela corrente específica.

$$V_X = V_{T0} + n\phi_t \left[ -1 + \ln\left(\frac{i_f}{2}\right) \right] \tag{18}$$

Adicionalmente, vemos em (18) que  $V_X$  deve variar de forma aproximadamente linear com a temperatura pois  $V_{T0}$  varia linearmente com T. Caso esta tensão diminua com a temperatura, isto pode aumentar ainda mais a sensibilidade da frequência com a temperatura sem comprometer a linearidade.

Adotando  $i_f = 0.1$  (inversão fraca), extraindo da tecnologia  $V_{T0} = 471 \text{mV}$  e n = 1.48 aos 40 °C, obtemos  $V_X = 312 \text{ mV}$ . Assim, temos que  $V_{DDosc} \cong 2V_X = 632 \text{ mV}$ . Substituindo este valor em (19), obtemos que a capacitância necessária por estágio é  $C_L = \frac{37.7f}{632m} = 60.5 \text{ fF}$ .

Segundo [20], as capacitâncias associadas ao potencial  $V_{out}$  entre os dois inversores cascateados são sumarizadas na Figura 21. Estas capacitâncias dependem de parâmetros da tecnologia e do dimensionamento dos transistores. A capacitância entre porta e dreno de  $M_1$  e  $M_2$  é representada por  $C_{gd}$ , entre dreno e substrato é  $C_{db}$ , entre porta e fonte  $C_{g3}$  e, por fim, a capacitância da interconexão é representada por  $C_w$ , onde o número do índice indica qual é o transistor referido.

$V_{DD}$

Figura 21 Capacitâncias associadas a dois inversores cascateados

Fonte: [20]

Desta forma, a capacitância total  $C_L$  é a soma destas capacitâncias, conforme a expressão (19).

$$C_L = C_{gd1} + C_{gd2} + C_{db1} + C_{db2} + C_{g3} + C_{g4} + C_w$$

(19)

Contudo, como os inversores são projetados idênticos e, para balancear os transistores, os dispositivos PMOS são X vezes maiores que os NMOS (com  $X = \frac{W_p/L_p}{W_n/L_n}$  obtido entre 3 e 4 por meio de simulação para a tecnologia utilizada), as capacitâncias de cada transistor vão ser

escaladas por este mesmo fator<sup>[20]</sup>. Esta aproximação é mostrada na expressão (24), onde  $C_{dn1}$  é a capacitância equivalente de difusão do transistor NMOS do primeiro inversor,  $C_{gn2}$  é a capacitância de porta do segundo inversor e  $C_w$  a capacitância da interconexão.

$$C_L = (1+X)(C_{dn1} + C_{gn2}) + C_w$$

(20)

De [20], obtemos  $C_{dn1} = W_n L_n C_J + (2L_n + W_n) C_{JSW}$  e  $C_{gn2} = W_n L_n C_{ox} + 2C_o W_n$ , onde  $C_J$  é a capacitância de junção por área,  $C_{JSW}$  é a capacitância de junção por perímetro,  $C_{ox}$  é a capacitância do óxido por área de porta,  $C_o$  é a capacitância de sobreposição de porta e X = 4, com valores obtidos da tecnologia.

Aplicando

$$i_f = 0.1$$

,  $I_{SH} = 130$  nA e  $I_D = 339$ nA/9 em (13), obtemos (21).

$$\frac{W_n}{L_n} = \frac{339n/9}{130n*0.1} \approx 3$$

(21)

Utilizando a expressão (21) em (20) e considerando que  $C_L=60.5\,f$ F, obtemos que  $W_n=1800\,\mathrm{nm}$  e  $L_n=600\,\mathrm{nm}$ .

Porém, por meio de simulações, verificamos que o valor de  $V_{DDosc}$  é de aproximadamente 447 mV, o que altera a capacitância necessária  $C_L$  para 84 fF. Repetindo as mesmas iterações, obtemos  $W_n=2160$  nm e  $L_n=722$  nm. O valor da largura do canal foi mantido, mas o comprimento do canal foi aproximadamente dobrado para diminuir a sensibilidade com a fonte de alimentação, o que resulta no nível de inversão  $i_f=0.2$ , ainda considerado inversão fraca e relação de aspecto  $\frac{W_n}{L_n}=\frac{2.16\mu\text{m}}{1.44\mu\text{m}}=\frac{12}{8}$ .

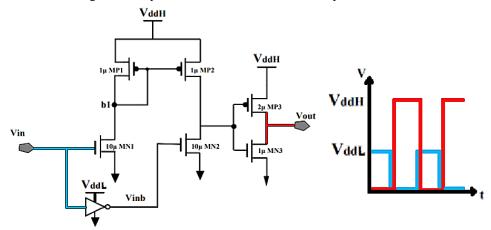

#### 3.3 LEVEL SHIFTER

Ao polarizar o oscilador com fonte de corrente, a excursão da oscilação fica limitada a  $V_{DDosc}$ . Para obter excursão do sinal igual à tensão de alimentação  $V_{DD}$ , foi utilizado um circuito conhecido como *Level Shifter* (LS). Algumas das principais topologias de LS, apresentadas em [21], são: a configuração com polarização cruzada ou com espelho de corrente que necessitam do sinal com excursão limitada e de seu complemento, o que impacta em um inversor adicional para obter o complemento; e a configuração que não necessita obter o complemento do sinal, mas pode ter correntes de fuga significativas se a diferença entre as tensões de alimentação for relativamente elevada.

Figura 22 Esquematico do Level Shifter com espelho de corrente

Fonte: Adaptado de [21].

Levando em conta estas configurações e suas limitações, foi verificado que a configuração com polarização cruzada necessita de transistores NMOS maiores em relação a topologia com espelho de corrente, devido à baixa amplitude do sinal de entrada. Desta forma, foi escolhida a segunda topologia, com espelho de corrente, mostrada na Figura 22, devido à capacidade de obter uma boa performance mesmo tendo uma diferença entre as fontes de alimentação relativamente elevada. Quando  $V_{in}$  está em nível lógico baixo,  $M_{N1}$  fica em corte e, caso  $V_{ddL}$  seja suficiente para que  $M_{N2}$  entre em saturação,  $M_{N2}$  conduz, deixa nível baixo na entrada do inversor formado por  $M_{N3}$  e  $M_{P3}$ , e então,  $V_{out}$  é igual a  $V_{ddH}$ . Por outro lado, quando  $V_{in}$  está em nível lógico alto, o que corresponde à tensão de alimentação  $V_{ddL}$ , caso seja suficiente para  $M_{N1}$  entrar em saturação, o transistor  $M_{N1}$  conduz,  $M_{N2}$  fica em corte e o espelho de corrente carrega com nível lógico alto o inversor formado por  $M_{N3}$  e  $M_{P3}$ , e assim,  $V_{out}$  fica em nível baixo.

A configuração da Figura 22 necessita de um inversor com a mesma alimentação  $V_{DDosc}$ . Para reduzir o desbalanceamento entre os estágios foi adicionada uma cópia deste inversor em cada estágio, como mostrado na Figura 23. Dois inversores consecutivos são conectados ao LS, fornecendo sinais com diferenças de fase de cerca de  $160^{\circ}$  (devido ao atraso do estágio, o que altera levemente o ciclo de trabalho, não relevante para a medida da frequência).

Para reduzir o impacto das capacitâncias e da corrente destes inversores no oscilador, os transistores PMOS e NMOS foram dimensionados com largura mínima, 220 nm, e com comprimento relativamente maior, 1260 nm. Para os transistores do LS foram adotados a largura mínima de 220 nm e comprimento do canal de 1800 nm. No inversor de saída foram colocados transistores em série para aumentar ainda mais o comprimento efetivo do canal e reduzir a corrente consumida. Este dimensionamento foi obtido por meio de simulações, mantendo um compromisso entre o consumo de corrente e área ocupada.

#### 3.4 BUFFER

Por fim, para possibilitar as medições do TCO, é necessário projetar um *buffer* capaz de carregar a capacitância de saída, de cerca de 20 pF. O *buffer*, em geral, consiste em uma cadeia de inversores em que a largura de cada estágio é aumentada por um fator constante até ser capaz de acionar a capacitância desejada dentro de um período de tempo razoável<sup>[22] [23]</sup>. No caso deste projeto foi verificado, por meio de simulação, que adicionando apenas mais um inversor com comprimento do canal mínimo de 180 nm e largura do canal maior que 5  $\mu$ m é possível carregar a capacitância de saída de 20 pF. Contudo, para garantir o funcionamento pleno do *buffer* e aproveitando a área disponível que restou no leiaute, este inversor foi dimensionado com relações de aspecto de  $\frac{W}{L} = \frac{9.72 \mu m}{0.18 \mu m} = \frac{54}{1}$ , iguais para os transistores PMOS e NMOS, atingindo o comportamento desejado de forma satisfatória, mas consumindo muito mais corrente que o restante do TCO completo.

O dimensionamento dos transistores do oscilador em anel, do LS e do *buffer* é mostrado na Tabela 4.

| Tabela 4 Dimensionamento do CSRO |                   |                     |

|----------------------------------|-------------------|---------------------|

| Transistor                       | NMOS              | PMOS                |

|                                  | W/L (µm/µm)       | $W/L (\mu m/\mu m)$ |

| Inversor                         | 2.16              | 8.64                |

| principal                        | $\overline{1.44}$ | $\overline{1.44}$   |

| Inversor de                      | 0.22              | 0.22                |

| entrada do LS                    | 1.26              | 1.26                |

| LS                               | 0.22              | 0.22                |

|                                  | 1.8               | 1.8                 |

| Inversor do                      | 9.72              | 9.72                |

| Buffer                           | 0.18              | $\overline{0.18}$   |

Tabela 4 Dimensionamento do CSRO

### 3.5 SIMULAÇÕES DO CSRO

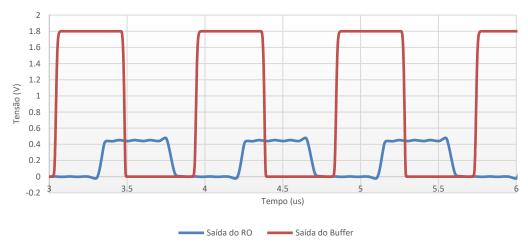

Utilizando o dimensionamento apresentado, na Figura 24 estão as tensões de saída do CSRO aos 40 °C com a fonte de alimentação em 1.8 V, obtidas através da simulação do esquemático. A curva em azul mostra a tensão de um dos 9 estágios de inversores, oscilando com amplitude de aproximadamente 450 mV. Esta tensão é então elevada pelo LS para oscilar com a amplitude da fonte de alimentação. A saída do LS, por sua vez, é enviada para o *buffer* de saída, resultando na curva em vermelho, da tensão na capacitância de carga de 20 pF.

Figura 24 Tensões na saída de um inversor do CSRO e na capacitância de carga.

Fonte: Elaborada pelo autor.

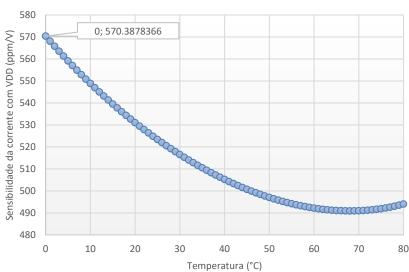

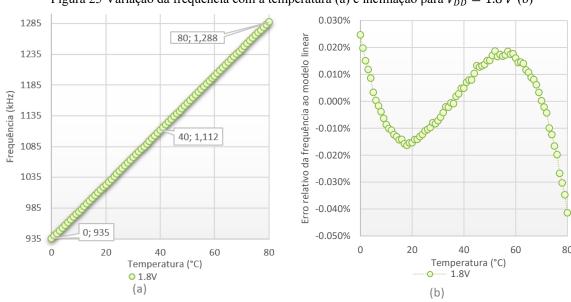

Na Figura 25 (a) é mostrada a variação da frequência em função da temperatura para o caso de parâmetros típicos. A tensão de alimentação é mantida em 1.8 V e a temperatura varia de 0 até 80 °C, com sensibilidade à temperatura da ordem de 3964 ppm/°C. A frequência de oscilação está cerca de 10 % acima de 1 MHz em 40 °C, mas, como será posteriormente verificado, é reduzida após a extração das capacitâncias parasitas no leiaute e ficando mais

próxima da desejada, de 1 MHz a 40 °C. Em (b) é mostrado o erro relativo ao modelo linear. Vemos que a linearidade está aproximadamente equilibrada perto de 40 °C, mas é deteriorada ao se aproximar da temperatura máxima.

Figura 25 Variação da frequência com a temperatura (a) e inclinação para  $V_{DD}=1.8\ V$  (b)

Fonte: Elaborada pelo autor.

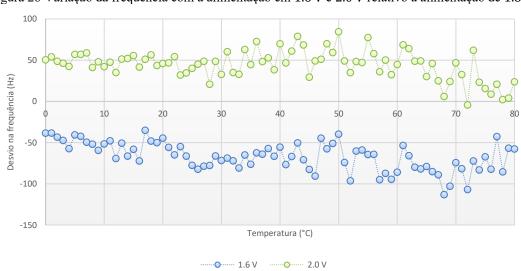

Como o desvio da frequência quando a tensão de alimentação varia não fica visível no mesmo gráfico de variação com a temperatura, na Figura 26 está o desvio na frequência relativo à alimentação de 1.8 V quando a tensão de alimentação é de 1.6 V e 2.0 V. O desvio máximo é de 113 Hz aos 68 °C em relação a 1.8 V, cerca de 0.009 %.

Figura 26 Variação da frequência com a alimentação em 1.6 V e 2.0 V relativo à alimentação de 1.8 V

Na Figura 27, em (a) vemos a sensibilidade da frequência com a temperatura para diferentes tensões de alimentação. Esta sensibilidade se mantém aproximadamente constante, com menor valor igual a 3964 ppm/°C em 2.0 V. Já em (b), temos a sensibilidade da frequência com a tensão da fonte de alimentação para diferentes temperaturas, onde a maior variação é de 358 ppm/V aos 45 °C. Assim, vemos que a cada 1 °C de variação, a frequência muda quase 4000 ppm frente ao desvio relativo à tensão de alimentação igual a 144 ppm (para 400 mV de variação da fonte). Portanto, uma variação da tensão de alimentação entre 1.6 V e 2.0 V irá corresponder a um erro de 0.036 °C (144ppm/4000ppm/°C).

Figura 27 Variação da sensibilidade do coeficiente de temperatura em função de  $V_{DD}$  (a) e sensibilidade à tensão de alimentação (b)

Fonte: Elaborada pelo autor.

Contudo, este funcionamento corresponde apenas ao caso típico do processo. Como o objetivo é obter variação da frequência de forma aproximadamente linear com a temperatura e com baixa dependência da fonte de alimentação, o próximo passo é verificar a linearidade da variação da frequência e a dependência com a fonte em todos os corners do processo, estimando o pior cenário.

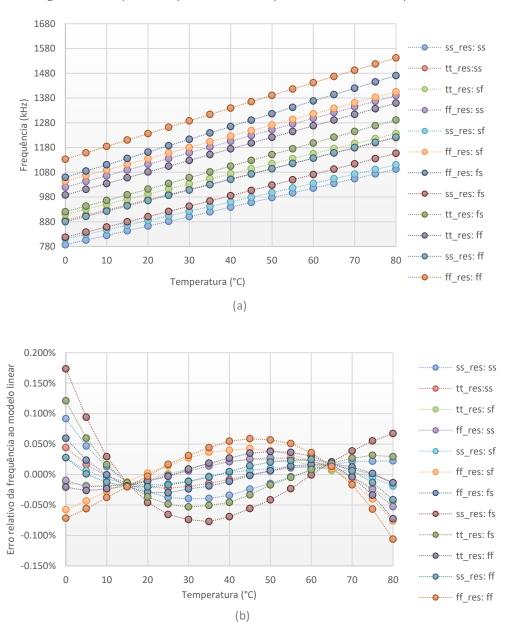

Dessa forma, na Figura 28 em (a) é obtida a variação da frequência com a temperatura nos corners do processo. Em (b) observamos que todas as curvas apresentam excelente linearidade, com erro relativo ao modelo linear menor que 0.2 %.

Figura 28 Variação da frequência com a temperatura nos corners do processo

Na Figura 29 é mostrada a sensibilidade da frequência com a fonte de alimentação nos corners do processo para 3 temperaturas de interesse, 0, 40 e 80 °C. Desta figura, vemos que as variações de frequência com a tensão da fonte são menores que 600 ppm/V.

Figura 29 Sensibilidade da frequência com a alimentação em 0, 40, 80°C nos corners do processo

Considerando um cenário de produção de alguns chips para testagem e obtenção do erro na medida da temperatura, uma forma de calibrar a variação com a temperatura é considerando um modelo linear a partir de medidas feitas, medindo ao menos dois pontos e traçando uma reta sobre estes pontos. Utilizando as curvas em (a) da Figura 28 e traçando uma reta sobre dois pontos para cada curva, obtemos o erro em relação ao modelo linear mostrado na Figura 30, onde os dois pontos de referência em (a) foram os extremos da temperatura, obtendo erro de  $\pm 0.44$  °C; em (b) foram 10 e 70 °C, resultando em menor erro de cerca de  $\pm 0.30$  °C; e, por fim, em (c) foram 20 e 60 °C, onde o erro nos extremos é maior mas entre 10 e 70 °C é menor que  $\pm 0.20$  °C. Para calcular o erro da temperatura em relação ao modelo linear, foi feita a aproximação linear da temperatura pela frequência e subtraído a temperatura estimada pelo modelo linear da temperatura medida nos pontos.

0.50 •···· ss\_res: ss 0.40 ··· tt\_res:ss 0.30 Erro na temperatura (°C) tt\_res: sf 0.20 ff\_res: ss 0.10 ss\_res: sf 0.00 ··· ff\_res: sf -0.10 ··· ff\_res: fs -0.20 ··· ss\_res: fs -0.30 ··· tt\_res: fs -0.40 -0.50 •···· tt\_res: ff 0 20 40 60 • ss\_res: ff Temperatura (°C) ••···· ff\_res: ff (a) 0.40 ss\_res: ss 0.30 tt\_res:ss Erro na temperatura (°C) 0.20 tt\_res: sf ff\_res: ss 0.10 ss\_res: sf 0.00 ff\_res: sf -0.10 ff\_res: fs -0.20 ss\_res: fs -0.30 tt\_res: fs -0.40 •••• tt\_res: ff 0 60 20 40 Temperatura (°C) ····• ss\_res: ff ····• ff\_res: ff (b) 0.60 ··· ss\_res: ss 0.40 ·· tt\_res:ss Erro na temperatura (°C) ··· tt\_res: sf 0.20 - ff\_res: ss ss\_res: sf 0.00 ··· ff\_res: sf -0.20 ··· ff\_res: fs ··· ss\_res: fs -0.40 tt\_res: fs ···· tt\_res: ff -0.60 0 20 60 40 ··· ss\_res: ff Temperatura (°C) •···· ff\_res: ff (c)

Figura 30 Erro da temperatura em relação ao modelo linear

Outra característica importante do projeto é a corrente média consumida. Por projeto, a SBCS consome ao menos  $2I_{Rx}$  internamente e entrega  $3I_{Rx}$  para o CSRO, totalizando ao menos 650nA aos 80 °C. O restante vem do LS e do *buffer* de saída. Como a corrente do *buffer* é muito maior devido à necessidade de carregar 20pF na saída, na Figura 31 em (a) está a corrente consumida no *buffer* e em (b) a corrente consumida no restante do circuito, ambas para todos os corners da tecnologia. Vemos assim que corrente máxima consumida no *buffer* é de 86.3  $\mu$ A e no restante do TCO é de 1.20  $\mu$ A, para a maior temperatura e maior tensão de alimentação.

90 1250 2; 86.34623695 2; 1208.491926 1200 ss res: ss ss\_res: ss 80 1150 tt res:ss tt\_res:ss 1100 Corrente no buffer (uA) 70 (nA) 1050 ·· ss res:sf 001 1000 ··· tt\_res:sf 60 950 ··· ff res:sf ff\_res:sf 900 tt\_res:fs tt res:fs 50 850 800 ss res:fs 40 750 tt res:ff tt\_res:ff 700 ··· ff res:fs ff res:fs 650 ··· ff res:ff ff\_res:ff 1.6 1.7 1.8 1.9 1.7 1.6 1.8 VDD (V) VDD (V) · ss\_res:ff ···· ss\_res:ff (a) (b)

Figura 31 Corrente consumida em função da temperatura no buffer (a) e no restante do TCO (b)

Fonte: Elaborada pelo autor.

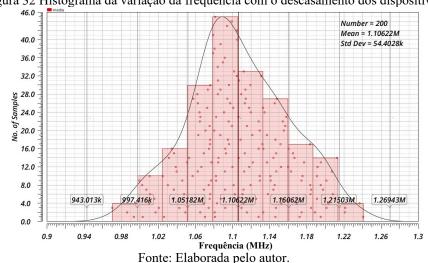

Por fim, é analisado o efeito do descasamento dos dispositivos, considerando o processo típico, através da simulação de Monte Carlo mostrada na Figura 32, obtendo a frequência média de 1.11 MHz e desvio padrão de 0.054 MHz aos 40 °C, evidenciando a necessidade de calibração do TCO para obter a precisão desejada.

Figura 32 Histograma da variação da frequência com o descasamento dos dispositivos

#### 3.6 LEIAUTE

Como a principal responsável pela variação da frequência com a temperatura e baixa sensibilidade com a fonte é a SBCS, o leiaute do CSRO necessita de menos considerações. A principal diferença após o leiaute do CSRO são as capacitâncias parasitas que serão adicionadas a cada estágio, reduzindo a frequência em todo o intervalo. Para reduzir os efeitos do descasamento e das capacitâncias de interconexão, os estágios inversores do CSRO foram conectados o mais próximo possível.

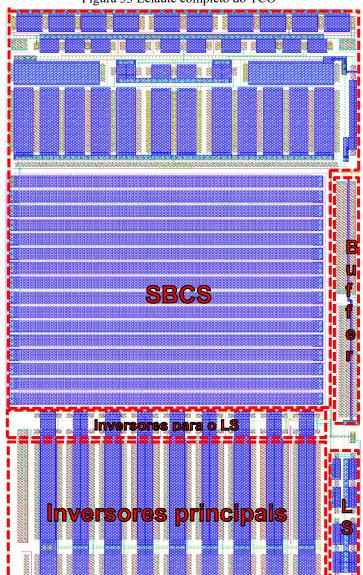

Na Figura 33 está o leiaute completo do TCO, com medida horizontal de 30  $\mu$ m e vertical de 50  $\mu$ m, compreendendo, portanto, área de 1500  $\mu$ m<sup>2</sup>.

Figura 33 Leiaute completo do TCO

### 4 RESULTADOS OBTIDOS APÓS O LEIAUTE

Após completar o leiaute do TCO, foram verificadas as regras de projeto através do DRC e, em seguida foi verificada a compatibilidade com o circuito esquemático através do LVS e, por fim, extraídas as resistências e capacitâncias parasitas associadas aos dispositivos e interconexões do projeto. Então, foi verificado o desempenho do circuito extraído, conforme mostrado nas simulações a seguir.

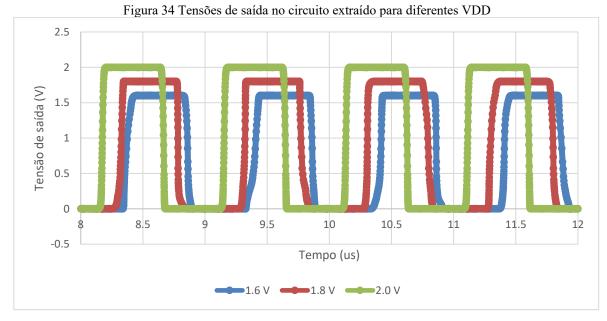

Como são adicionadas novas impedâncias parasitas aos dispositivos, é importante verificar se o *buffer* continua funcionando da forma desejada, possibilitando a medida da frequência. Na Figura 34, vemos a tensão de saída do *buffer* carregando a capacitância de carga de 20 pF quando a fonte de alimentação é igual a 1.6 V, 1.8 V ou 2.0 V. Vemos que o *buffer* é capaz de carregar/descarregar adequadamente a impedância de carga na frequência de oscilação.

Fonte: Elaborada pelo autor.

A variação da frequência com a temperatura para tensões de alimentação de 1.6 V, 1.8 V e 2.0 V para o circuito extraído é mostrada na Figura 35. Vemos que, conforme esperado, a frequência diminuiu em todas as temperaturas em relação à simulação antes da extração, mostrada na Figura 25, onde a frequência varia de 935 até 1285 kHz. Por sua vez, na simulação pós-leiaute a frequência de oscilação varia de 855 até 1185 kHz. O erro em relação ao modelo linear também aumentou, com o valor máximo, em módulo, de 0.04 % para 0.08 %. Vemos

que os pontos onde o erro é mínimo foram deslocados para a direita, de 5, 35 e 70 °C para 10, 45, 80 °C. Isto indica que a linearidade foi degradada para temperaturas menores e ampliada para temperaturas maiores. Aos 40 °C, a frequência típica é de 1.02 MHz com  $V_{DD}$  de 1.8 V.

1205 0.08% Erro relativo da frequência em relação 1155 0.06% 1105 Frequência (kHz) 0.04% ao modelo linear 1055 0.02% 1005 40; 1,021 955 0.00% 905 -0.02% 855 0 40 60 20 80 -0.04% Temperatura (°C) Temperatura (°C) --- 1.6 V 1.8 V --- 1.6 V 1.8 V (b) (a)

Figura 35 Variação da frequência extraída com a temperatura para diferentes valores de  $V_{DD}$  (a) e erro relativo ao modelo linear (b)

Fonte: Elaborada pelo autor.

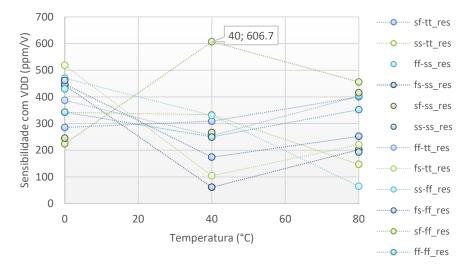

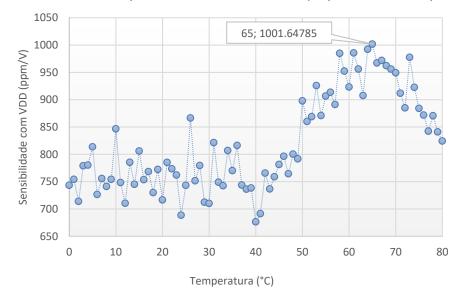

Em relação à sensibilidade da frequência com a fonte de alimentação, na Figura 36 vemos um aumento considerável em relação aos resultados obtidos antes da extração na Figura 27 em (b). A variação máxima passou de 358 ppm/V em 45 °C para 1002 ppm/V em 65 °C. Outro fato verificado foi que no leiaute alguns dispositivos tiveram parâmetros alterados em relação aos simulados, como no caso de transistores compartilhando a mesma difusão de fonte em que mudam parâmetros das dimensões efetivas como o perímetro e área, alterando levemente a resposta dos dispositivos e tendo o comportamento deslocado em relação ao simulado previamente.

Já a sensibilidade com a temperatura se mantém aproximadamente constante com  $V_{DD}$ , com valor mínimo de 4028 ppm/°C. Isto resulta em um erro máximo na medida da temperatura de  $\pm 0.1$  °C devido à fonte de alimentação.

Figura 36 Sensibilidade da frequência com a tensão de alimentação para diferentes temperaturas

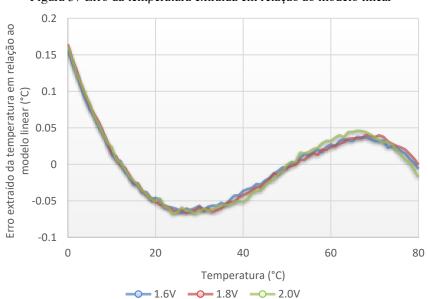

O erro da temperatura em relação ao modelo linear é mostrado na Figura 37. Acontece o mesmo que no erro relativo à frequência, o ponto de operação foi deslocado para a direita e assim aumentou a erro para as menores temperaturas. O erro máximo do circuito extraído na medida de temperatura em relação ao modelo linear é de  $\pm 0.16$  °C para todo o intervalo de operação e menor que  $\pm 0.07$  °C no intervalo de 6 até 80 °C.

Figura 37 Erro da temperatura extraída em relação ao modelo linear

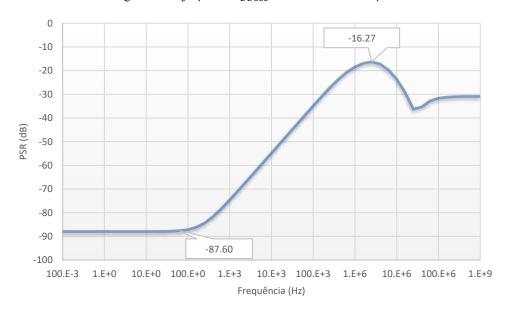

Por fim, foi verificada a rejeição de  $V_{DDosc}$  em relação a variações da tensão de alimentação, conforme mostrado na Figura 38. Deve ser observado que no projeto do TCO foram consideradas apenas variações de nível contínuo da fonte de alimentação e não ondulações no sinal. A Figura 38 mostra que até 100 Hz a atenuação de variações em  $V_{DD}$  sobre  $V_{DDosc}$  se mantém em cerca de 88 dB, atingindo valor mínimo de 16 dB para algumas unidades de MHz.

Figura 38 Rejeição de  $V_{DDosc}$  à fonte de alimentação

# 5 CONSIDERAÇÕES FINAIS E TRABALHOS FUTUROS

Seguindo a metodologia adotada para o desenvolvimento do projeto, foi descrito o funcionamento da fonte de corrente autopolarizada, com considerações sobre a escolha do resistor e a necessidade de inicialização, o dimensionamento dos dispositivos e as estratégias de leiaute. Por meio de simulações antes da extração do leiaute, foi determinada a sensibilidade do sensor com a temperatura de 3804 ppm/°C frente a uma sensibilidade de 570 ppm/V com a fonte de alimentação e boa linearidade, com erro relativo ao modelo linear menor que 0.25 %. Também foi verificado que a sensibilidade à tensão de alimentação nos corners da tecnologia é menor que 788 ppm/V.

Foi verificado que o uso do resistor na SBCS produz uma variação importante da corrente com o processo de fabricação, além de consumir área elevada para obter correntes reduzidas. Levando isso em consideração, alguns trabalhos futuros propostos incluem adicionar a possibilidade de calibrar essa resistência para obter a corrente desejada e, em consequência, ajustar a frequência nominal do CSRO. Isto pode ser feito incluindo resistências menores e utilizando palavras lógicas para fazer associações e obter a resistência desejada ou, também, utilizar a técnica apresentada de resistores compósitos, mas com variações opostas com o processo de fabricação. Outra alteração possível seria adotar outra topologia de fonte de corrente proporcional à temperatura absoluta que não utilize resistores. Para reduzir ainda mais o descasamento, uma sugestão é a de utilizar no leiaute dispositivos *dummy* e configurações de centroide comum para os espelhos de corrente e não apenas o leiaute interdigitado. Contudo, com a topologia utilizada, o desempenho obtido foi suficiente para alcançar os objetivos propostos.

Para o oscilador em anel também foram descritos o funcionamento e o dimensionamento do oscilador, assim como o do *Level Shifter* e do *Buffer* de saída, necessários para possíveis testes futuros, caso o TCO seja integrado.

Após a extração de impedâncias parasitas do leiaute, o desempenho do oscilador simulado continuou indicando boa linearidade, com sensibilidade à temperatura da ordem de 4000 ppm/°C e uma sensibilidade de 1002 ppm/V à tensão de alimentação.

Por fim, o TCO desenvolvido apresentou uma área de 30  $\mu$ m por 50  $\mu$ m, totalizando 1500  $\mu$ m<sup>2</sup>. O erro máximo devido a variações de 1.6 V a 2.0 V na fonte de alimentação é de  $\pm 0.1$  °C enquanto o desvio máximo em relação ao modelo linear é de  $\pm 0.16$  °C, totalizando aproximadamente  $\pm 0.3$  °C de erro, considerando que os erros são independentes um do outro.

O leiaute desenvolvido possibilita a fabricação do TCO na tecnologia CMOS de 0.18 µm para comprovação do seu real funcionamento no futuro.

Como trabalhos futuros sugerimos estudos e realização de métodos de calibração, tanto no valor da frequência a uma dada temperatura quanto no ajuste do coeficiente de temperatura e, adicionalmente, estudos sobre o impacto do ruído *jitter* no oscilador em anel.

## REFERÊNCIAS

- [1] TEXAS INSTRUMENTS (Dallas). **The Engineer's Guide to Temperature Sensing**. 2019. Disponível em: https://www.ti.com/lit/eb/slyy161/slyy161.pdf. Acesso em: 17

jun. 2021.

- [2] IKEUCHI, Motoaki; FURUKAWA, Tomozo; MATSUMOTO, Goro. A Linear Temperature-to-Frequency Converter. **IEEE Transactions on Instrumentation and Measurement**, v. 24, n. 3, p. 233-235, 1975. Institute of Electrical and Electronics Engineers (IEEE). http://dx.doi.org/10.1109/tim.1975.4314416.

- [3] MAKINWA, Kofi A. A.; SNOEIJ, Martijn F.. A CMOS Temperature-to-Frequency Converter with an Inaccuracy of Less Than ±0.5°C (3σ) From −40°C to 105°C. **IEEE Journal of Solid-State Circuits**, v. 41, n. 12, p. 2992-2997, dez. 2006. Institute of Electrical and Electronics Engineers (IEEE). http://dx.doi.org/10.1109/jssc.2006.884865.

- [4] UENO, Ken; ASAI, Tetsuya; AMEMIYA, Yoshihito. Temperature-to-frequency converter consisting of subthreshold MOSFETs circuits for smart temperature-sensor LSIs. In: 2009 TRANSDUCERS International Solid-State Sensors, Actuators and Microsystems Conference. Denver: IEEE, 2009. p. 2433-2436.

- [5] CHOUHAN, Shailesh Singh; HALONEN, Kari. A Low Power Temperature to Frequency Converter for the On-Chip Temperature Measurement. **IEEE Sensors Journal**, v. 15, n. 8, p. 4234-4240, ago. 2015. Institute of Electrical and Electronics Engineers (IEEE). http://dx.doi.org/10.1109/jsen.2015.2414667.

- [6] CHIANG, Cheng-Ta; CHANG, Fu-Wen. A CMOS temperature difference to frequency converter with calibration circuits for environmental temperature difference monitoring applications. In: **2015 IEEE International Conference on Mechatronics and Automation (ICMA).** Beijing: IEEE, 2015. p. 1060-1064.

- [7] LI, Wenyuan; ZHOU, Dehua. 1.8V -0.18-µm CMOS Temperature Sensor with Frequency Output. In: **2018 IEEE Canadian Conference on Electrical & Computer Engineering (CCECE).** Quebec: IEEE, 2018. p. 1-4.

- [8] WANG, Hui; MERCIER, Patrick P.. A 763 pW 230 pJ/Conversion Fully Integrated CMOS Temperature-to-Digital Converter with +0.81 °C/-0.75 °C Inaccuracy. **IEEE Journal of Solid-State Circuits**, v. 54, n. 8, p. 2281-2290, ago. 2019. Institute of Electrical and Electronics Engineers (IEEE). http://dx.doi.org/10.1109/jssc.2019.2916418.

- [9] ANGEVARE, Jan A.; MAKINWA, Kofi A. A.. A 6800-μ² Resistor-Based Temperature Sensor with ±0.35 °C (3σ) Inaccuracy in 180-nm CMOS. **IEEE Journal of Solid-State Circuits**, v. 54, n. 10, p. 2649-2657, out. 2019. Institute of Electrical and Electronics Engineers (IEEE). http://dx.doi.org/10.1109/jssc.2019.2921450.

- [10] SCHNEIDER, Marcio Cherem; GALUP-MONTORO, Carlos. **CMOS Analog Design Using All-Region MOSFET Modeling**. New York: Cambridge University Press, 2010. 486 p.

- [11] BAKER, R. Jacob. **CMOS Circuit Design, Layout, and Simulation**. Piscataway: Wiley-IEEE Press, 2010. 1208 p.

- [12] GREGOIRE, B. Robert; MOON, Un-Ku. Process-Independent Resistor

Temperature-Coefficients using Series/Parallel and Parallel/Series Composite Resistors. In:

2007 IEEE International Symposium on Circuits and Systems. New Orleans: IEEE, 2007.

p. 2826-2829.

- [13] GRAY, Paul R.; HURST, Paul J.; LEWIS, Stephen H.; MEYER, Robert G.. Analysis and Design of Analog Integrated Circuits. 4. ed. New York: John Wiley & Sons, 2001.

- [14] OGUEY, H.J.; AEBISCHER, D.. CMOS current reference without resistance. **IEEE Journal of Solid-State Circuits**, v. 32, n. 7, p. 1132-1135, jul. 1997. Institute of Electrical and Electronics Engineers (IEEE). http://dx.doi.org/10.1109/4.597305.

- [15] HASTINGS, Alan. **The Art of Analog Layout**. 2. ed. New Jersey: Prentice Hall, 2005. 672 p.

- [16] RAZAVI, Behzad. **Design of Analog CMOS Integrated Circuits**. Boston: McGraw-Hill, 2001.

- [17] MONTASERI, Mohammad; NAIMI, Hossein. Novel power supply independent ring oscillator. In: **2010 Proceedings of the 9th Wseas Int. Conf. on Electronics Hardware Wireless and Optical Communications**, Cambridge: Wseas Press, 2010. p. 80-87.

- [18] PANYAI, Sahakoon; THANACHAYANONT, Apinunt. Design and realization of a process and temperature compensated CMOS ring oscillator. In: **2012 9th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology.** Phetchaburi: IEEE, 2012. p. 1-4.

- [19] MONTASERI, Mohammad Hassan; NAIMI, Hossein Miar. Power supply dependency reduction of Ring Oscillators using self biasing. In: **2010 2nd International**Conference on Mechanical and Electronics Engineering. Kyoto: IEEE, 2010. p. 72-76.

- [20] RABAEY, Jan M.; CHANDRAKASAN, Anantha P.; NIKOLIC, Borivoje. **Digital Integrated Circuits**. 2. ed. Nova Jersey: Prentice Hall, 2003. 761 p.