# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIAS DA COMPUTAÇÃO

José Luis Conradi Hoffmann

Optimizing Energy Consumption of Multicore Real-Time Embedded Systems using Machine Learning

# José Luis Conradi Hoffmann

# Optimizing Energy Consumption of Multicore Real-Time Embedded Systems using Machine Learning

Dissertação submetida ao Programa de Pós-Graduação em Ciências da Computação da Universidade Federal de Santa Catarina para a obtenção do Grau de Mestre em Ciência da Computação.

Orientador: Prof. Antônio A. M. Fröhlich, PhD.

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Hoffmann, José Luis Conradi

Optimizing Energy Consumption of Multicore Real-Time Embedded Systems using Machine Learning / José Luis Conradi Hoffmann ; orientador, Antônio Augusto Medeiros Fröhlich, 2020.

128 p.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Ciência da Computação, Florianópolis, 2020.

Inclui referências.

1. Ciência da Computação. 2. Sistemas Multicore Embarcados de Tempo Real. 3. Otimização Energética. 4. Aprendizado de Máquina. 5. Monitoramento Não Intrusivo. I. Fröhlich, Antônio Augusto Medeiros. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Ciência da Computação. III. Título.

# José Luis Conradi Hoffmann

# Optimizing Energy Consumption of Multicore Real-Time Embedded Systems using Machine Learning

O presente trabalho em nível de Mestrado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. Rafael de Santiago, PhD Universidade Federal de Santa Catarina

Prof. Marcus Völp, PhD Université du Luxembourg

Prof. Nikil Dutt, PhD University of California

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de Mestre em Ciência da Computação.

Prof. Vania Bogorny, PhD. Coordenadora do Programa de Pós-Graduação

Prof. Antônio A. M. Fröhlich, PhD. Orientador

# **ACKNOWLEDGEMENTS**

First, I would like to thank my Father, Cezar Nilo Hoffmann, and my Mother, Ivonete Terezinha Conradi Hoffmann, my sister, Munick Conradi Hoffmann, and my brother in law and great friend, Leonardo do Nascimento, for all the emotional support and encouragement provided.

I would like to thank my advisor Antônio Augusto Medeiros Fröhlich, for the scientific support and helpful discussions that lead to this work conclusion and for the opportunity to be a member of LISHA. I also would like to thank my dear friend, Leonardo Passig Horstmann, for the scientific discussions that helped me during the development of this work and the encouraging words. Many thanks also to all colleagues at LISHA.

I am also grateful to Prof. Rafael de Santiago, Prof. Marcus Völp, and Prof. Nikil Dutt for serving on my thesis committee.

Last but not least, many thanks to CAPES for financial support during two years in the graduate program.

#### **ABSTRACT**

Modern multicore processors must combine a large variety of architectural features to cope with the growing demands imposed by applications, often featuring heterogeneous cores, SIMD units, and application-specific accelerators, all interconnected by Network-on-Chip (NoC) technology. Such extreme variability usually requires some level of self-adaptation to attain the expected performance of real-time scenarios while managing energy consumption to fit with the constraints imposed by Embedded Environments. In this way, this work combines a careful Non-intrusive Monitoring and a Non-Intrusive energy optimizer design supported by Machine Learning techniques to enable safe actuation by learning the system demands using the data such systems produce as they operate. The Monitoring design proposed abstracts the available sensors and actuators in such platforms through a lean, architecture-independent API. The implementation focuses on non-intrusiveness, with a measured overhead of at most 0.0718% and maximum added jitter of less than 40 µs. The Non-intrusive Monitoring design is then used to explore the architectural behavior impact over performance aspects in a multicore platform, enabling Machine Learning techniques to build awareness of the current performance demands and the impact of the Dynamic Voltage-Frequency Scaling regimen on critical tasks, thus, guiding the energy optimizer, voting and actuation. To enable adaptation to the system variability, the energy optimizer encompasses Online Learning capabilities, implemented through an Artificial Neural Network design. The proposed ANN model is supported by feature selection, which provides the most relevant variables to describe shared resource contention in the selected multicore architecture. They are used at runtime to produce a performance trace that encompasses sufficient information for the ANN model to predict the impact of a frequency change on the performance of tasks. A migration heuristic encompassing a weighted activity vector is combined with the ANN model to dynamically adjust frequencies and also to trigger task migrations among cores, enabling further optimization by solving resource contentions and balancing the load among cores. The proposed solution achieved energy-savings of 24.97% on average when compared to the run-to-halt approach, and it did it without compromising the criticality of any single task. The overhead incurred in terms of the execution time was 0.1791% on average. Each prediction added 15.3585µs on average, and each retraining cycle triggered at frequency adjustments was never larger than 100 µs.

**Keywords**: Real-time systems and embedded systems, Multi-core/single-chip multiprocessors, Scheduling and task partitioning, Machine learning, Energy-aware systems.

#### **RESUMO**

Os processadores multicore modernos devem combinar uma grande variedade de recursos arquitetônicos para lidar com as demandas crescentes impostas pelos aplicativos, muitas vezes apresentando núcleos heterogêneos, unidades SIMD e aceleradores específicos do aplicativo, todos interconectados pela tecnologia Network-on-Chip (NoC). Essa extrema variabilidade geralmente requer algum nível de autoadaptação para suprir o desempenho esperado de cenários em tempo real enquanto gerencia o consumo de energia para se ajustar às restrições impostas pelos ambientes embarcados. Desta forma, este trabalho combina um monitoramento não intrusivo cuidadoso e um otimizador de energia não intrusivo apoiado por técnicas de aprendizado de máquina para permitir uma atuação segura, aprendendo as demandas do sistema usando os próprios dados que esses sistemas produzem enquanto operam. O monitoramento proposto abstrai os sensores e atuadores disponíveis em tais plataformas por meio de uma API enxuta e independente de arquitetura. A implementação é focada na não intrusão, com um overhead medido de no máximo 0.0718% e jitter adicionado máximo inferior a 40µs. O design de monitoramento não intrusivo é então usado para explorar o impacto do comportamento arquitetural sobre os aspectos de desempenho em uma plataforma multicore, permitindo que as técnicas de aprendizado de máquina criem consciência das demandas de desempenho atuais e do impacto do regime Dynamic Voltage-Frequency Scaling em tarefas críticas, orientando assim o votação e atuação do otimizador de energia. Além disso, para permitir a adaptação à variabilidade do sistema, o otimizador de energia engloba recursos de Aprendizado Online, implementado por meio de um design de uma Artificial Neural Network. O modelo ANN proposto é apoiado pela seleção de features, resultando nas variáveis mais relevantes para descrever a contenção de recursos compartilhados na arquitetura multicore selecionada. As variáveis são usadas em tempo de execução para produzir um trace de desempenho que engloba informações suficientes para o modelo ANN prever o impacto de uma mudança de frequência no desempenho das tarefas. Uma heurística de migração que abrange um vetor de atividade ponderada é combinada com o modelo ANN para ajustar dinamicamente as frequências e também para acionar migrações de tarefas entre os núcleos, permitindo uma otimização adicional resolvendo contenções de recursos e balanceando a carga entre os núcleos. A solução proposta alcançou economia de energia média de 24,97% guando comparada com a abordagem run-to-halt, e sem comprometer a criticidade de nenhuma tarefa. O overhead incorrido em termos de tempo de execução foi de 0.1791% em média. Cada previsão adiciona 15.3585 µs em média e cada ciclo de retreinamento disparado nos ajustes de frequência nunca foi maior que 100 μs.

**Palavras-chave**: Sistemas de Tempo-Real e Sistemas Embarcados, processadores Multi-core/single-chip, Escalonamento e Migração de tarefas, Aprendizado de Máquina, Sistemas conscientes de energia.

#### **RESUMO EXPANDIDO**

# Introdução

Em sistemas embarcados a expansão das funcionalidades exigidas por novos aplicativos (SARMA et al., 2015), particularmente para ambientes críticos, como aqueles que lidam com a visão computacional em veículos autônomos, aumenta as demandas de desempenho da plataforma embarcada destino para que seja capaz lidar com as restrições de tempo. No entanto, aumentar o desempenho de uma plataforma embarcada também aumenta seu consumo de energia, o que é um desafio considerando as restrições de energia de tais ambientes. Aumentar o número de núcleos nessas plataformas é uma solução para acomodar as crescentes demandas de tais aplicações. Processadores embarcados multicore modernos combinam uma grande variedade de recursos arquitetônicos, incluindo núcleos heterogêneos, unidades SIMD e aceleradores específicos de aplicação, estes interconectados por uma tecnologia Network on Chip. Todavia, essas arquiteturas complexas fazem uso intenso de paralelismo e mecanismos de ocultação de latência que causam variações no desempenho das tarefas em execução (CRAEYNEST et al., 2012; KEDAR et al., 2017).

Essas plataformas, no entanto, são sistemas ciberfísicos altamente instrumentados que podem ser monitorados e controlados com base nos dados que produzem durante a operação (MÜCK et al., 2018). Os contadores de desempenho de hardware (HPC) foram introduzidos por fabricantes de chips de processador por meio do componente Performance Monitoring Unit (PMU). PMUs são usadas para amostrar ocorrências de eventos de desempenho durante a execução, fornecendo informações sobre o uso da arquitetura, como Taxa de Instruções Finalizadas, Acesso à Memória, Branches Executados e Ciclos de Estagnação. Assim, para fornecer um nível mais alto de confiabilidade, garantir a exatidão do tempo de tarefas críticas e economizar energia, conjuntos de tarefas específicas requerem que os aspectos arquitetônicos sejam constantemente avaliados para atingir o nível esperado de determinismo, avaliando as necessidades imediatas de recursos da execução das tarefas a fim de prever o impacto das medidas de economia de energia em suas restrições em tempo real.

No entanto, lidar com a otimização de energia em cenários críticos em plataformas multicore vai além de modelar o desempenho do sistema manualmente e garantir estimativas Worst Case-Execution Time. A complexidade de novas aplicações críticas, com várias tarefas e vários núcleos, como é o caso dos veículos autônomos, exige controle de desempenho, temperatura e consumo de energia de forma mais automatizada. O problema de encontrar uma configuração ideal, que forneça desempenho suficiente com o menor consumo de energia possível, geralmente requer conhecimento especialista do conjunto de tarefas e da plataforma. Nesse sentido, o Aprendizado de Máquina

(ML) se destaca como uma alternativa para automatizar o processo de aquisição do conhecimento necessário sobre os fenômenos arquitetônicos expressos por rastreamentos de desempenho e estatísticas de Sistemas Operacionais (OS).

Técnicas de aprendizado de máquina podem ser utilizadas para automatizar o processo de mapear rastros da execução de tarefas obtidas através do uso arquitetural em informações úteis para suportar otimização de tempo de execução. Por exemplo, em (LAHIRI et al., 2007; JUNG; PEDRAM, 2010) os autores usam modelos de Artificial Neural Network (ANN) focando em estatísticas de tempo do conjuntos de tarefas para otimizar a frequência da CPU. Outros trabalhos exploram modelos de Reinforcement Learning para encontrar a melhor configuração Dynamic Voltage-Frequency Scaling com base em características temporais (ISLAM et al., 2018) e a contagem de ciclos de processamento (DAS et al., 2015). Outros trabalhos (CHEN et al., 2018; JUNG; PEDRAM, 2010; RAI et al., 2010) combinam características temporais e contadores de desempenho, como a taxa de instruções finalizadas e a taxa de acessos a elementoschave na hierarquia de memória para fornecer informações mais detalhadas para algoritmos de aprendizado supervisionado a fim de prever o impacto das operações de economia de energia no desempenho. No entanto, a realização de otimizações baseadas em aprendizado de máquina em tempo de execução junto com a execução de tarefas críticas requer que otimizadores garantam o mesmo nível de determinismo temporal definido para as tarefas. Portanto, eles devem coletar dados e executar algoritmos sem interferir nas tarefas em execução, e as otimizações propostas, que podem incluir ajustes de frequência e migrações de tarefas, não devem prejudicar a execução de nenhuma tarefa crítica.

Portanto, para que otimizações energéticas em sistemas embarcados em tempo real sejam suportadas em uma plataforma multicore, eles devem ser capazes de construir autoconsciência da utilização atual e de garantir otimizações de forma a não prejudicar a execução das tarefas, permitindo que o sistema alcance o equilíbrio de desempenho/potência esperado sem prejudicar nenhuma tarefa crítica. Combinando monitoramento de desempenho não intrusivo e técnicas de aprendizado de máquina, tal sistema deve ser capaz de aprender um comportamento de conjunto de tarefas, gerando indicadores em tempo de execução para o sistema se adaptar. Assim, um sistema embarcado multicore em tempo real pode executar a atuação guiada por aprendizado de máquina seguindo uma margem de segurança de reserva de recursos, permitindo a execução de forma segura de medidas de economia de energia (por exemplo, ajuste de frequência, migração de tarefa e gerenciamento de energia) para atingir o nível exigido de desempenho enquanto provê economia de energia.

# **Objetivos**

Considerando em sistemas embarcados multicore em tempo real os desafios acima mencionadas e as capacidades de aprendizagem das técnicas de aprendizado de máquina, o objetivo principal deste trabalho é definido como para projetar, implementar e validar um otimizador de energia de tempo de execução não intrusivo, baseado em ANN que abrange a migração de tarefas e Dynamic Voltage-Frequency Scaling. O otimizador de energia é construído sobre o monitoramento de desempenho, usando a ANN como um preditor para orientar a economia de energia sem prejudicar a execução de qualquer tarefa crítica. Isto é feito por meio dos seguintes objetivos específicos:

- Realizar uma revisão do estado da arte sobre os conceitos de Tempo Real e Aprendizado de Máquina, com foco em plataformas multicore em tempo real e Aprendizado de Máquina aplicado ao gerenciamento de energia.

- Projetar um sistema de monitoramento de desempenho não intrusivo e implementálo para as arquiteturas Intel e ARM.

- Projetar uma coleção de rastros de uso arquitetural por meio de conjuntos de tarefas em tempo real, sintéticos e específicos à arquitetura, que incluem todos os contadores de desempenho disponíveis e estatísticas do sistema operacional, que também permita a análise de contenção de recursos compartilhados.

- Projetar uma seleção de features de forma off-line para filtrar o conjunto de recursos mais expressivo dos dados coletados em relação ao desempenho das tarefas e contenção de recursos compartilhados.

- Projetar uma estratégia de treinamento offline para um modelo inicial de ANN de baixa intrusão para prever o impacto das medidas de economia de energia no desempenho da tarefa.

- Elaborar um treinamento incremental online não intrusivo para o modelo ANN se adaptar em tempo de execução ao conjunto de tarefas corrente.

- Projetar um algoritmo de migração de tarefas baseado no monitoramento de desempenho para equilíbrio de atividades das CPUs.

- Projetar e implementar o processo de atuação do otimizador de energia não intrusivo, baseado em ANN, permitindo que os sistemas embarcados em tempo real atinjam uma configuração de frequência e distribuição de tarefas otimizada sem prejudicar o desempenho de tarefas críticas, incluindo otimizações de distribuição de carga e prevenção de contenção de recursos compartilhados.

# Metodologia

A metodologia deste trabalho caracteriza-se como uma pesquisa aplicada de abordagem quantitativa, implementada por meio de pesquisa exploratória composta por pesquisa bibliográfica e procedimentos experimentais.

Para tal, uma coleção de dados é executada a fim de extrair dados de uma plataforma multicore embarcada de tempo real executando benchmarks sintéticos, específicos de arquitetura (VENKATA et al., 2009; GRACIOLI et al., 2019) representando aplicativos embarcados relevantes para estimular os fenômenos arquitetônicos da plataforma alvo sob várias configurações. O conjunto de dados incluí todos os contadores de desempenho disponíveis na plataforma de destino e estatísticas úteis do sistema operacional, onde a coleta é realizada através de um sistema de monitoramento não intrusivo. Por meio dos dados coletados, uma seleção de features é realizada para encontrar o conjunto de features mais relevantes que será usado para construir o preditor. O preditor utilizado neste trabalho é um regressor ANN que toma como entrada as features selecionadas e prevê a utilização de uma tarefa em uma configuração de frequência mais baixa. A ANN é inicialmente treinada offline, evitando assim problemas de cold start e possibilitando o ajuste de sua topologia. Além disso, o treinamento offline da ANN segue uma abordagem de aprendizado incremental, onde a métrica de avaliação de desempenho utilizada para o processo de ajuste leva em consideração a quantidade, em média, necessária de treinamentos incrementais para a ANN se adaptar a um novo cenário considerando um limite de desvio. O preditor é subsegüentemente treinado em tempo de execução sempre que a frequência é ajustada ou uma tarefa é migrada, assim, liberando-o do conjunto de tarefas sintéticas inicial. Por fim, para permitir ainda mais otimizações de energia junto com o controle de frequência, uma heurística de migração é proposta como um vetor de atividade ponderada com base nos mesmos recursos usados pela ANN.

O otimizador de energia implementado é avaliado por meio de três conjuntos de tarefas diferentes, compostos por benchmarks relevantes. A avaliação se da pela análise do overhead adicionado à execução do sistema embarcado, a precisão e adaptabilidade do modelo e a economia de energia proporcionada pela solução proposta.

# Resultados e Discussão

Os principais resultados provenientes das análises de desempenho da implementação de prova de conceito do otimizador energético proposto são os seguintes:

• O otimizador energético proposto é avaliado em questão de overhead adicionado ao sistema, impacto no tempo de execução das tarefas, adaptação em tempo de

execução do preditor produzido, e economia de energia proporcionada, sendo todos as análises apresentadas provindas de uma implementação de prova de conceito sob uma plataforma multicore real, mais especificamente, um processador quadcore Cortex-A53.

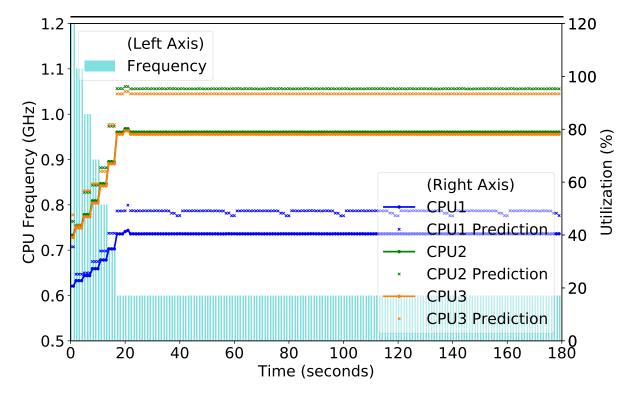

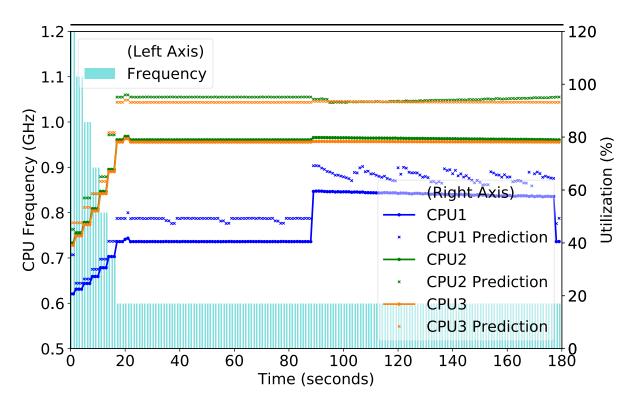

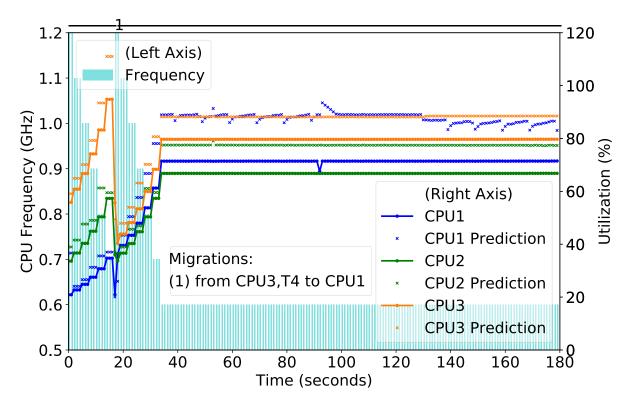

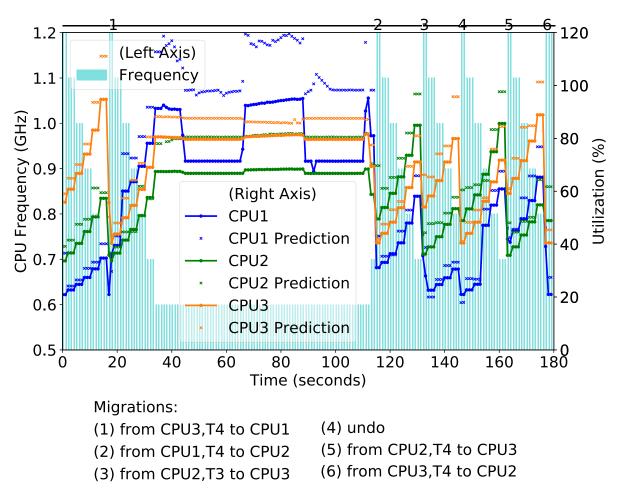

- O otimizador energético proposto é avaliado inicialmente sobre três diferentes conjuntos de tarefas, sendo o primeiro um cenário mais simples, o segundo, um cenário com diferentes fases de execução das tarefas, e o terceiro, um cenário com alta taxa de contenção por recursos compartilhados sobre as tarefas executadas em paralelo.

- A análise de overhead é dividida em três etapas:

- o sistema de monitoramento: sendo esta uma avaliação de sua implementação em um processador Intel i7-2600, apresenta um baixo impacto no tempo de ociosidade do sistema (cerca de 43 ms em 1 minuto, aproximadamente 0.0718%) e uma baixa intrusividade no tempo de ativação das tarefas, apresentado um jitter máximo menor que 40μs.

- O otimizador energético em execução: o mesmo apresenta um baixo nível de intrusão no tempo ocioso do sistema, cerca de 15µs por ativação do sistema de votação e atuação, e de no máximo 92µs para ativações que envolvem o treinamento online do preditor, onde tais ativações ocorrem de acordo com a configuração de gatilho do otimizador energético, no caso dos cenários apresentados, o hyper-período do conjunto de tarefas.

- O impacto na execução das tarefas: tarefas de uso intenso de CPU não sofreram nenhum impacto no seu tempo de execução, tarefas de uso médio de CPU e Memória sofreram, em média, um impacto próximo a 0.036% em seu tempo de execução, e tarefas de uso intenso de memória sofreram, em média, um impacto próximo a 0.18%

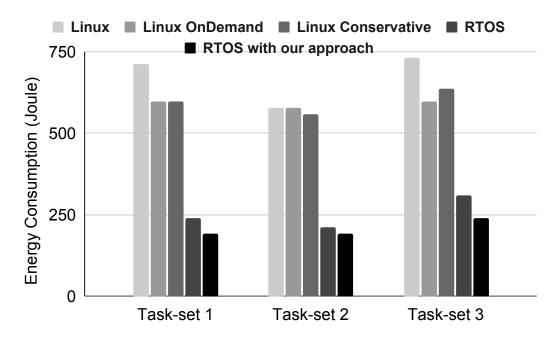

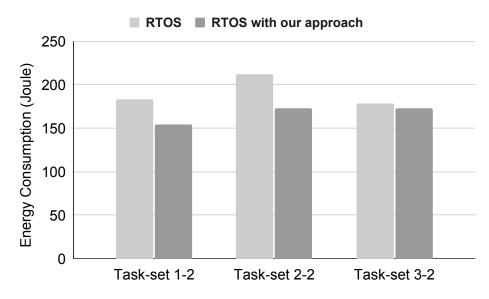

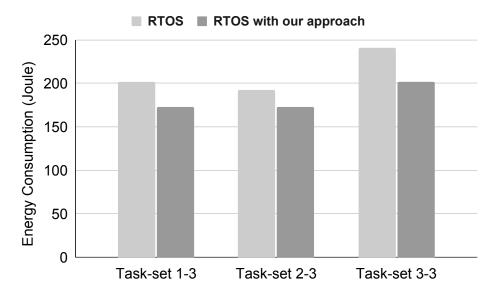

- A economia de energia proporcionada pelo otimizador energético é comparada com o consumo energético dos mesmos conjuntos de tarefas executando sobre o mesmo sistema operacional de tempo real (EPOS), o qual implementa uma política run-to-halt, onde a frequência da CPU é maximizada a fim de maximizar o tempo ocioso do sistema, e também comparando os resultados obtidos em relação ao sistema operacional Linux executando o mesmo conjunto de tarefas sob três políticas de otimização de energia distintas, run-to-halt, OnDemand, e Conservative. O otimizador energético obteve sempre o melhor resultado quando comparado com os cenários citados, e o fez sem comprometer a execução de nenhuma tarefa crítica, utilizando ambas as técnicas de DVFS e migração de tarefas. Os resultados obtidos foram os seguintes: 24.97% de redução, em média, no consumo energético quando comparado ao EPOS sob a politica run-to-halt, e

- 68.91%, 64.70% e 65.13%, em média, quando comparado ao Linux executando sob a política run-to-halt, OnDemand, e Conservative, respectivamente.

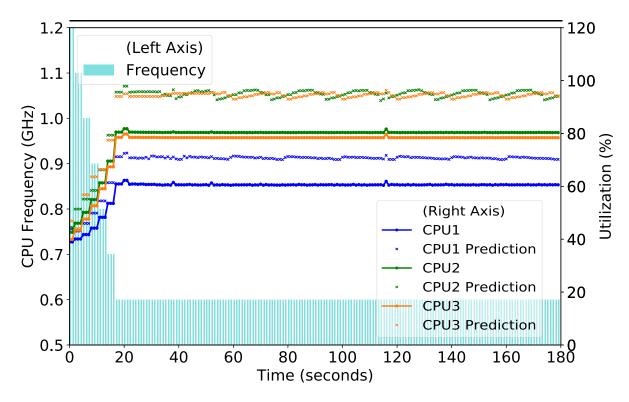

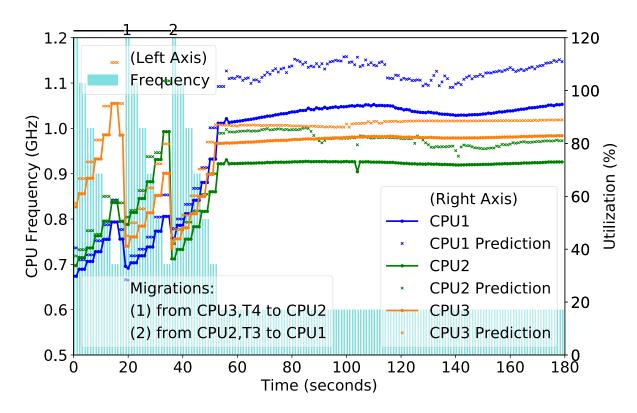

- A avaliação do otimizador energético proposto também incluí uma análise dos desvios das predições em tempo de execução do modelo ANN proposto e os resultados do respetivo retreinamento online do modelo. Tal avaliação é demonstrado em uma análise de cenários com alta variabilidade na execução das tarefas, concluindo que o modelo é capaz de rapidamente se adaptar a novos cenários sem comprometer a execução de tarefas críticas.

O projeto do otimizador de energia foi avaliado por meio de uma implementação de prova de conceito. A implementação teve como foco o design não intrusivo e os recursos da API de monitoramento e atuação proposta neste trabalho. Quando aliado à baixa intrusão apresentada por um RTOS (Embedded Parallel Operating System (EPOS)), o design da API cria uma estrutura de um otimizador limpa e confiável com recursos poderosos de monitoramento e atuação. Com o RTOS focado no manuseio de um determinado conjunto de tarefas, o monitoramento de desempenho e o projeto de atuação podem ser controlados sem prejudicar o determinismo da execução de qualquer tarefa.

Para implementar o otimizador de energia, primeiro, um preditor de utilização é necessário e, para cumprir o design proposto, um preditor com recursos de aprendizado online é desejado. Portanto, um modelo de ANN treinado incrementalmente é proposto juntamente com a exploração de perfilamento de fenômenos arquitetônicos por meio do monitoramento de desempenho. Além disso, o projeto da ANN está focado em dois momentos de aprendizagem: Um treinamento off-line usando um conjunto de tarefas sintéticas para ajuste de arquitetura e prevenção de problemas de inicialização a frio. E o treinamento online, para tornar o modelo livre do conjunto de tarefas sintéticas usado no treinamento offline, levando em conta a variabilidade de desempenho do conjunto de tarefas, proveniente tanto das tarefas quanto dos fenômenos arquitetônicos.

A exploração de features é realizada através de uma análise de contadores de desempenho disponíveis na arquitetura, com foco em identificar os mais relevantes no que se diz a fenômenos arquiteturais relacionados ao desempenho das tarefas, especialmente problemas decorrentes da contenção de recursos compartilhados gerados pela arquitetura multicore. Com o objetivo de tornar este processo completamente independente de conhecimento especialista e análises manuais, uma abordagem de mineração de dados para seleção de features é implementada. O método proposto inclui um fluxo de trabalho de pré-processamento juntamente com a combinação de três diferentes abordagens de seleção de features. Este processo é combinado com a remoção de

redundância para melhorar a cobertura do conjunto de features resultante. A cobertura do conjunto de features resultante inclui contadores de desempenho cobrindo o uso de memória e o uso da CPU de tarefas, no qual a memória constitui o principal recurso compartilhado na arquitetura alvo. As informações de desempenho extraídas por meio de tais contadores foram suficientes para construir o modelo de aprendizado de máquina previsto para controlar a atuação do DVFS e orientar a migração da tarefa, o que corroborou a eficácia da abordagem utilizada para extração de features, o conjunto de tarefas sintéticas utilizadas juntamente com o sistema de monitoramento não intrusivo e o processo de seleção de features.

# Considerações Finais

Neste trabalho, um otimizador de energia não intrusivo baseado em uma Artificial Neural Network (ANN) para arquiteturas multicore de tempo-real embarcadas que atua em tempo de execução é proposto. O otimizador de energia é capaz de prover otimizações energéticas sem comprometer os rigorosos requisitos de tempo de tarefas críticas. Os recursos do otimizador de energia incluem Dynamic Voltage-Frequency Scaling (DVFS) e migrações de tarefas, as quais atuam com base nas saídas do modelo ANN e de uma heurística baseada no conceito de vetor de atividades ponderado. A ANN é um componente do otimizador de energia que visa fornecer previsões sobre o impacto que um ajuste da frequência de execução de uma CPU terá no desempenho da tarefa, usando contadores de desempenho como entrada. O otimizador de energia considera cada tarefa em execução em cada núcleo do processador para conceber uma atuação, compondo uma predição de tempo de ociosidade disponível e uma margem de segurança de atuação definida pelo usuário. O modelo ANN é construído sobre rastros de execução coletados de contadores de desempenho de hardware e estatísticas do sistema operacional, selecionados através de algoritmos de extração de features offline. O processo de extração de recursos visa expor as variáveis mais relevantes relacionadas ao desempenho usando conjuntos de tarefas sintéticos específicos da arquitetura. Os rastros de desempenho também são usados para construir um treinamento offline para ajustar a configuração da ANN. O preditor é então treinado em tempo de execução sempre que a frequência é ajustada, liberando-o do conjunto de tarefas sintéticas inicial. A migração da tarefa é baseada em um conceito de vetor de atividade ponderado e usa os mesmos contadores de desempenho usados pela ANN. O objetivo da migração de tarefas é reduzir a variação da atividade entre CPUs em um estilo de balanceamento de carga, incluindo migração de tarefas e trocas de tarefas entre CPUs para obter uma melhor distribuição de carga e resolver contenções sobre recursos compartilhados. Os pesos usados pelo algoritmo são traçados de antemão através da técnica de Gradiente Descendente. Com isso, os resultados obtidos pela implementação de prova de conceito demonstram que a solução foi capaz de otimizar

o consumo da plataforma alvo eficientemente sem prejudicar o desempenho de nenhuma tarefa crítica através de um solução com suporte a adaptação online do modelo de aprendizado de máquina utilizado de forma não intrusiva ao sistema.

**Palavras-chave**: Sistemas de Tempo-Real e Sistemas Embarcados, processadores Multi-core/single-chip, Escalonamento e Migração de tarefas, Aprendizado de Máquina, Sistemas conscientes de energia.

# LIST OF FIGURES

| Figure 1 – Envisioned energy-optimizer solution overview                                                                                                                                                                                                                             | 3        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2 — Rate Monotonic Scheduling for a task-set with 91.67% of usage, presenting a deadline miss                                                                                                                                                                                 | 13       |

| Figure 3 – Earliest Deadline First Scheduling for a task-set with 91.67% of usage, without presenting deadline misses.                                                                                                                                                               | 14       |

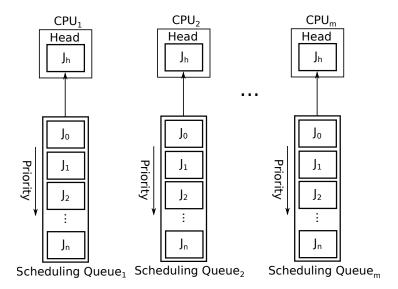

| Figure 4 – Unicore Scheduling Queue                                                                                                                                                                                                                                                  | 15       |

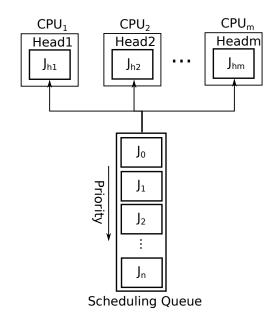

| Figure 5 - Multicore Scheduling Queue - Partitioned Configuration                                                                                                                                                                                                                    | 16       |

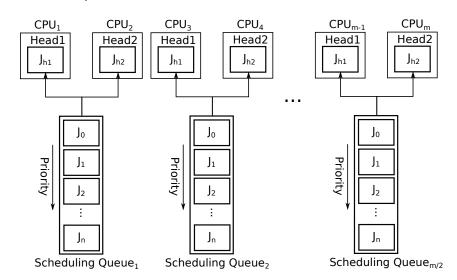

| Figure 6 – Multicore Scheduling Queue - Global Configuration                                                                                                                                                                                                                         | 16       |

| Figure 7 — Multicore Scheduling Queue - Clustered Configuration                                                                                                                                                                                                                      | 17       |

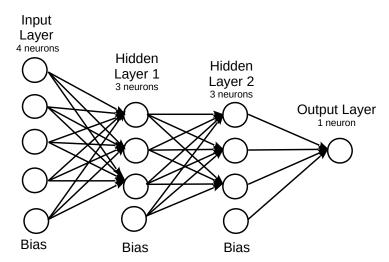

| Figure 8 – A multilayer feedforward ANN fully connected with two hidden layers                                                                                                                                                                                                       | 21       |

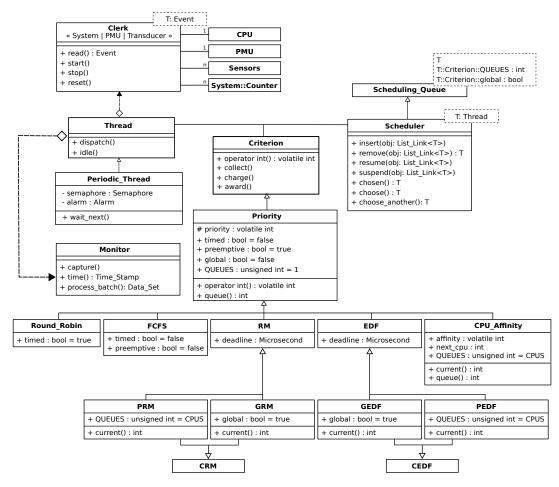

| Figure 9 – Scheduler Framework UML class diagram with the Monitoring API extension                                                                                                                                                                                                   | 36       |

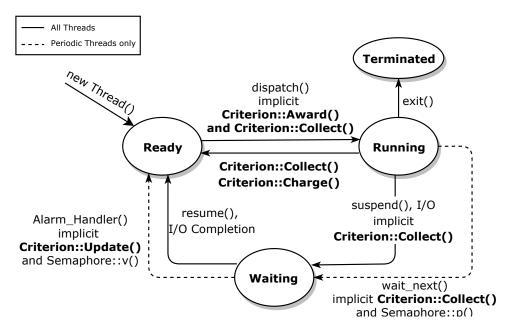

| Figure 10 – Thread state diagram and the associated methods of class Criterion.                                                                                                                                                                                                      | 38       |

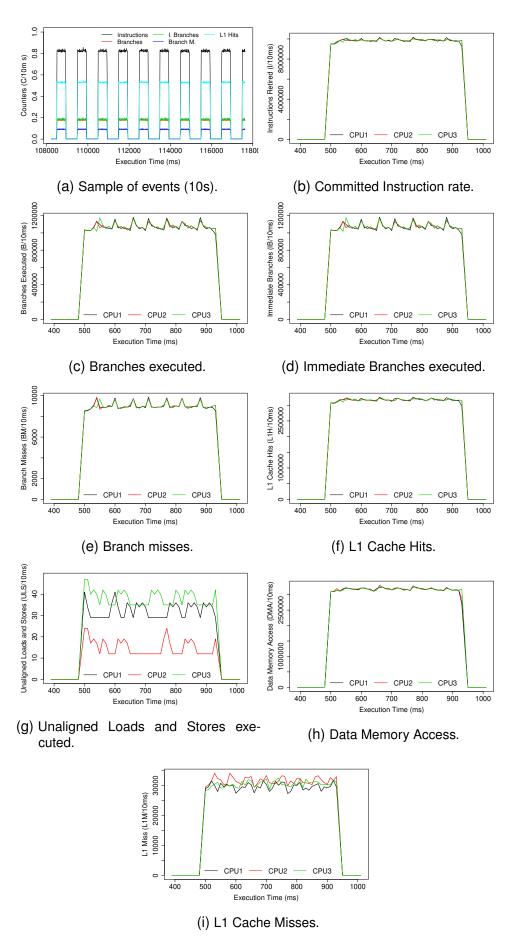

| Figure 11 – Example of run-time data collected by the Monitoring system                                                                                                                                                                                                              | 44       |

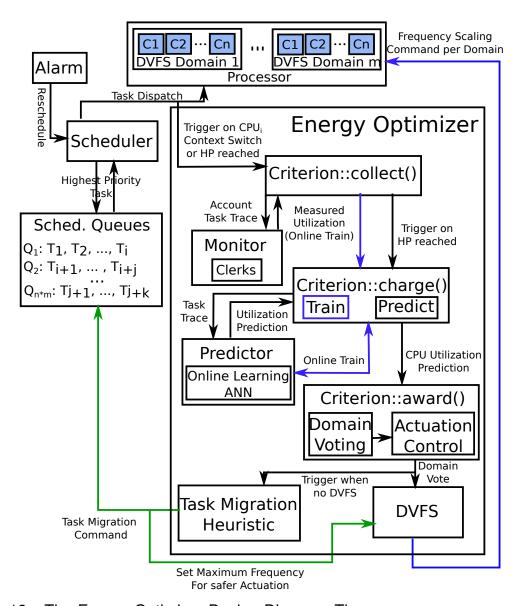

| Figure 12 – The Energy Optimizer Design Diagram. The green arrows represent the execution flow for a task migration actuation, while the blue arrows, the execution flow for a DVFS actuation, which also includes                                                                   |          |

| an online learning section                                                                                                                                                                                                                                                           | 46       |

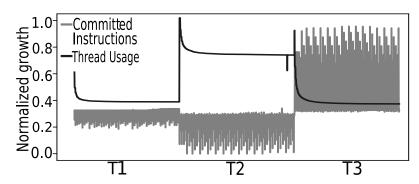

| Figure 13 – Committed Instructions trace of a task in three different scenarios:  T1 runs in a no contention scenario, T2 runs in a high contention scenario, and T3 runs in a low contention scenario                                                                               | 58       |

| Figure 14 – Bus Access for Memory Write trace of a task in three different scenar-                                                                                                                                                                                                   |          |

| ios: T1 runs in a no contention scenario, T2 runs in a high contention scenario, and T3 runs in a low contention scenario                                                                                                                                                            | 58       |

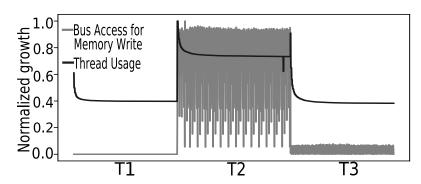

| Figure 15 – Ten most relevant features according to the feature selection techniques used                                                                                                                                                                                            | 70       |

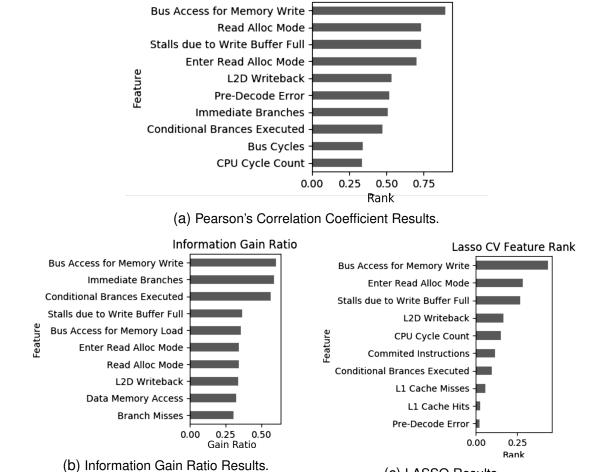

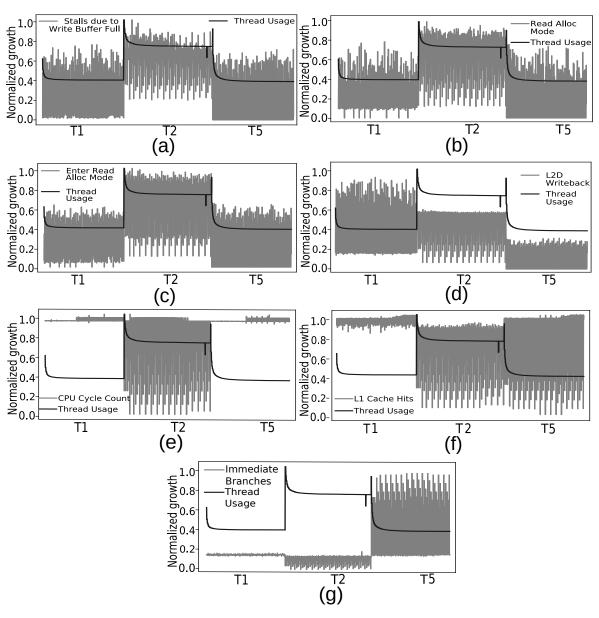

| Figure 16 – Stalls due to Write Buffer Full and Read Alloc Mode performance Counters trace (highly correlated counters following PCC): (a) Stalls due to Write Buffer Full, (b) Read Alloc Mode, and (c) Enter Read Alloc Mode. And Performance Counters trace of (d) L2D Writeback, |          |

| (e) CPU Cycles, (f) L1 Cache Hits, and (g) Immediate Branches                                                                                                                                                                                                                        | 72<br>74 |

| Figure 17 – Artificial Neural Network final architecture                                                                                                                                                                                                                             | 74<br>79 |

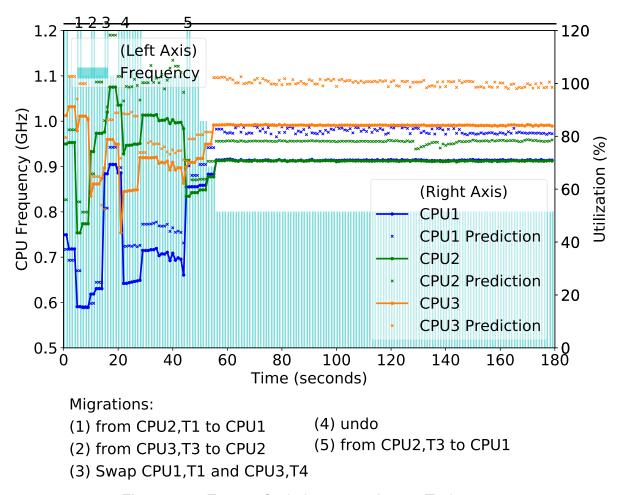

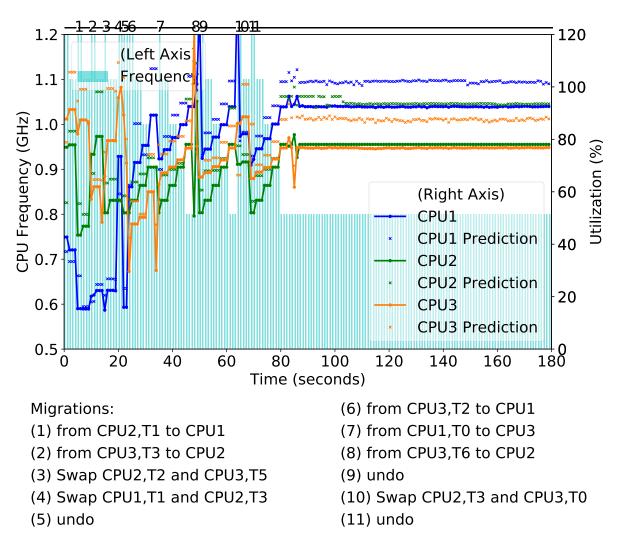

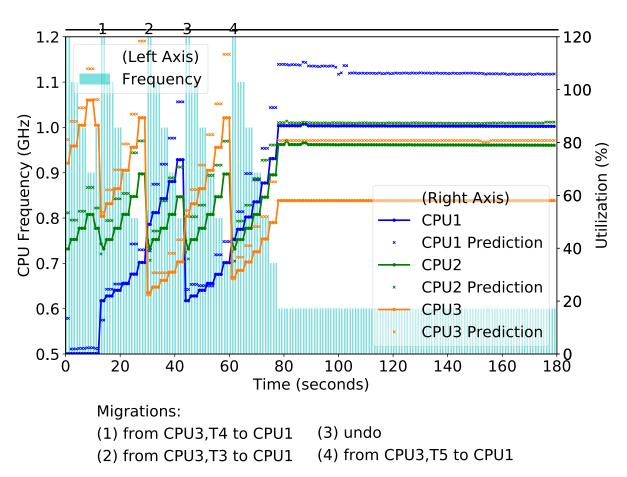

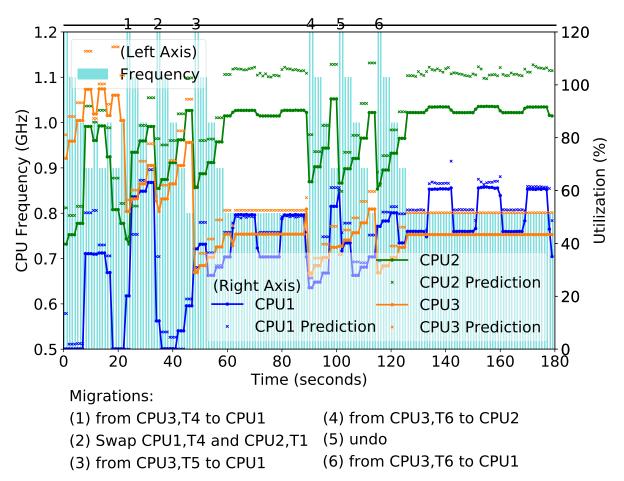

| Figure 19 – Energy Optimizer actuation on Task-set 1                                                                                                                                                                                                                                 | 80       |

| Figure 20 – Energy Optimizer actuation on Task-set 2                                                                                                                                                                                                                                 |          |

| 82 |

|----|

|    |

| 83 |

|    |

| 83 |

|    |

|    |

| 84 |

|    |

| 84 |

|    |

| 86 |

|    |

| 86 |

|    |

| 87 |

|    |

| 88 |

|    |

| 89 |

|    |

# LIST OF TABLES

| Table 1 - | Qualitative Comparison to Related Works Over the Main Concepts |    |

|-----------|----------------------------------------------------------------|----|

|           | Addressed by This Work                                         | 33 |

| Table 2 - | Task-sets configuration                                        | 68 |

# **CONTENTS**

| 1       | INTRODUCTION                                              | 1  |

|---------|-----------------------------------------------------------|----|

| 1.1     | GOALS                                                     | 2  |

| 1.1.1   | Specific Goals                                            | 3  |

| 1.2     | PREVIOUS RELATED WORKS BY THE GROUP                       | 2  |

| 1.3     | METHODOLOGY                                               | 2  |

| 1.4     | CONTRIBUTIONS                                             | 5  |

| 1.5     | OVERVIEW                                                  | 6  |

| 2       | LITERATURE REVIEW                                         | 7  |

| 2.1     | BACKGROUND                                                | 8  |

| 2.1.1   | Real-Time Scheduling                                      | 8  |

| 2.1.1.1 | Unicore Real-Time Scheduling                              | 12 |

| 2.1.1.2 | Multicore Real-Time Scheduling                            | 14 |

| 2.1.2   | Machine Learning                                          | 18 |

| 2.1.2.1 | Artificial Neural Networks                                | 21 |

| 2.1.2.2 | Feature Selection                                         | 23 |

| 2.2     | RELATED WORKS                                             | 24 |

| 2.2.1   | Real-time Multicore Scheduling                            | 24 |

| 2.2.2   | Contention-aware Task Allocation                          | 25 |

| 2.2.3   | Task Migration                                            | 26 |

| 2.3     | MACHINE LEARNING FOR ENERGY OPTIMIZATION IN MULTICORE     |    |

|         | SYSTEMS                                                   | 27 |

| 2.3.1   | Supervised Learning approaches for Energy Optimization    | 27 |

| 2.3.2   | Reinforcement Learning approaches for Energy Optimization | 31 |

| 2.3.3   | Summary of the Literature Review                          | 33 |

| 3       | NON-INTRUSIVE MONITORING                                  | 35 |

| 3.1     | SCHEDULER FRAMEWORK                                       | 35 |

| 3.2     | NON-INTRUSIVE MONITOR DESIGN                              | 38 |

| 3.2.1   | Non-Intrusiveness                                         | 39 |

| 3.2.2   | Per Task Monitoring Functionality                         | 40 |

| 3.2.3   | Actuation Design                                          | 41 |

| 3.2.4   | A Generalized Learning Strategy                           | 41 |

| 3.3     | SUMMARY OF THE NON-INTRUSIVE MONITOR                      | 43 |

| 4       | ENERGY OPTIMIZER                                          | 45 |

| 4.1     | ENERGY OPTIMIZER DESIGN                                   | 45 |

| 4.1.1   | Collecting                                                | 47 |

| 4.1.2   | Charging                                                  | 49 |

| 4.1.3   | Actuation                                                 | 51 |

| 4.1.3.1 | Task Migration                                    | 52 |

|---------|---------------------------------------------------|----|

| 4.2     | LEARNING WORKFLOW: FEATURE EXPLORATION AND ONLINE |    |

|         | LEARNING ANN                                      | 56 |

| 4.2.1   | Pre-processing                                    | 59 |

| 4.2.2   | Feature Selection                                 | 61 |

| 4.2.3   | ANN Design                                        | 63 |

| 4.3     | SUMMARY OF THE RUN-TIME ENERGY OPTIMIZER DESIGN   | 65 |

| 5       | PROOF OF CONCEPT IMPLEMENTATION                   | 67 |

| 5.1     | DATA COLLECTION                                   | 67 |

| 5.1.1   | Benchmarks                                        | 68 |

| 5.1.2   | Feature Selection Results                         | 70 |

| 5.1.3   | ANN Configuration                                 | 73 |

| 5.1.3.1 | ANN Implementation Library                        | 75 |

| 5.2     | PROPOSAL EVALUATION                               | 75 |

| 5.2.1   | Overhead Analysis                                 | 76 |

| 5.2.2   | Experimental Results                              | 78 |

| 5.3     | DISCUSSION                                        | 90 |

| 6       | CONCLUSION                                        | 95 |

| 6.1     | FUTURE WORKS                                      | 96 |

|         | REFERENCES                                        | 98 |

#### 1 INTRODUCTION

In the realm of embedded systems, the expanding functionalities required by new applications (SARMA et al., 2015), particularly for critical environments such as those handling computer vision in autonomous vehicles, increases the performance demands of the target embedded platform in order to cope with time constraints. Nevertheless, increasing the performance of an embedded platform also increases its energy consumption, which is challenging considering the energy constraints of such environments. Increasing the number of cores in those platforms is a solution to accommodate the growing application demands. Modern embedded multicore processors combine a large variety of architectural features, including heterogeneous cores, SIMD units, and application-specific accelerators interconnected by NoC technology. These complex architectures make intense use of parallelism and latency hiding mechanisms that cause variations in the performance of running tasks (CRAEYNEST et al., 2012; KEDAR et al., 2017).

These platforms, however, are themselves highly instrumented cyber-physical systems that can be monitored and controlled based on the data they produce during operation (MÜCK et al., 2018). Hardware Performance Counters (HPC) have been introduced by processor chip manufacturers through a Performance Monitoring Unit (PMU) component. PMUs are used to sample performance events occurrences during execution, providing information regarding the architectural usage, such as Committed Instructions Rate, Memory Access, Branches Executed, and Stalls Cycles. Thus, to provide a higher level of reliability, guarantee the timing correctness of critical tasks, and save energy, specific task-sets are often required to look after such architectural aspects to attain the expected level of determinism, assessing the immediate resource needs of running tasks and predicting the impact of power-saving measures on their real-time constraints.

However, handling energy optimization in critical scenarios on multicore platforms goes beyond modeling system performance manually and assuring Worst CaseExecution Time (WCET) estimations. The complexity of new critical applications, with

several tasks and several cores, as is the case for autonomous vehicles, requires handling performance, temperature, and energy consumption in a more automated way.

The problem of finding an optimal configuration, which provides sufficient performance

with the lowest energy consumption possible, often requires expert knowledge about the

task-set and the platform. In this sense, Machine Learning stands up as an alternative

to automate the process of acquiring the necessary knowledge about the architectural

phenomena expressed by performance traces and OS statistics.

Machine Learning (ML) techniques are being used to automate the process of mapping performance traces provided by the architecture into useful information to

support runtime optimizations. For instance, works like (LAHIRI et al., 2007; JUNG; PEDRAM, 2010) use ANN models in combination with timing specs of task-sets to optimize the CPU frequency. Other works envision Reinforcement Learning (RL) models to find the best Dynamic Voltage-Frequency Scaling configuration based on timing (ISLAM et al., 2018) and cycle counting (DAS et al., 2015). Other works (CHEN et al., 2018; JUNG; PEDRAM, 2010; RAI et al., 2010), combine with timing specs performance counters, such as the rate of instructions committed and the rate of accesses to key elements in the memory hierarchy to supply more detailed information for supervised learning algorithms to predict the impact of energy-saving operations on performance. However, performing ML-based optimizations at runtime along with the execution of critical tasks requires optimizers to secure the same level of temporal determinism defined for the tasks. Therefore, they must collect data and run algorithms without interfering with running tasks, and the proposed optimizations, which may include frequency scaling and task migrations, must not impair the execution of any critical task.

Therefore, for real-time embedded systems to endure in a multicore platform, they must build self-awareness of the current performance and be able to ensure optimizations, enabling the system to reach the expected performance/power balance without impairing any critical task. Combining non-intrusive performance monitoring and ML techniques, the system is able to learn a task-set behavior, yielding indicators at runtime for the system to adapt itself. Thus, a real-time multicore embedded system can run the ML-guided actuation matching a safety margin of resource reservation, enabling power-saving measures (e.g., frequency scaling, task migration, and power management) to achieve the desired performance level while optimizing energy-savings.

# 1.1 GOALS

Considering the aforementioned constraints of real-time multicore embedded systems and the learning capabilities of ML-techniques, the main goal of this work is defined as to design, implement and validate a non-intrusive, ANN-Based, runtime energy optimizer that encompasses task migration and DVFS. The energy optimizer is built upon performance monitoring, using the ANN as a predictor to guide energy-savings without impairing the execution of any critical task.

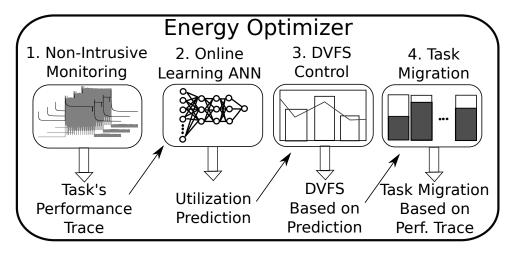

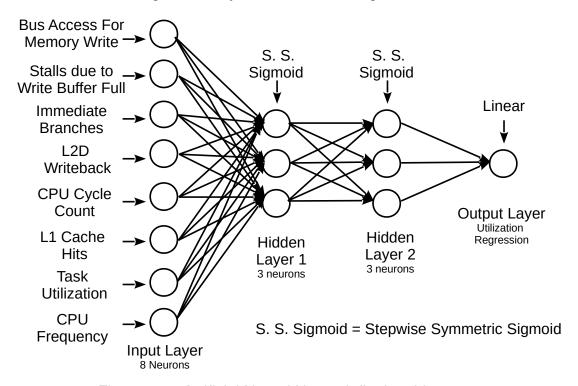

A top-level depiction of the proposed system is presented in Figure 1. The ANN model takes execution traces of individual tasks as input to predict their performance in case the core where they are running is subjected to an energy-saving actuation. Traces are built at runtime out of hardware performance counters, sensors, and OS variables, selected by offline feature extraction algorithms. The predictor aims at initial offline training using a synthetic task-set to tune its configuration and avoid cold start issues, and is subsequently trained at runtime whenever the frequency is scaled or

a task is migrated, thus, setting it free from the initial synthetic task-set. Besides the predictor, the optimizer makes use of a task migration heuristic that encompasses a notion of resource reservation as an additional measure to avoid impairing critical tasks.

Figure 1 – Envisioned energy-optimizer solution overview.

# 1.1.1 Specific Goals

The proposed energy optimizer is designed and implemented corroborating with the following specific goals:

- Perform a state-of-the-art review over Real-Time and Machine Learning concepts, focused on real-time multicore platforms and Machine Learning applied for energy management.

- Design a non-intrusive performance monitoring system and implement it for Intel and ARM architectures.

- Design a performance trace collection through real-time, synthetic, architecturespecific task-sets, that includes every performance counter available and OS statistics, and also enables shared resource contention analysis.

- Design an offline feature selection to filter the most expressive feature-set from the collected data regarding tasks' performance and shared resource contention.

- Design an offline training strategy for an initial, low-intrusive, ANN model to predict the impact of power-saving measures at task performance.

- Design a non-intrusive online incremental training for the ANN model to adapt itself at run time to the current task-set.

- Design a task migration algorithm based on performance monitoring for activity balance of CPUs.

Design and implement the non-intrusive, ANN-based, energy optimizer actuation process, enabling the real-time embedded systems to achieve optimal frequency configuration without impairing critical tasks, including load distribution optimizations and shared resource contention avoidance.

# 1.2 PREVIOUS RELATED WORKS BY THE GROUP

This master's project was developed at the Software/Hardware Integration Laboratory (LISHA) at the Federal University of Santa Catarina (UFSC). Over the last decades, several research projects have been conducted in the group on the topic of Real-Time Multicore Systems, Performance Monitoring, and Power Management. These works granted the group the required perspective and experience that led to the idea of the Online Learning Energy Optimizer. What follows is a list in chronological order of the main past contributions with their main authors that directly influenced the present work:

- Antônio Augusto Fröhlich, Application-Oriented Operating Systems (FRÖHLICH, A. A., 2001) - For the design of the Embedded Parallel Operating System (EPOS) and the first version of the Scheduler Framework;

- Arliones Stevert Hoeller Junior (JUNIOR, 2007), Application Oriented Power Management in Embedded Systems (free translation of "Gerência do Consumo de Energia Dirigida pela Aplicação em Sistemas Embarcados") For the perspective and notions of Power Management in embedded systems;

- Hugo Marcondes, A Hybrid Hardware and Software Component Architecture for Embedded System Design (MARCONDES, 2009) - For the real-time implementation of the Scheduler Framework;

- Gustavo Roberto Nardon Meira, Real-Time Dynamic Voltage and Frequency Scaling on EPOS System (MEIRA, 2011) For the perspective and notions of DVFS in real-time systems;

- Giovani Gracioli, Real-Time Operating System Support for Multicore Applications; (GRACIOLI, 2014) - For the perspective and notions of real-time multicore systems, and the multicore implementation of the multicore Scheduler Design;

# 1.3 METHODOLOGY

The methodology of this work is characterized as applied research on a quantitative approach, implemented through exploratory research composed of bibliographic research and experimental procedures.

It includes the building of a database by extracting data from a real embedded multicore platform running synthetic, architecture-specific, benchmarks (VENKATA et al., 2009; GRACIOLI et al., 2019) representing embedded applications to stimulate the architectural phenomena of the target embedded multicore platforms under several configurations. The dataset will include every available performance counter in the target platform and useful OS statistics, where the collection will be done using a non-intrusive monitoring design. Through the collected, a feature selection will be performed to find the most relevant feature-set that will be used to build the predictor. The predictor used in this work is an ANN regressor that takes as input the selected features and predicts the utilization of a task in a lower frequency configuration. The ANN is initially trained offline, thus, avoiding cold start issues and enabling its topology tuning. Moreover, the ANN offline training follows a incremental learning approach, where the performance evaluation metric used for the tuning process takes into account the amount of incremental retrains that are necessary on average for the ANN to adapt to a new scenario considering a deviation threshold. The predictor is subsequently trained at runtime whenever the frequency is scaled or a task is migrated, thus, setting it free from the initial synthetic task-set. Lastly, to further enable energy optimizations alongside the frequency control, a migration heuristic is proposed as a weighted activity vector based on the very same features used by the ANN.

The implemented energy optimizer is evaluated through three different tasksets composed of relevant benchmarks, where the added overhead to the embedded system execution, model accuracy and adaptability, and energy consumption reductions achieved are measured to evaluate the proposed solution.

# 1.4 CONTRIBUTIONS

This work contributes to the Computing Science area as it proposes a novel solution for DVFS and Task migration on Multicore Real-Time Embedded Systems through a lean and non-intrusive approach that builds on Machine Learning predictors. Specifically to the aforementioned area, the following contributions are achieved by this work:

- The design, implementation, and evaluation of a Non-intrusive Monitoring API.

- The design of collection and feature selection process that accounts for architectural phenomenal that is agnostic of the target task-set.

- The usage of adaptable predictors to enable safe run-time actuation even in unforeseen scenarios, thus, not disrupting the criticality of any task in the system during actuation.

- The Energy Optimizer design that encompasses machine learning based DVFS and Task migration control at run-time on a non-intrusive design.

- The proof of concept implementation and evaluation of the proposed non-intrusive Energy optimizer.

# 1.5 OVERVIEW

Chapter 2 presents an overview of the state-of-the-art solutions for energy optimization in Multicore Scenarios, focusing on Machine Learning techniques for DVFS and Task Migration. Chapter 3 presents the design of the non-intrusive Monitor API, a lean and architecture-independent monitoring API that abstracts Performance Monitoring Unit counters, OS statistics, and Sensors. The Monitor API also provides tools for run-time actuation based on monitored data. Chapter 4 presents the energy optimizer design, including the modeling of data collection, predictor design and integration, online training and actuation, and the DVFS voting system alongside the migration heuristic proposed. Moreover, Chapter 4 also includes the design of the feature extraction proposed, the offline Machine Learning Model design and its online learning integration.

Chapter 5 presents the proof of concept implementation over a Cortex-A53 architecture, including the implementation of the data analysis, online monitoring, and actuation processes proposed in this work. The energy optimizer performance is then evaluated over three aspects: (i) Energy-savings achieved, by measuring the energy consumption on the platform used for the proof of concept implementation, and comparing the results to a run-to-halt approach and Linux's Ondemand and Conservative Power Governors; (ii) Machine learning capabilities, which includes evaluating the final DVFS and Allocation configuration achieved for each scenario and measuring the predictions deviations before and after online training; (iii) Non-intrusiveness, where the proposed solution is evaluated regarding the added overhead and the impact on tasks' execution time. Moreover, a discussion covering the complete design and implementation and the presented results concludes the Chapter 5.

The work is concluded in Chapter 6, with a recapitulation of the main contributions and the presentation of the final remarks for this work.

# **2 LITERATURE REVIEW**

Real-time embedded systems manages tasks through a description of their timeliness characteristics, often represented by periodicity and deadlines. Such characteristics is used to create a notion of priority, which is a notion that varies according to scheduling policies like Earliest Deadline First (EDF), Rate Monotonic (RM), and Deadline Monotonic (DM). Moreover, by assessing a task performance demands, like its Worst Case-Execution Time (WCET) enables a offline feasibility analysis of the system scheduling. However, the intense use of parallelism and latency hiding mechanisms present in complex architectures, like modern multicore platforms, incurs into variations on the performance of running tasks (CRAEYNEST et al., 2012). Thus, offline solutions, which can only assess timing specs of tasks (i.e., Worst-Case Execution Time estimation through extensive profiling), must ensure a large resource reservation to guarantee real-time constraints. Such a large reservation ensure performance by wasting computational power and energy, requiring expensive multicore processors running at high-frequency levels to cope with the requirements imposed by only relying on offline estimations.

Several works have investigated the representativeness of PMU events monitoring on providing information of the current architectural usage, avoiding relying only on worst-case estimation. For instance, Singh et al. (SINGH et al., 2009), aiming at estimating power consumption, uses cache misses and hits, Committed Instructions rate, and Stalls. Similarly, Eyerman et al. (EYERMAN; EECKHOUT, 2010) proposes a profitability estimation of DVFS effects over a counter architecture to estimate energy consumption given a power budget. The energy consumption estimation is achieved by analyzing tasks' pipe-lined time, which is affected by DVFS, and the non-pipe-lined time, which is not. As a relevant trend, performance monitoring can lend essential information from the current task's demands. When combining meaningful performance counters with OS statistics, a broader analysis can be achieved when estimating the performance of tasks in the near future or a different configuration. In this sense, Machine Learning stands up as an alternative to automate the process of acquiring the necessary knowledge about the architectural phenomena expressed by performance traces and OS statistics, that, when provided with sufficient information, result in a reliable prediction of an outcome for actuation, and thus, enabling the definition of an actuation plan to safely optimize the Multicore Real-Time embedded system at run-time.

Controlling the power consumption of a multicore processor is an essential step to enable a balance between performance and energy. The Power Dissipation in a CMOS chip can be approximated as  $P_{core} = P_{static} + P_{dynamic}$  (RABAEY; PEDRAM, 2012), where  $P_{static}$  (also called leakage) is the power loss due to transistor leakage currents, and  $P_{dynamic}$  is the dynamic power consumption based on the current config-

uration of the processor core, which can be approximated as  $P_{dynamic} = CV^2f$ , where C is the capacitance, V is the Voltage, and f is the frequency of the processor core. So, DVFS comes as a powerful and widespread actuation strategy to improve energy-saving in a multicore platform, reducing the operating frequency and voltage of a core to reduce its power consumption (HSU, 2003). Therefore, by monitoring the system's behavior, it is possible to apply DVFS safely, and reach a better performance and energy ratio (DEHMELT, 2014). Similarly, Dynamic Power Management (DPM) mechanisms, implemented by the underlying OS, can also be used for optimizing energy consumption. They consist of putting hardware components in low-power states when they are idle (FRÖHLICH, A. A., 2011). Since bringing a component back to an operational state requires additional energy and time, this strategy must evaluate the overall energy-saving and performance impact before actuating. Moreover, alongside DVFS, an optimal task allocation can enhance both performance and energy-savings, by avoiding shared resource contention between tasks running in parallel, and by achieving a balanced load distribution between CPUs.

# 2.1 BACKGROUND

This section is dedicated to summarize the aspects that basis this work. It starts with a discussion of relevant Real-Time concepts, including task definition and criticality, and unicore and multicore scheduling. Next, relevant Machine Learning concepts for this work are discussed, including supervised learning and feature selection.

# 2.1.1 Real-Time Scheduling

A Real-Time system is characterized by a set of tasks with timing constraints, where the system behavior depends not only on the logical correctness of their execution but also on the time they are executed. A Real-Time task can be defined as a set of related jobs that provide some system function, where each job is an instance of the task that is scheduled according to the task requirements (LIU, J. W. S., 2000).

Real-Time tasks can be classified into three main task models (GRACIOLI, 2014): periodic (LIU, C. L.; LAYLAND, 1973), sporadic (MOK, 1983), and aperiodic. A periodic task model defines that each task  $T_i \in \{T_1, T_2, ..., T_n\}$ , a set of tasks  $\tau$ , releases a job at every period  $p_i$ , thus, every job  $J_{i,j}$ , the  $j^{th}$  job of task  $T_i$ , has a release time  $r_{i,j}$ , which can be expressed as  $r_{i,j} = p_i * j$ . OS operations like reschedule, priority update, and dispatch, are implemented in order to handle job scheduling, where job releases can be triggered through device interrupts or timers (GRACIOLI, 2014). Sporadic tasks, on the other hand, defines the period  $p_i$  of a task  $T_i$  as a lower bound on job separation (MOK, 1983). A Sporadic task model can be analyzed as a periodic task model if  $p_i$  is considered the minimum time interval between jobs. In the aperiodic task model,

the tasks work in an event-driven fashion instead of a time-triggered one. Thus, they can be released at any time without the specification of a period or a minimum period interval (GRACIOLI, 2014).

Moreover, in this work, it is considered that a Real-Time system task can be classified into two groups regarding their timing constraints: **hard real-time** and **soft real-time**. Tasks that have a hard deadline must never miss a deadline to be considered correct, thus, representing critical scenarios where the loss of a deadline can cause catastrophic damage (i.e., loss of human lives and money). On the other hand, on tasks that have a soft deadline, the loss of a deadline is tolerable, limited by a Quality of Service (QoS) constraint, thus, representing non-critical scenarios where only the QoS is affected, like on multimedia applications. In this way, the deadline of a task is a parameter defined to represent it's correct behavior on the system and is extended to each job j of the task  $T_i$  according to its release time, providing an absolute deadline notion. For instance, in a Periodic task model, the deadline of the  $j^{th}$  job of the task  $T_i$  is defined as  $d_{i,j} = r_{i,j} + d_i$ , thus, if the time the  $j^{th}$  job finishes its execution is  $\leq d_{i,j}$ , the job meet its deadline. In a hard real-time scenario, the correctness of a task can be expressed by  $R_j \leq d_i$ , where  $R_j$  is the maximum response time of the task's jobs (BRANDENBURG, 2011).

As this work aims at handling energy optimizations on critical systems, the periodic task model is assumed, focusing on hard real-time scenarios. Thus, a complete definition of the periodic task model is defined below.

- **Task**: In a periodic task model, each task has three basic parameters  $p_i$ ,  $d_i$ ,  $c_i$ .  $p_i$  is the period of  $T_i$  and represents the distance in time between each job of the task  $T_i$ . Thus, at every  $p_i$  units of time, a job of task  $T_i$  is released by the OS and inserted into the Scheduling Queue. The state of the job at its release is defined by the scheduler according to the scheduling policy implemented.  $d_i$  is the relative deadline of the job and represents its timing constraint.  $c_i$  represents the Worst-Case Execution Time (WCET) estimation of  $T_i$ , and provides a notion of CPU time required by the task, where  $c_i > 0$ . Worth mentioning that  $c_i$  is a static estimation and naturally depends on the hardware platform speed. Furthermore, this measure is affected by DVFS. For the WCET estimation to be accurate, it requires extensive profiling, especially for multicore platforms, where the parallel access to share resources highly affects a job execution time (GRACIOLI, 2014). On the other hand,  $p_i$  and  $d_i$  are machine-independent parameters, defined by the application design itself (BRANDENBURG, 2011).

- Jobs: A job is considered to be in Ready state when is release time r<sub>i,j</sub> is reached, and will be set to Running according to the scheduling policy implemented. In a periodic task model, a job has an absolute deadline d<sub>i,j</sub> that must be met for

its execution to be considered correct, taking at most  $c_i$  time units to run. The completion time  $f_{i,j}$  defines its correctness, respecting both the task period, where  $f_{i,j} \geq r_{i,j} | r_{i,j} = p_i * j, j \geq 0$ , and the task relative deadline  $f_{i,j} \leq d_{i,j}$ . The maximum response time  $R_i$  of a task  $T_i$  is obtained as follows:  $R_{i,j} = f_{i,j} - r_{i,j}$ ,  $R_i = max(R_{i,j})$ .

- **Deadlines**: The acceptable range of response times of a task  $T_i$  is defined by the task relative deadline  $d_i$ . If the job completion time  $f_{i,j} > d_{i,j}$ , the absolute deadline of a job, it means that the job has missed a deadline. A task deadline can be defined as implicit, constrained. A implicit deadline is defined as  $d_i = p_i$ . A constrained deadline means that  $d_i \leq p_i$ . Moreover, a task-set  $\tau$  is classified as implicit if every task  $T_i \in \tau$  is implicit. The same is valid for constrained task-sets. If a task-set is neither implicit nor constrained, it is classified as arbitrary (GRACIOLI, 2014).

- **Utilization and Density**:  $U_i$  is the utilization of task  $T_i$ , and is defined as  $\frac{c_i}{\rho_i}$ , representing the amount of time a periodic task keeps the processor busy (LIU, J. W. S., 2000). The utilization of the task-set can be approximated at design time as the sum of each task utilization:  $U_{\tau} = \sum_{T_i \in \tau} U_i$ . Considering constrained task-sets, the density measure of a task-set is a useful information in the schedulability analysis. The density  $\delta_i$  corresponds to the rate of execution of a task, and is obtained by normalizing the task utilization by its relative deadline. The density of a task  $T_i$  is defined as  $\delta_i = \frac{c_i}{\min(d_i, p_i)}$  (GRACIOLI, 2014).

- Deadline Definition Limitation: In this work, as the goal is to reduce the execution frequency of a task-set to achieve energy savings while still meeting every deadline of critical tasks, it is assumed that the task-set has implicit deadlines, as the metric used for voting and actuation is the very-own task-set measured utilization.

Considering the aforementioned definitions, several scheduling policies have been defined for real-time scenarios. Those algorithms are based on the task-set parameters of  $p_i$ ,  $d_i$ ,  $c_i$  to provide a prioritization of tasks, enabling ordering the jobs dispatching in such a way that their timing constraints are met. In this way, a design-time evaluation of the system correctness, at least when considering a static configuration (e.g., a static processor speed, and for multicore platforms, a static task allocation), is a concept presented by the literature as schedulability, where every scheduling algorithm has a respective schedulability test that aims at evaluating if the task-set is schedulable or not following its scheduling policy.

A task-set is considered **schedulable** under some policy if the scheduling algorithm is capable of providing an ordering that meets every task's jobs  $d_{i,j}$ . A task-set is said **feasible** if there exists a scheduling algorithm A such that  $\tau$  is schedulable under

A (GRACIOLI, 2014). For instance, an easy and straightforward schedulability test is that the total utilization of a task-set must fit in the computational power available (i.e.,  $U_{\tau} \leq m$ , where m is the number of processors available). Moreover, a schedulability test can be *pessimistic* and may state that a task-set is not schedulable, when in fact, it is schedulable (BRANDENBURG, 2011).

Some common assumptions for real-time scheduling algorithms are the following (BRANDENBURG, 2011):

- Tasks are independent: tasks do not share any kind of resources besides the processor.

- Jobs do not self-suspend: jobs are always ready to execute when allocated to a processor by the scheduler.

- **Jobs are preemptive**: at any time, the scheduler may replace the executing job with a higher priority job.

- **Jobs respects their periods**: jobs release are separated by their period  $p_i$ .

- Run-time overhead is negligible: the RTOS run-time overhead, such as the time for context-switch between jobs is negligible.

In this sense, some of those assumptions somehow simplify the scheduling problem, as its the case of run-time overhead being negligible and tasks being independent. OS interference caused at run-time by I/O and timer interruptions, or even the very own hardware accelerators impact (e.g., memory caches), and especially the shared resource contention present on complex multicore platforms, can create additional overhead that is complex to be modeled offline. The other assumptions are safe to be assumed in a real-time scenario, like job releases respecting their periods, self-suspension nonexistence, and jobs being preemptive.

In a non-real-time scenario, several algorithms have been proposed aiming at keeping the CPU busy at all times and deliver acceptable response times for all programs. For instance, scheduling algorithms like Round-Robin (TANENBAUM; BOS, 2015) promotes a time-slicing of the CPU between tasks in the scheduling queue. Round-Robin is a widespread scheduling algorithm that provides to the user interacting with the system a notion of multitasking even in a unicore processor, which is achieved by selecting a sufficient small slice size (called slot or quantum). Thus, at the end of a quantum, if the task has not been completed yet, the scheduler under the round-robing policy will preempt the task currently running to dispatch the next one at the head of the scheduling queue, reinserting the preempted one at the end. Priority-based algorithms, on the other hand, assigns priority to each task according to its policy and selects the one with the highest priority in the system.

In the realm of priority based-scheduling, scheduling algorithms can be classified into two types: those that assign *static* priority and those that enable *dynamic* priority assign. Real-time schedulers fit into the priority-based schedulers and can be either static or dynamic. A static algorithm relies on a more predictable scenario, where tasks priorities are assigned offline based on the task-set configuration, assuming release and execution times for all jobs in the system. The extensive offline analysis and validation available for static priority algorithms is an advantage. However, they became inflexible to variability into release and execution times (LIU, J. W. S., 2000), requiring a deterministic behavior of the execution. Dynamic schedulers, on the other hand, enables priority update at run-time at scheduling decisions. However, due to the priority changes at run-time, reaching an optimal scheduling configuration is harder. For both scenarios, a scheduling decision can be time-triggered or priority-driven, encompassing reschedule, priority updates, periodically (time-triggered), job completion, and job releases (priority-driven).

# 2.1.1.1 Unicore Real-Time Scheduling

Unicore architectures, due to the nonexistence of parallel executions, and the shared resource contention caused by them, has a lower scheduling complexity than multicore platforms, making an offline analysis of WCET more reliable as the only effect caused by multiple tasks execution is reasonably represented by it. For instance, the WCET of a task is often its first job execution, where the data and instruction caches are loaded for the first time, or a job execution where additional overhead is generated by cache lines eviction due to preemptions or the very own sequential execution of other tasks.

In this way, unicore (or uniprocessor) real-time scheduling is a well studied and formalized concept in the literature. The first work to address unicore real-time for a periodic task model was proposed by Liu and Layland (LIU, C. L.; LAYLAND, 1973), presenting scheduling policies for fixed priority and for job-level fixed priority, a class of scheduling policies in which each job of a task can have different priorities. A priority-based scheduler in a unicore scenario can be seen as a queue manager, where the queue is sort descending. Whenever a job is released, it is inserted into the queue in a position corresponding to its priority as follows:  $P(J_i) \leq P(J_{i-1} and P(J_i) \geq P(J_{i+1},$  where  $J_{i,0}$  is the highest priority job and will be selected as the next job to run at the processor.

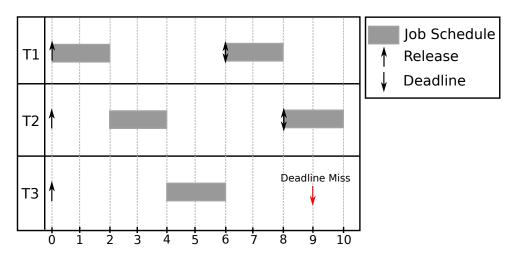

One of the fixed priority algorithms was rate monotonic (RM) (LIU, C. L.; LAY-LAND, 1973), a widespread scheduling policy that assigns priority according to the task period, in inverse relation, where the task with the shortest period has the highest priority. An example of Rate Monotonic scheduling is depicted in Figure 2. In this scenario, the task-set is composed of three hard real-time tasks: *T1* is a task that must

run for 2 units of time every 6, T2 is a task that must run for 2 units of time every 8, and T3 is a task that must run for 3 units of time every 9. This task-set presents a total utilization U = 0.9167 (91.67%), and by following Rate Monotonic scheduling, the highest priority task is T1, followed T2 and T3, respectively. In this way, whenever a job of T1 is released, it preempts any other job currently running, as it has the highest priority on the system. In the example depicted in Figure 2, at time 0 every task has a job released, and T1 is scheduled to run for 2 units of time consecutively, as it has the highest priority. At time 2, when T1 job finishes its execution, T2 job is scheduled and runs until it finishes at time 4. Then, *T3* job, which requires 3 units of time for completion, is scheduled and runs for until time 6, where a new job from T1 is released, incurring into a context switch between T1 and T3, as T1 has a highest priority. In this way, T1 runs until it finishes at time 8, where a new job of task T2 is released and subsequently scheduled to the CPU as it has a priority higher than T3. As T2 job runs for 2 units of time, it ends at time 10, while the job of T3 misses a deadline at time 9, as it still needed one unit of time of execution to finish. In this way, this task-set is not schedulable under the RM scheduling policy.

Figure 2 – Rate Monotonic Scheduling for a task-set with 91.67% of usage, presenting a deadline miss.

Liu and Layland (LIU, C. L.; LAYLAND, 1973) proposed a schedulability test for RM, where for a given task-set  $\tau$  with size n and tasks with implicit deadline,  $\tau$  is schedulable under RM if  $U_{\tau} \leq n(2^{1/n}-1)$ . In this sense, considering the limit of this function when  $n \to \infty$ , the upper bound converges to  $ln(2) \approx 0.69$ , restraining the utilization to such limit of 69.00%. For the example depicted in the previous paragraph, following the schedulability test proposed by Liu and Layland, the maximum utilization RM will be capable to handle, following this schedulability test, with n=3 will be  $3*(2^{(1/3)}-1)\approx 0.7798$ .

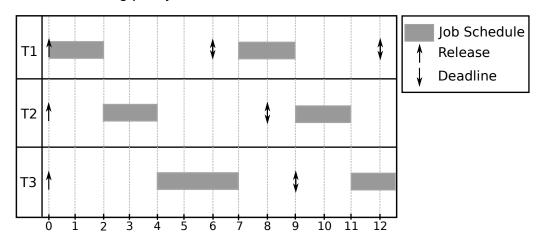

Earliest Deadline First (EDF) (LIU, C. L.; LAYLAND, 1973) is the most important and widespread job-level priority fixed scheduling algorithm (GRACIOLI, 2014). On

EDF, the priority of a job of a task is given by its absolute deadline  $d_{i,j}$ , and similarly to RM, the priority is an inverse relation, where, as the scheduling algorithm name suggest, the task with the earliest deadline has the highest priority. Moreover, EDF has been proved to have maximum utilization of 100.00%. Thus, every periodic task-set  $\tau$  with implicit deadlines is schedulable under EDF on a unicore system if and only if  $U_{\tau} \leq 1$  (LIU, C. L.; LAYLAND, 1973). An example of the EDF scheduling with the same task-set presented in Figure 2 for the RM scheduling policy is presented for EDF in Figure 3. In this scenario, as EDF assigns priorities for jobs according to their absolute deadlines  $d_{i,j}$ , at time 6, when the second job of T1 is released, its priority is assigned as 12 ( $d_{i,j} = p_i * j + d_i$ , with  $p_i = 6$ , j = 1, and  $d_i = 6$ ), while T3 first job has a priority of 9 ( $d_{3,0} = 9*0+9$ ), and finishes its execution at time 7, without missing any deadline. In this scenario, as the utilization of this task-set is 0.9167 (< 1), through the schedulability test proposed by Liu and Layland (LIU, C. L.; LAYLAND, 1973), the task-set is schedulable under EDF scheduling policy.

Figure 3 – Earliest Deadline First Scheduling for a task-set with 91.67% of usage, without presenting deadline misses.

# 2.1.1.2 Multicore Real-Time Scheduling

Multicore architectures create a more complex scenario, with an increase of the interference due to shared resource contention and the management of several CPUs executions. As previously explained, an offline analysis over the schedulability of a task-set assumes no interference between tasks, thus simplifying the analysis. In this way, critical application designers must take into account the variability of multicore architectures through WCET estimations and resource reservations, which requires extensive profiling to achieve a measure closer to reality, especially for complex scenarios with several tasks and several CPUs, as it is the case for autonomous vehicles handling computer vision applications.

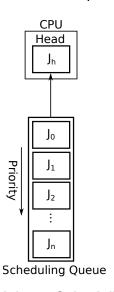

Considering a real-time scheduler as a queue manager, which orders such a queue by using tasks (or jobs) priority, the scheduling policies described in the previous

section can be extended for multicore scheduling by extending the queue design. In this way, one can reduce the problem of multicore scheduling into a set of *m* simpler unicore schedulers. The scheduling in a multicore platform can be classified into three queue configurations: Global, Partitioned, and Clustered (CARPENTER et al., 2004). On a unicore configuration, there is only one Ready queue and one Head element, where the first element of the queue is the second element with the highest priority on the system, currently awaiting for the resource, and the HEAD is the one with the highest priority, currently using the target resource (also called running or chosen()). A depiction of the Queue configuration for the unicore scenario is presented in Figure 4.

Figure 4 – Unicore Scheduling Queue.