FRANCIELE NÖRNBERG

### DESIGN OF AN ULTRA-LOW-VOLTAGE DICKSON CONVERTER BASED ON AN LC OSCILLATOR

FLORIANÓPOLIS 2019 Franciele Nörnberg

### DESIGN OF AN ULTRA-LOW-VOLTAGE DICKSON CONVERTER BASED ON AN LC OSCILLATOR

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica para obtenção do grau de "Mestre em Engenharia Elétrica".

**Orientador**: Prof. Dr. Márcio Cherem Schneider.

**Coorientador**: Prof. Dr. Márcio Bender Machado.

Florianópolis 2019

Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Nörnberg, Franciele Design of an ultra-low-voltage Dickson converter based on an LC oscillator / Franciele Nörnberg ; orientador, Márcio Cherem Schneider, coorientador, Márcio Bender Machado, 2019. 82 p. Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2019. Inclui referências. 1. Engenharia Elétrica. 2. Conversores DC-DC elevadores para ultra-baixa-tensão.. 3. Osciladores LC para ultra baixa-tensão.. 4. Circuito de inicialização. 5. Energy harvesting. I. Schneider, Márcio Cherem. II. Machado, Márcio Bender. III. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. IV. Título.

Franciele Nörnberg

### DESIGN OF AN ULTRA-LOW-VOLTAGE DICKSON CONVERTER BASED ON AN LC OSCILLATOR

O presente trabalho em nível de mestrado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Eng. Dr. Heider Marconi Madureira Chipus

Prof. Ph.D Cesar Ramos Rodrigues UFSC

Prof. Ph.D Carlos Galup Montoro, UFSC

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de Mestre em Engenharia Elétrica.

Prof. Dr. Bartolomeu Ferreira Uchôa Filho Coordenador do Programa de Pós-Graduação em Engenharia Elétrica

> Prof. Dr. Márcio Cherem Schneider Orientador

Florianópolis, 27 de Setembro de 2019.

Dedico esta monografia a minha família pelo apoio incondicional.

Aos amigos pelo convívio em momentos difíceis e alegres.

Aos professores por nortear meu caminho.

A todos que não desistem de seus ideais, seguindo sempre em frente em meio às diversidades.

## AGRADECIMENTOS

Agradeço aos meus orientadores Márcio Schneider e Márcio Bender pelo conhecimento compartilhado, pela orientação recebida e pela disposição durante a realização deste trabalho.

Agradeço aos membros da banca examinadora Heider Marconi, César Ramos e Carlos Galup pela disposição em avaliar e enriquecer este trabalho.

Agradeço aos amigos do laboratório LCI, Evandro, Luis Rodovalho, Thiago, Rafael Radin, Rodrigo, Cristina, Rafael, Victoria, Nazide e demais integrantes, com quem compartilhei muitos momentos, muito conhecimento e discussões enriquecedoras.

Agradeço à CAPES, pelo apoio financeiro, e à MOSIS pela fabricação dos circuitos prototipados.

Agradeço aos amigos Luis Otavio, Patricia, Filipe, Palloma, Vitor Couto, Ana Carolina, Joelma, Tuane, Théu, Camila, Michele e Eduarda, por todo apoio nas dificuldades, momentos de descontração e conversas sobre assuntos diversos.

Agradeço a minha família, pelo amor, incentivo e apoio incondicional.

Agradeço a Deus por ter me dado saúde e força para superar as dificuldades.

Nada dura para sempre, nem as dores, nem as alegrias. Tudo na vida é aprendizado. Tudo na vida se supera.

– Caio Fernando Abreu

## RESUMO

O presente trabalho de dissertação apresenta a análise e o projeto de conversores DC/DC Dickson operando a partir de ultrabaixa tensão, aplicados para colheita de energia. Os conversores aqui descritos, quando operam em muito baixa tensão, são normalmente utilizados como blocos de inicialização, mas podem também ser utilizados para alimentar diretamente a carga, em aplicações em que a eficiência não seja o principal requisito. Primeiramente, a operação do conversor Dickson como bomba de carga é descrita para aplicações de ultrabaixa tensão. Expressões para a tensão de saída, eficiência na conversão de energia e resistência de entrada em termos dos parâmetros físicos do diodo, da corrente de saída e do número de estágios são derivadas. A operação em ultrabaixa tensão, viabilizada pelo uso de osciladores em anel indutivos e transistores do tipo Zero-VT, é demonstrada em dois protótipos fabricados em tecnologias CMOS de 180 nm e 130 nm. Os dois conversores são totalmente integrados, tendo apresentado funcionamento a partir de 85 mV de tensão de entrada. Para tensões DC de entrada de aproximadamente 120 mV e 150 mV os conversores entregam 1  $\mu$ W na saída.

**Palavras-chave:** circuitos integrados CMOS, bomba de carga de Dickson , oscilador em anel indutivo, colheita de energia.

## **RESUMO EXPANDIDO**

#### Introdução

Os conversores do tipo bomba de carga (do inglês *charge pump*) introduzidos por Dickson [1] foram empregados em uma ampla variedade de aplicações, incluindo, por exemplo, geradores de tensão para polarização de memórias RAM e memórias flash, drivers para diodos emissores de luz e monitores de cristal líquido e conversores de corrente contínua que extraem energia de um sinal de RF [2,3]. No campo de eliminação de energia, a demanda por autonomia energética impulsionou a busca por conversores do tipo *boost* capazes de operar a partir de tensões extremamente baixas. Monitoramento *in vivo* da atividade dos órgãos humanos, por exemplo, eletrocardiograma, eletroencefalograma ou exames de pressão intra-ocular e estimulação de tecidos humanos, que geralmente consomem algumas dezenas de micro watts [4,5], abriram espaço para uma nova classe de coletores de energia (*energy harvesting*) de ultra-potência (ULP) e ultra-baixa tensão (ULV).

Em geral, a estrutura desses conversores é dividida em dois blocos: um conversor de incialização e outro de alta eficiência [6–10]. O bloco de inicialização, responsável pela operação inicial da conversor, é composto por um oscilador e um *charge pump*. O principal requisito para esse bloco é iniciar a partir de uma voltagem muito baixa, por exemplo, 50 mV ou até menos, enquanto que o oscilador de alta eficiência normalmente é um conversor do tipo boost indutivo.

Com o objetivo de gerar uma tensão DC de inicialização para os conversores boost ou fornecer energia para cargas da ordem de micro-watt a partir de baixas tensões, este trabalho apresenta conversores DC/DC construídos com conversores charge pump do tipo Dickson (DCP), juntamente com um oscilador em anel indutivo (IRO) ou um oscilador em anel aprimorado (ESRO). São apresentadas as principais equações do DCP, IRO e ESRO, que levam em consideração o acoplamento entre o DCP e o oscilador. Depois disto, os conversores foram projetados, fabricados e testados, sendo dois protótipos totalmente integrados que elevam uma tensão de entrada DC de aproximandamente 100 mV até 1 V.

#### Objetivos

O principal objetivo desta monografia foi projetar e medir conversores de inicialização totalmente integrados, com base no Dickson *charge pump* e osciladores em anel indutivo operando em tensões muito baixas para inicializar conversores eficientes.

Os objetivos específicos da tese são:

• Apresentar as análises teóricas do DCP em termos de parâmetros do diodo,

número de estágios e corrente de carga para derivar expressões para a tensão de saída, eficiência energética e resistência de entrada, válidas para operação ULV;

- Projetar um IRO e um ESRO para obter uma baixa tensão de inicialização;

- Desenvolver uma metodologia de projeto para projetar os dois blocos principais, a saber, o DCP e o oscilador;

- Analisar numericamente o comportamento dos blocos acoplados, nomeadamente DCP e oscilador;

- Projetar, prototipar e medir os conversores DC/DC.

#### ·

#### Metodologia

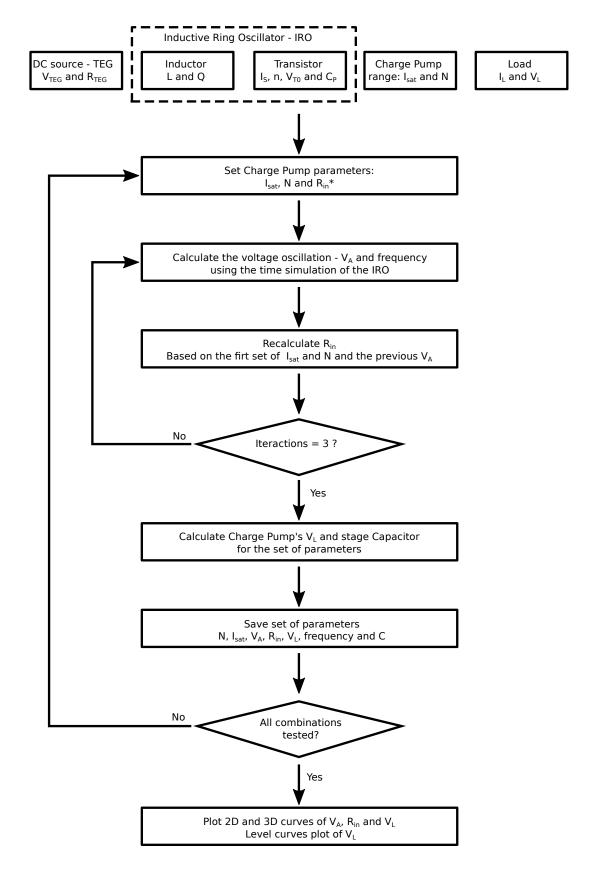

O projeto de um conversor DC-DC tem muitos graus de liberdade, como os parâmetros do oscilador e do *charge pump*. Além disso, o oscilador e o DCP não podem ser projetados independentemente, pois a amplitude do oscilador  $(V_A)$  depende de sua carga  $(R_{in})$ , a resistência de entrada do DCP, que, por sua vez, depende da amplitude do oscilador. Essa dependência mútua entre os parâmetros dos dois blocos dificulta o projeto manual do conversor.

Para tornar o projeto do conversor Dickson menos dependente do simulador de circuito, uma rotina MatLab foi desenvolvida. A rotina utiliza os parâmetros e equações desenvolvidos para o projeto do oscilador e do *charge pump*. Os parâmetros elétricos dos componentes, nomeadamente transistores, indutores e capacitores, são extraídos do simulador. Todos esses parâmetros são usados para simular o comportamento do conversor no tempo.

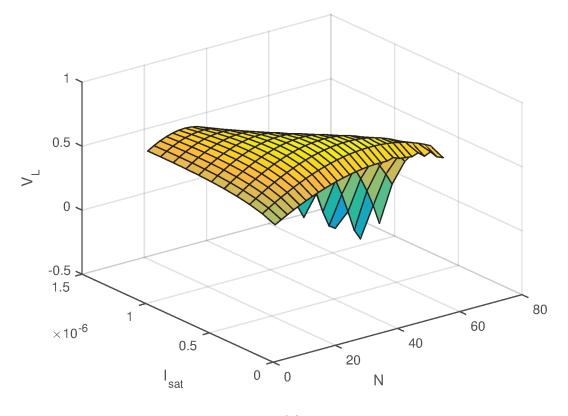

A rotina fornece uma visão geral da tensão de saída do conversor para um determinado espaço de projeto composto pelo número de estágios e pela corrente de saturação do diodo empregada no Dickson *charge pump*.

Depois que muitos dos parâmetros foram definidos, os componentes foram introduzidos no simulador para verificar o comportamento elétrico. Assim, ao encontrar a combinação de parâmetros que atende as especificações do projeto, o mesmo é passado para a fase de *layout* e fabricação do protótipo.

#### Resultados

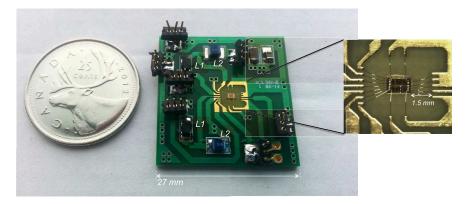

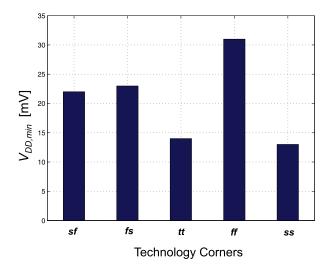

Foram implementados dois protótipos do conversor de incialização. O primeiro conversor, chamado de design DCP com IRO, foi fabricado utilizando a tecnologia CMOS 180 nm da TSMC, enquanto que o segundo, chamado de design DCP com ESRO, foi integrado na tecnologia CMOS 130 nm da IBM.

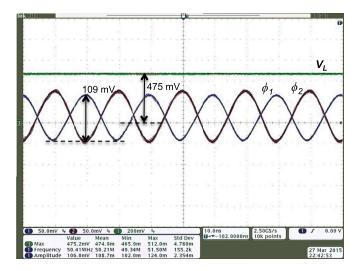

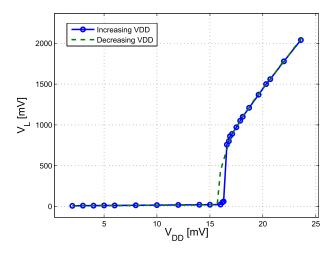

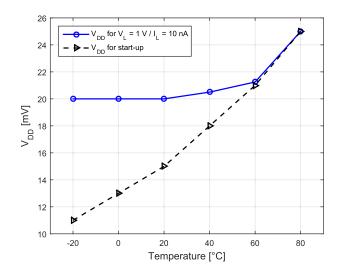

O conversor DCP com IRO apresentou tensão média de inicialização das amostras igual a 84 mV, para o conversor sem carga. Como o conversor foi projetado para suprir uma carga de 500 mV/200 nA, um resistor de 2,5 M  $\Omega$  foi usado para emular a carga. Nesta condição, o conversor inicia em  $V_{TEG} = 85$  mV e atinge a saída de 500 mV quando  $V_{TEG} = 94$  mV. Alterando a carga do conversor para um resistor de  $R_L = 1$  M  $\Omega$ , o conversor entrega  $V_L = 1$  V quando  $V_{TEG} = 120$  mV.

O conversor DCP com ESRO apresentou tensão média de inicialização das amostras medidas igual a 78,75 mV para o conversor sem carga. A tensão de entrada necessária para atingir  $V_L = 1$  V é 150,5 mV para  $R_L = 1$  M  $\Omega$ .

Para tensões DC de entrada de aproximadamente 120 mV e 150 mV os conversores entregam 1  $\mu$ W na saída.

#### Considerações Finais

As características das arquiteturas de conversores, usando um IRO ou um ESRO, apresentaram características semelhantes. Para as tecnologias empregadas, o fator de baixa qualidade dos indutores parece limitar fortemente a eficiência dos conversores. Apesar das limitações dos osciladores LC totalmente integrados que foram empregados neste trabalho, os dois conversores projetados neste documento podem ser muito úteis para iniciar um conversor eficiente.

Também apresentamos um modelo preciso do Dickson *charge pump*, que inclui a resistência de entrada do DCP com dependência explícita dos parâmetros do diodo, corrente de carga e número de estágios. A expressão derivada para a resistência de entrada é de grande valor, pois deve ser considerada no design do oscilador, pois afeta diretamente a tensão de inicialização do oscilador.

A análise computacional do conversor, que inclui a resistência de entrada do DCP, é uma ferramenta muito útil para projetar o oscilador, pois leva em consideração a influência do DCP no oscilador. Como resultado, a solução numérica assim obtida para os parâmetros DCP fornece uma entrada inicial para o simulador muito próxima da solução ótima pesquisada.

## ABSTRACT

This thesis presents the analysis and design of Dickson charge pump converters operating from low-voltage supply, for energy harvesting applications. The DC/DC converters described herein, when operating at very low voltage, are commonly used as startup blocks, but can also be used to directly supply the load in applications in which efficiency is not of major concern. Firstly, the operation of the Dickson charge pump for ultra-low voltage is described. Expressions for the output voltage, power conversion efficiency and input resistance in terms of the diode physical parameters, the output current, and the number of stages are derived. The low-voltage operation, made feasible through the use of inductive ring oscillators and zero-VT transistors, is demonstrated via two prototypes fabricated in 180 nm and 130 nm CMOS technologies. Both converters are fully integrated and started up from around 85 mV of input voltage. For input voltages of around 120 mV and 150 mV the two converters deliver 1  $\mu$ W to the load.

**Keywords:** Dickson Charge Pump, Inductive Ring Oscillator, Energy Harvesting.

# LIST OF FIGURES

| 1.1          | Hybrid configuration composed of two voltage converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

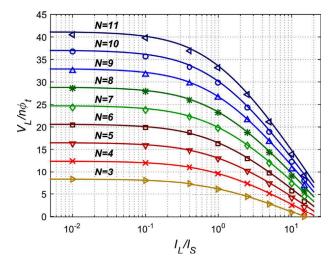

| $2.1 \\ 2.2$ | DC-DC Dickson charge pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25              |

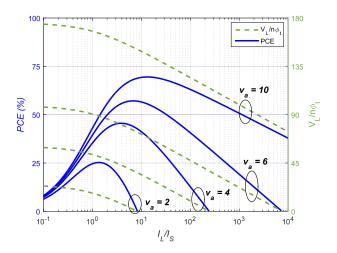

| 2.3          | capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27              |

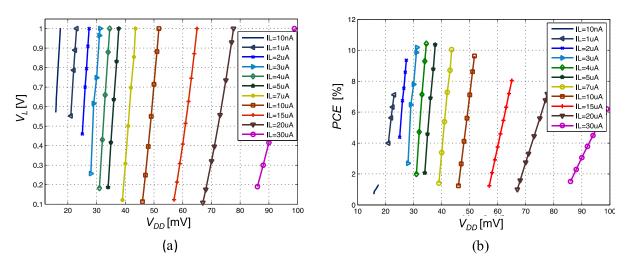

| 2.4          | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29              |

| 2.5          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30              |

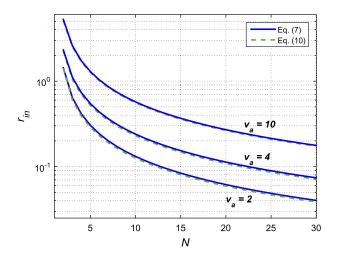

| 2.6          | oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31<br>32        |

| 2.7          | Schematic of the Dickson charge pump including the stray capacitances.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\frac{52}{33}$ |

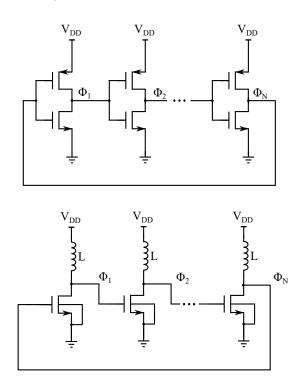

| 3.1<br>3.2   | Configurations of a conventional ring oscillator and of an inductive ring oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35              |

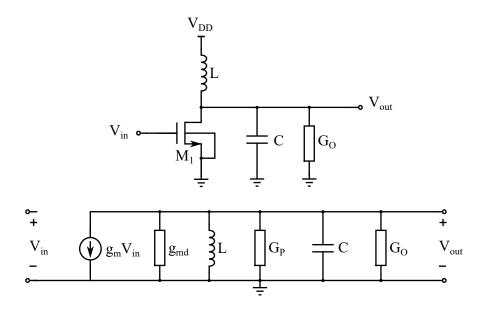

| 3.3          | signal model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\frac{36}{38}$ |

| $4.1 \\ 4.2$ | Startup schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40              |

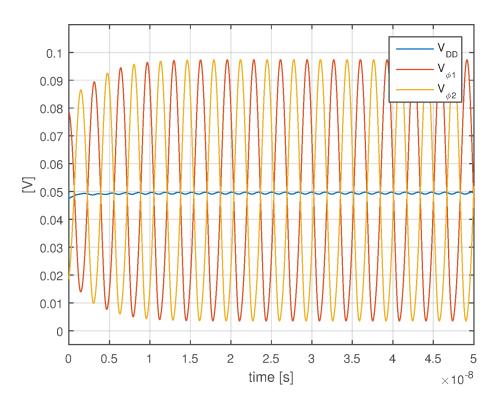

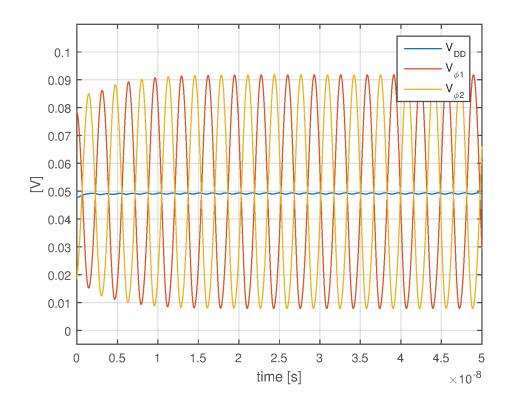

|              | both for $I_{sat} = 900$ nÅ, $N = 27$ and $V_{TEG} = 52$ mV. $(a)$ $(b)$ $(b)$ $(b)$ $(c)$ $(b)$ $(c)$ | 42<br>42<br>42  |

| 4.3          | Flowchart of the Matlab routine employed for finding the values of $I_{sat}$ and $N$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43              |

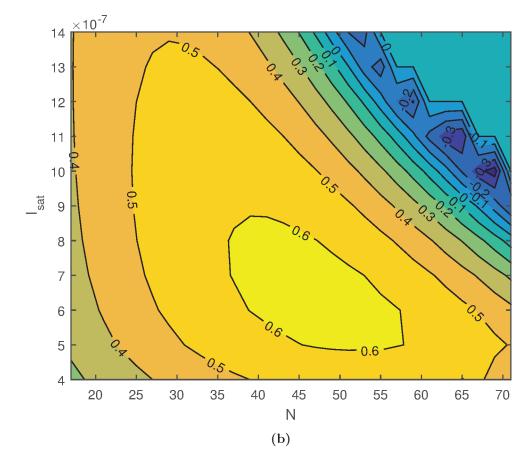

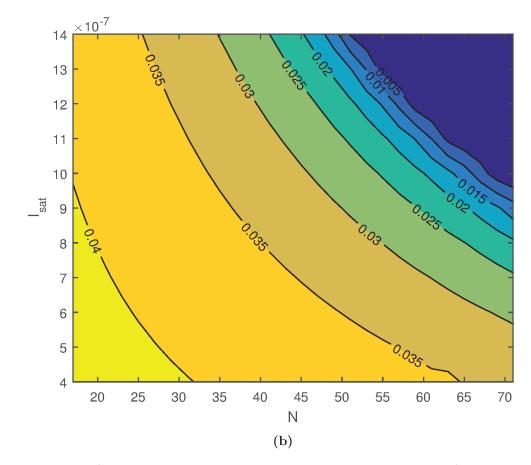

| 4.4          | a) Converter output voltage and b) Level curves of $V_L$ for $N$ varying<br>from 3 to 70, $I_{sat}$ ranging from 0.4 $\mu$ A to 1.4 $\mu$ A and $V_{TEG} = 52$ mV.<br>(a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45<br>45<br>45  |

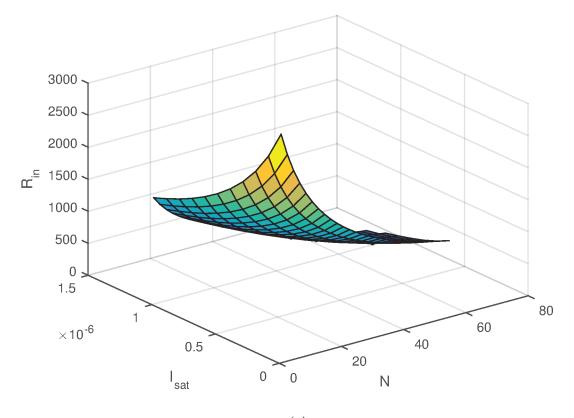

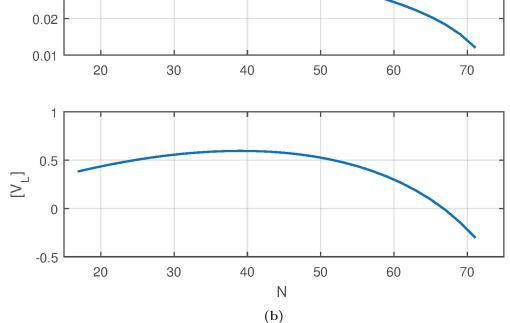

| 4.5          | a) Input resistance of the Dickson charge pump and b) Level curves of the oscillator voltage amplitude, for $N$ varying from 3 to 70, $I_{sat}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

|              | ranging from 0.4 $\mu$ A to 1.4 $\mu$ A and $V_{TEG} = 52$ mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46<br>46        |

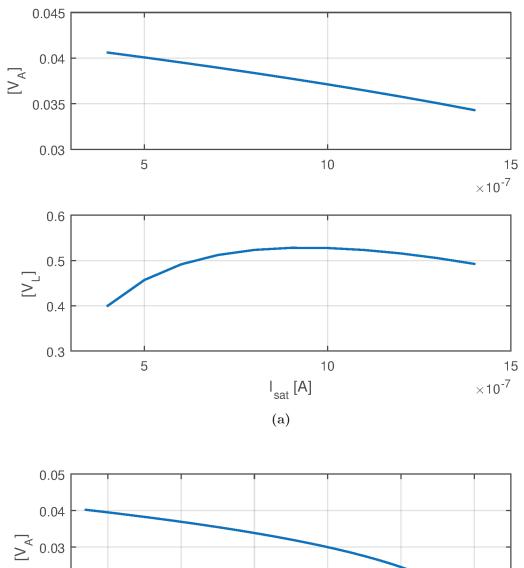

| 4.6          | (b)Oscillator and DCP output voltage variation for $V_{TEG} = 52$ mV. a) $V_A$ and $V_L$ versus $I_{sat}$ for $N = 27$ . and b) $V_A$ and $V_L$ versus N for $I_{sat} = 900$ nA.(a)(b)(b) | 46<br>47<br>47<br>47 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

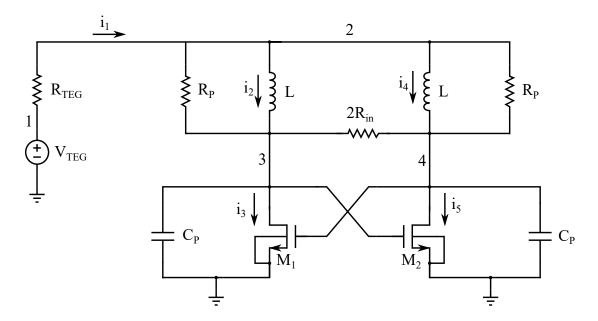

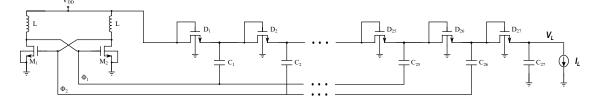

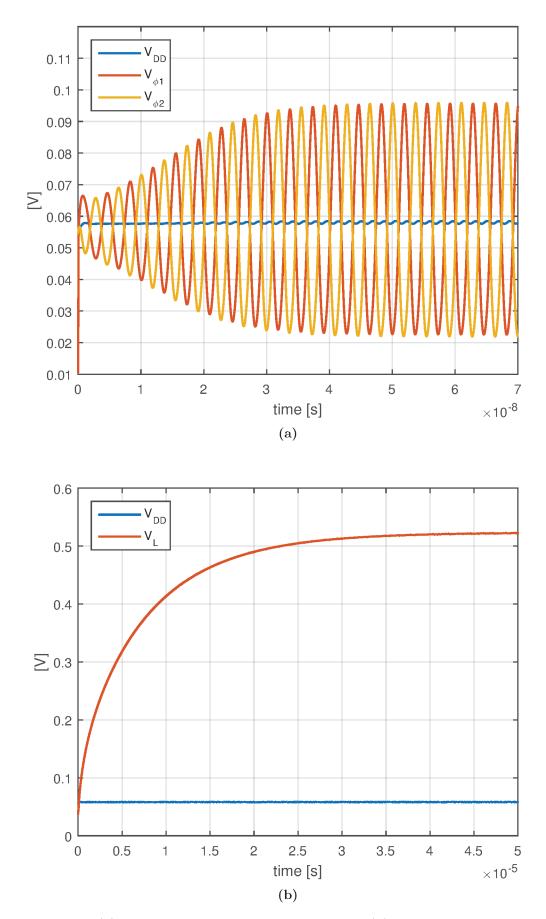

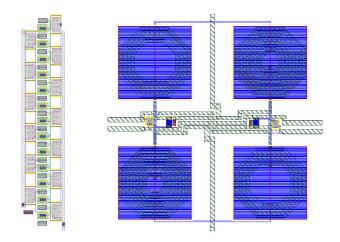

| $5.1 \\ 5.2$ | Schematics of the Dickson design with IRO                                                                                                                                                 | 49                   |

|              | $V_{TEG} = 63 \text{ mV}$ and $R_{TEG} = 5 \Omega$ . The converter load is $R_L = 2.5 \text{ M}\Omega$ .<br>(a)                                                                           | 50<br>50             |

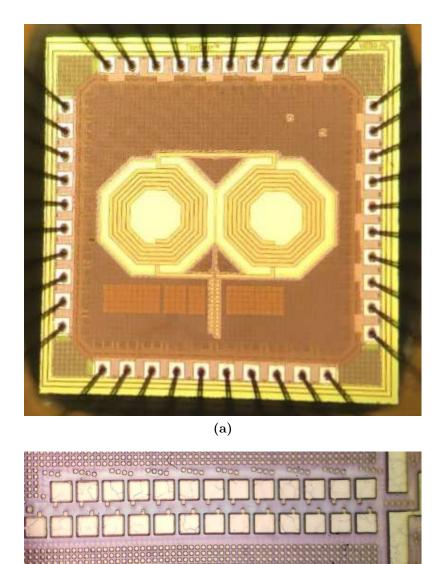

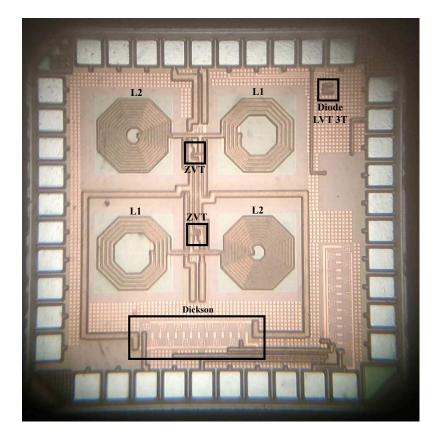

| 5.3          | <ul> <li>(a) Micrograph of the chip of the Dickson converter using IRO; (b)</li> </ul>                                                                                                    | 50                   |

| 0.0          | Detail of the micrograph showing the Dickson charge pump                                                                                                                                  | 51                   |

|              | (a)                                                                                                                                                                                       | 51                   |

|              | (b)                                                                                                                                                                                       | 51                   |

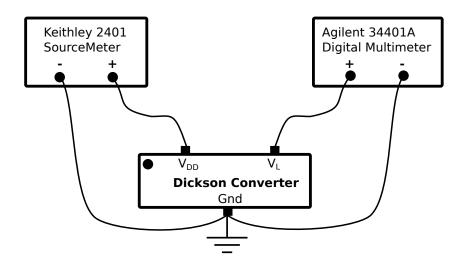

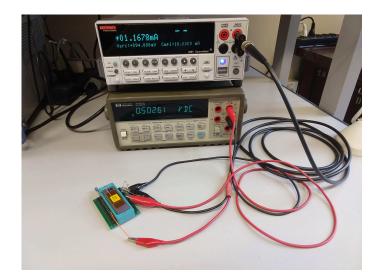

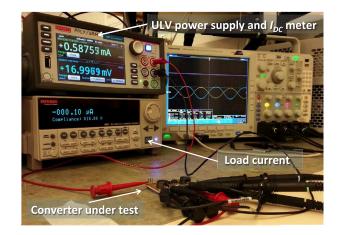

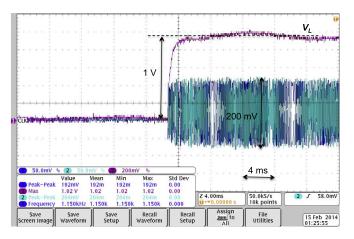

| 5.4          | Measurement setup of the DC/DC converter                                                                                                                                                  | 52                   |

| 5.5          | Setup for measuring the converter output voltage                                                                                                                                          | 52                   |

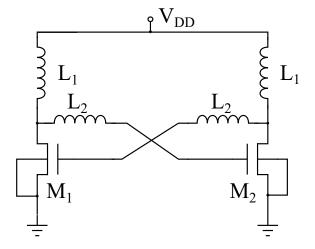

| 5.6          | Schematics of the converter, ESRO followed by the DCP                                                                                                                                     | 54                   |

| $5.7 \\ 5.8$ | DCP (left) and ESRO (right) layouts, not drawn to scale                                                                                                                                   | $55 \\ 55$           |

|              |                                                                                                                                                                                           |                      |

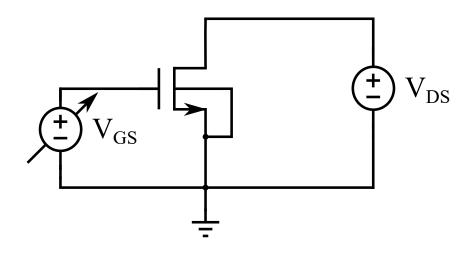

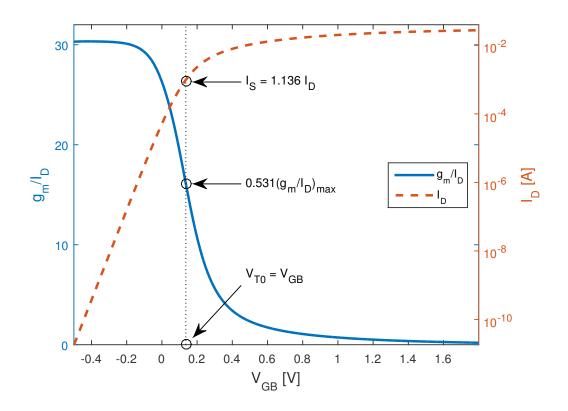

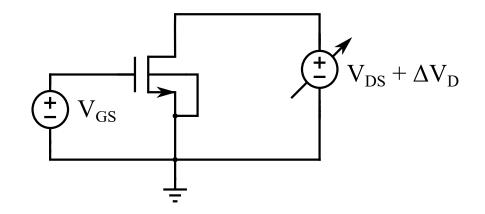

| A.1<br>A.2   | Circuit configuration for transistor parameter extraction Transconductance-to-current ratio and drain current vs. gate voltage                                                            | 64                   |

| 1.0          | of a native NMOS with $W/L = 2496 \ \mu m/500 \ nm$ , for $V_{DS} = \phi_t/2$ .                                                                                                           | 65<br>65             |

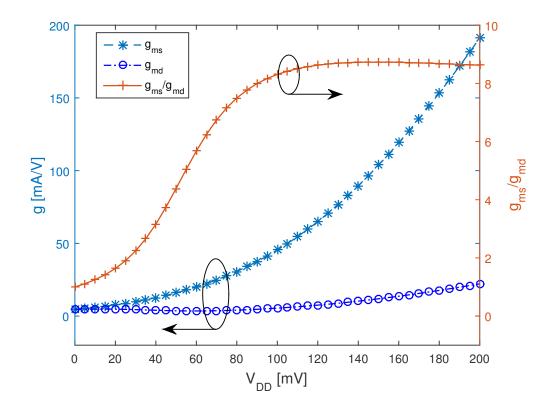

| A.3<br>A.4   | Circuit configuration for transistor transconductances extraction<br>Drain and source transconductances, and their ratio, for the native                                                  | 65                   |

|              | NMOS transistor of the 180 nm technology, with $W/L = 2496 \ \mu m/500$                                                                                                                   |                      |

|              | nm, for $V_{DD} = 0$ to 200 mV                                                                                                                                                            | 66                   |

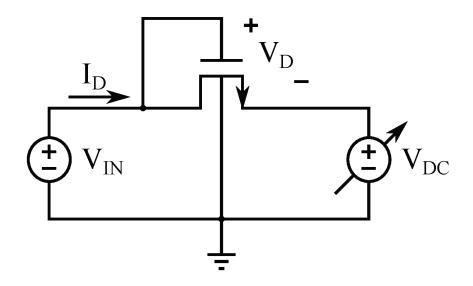

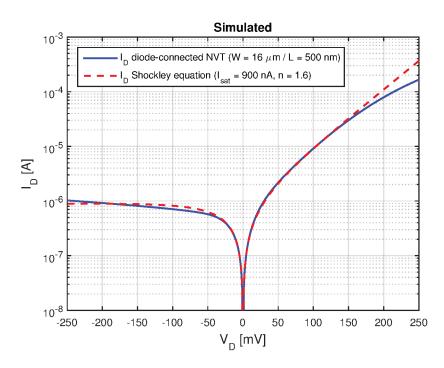

| A.5          | Circuit configuration for the extraction of the diode parameters                                                                                                                          | 67                   |

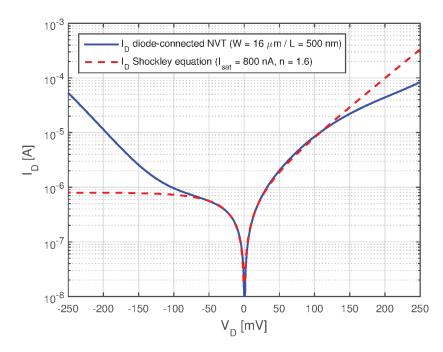

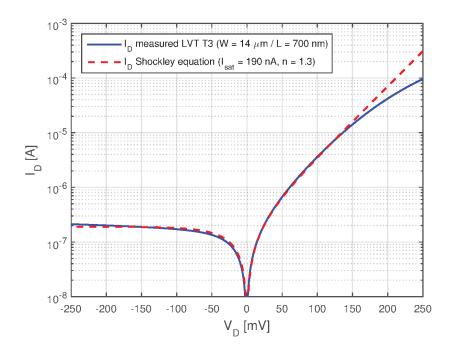

| A.6<br>A.7   | $I_D$ current fitting by Shockley equation with $V_{IN} = 50 \text{ mV}.$ Measured $I_D$ current of diode-connected native transistor on chip C                                           | 67                   |

| A.1          | and fitting by Shockley equation.                                                                                                                                                         | 68                   |

| A.8          | Fitting of measured diode current by Shockley equation (dashed line).                                                                                                                     | 69                   |

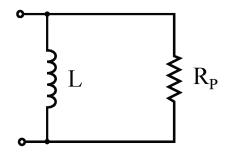

| A.9          | Inductor equivalent circuit                                                                                                                                                               | 70                   |

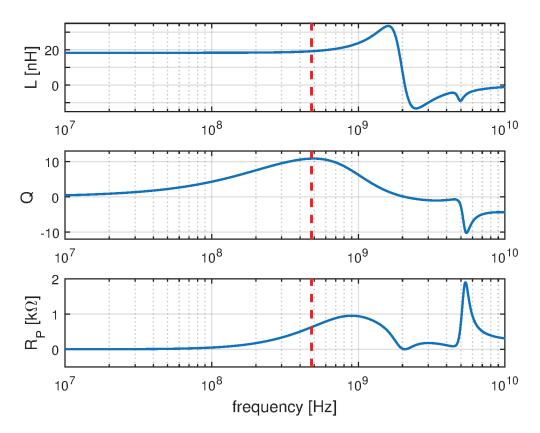

|              | Inductance and quality factor versus frequency.                                                                                                                                           | 70                   |

# LIST OF TABLES

| 1.1          | Main characteristics of converters that use hybrid topology and a                                                                            | 22       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2          | TEG as a voltage source                                                                                                                      | 23<br>24 |

| 2.1          | Dickson charge pump equations                                                                                                                | 34       |

| 4.1          | $R_{in}$ and $V_A$ variation over 4 iterations for $I_{sat} = 900$ nA, $N = 27$ and                                                          |          |

| 4.2          | $V_{TEG} = 52 \text{ mV.}$ Oscillator parameters                                                                                             | 41<br>44 |

| 5.1          | Dickson design with IRO Oscillator parameters.                                                                                               | 49       |

| 5.2          | Startup voltage for the converter loaded with the multimeter probe $(R_{in} > 10 \text{ G}\Omega)$                                           | 51       |

| 5.3          | Converter input voltage $(V_{TEG})$ and current $(I_{TEG})$ for $I_L = 200$ nA                                                               | 59       |

| 5.4          | and $V_L$ equal to 500 mV and 1 V                                                                                                            | 53       |

| 5.5          | and $V_L$ equal to 500 mV and 1 V                                                                                                            | 53       |

| 0.0          | and $V_L$ equal to 500 mV and 1 V                                                                                                            | 53       |

| $5.6 \\ 5.7$ | Converter parameters                                                                                                                         | 54       |

| 5.8          | and loaded converter                                                                                                                         | 56       |

|              | loads value.                                                                                                                                 | 56       |

| A.1          | Diode-connected native transistor characterization.                                                                                          | 68       |

| A.2<br>A.3   | Diode measured parameters                                                                                                                    | 69       |

|              | $N = 5.5$ , inner radius = 150 $\mu$ m, spacing between turns = 3 $\mu$ m and guard ring distance = 50 $\mu$ m.                              | 71       |

| A.4          | Capacitors and their respective stray capacitances considering ground connected to the bottom (position 1) and top (position 2) plate of the |          |

|              | capacitors                                                                                                                                   | 71       |

# LIST OF ABBREVIATIONS

| Abbreviation | Description                                       |

|--------------|---------------------------------------------------|

| AC           | Alternating Current                               |

| ACM          | Advanced Compact MOSFET Model                     |

| CMOS         | Complementary MOS                                 |

| DC           | Direct Current                                    |

| DCP          | Dickson Charge Pump                               |

| ESRO         | Enhanced Swing Ring Oscillator                    |

| IRO          | Inductive Ring Oscillator                         |

| LC           | Inductive-Capacitive oscillator                   |

| MOS          | Metal-Oxide-Semiconductor                         |

| MOSFET       | Metal-Oxide-Semiconductor Field-Effect Transistor |

| MOSIS        | Metal-Oxide-Semiconductor Implementation Service  |

| NMOS         | N-Channel MOS                                     |

| PCE          | Power Converter Efficiency                        |

| PMOS         | P-Channel MOS                                     |

| RO           | Ring Oscillator                                   |

| TEG          | Thermoelectric Generator                          |

| T3LVT        | Triple-Well Low Voltage Threshold                 |

| ULP          | Ultra Low Power                                   |

| ULV          | Ultra Low Voltage                                 |

| WI           | Weak Inversion                                    |

| ZVT          | Zero Voltage Threshold                            |

# LIST OF SYMBOLS AND ACRONYMS

| Symbol            | Description                                              | Unity     |

|-------------------|----------------------------------------------------------|-----------|

| $C_{db}$          | Drain-bulk capacitance                                   | [F]       |

| $C_{gb}$          | Gate-bulk capacitance                                    | [F]       |

| $C_{gs}$          | Gate-source capacitance                                  | [F]       |

| $C_{jd}$          | Drain junction capacitance                               | [F]       |

| $C_{db}$          | Drain-bulk capacitance                                   | [F]       |

| $C_{ox}^{\prime}$ | Oxide capacitance per unit area                          | $[F/m^2]$ |

| $C_p$             | Parasitic capacitance                                    | [F]       |

| $f_{osc}$         | Oscillation frequency                                    | [Hz]      |

| $g_m$             | Gate transconductance                                    | [A/V]     |

| $g_{mb}$          | Bulk transconductance                                    | [A/V]     |

| $g_{md}$          | Drain transconductance                                   | [A/V]     |

| $g_{ms}$          | Source transconductance                                  | [A/V]     |

| $G_P$             | Inductor parallel conductance                            | [S]       |

| $G_o$             | Load conductance                                         | [S]       |

| $I_0$             | Modified Bessel function of the first kind of order zero |           |

| $I_1$             | Modified Bessel function of the first kind of order one  |           |

| $I_D$             | Drain current                                            | [A]       |

| $i_f$             | Forward normalized current                               |           |

| $I_F$             | Forward saturation current                               | [A]       |

| $i_r$             | Reverse normalized current                               |           |

| $I_R$             | Reverse saturation current                               | [A]       |

| $I_{sat}$         | Diode saturation current                                 | [A]       |

| $I_S$             | Specific current (normalization current)                 | [A]       |

| k                 | Boltzmann's constant $(1,38 \ge 10^{-23})$               | [J/K]     |

| L                 | channel length                                           | [m]       |

| n                 | Transistor slope factor                                  |           |

| n                 | Diode ideallity factor                                   |           |

| N                 | Number of stages                                         |           |

| $P_D$             | Diode power dissipated                                   | [W]       |

| $P_{in}$          | Input power                                              | [W]       |

| $P_{loss}$        | Power loss due to the diodes of the DCP                  | [W]       |

| $P_{out}$  | Output power                               | [W]        |

|------------|--------------------------------------------|------------|

| q          | Electronic charge $(1,6 \ge 10^{-19})$     | [C]        |

| Q          | Inductor quality factor                    |            |

| $R_{in}$   | Dickson input resistance                   | $[\Omega]$ |

| $r_{in}$   | Dickson normalized input resistance        |            |

| $R_S$      | Inductor series resistance                 | $[\Omega]$ |

| $R_{TEG}$  | Thermoelectric generator resistance        | $[\Omega]$ |

| T          | Absolute Temperature                       | [K]        |

| $v_a$      | Peak amplitude normalized of a sine signal |            |

| $V_A$      | Peak amplitude of a sine signal            | [V]        |

| $V_B$      | Bulk voltage                               | [V]        |

| $V_d$      | Diode forward voltage drop                 | [V]        |

| $V_D$      | Voltage across the diode                   | [V]        |

| $V_D$      | Drain voltage                              | [V]        |

| $V_{DD}$   | Supply voltage                             | [V]        |

| $V_{DS}$   | Drain-Source voltage                       | [V]        |

| $V_{\phi}$ | Sine signal                                | [V]        |

| $V_G$      | Gate voltage                               | [V]        |

| $V_L$      | Load Voltage                               | [V]        |

| $V_{in}$   | Input voltage                              | [V]        |

| $V_{out}$  | Output voltage                             | [V]        |

| $V_P$      | Pinch-off voltage                          | [V]        |

| $V_S$      | Source voltage                             | [V]        |

| $V_{T0}$   | Threshold voltage                          | [V]        |

| $V_{TEG}$  | Thermoelectric generator voltage           | [V]        |

| W          | Channel width                              | [m]        |

| $\phi_t$   | Thermal voltage                            | [V]        |

| ω          | Angular frequency                          | [rad/s]    |

|            |                                            |            |

# CONTENTS

| 1        | INT | TRODUCTION                                     | 22 |

|----------|-----|------------------------------------------------|----|

|          | 1.1 | Main and specific goals                        | 24 |

|          | 1.2 | Thesis organization                            | 24 |

| <b>2</b> | DIC | CKSON CHARGE PUMP                              | 25 |

|          | 2.1 | Introduction                                   | 25 |

|          | 2.2 | Dickson Charge Pump for ULV                    | 26 |

|          |     | 2.2.1 Output Voltage of the DCP - $V_L$        | 26 |

|          |     | 2.2.2 Power Conversion Efficiency - <i>PCE</i> | 28 |

|          |     | 2.2.3 DCP Input Resistance - $R_{in}$          | 31 |

|          |     | 2.2.4 DCP Coupling Capacitor - $C$             | 33 |

|          |     | 2.2.5 DCP Stray Capacitor - $C_s$              | 33 |

|          | 2.3 | Design Equations                               | 33 |

| 3        | LOV | W-VOLTAGE LC OSCILLATORS                       | 35 |

|          | 3.1 | Introduction                                   | 35 |

|          | 3.2 | Inductive Ring Oscillator - IRO                | 36 |

|          |     | 3.2.1 Frequency of oscillation                 | 36 |

|          |     | 3.2.2 Minimum transistor gain for start-up     | 37 |

|          |     | 3.2.3 Minimum start-up voltage                 | 37 |

|          | 3.3 | Enhanced Swing Ring Oscillator - ESRO          | 38 |

| 4        | CO  | MPUTATIONAL ANALYSES                           | 39 |

|          | 4.1 | Initial Conditions                             | 39 |

|          | 4.2 | Time analyses                                  | 40 |

|          | 4.3 | MatLab routine                                 | 41 |

|          | 4.4 | Converter design space                         | 41 |

| <b>5</b> | DES | SIGN AND EXPERIMENT                            | 48 |

|          | 5.1 | DCP design with IRO                            | 48 |

|          |     | 5.1.1 Schematic Simulation and Layout          | 48 |

|          |     | 5.1.2 Experimental Results                     | 49 |

|          | 5.2 | DCP design with ESRO                           | 54 |

|          |     | 5.2.1 Schematics Simulation and Layout         | 54 |

|          |     | 5.2.2 Experimental Results                     | 55 |

|          | 5.3 | Discussion                                     | 56 |

| 6.1   | Future Work                                   | 58 |

|-------|-----------------------------------------------|----|

| REFEI | RENCES                                        | 59 |

| APPE  | NDIX A COMPONENTS ANALYSES                    | 63 |

| A.1   | Transistor Model                              | 63 |

| A.2   | Transistor Characterization                   | 64 |

|       | A.2.1 Extraction of $V_T$ , $I_S$ and $n$     | 64 |

|       | A.2.2 Extraction of the Transconductances     | 65 |

|       | A.2.3 Extraction of the Parasitic Capacitance | 66 |

|       | A.2.4 Diode-Connected Transistor              |    |

| A.3   | Inductor Model                                | 69 |

| A.4   | Capacitor model                               | 71 |

| APPE  | NDIX B MATLAB ROUTINE                         | 72 |

| B.1   | IRO function                                  | 72 |

| B.2   | nmos ACM function                             | 73 |

| B.3   | Initial Conditions                            | 74 |

| APPE  | NDIX C PAPER ACCEPTED TO ELSEVIER MICROELEC-  |    |

|       | ICS JOURNAL                                   | 75 |

### 1. INTRODUCTION

The charge pump converters introduced by Dickson [1] have been employed in a wide variety of applications, including, for example, bias generators for dynamic random access memories and flash memories, drivers for light emitting diodes and liquid crystal displays, and AC-DC converters that harvest energy from a RF signal [2,3]. In the energy scavenging field, the demand for energy autonomy has driven the search for boost converters able to operate from extremely low voltages. *In vivo* monitoring of human organs activity, *e.g.* electrocardiogram, electroencephalogram, or intraocular pressure examinations, and stimulation of human tissues, which generally consume some dozens of micro-watts [4, 5], open space for a new class of ultra-low-power (ULP) and ultra-low-voltage (ULV) energy harvesters.

Solar cells in dark environments [11], wearable thermoelectric generators [6] and implantable glucose fuel cells [12], which typically generate less than 100 mV, are appealing choices to power the electronics of sensor networks and biomedical appliances. However, given the ULV levels generated by these energy harvesters, a boost converter is required to power conventional electronics which, in general, demands supply voltages around 1 V.

In the past decade, in an attempt to reduce the minimum voltage required to start up converters, many researchers have presented solutions employing schematics based on charge pumps or inductive boost converters. A challenge in the design of converters powered from voltages below 50 mV is the start-up stage, due to the low efficiency of devices operating at ULV and the need to generate oscillatory signals from such a low voltage.

In [4], a body sensor node is powered from a supply voltage of 30 mV of a thermoelectric harvester, but wireless RF power is provided for the kick start. In [13], a boost converter that works at minimum voltage of 30 mV, requires at least 50 mV to starts up. In [14], a 35 mV boost converter is presented; nevertheless, it requires a mechanical switch for the kick start of the converter. All these converters use off-chip inductors to start up. A start-up converter of 80 mV is presented in [15], but it requires a threshold-voltage-tuned oscillator in order to decrease the minimum start-up voltage. In recent publications [16–18], fully integrated solutions with no tuning processes are proposed, but they operate from around 100 mV.

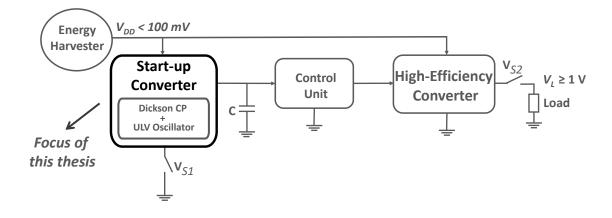

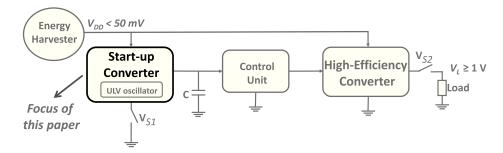

In order to deal with the conflicting requirements of very low voltage for the converter start-up and the high power conversion efficiency, the use of a hybrid configuration composed of two converters, similar to that shown in Fig. 1.1, has been widely employed [6–10]. Reference [6] reports a thermoelectric energy harvester which starts up from 65 mV. In [7], an on-chip transformer-based LC oscillator starts up at an open-circuit-voltage of 160 mV. [8] reports a DC-DC converter that operates from a 7 mV supply voltage, but requires a minimum self-start voltage of

210 mV. In [9], a start-up converter based on a ring oscillator and a charge pump starts up at 60 mV. In the converter of [10], an inductor of the start-up Colpitts oscillator is reused in the main boost converter to minimize the number of off-chip components, but it starts up from a minimum of 40 mV.

Figure 1.1: Hybrid configuration composed of two voltage converters.

The main characteristics of these converters are summarized in Table 1.1. All of them, which use a hybrid topology implemented in CMOS technology, have a boost converter as the main converter. These converters use a thermoelectric generator (TEG) as a voltage source and employ some off-chip components.  $V_{DD}$  is the source voltage,  $V_{out}$  is the load voltage and PCE is the Power Conversion Efficiency of the full converter.

**Table 1.1:** Main characteristics of converters that use hybrid topology and a TEG as a voltage source.

| Reference        | $V_{DD}$         | Vout             | PCE (end-to-end)            | Process           | Off-Shelf              |

|------------------|------------------|------------------|-----------------------------|-------------------|------------------------|

| Rozgic $(2017)$  | 65  mV           | $1.8 \mathrm{V}$ | 68~%@ 200 mV                | 65  nm            | inductor + capacitor   |

| Qian $(2018)$    | $160~{\rm mV}$   | $1.5 \mathrm{V}$ | 74~%@ 200 mV                | $180~\mathrm{nm}$ | oscillator + regulator |

| Luo $(2018)$     | $45~\mathrm{mV}$ | $1.5 \mathrm{V}$ | $41~\%$ @ $240~\mathrm{mV}$ | 65  nm            | inductor               |

| Dezyani $(2018)$ | $60 \mathrm{mV}$ | $1.0 \mathrm{V}$ | $47~\%$ @ $300~\mathrm{mV}$ | $180~\mathrm{nm}$ | inductor + capacitor   |

| Lim (2018)       | $40~{\rm mV}$    | $1.1 \mathrm{V}$ | $75~\%$ @ $150~\mathrm{mV}$ | 65  nm            | inductors              |

In general, the start-up converter, responsible for the initial operation of the harvester, is composed of an oscillator and a charge pump. The main requirement for this block is to start up from a very low voltage, *e. g.* 50 mV or even less. Power conversion efficiency is not the primary concern for the start-up block, since it can be turned off after the voltage on capacitor C has reached the minimum voltage required to operate the high-efficiency converter, as can be seen in Fig. 1.1. To kick start the circuit at extremely low voltages, a charge pump has been commonly used, as shown in Table 1.2. In the table,  $V_{DD}$  is the start-up voltage and IRO and RO mean Inductive Ring Oscillator and (conventional) Ring Oscillator, respectively.

Aiming at the generation of a DC voltage to kick-start boost converters or directly supply micro-watt loads from low voltages, this thesis presents DC/DC

| Reference     | $V_{DD}$         | Oscillator | Charge Pump (CP)            |

|---------------|------------------|------------|-----------------------------|

| Rozgic (2017) | $65 \mathrm{mV}$ | IRO        | 8-stage Dynamic CTS         |

| Qian $(2018)$ | $160~{\rm mV}$   | LC         | 10-stage CP                 |

| Luo (2018)    | $210~{\rm mV}$   | RO         | 3-stage Pelliconi CP        |

| Dezyani (2018 | 60  mV           | RO         | 40-stage Dickson CP         |

| Lim (2018)    | $40~{\rm mV}$    | Colpitts   | 10-stage Voltage Multiplier |

Table 1.2: Main characteristics of start-up converters based on charge pump.

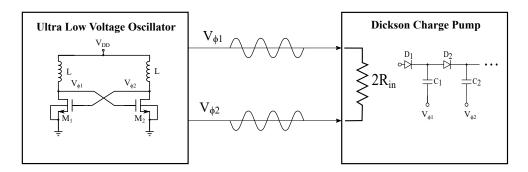

converters built with the Dickson charge pump (DCP) along with either an IRO or an Enhanced Swing Ring Oscillator (ESRO). The main equations of the DCP, IRO and ESRO, which take into account the coupling between the DCP and the oscillator, are presented . After all, the converters were designed and two fully integrated prototypes that convert a DC input voltage from down to 100 mV up to 1 V were fabricated and tested.

### 1.1. Main and specific goals

The main goal of this thesis has been to design and measure fully integrated start-up converters, based on Dickson charge pump and inductive ring oscillators operating at very low voltages in order to start up efficient converters.

Specifics goals of the thesis are:

- To present the theoretical analyses of the DCP in terms of the diode parameters, the number of stages, and the load current in order to derive expressions for the output voltage, power efficiency and input resistance, valid for ULV operation;

- To design both an IRO and an ESRO in order to achieve a low start-up voltage;

- To develop a design methodology to design the two main blocks, namely the DCP and the oscillator;

- To analyze numerically the behavior of the coupled blocks, namely DCP and oscillator;

- To design, prototype and measure the DC/DC converters.

#### 1.2. Thesis organization

The thesis is organized as follows. The ULV model of the Dickson charge pump is developed in Chapter 2. Chapter 3 presents the analyses of the ULV oscillators . A computational analysis of the converter is shown in Chapter 4. In the following, Chapter 5 presents the design and experimental results of the DC/DC converters. Chapter 6 concludes the thesis.

## 2. DICKSON CHARGE PUMP

### 2.1. Introduction

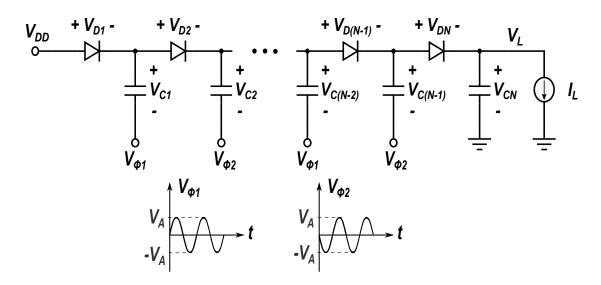

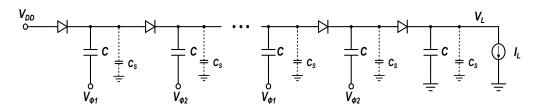

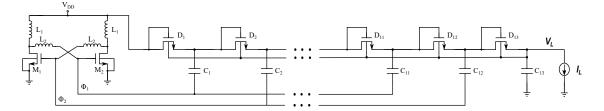

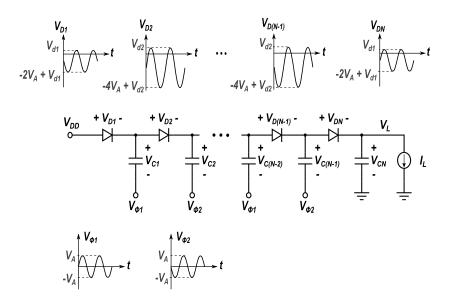

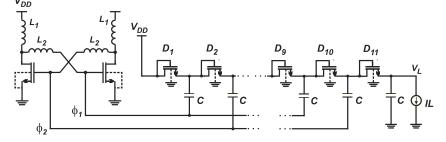

The Dickson charge pump is an DC-DC converter, based on the voltage multiplier concept first presented by Heinrich Greinacher [19], in which the nodes of a diode chain are coupled to the AC inputs via capacitors, as shown in Fig. 2.1 [1].

Figure 2.1: DC-DC Dickson charge pump.

The Dickson charge pump shown in Fig. 2.1 requires two out-of-phase clocks,  $V_{\phi 1}$  and  $V_{\phi 2}$ , but it can also operate from a single-phase generator. Briefly, looking the circuit shown in Fig. 2.1, assuming steady state and that the forward voltage drop across each diode is the same [1], the Dickson output voltage is given by

$$V_{L,ideal} = V_{DD} + (N-1)2V_A - NV_D$$

(2.1)

in which N is the number of stages,  $V_D$  is the diode voltage drop and  $V_A$  is the peak voltage of  $V_{\phi}$ . Here, ideal means that the stray capacitances from the intermediate nodes to ground are negligible and the voltage ripple in the capacitors is very small. This approach gives a good approximation of the Dickson output voltage. However, the diode forward voltage drop was not made explicit in terms of the circuit parameters in [1]. As we shall see in the following, an appropriate estimate of the value of  $V_D$  is essential for the calculation of the output voltage, especially for ultra-low-voltage converters.

### 2.2. Dickson Charge Pump for ULV

To analyze the DCP down to input voltages of the order of dozens of mV, its model should consider that the forward voltage drop across the diodes is not constant and is dependent on both the diode physical parameters and the load current. In [16, 20], the output voltage of the Dickson charge pump was analyzed for a square wave as the oscillatory signal. Based on this previous work, we have modeled the DCP's output voltage, power converter efficiency and input resistance for a sinusoidal wave, as shown in Fig. 2.1.

Firstly, the diode is modeled by the Shockley equation [16, 20, 21] below

$$I_D = I_{sat} \left( e^{\frac{V_D}{n\phi_t}} - 1 \right) \tag{2.2}$$

in which  $I_{sat}$  is the diode saturation current, n is the diode ideality factor, and  $\phi_t$  is the thermal voltage (kT/q).

Secondly, in steady state the diode average current is equal to the load current,  $I_L$ , *i. e.*

$$I_L = \frac{1}{2\pi} \int_{-\pi}^{\pi} I_{sat} \left( e^{\frac{V_D}{n\phi_t}} - 1 \right) d\theta \tag{2.3}$$

These assumptions are applied in the next sections in order to model the DCP. These equations are summarized in a recent paper [22].

### 2.2.1. Output Voltage of the DCP - $V_L$

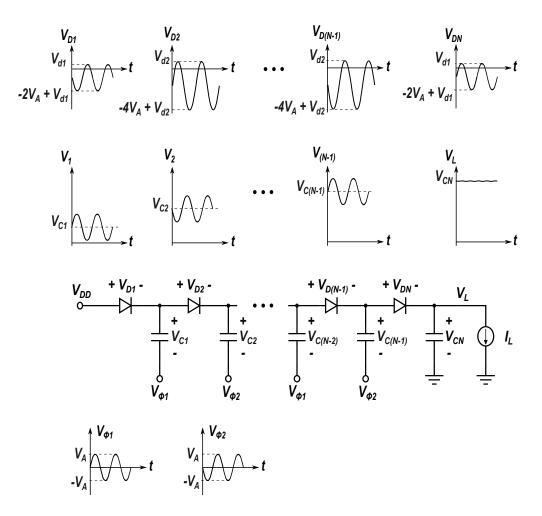

Figure 2.2 shows the DCP schematics and the voltage drop across the diodes and capacitors under steady state operation. The voltage waveforms of the leftmost and rightmost diode behave differently from the intermediate diodes, because both  $D_1$  and  $D_N$  have one terminal connected to a DC voltage ( $V_{DD}$  and  $V_L$ , respectively). Therefore, the average voltage across  $D_1$  and  $D_N$  are the same,  $\overline{V_{D1}} = \overline{V_{DN}}$ , while, for the other diodes, the average voltage across them are equal, *i.e.*  $\overline{V_{D2}} = \dots = \overline{V_{D(N-1)}}$ [16, 20].

Hence, the DCP output voltage (2.1) is rewritten as

$$V_{L} = V_{DD} - \overline{V_{D1}} - \overline{V_{D2}} - \dots - \overline{V_{D(N-1)}} - \overline{V_{DN}}$$

$$V_{L} = V_{DD} - 2\overline{V_{D1}} - (N-2)\overline{V_{D2}}$$

(2.4)

The diode voltages  $V_{D1}$  and  $V_{D2}$  are calculated for steady state operation and constant load output voltage and current. Furthermore, it is assumed that  $V_{\phi 1} = -V_{\phi 2} = V_A \cos\theta$  and that the capacitors are high enough to keep the voltage constant.

From Fig. 2.1, the voltage across  $D_1$  is

$$V_{D1} = V_{DD} - V_{C1} - V_A \cos\theta$$

(2.5)

The substitution of  $V_{D1}$  of (2.5) into (2.3) gives

Figure 2.2: Dickson charge pump schematic and voltage across the diodes and capacitors.

$$I_L = \frac{1}{2\pi} \int_{-\pi}^{\pi} I_S \left[ e^{\frac{V_{DD} - V_{C1} - V_A \cos \theta}{n\phi t}} \right] d\theta \tag{2.6}$$

Solving (2.6) for the voltage stored in  $C_1$  and substituting the resulting value into the voltage drop across  $D_1$  gives, respectively,

$$V_{C1} = V_{DD} + n\phi_t \ln\left[\frac{I_0(v_a)}{1 + \frac{I_L}{I_{sat}}}\right]$$

(2.7)

$$V_{D1} = -V_A \cos \theta - n\phi_t \ln \left[ \frac{I_0 \left( v_a \right)}{1 + \frac{I_L}{I_{sat}}} \right]$$

(2.8)

where  $v_a = V_A/n\phi_t$  is the normalized magnitude of the oscillator output voltage and  $I_0(z) = \frac{1}{\pi} \int_0^{\pi} e^{z\cos\theta} d\theta$  is the modified Bessel function of the first kind of order zero [23].

The voltage across  $D_2$  is

$$V_{D2} = V_{C1} - V_{C2} + 2V_A \cos\theta \tag{2.9}$$

Replacing  $V_D$  of (2.9) into (2.3) gives

$$I_L = \frac{1}{2\pi} \int_{-\pi}^{\pi} I_S \left[ e^{\frac{V_{C1} - V_{C2} - 2V_A \cos \theta}{n\phi t}} \right] d\theta$$

(2.10)

Solving (2.10) for the voltage of  $C_2$  and substituting the resulting value of  $V_{C2}$  into the voltage drop across  $D_2$  gives, respectively,

$$V_{C2} = V_{DD} + n\phi_t \ln\left[\frac{I_0(v_a)}{1 + \frac{I_L}{I_{sat}}}\right] + n\phi_t \ln\left[\frac{I_0(2v_a)}{1 + \frac{I_L}{I_{sat}}}\right]$$

(2.11)

$$V_{D2} = 2V_A \cos \theta - n\phi_t \ln \left[\frac{I_0 \left(2v_a\right)}{1 + \frac{I_L}{I_{sat}}}\right]$$

(2.12)

Replacing the average values  $\overline{V_{D1}}$  and  $\overline{V_{D2}}$  of (2.8) and (2.12), respectively, into (2.4) gives the DCP output voltage for N stages.

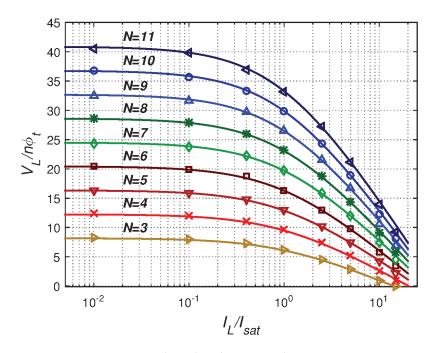

$$V_{L} = V_{DD} + 2n\phi_{t} \ln\left[\frac{I_{0}(v_{a})}{1 + \frac{I_{L}}{I_{sat}}}\right] + (N - 2)n\phi_{t} \ln\left[\frac{I_{0}(2v_{a})}{1 + \frac{I_{L}}{I_{sat}}}\right]$$

(2.13)

Assuming  $v_a > 3$ , the Bessel function  $I_0(z)$  can be approximated by  $e^z/\sqrt{2\pi z}$  [23], with an error of less than 5%. For such a case, Eq. (2.13) reduces to

$$V_L = V_{DD} + 2(N-1)V_A - Nn\phi_t \ln\left[\sqrt{2\pi 2v_a}\left(1 + \frac{I_L}{I_{sat}}\right)\right] + n\phi_t \ln(2)$$

(2.14)

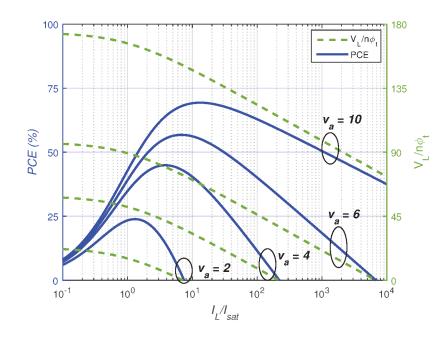

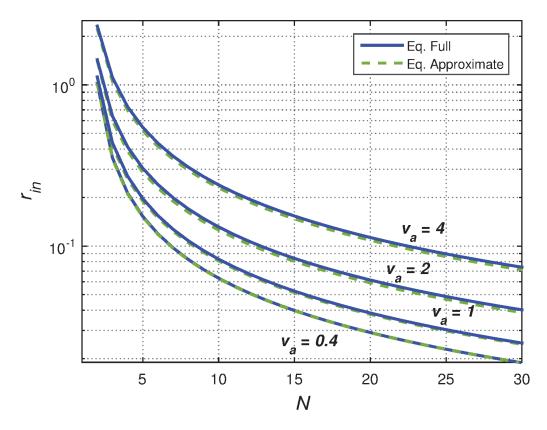

The simplified equation (2.14) presents an error less than 2% when compared to the full equation (2.13), which is a very acceptable error, since the last equation does not make use of the Bessel function.