#### Roberto de Matos

# CONVERSORES REVERSOS RNS-BINÁRIO EFICIENTES PARA APLICAÇÕES COM AMPLA FAIXA DINÂMICA

Tese submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para obtenção do grau de Doutor em Engenharia Elétrica.

Orientador:Dr. Eduardo Augusto Bezerra Co-orientador:Dr. Hector Pettenghi Roldan

Florianópolis 2018

## Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

de Matos, Roberto CONVERSORES REVERSOS RNS-BINÁRIO EFICIENTES PARA APLICAÇÕES COM AMPLA FAIXA DINÂMICA / Roberto de Matos ; orientador, Eduardo Augusto Bezerra, coorientador, Héctor Pettenghi Roldán, 2018. 113 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós Graduação em Engenharia Elétrica, Florianópolis, 2018.

Inclui referências.

1. Engenharia Elétrica. 2. Sistema Numérico por Resíduos. 3. RNS. 4. Multiplicadores. 5. Teorema Chinês do Resto. I. Bezerra, Eduardo Augusto. II. Roldán, Héctor Pettenghi. III. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. IV. Título.

#### Roberto de Matos

# CONVERSORES REVERSOS RNS-BINÁRIO EFICIENTES PARA APLICAÇÕES COM AMPLA FAIXA DINÂMICA

Esta Tese de Doutorado foi julgada adequada para obtenção do Título de "Doutor" em Engenharia Elétrica, Área de Concentração em Circuitos e Sistemas Integrados, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina.

|           | Florianópolis, 22 de Março de 2018                          |

|-----------|-------------------------------------------------------------|

|           | Prof. Dr. Marcelo Lobo Heldwein                             |

|           | Coordenador do Curso                                        |

|           | Prof. Dr. Eduardo Augusto Bezerra<br>Orientador             |

|           | Prof. Dr. Hector Pettenghi Roldan<br>Co-orientador          |

| Banca Exa | aminadora:                                                  |

|           | Prof. Dr. Fabian Luis Vargas                                |

| Po        | ntifícia Universidade Católica do Rio Grande do Sul – PUCRS |

|           | Prof. Dr. Leonel Sousa                                      |

|           | Universidade de Lisboa – IST                                |

|           | Prof. Dr. Cesar Albenes Zeferino                            |

|           | Universidade do Vale do Itajaí – Univali                    |

### Agradecimentos

Muitas pessoas merecem agradecimentos por terem contribuído na realização desse trabalho. Em primeiro lugar meu orientador, professor Eduardo Augusto Bezerra, que desde o primeiro contato abriu a oportunidade para entrada no programa de pós-graduação e me apoiou de forma incondicional em todos os momentos do doutorado, além de ser uma inspiração como pessoa e profissional. Em seguida, meu co-orientador, professor Hector Pettenghi Roldan, que me apresentou uma nova área com dedicação e paciência, contribuiu de uma forma muito próxima no direcionamento do tema, implementações e análises. Ao colega, Rogério Paludo, que muito contribuiu com comentários, discussões, implementações e esclarecimentos sobre o tema. Finalmente, a todos os meus colegas do IFSC que apoiaram direta ou indiretamente o trabalho e ao IFSC como instituição que possibilitou o meu afastamento para conclusão do doutorado.

### Resumo

Aritmética de resíduos, baseada em Sistema Numérico por Resíduos (RNS - Residue Number Systems), tem sido utilizada em sistemas digitais durante vários anos. RNS é uma abordagem aritmética livre de carry que oferece o potencial para alta velocidade e computação paralela. Operações aritméticas, como adição, subtração e multiplicação, podem ser realizadas de forma mais eficiente do que nos sistemas binários convencionais, de forma independente e simultânea, em vários canais de resíduos. A adoção de RNS tem proporcionado melhorias significativas na eficiência de diferentes tipos de aplicações de processamento digital de sinal. Uma unidade aritmética completa baseada em RNS possui quatro características principais relacionadas com a sua funcionalidade: a) conjunto de módulos, b) conversão direta, c) unidades aritméticas modulares e d) conversão reversa. Cada unidade completa é baseada em um conjunto de módulos, os quais são inteiros primos entre si. A faixa dinâmica é definida pelo produto de todos os módulos e define o intervalo de entrada. O conversor direto, também chamado de conversor binário para RNS, converte um número binário na representação RNS, baseada no conjunto de módulos. As unidades aritméticas modulares são os blocos instanciados paralelamente que de fato executam as operações livre de carry de soma, subtração e multiplicação. Por fim, o conversor reverso, também chamado de conversor RNS para binário, transforma os vários resíduos calculados pelos canais paralelos no resultado binário equivalente. Um grande número de canais pode melhorar o cálculo aritmético, entretanto pode haver grandes perdas de desempenho causado pelo custo da execução da conversão reversa. Com conversores reversos eficientes, capazes de suportar grandes conjuntos de módulos, é possível compensar este custo adicional, especialmente quando várias operações aritméticas precisam de ser realizadas. Este trabalho propõe conversores reversos eficientes para aplicações com uma faixa dinâmica ampla que foram implementados com um método de compactação lógica que supera o melhor conversor reverso do estado da arte, com um faixa dinâmica equivalente, apresentando uma aceleração de 2,77 vezes, e uma redução média de 82,16% e 88,32% em área e potência, respectivamente.

**Palavras-chave:** Sistema Numérico por Resíduos, RNS, operadores aritméticos, multiplicadores, somadores, teorema chinês do resto, CRT.

### **Abstract**

Residue Number System (RNS) has been used in digital processing realm for many years. RNS is a carry-free arithmetic system with modular characteristics offering the potential for high-speed and parallel computation. Arithmetic operations, such as addition, subtraction, and multiplication, can be carried out more efficiently than in the conventional binary systems. Because they are performed independently and concurrently in several residue channels. Each RNS unit is based on a moduli set, which are co-prime integers. The dynamic range is defined by the product of the moduli and defines the unit input range. The choice of the moduli set is of key importance in order to obtain an efficient RNS unit. A complete arithmetic unit based on RNS has three stages: a) forward conversion, b) modular arithmetic unit, and c) reverse conversion. Forward converter transforms a binary number into its specific RNS representation. The modular arithmetic unit is the processing blocks instantiated in parallel to actually perform the sum, subtraction, and multiplication. Finally, the reverse converter transforms an RNS represented number into its equivalent binary number. Several channels can improve the arithmetic computation at the cost of reverse conversion performance. With efficient reverse converters, capable of supporting large moduli sets, it is possible to compensate for this extra cost, especially when several arithmetic operations have to be performed. This work proposes an efficient reverse converter for applications with a large dynamic range. It has been implemented with a logical compression method and experimental results suggest that area reductions up to 82.16% and speed up of 2.77 can be obtained with our proposal in comparison with the best state-of-the-art reverse converter with an equivalent dynamic range. The proposed converter allows fewer bits per channel in comparison with the most efficient solutions with smaller dynamic ranges.

**Keywords:** Residue Number System, RNS, arithmetic operators, multipliers, adders, Chinese Remainder Theorem, CRT.

# Lista de Figuras

| 2.1  | Diagrama de blocos de uma unidade aritmética completa baseada em RNS                                          | 31 |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Esquema de conversão direta para os módulos $2^n, 2^n - 1, 2^n + 1$ de um valor $X$                           | 36 |

| 2.3  | Arquitetura genérica de conversor binário para RNS                                                            | 37 |

| 2.4  | Árvore <i>CSA</i> para soma modular $\{2^n - 1\}$ de 10 operandos                                             | 39 |

| 2.5  | Compressor $(10:2)$ , a partir de compressores $(4:2)$ , para $10$ operandos.                                 | 40 |

| 2.6  | Estrutura Paralela do Conversor Final (FC)                                                                    | 40 |

| 2.7  | Multiplicação modular $\{2^n-1\}$ com $n=8$ $vs.$ multiplicação binária                                       | 41 |

| 2.8  | Multiplicação modular $\{2^n+1\}$ com $n=8$ $vs.$ multiplicação binária                                       | 42 |

| 2.9  | Multiplicação modular $\{2^n - 3\}$ com $n = 8$                                                               | 43 |

| 2.10 | Multiplicação modular $\{2^n - 3\}$ com $n = 8$                                                               | 44 |

| 2.11 | Diagrama de blocos genéricos dos conversores reversos baseados no CRT e Novo CRT-I                            | 48 |

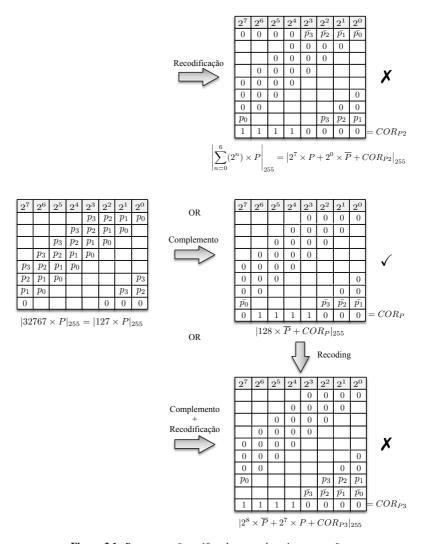

| 3.1  | Representação gráfica da etapa de pré-computação                                                              | 53 |

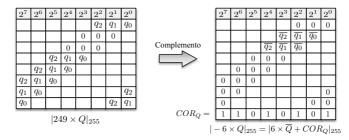

| 3.2  | Representação gráfica do resultado da pré-computação para $ 249 \times Q _{255}$ complementado                | 54 |

| 3.3  | Representação gráfica do resultado da pré-computação para $ 193 \times R _{255}$ complementado e recodificado | 55 |

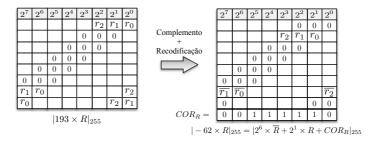

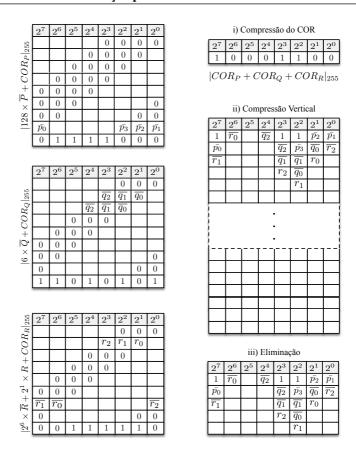

| 3.4  | As três técnicas da etapa de compactação vertical para o exemplo proposto                                     | 56 |

| 3.5  | Etapa de Deslocamento Horizontal                                                                              | 57 |

| 3.6  | Produtos Parciais da operação $ 222 \times x _{253}$ antes da otimização                                      | 58 |

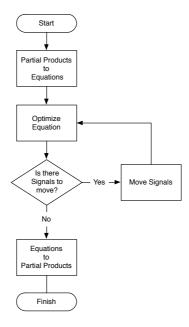

| 3.7  | Algoritmo da etapa de otimização lógica                                                                       | 58 |

| 3.8  | Produtos Parciais da operação $ 222 \times x _{253}$ depois da otimização                                     | 59 |

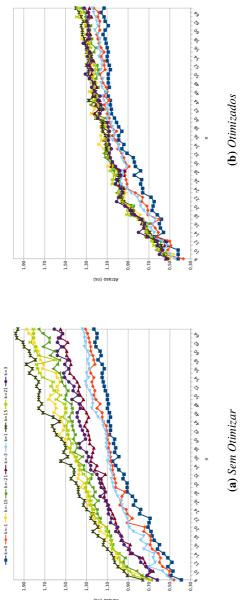

| 3.9  | Resultados experimentais para uma unidade modular MAC por constante, variando o módulo $\{2^n \pm k\}$ e a largura de <i>bits</i> $(n)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

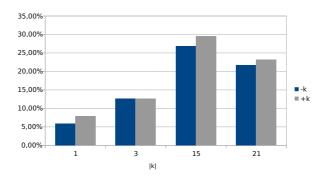

| 3.10 | Percentual de otimização para $\pm k$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62 |

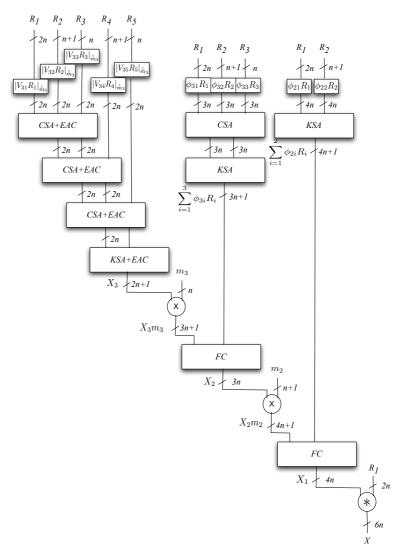

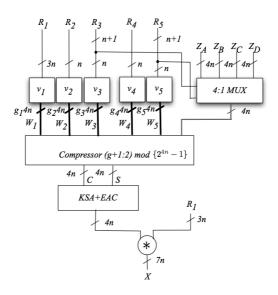

| 4.1  | Diagrama de bloco do conversor reverso $\{2^{2n}, 2^n \pm \mathbf{k}_1, 2^n \pm 1\}$ para abordagem <i>Multi-level</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72 |

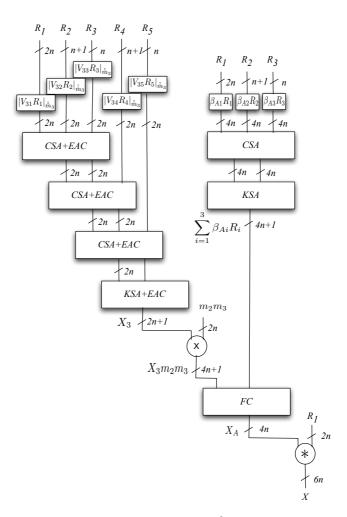

| 4.2  | Diagrama de bloco do conversor reverso $\{2^{2n}, 2^n \pm \mathbf{k}_1, 2^n \pm 1\}$ para abordagem <i>Two-level</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76 |

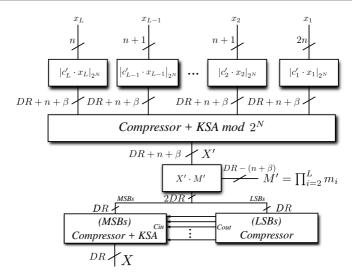

| 4.3  | Arquitetura de hardware proposta para o algoritmo CRTf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84 |

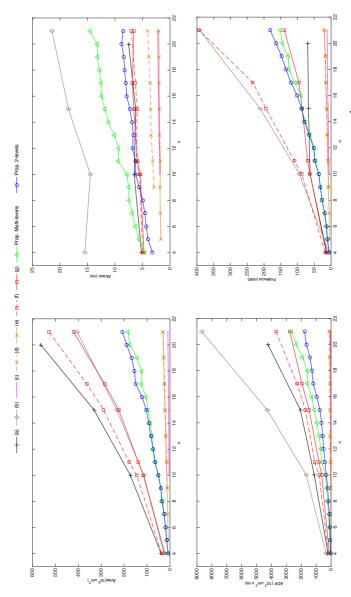

| 4.4  | Resultados Experimentais dos conversores reversos para o conjunto de módulo com $DR = 6n$ bits: $\{2^{2n}, 2^n \pm 3, 2^n \pm 1\}$ baseados em (a) CRT [1] e (b) MRC [3]; (c) $\{2^{2n}, 2^n \pm 1, 2^{2n} + 1\}$ [17]; (d) $\{2^n, 2^n \pm 1, 2^n \pm 2^{\frac{n+1}{2}} + 1, 2^{n+1} + 1\}$ e $\{2^n, 2^n \pm 1, 2^n \pm 2^{\frac{n+1}{2}} + 1, 2^{n-1} + 1\}$ [21] com $\beta = 0$ ; (e) $\{2^{2n}, 2^n \pm 1, 2^n \pm 2^{\frac{n+1}{2}} + 1\}$ [21] com $\beta = n$ ; (f) $\{2^n, 2^n \pm 3, 2^n \pm 1\}$ [9] e (g) $\{2^{2n}, 2^n \pm 3, 2^n \pm 1\}$ [9], ambos baseados no Novo CRT-I; $\{2^{2n}, 2^n \pm 3, 2^n \pm 1\}$ para as duas propostas <i>Two-level</i> e <i>Multi-Level</i> | 86 |

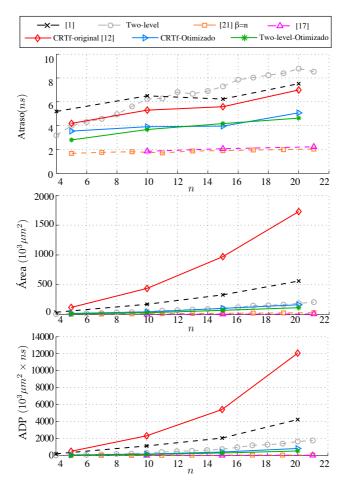

| 4.5  | Resultados Experimentais obtidos para $DR = 6n$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90 |

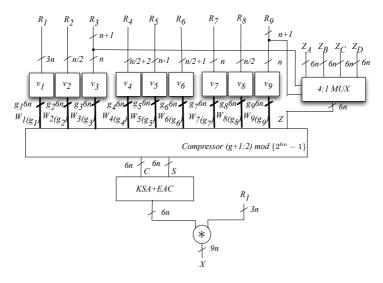

| 5.1  | Conversor reverso com $DR = 7n$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95 |

| 5.2  | Conjunto de módulos derivado de $\hat{m}_1 = 2^{6n} - 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96 |

| 5.3  | Diagrama de bloco do conversor reverso proposto com $DR \simeq 9n$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99 |

## Lista de Tabelas

| 2.1 | Principais conjuntos de módulos do estado da arte organizados com relação ao número de módulos vs. <i>DR</i>                    |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 3.1 | MACs Binário vs. RNS para $DR = 110$ bits 63                                                                                    |

| 4.1 | Comparação de operações entre as abordagens dos algoritmos de conversão para $\{2^{2n}, 2^n \pm 3, 2^n \pm 1\}, n = 4 \dots 80$ |

| 4.2 | Desempenho dos conversores reversos para $DR = 10n \ bits$ 88                                                                   |

| 4.3 | Resultados Experimentais para $DR = 8n$                                                                                         |

| 4.4 | Resultados Experimentais para $DR = 10n.$                                                                                       |

| 5.1 | Exemplo numérico para $n = 6$ , com a extensão proposta, $\beta = 2n$ , ( $DR$ de 54-bits)                                      |

| 5.2 | Atraso "unit-gate" para soma nos canais modulares do conjunto proposto                                                          |

| 5.3 | Atraso e Área do conversor reverso para os vários conjuntos de módulos                                                          |

| 5.4 | Resultados de Área, Atraso e Potência obtidos a partir da síntese 104                                                           |

## Lista de Siglas

| RNS  | Residue Number Systems ix                           |

|------|-----------------------------------------------------|

| DSP  | Digital Signal Processing                           |

| CRT  | Chinese Remainder Theorem                           |

| MRC  | Mixed-Radix Conversion                              |

| DR   | Dynamic Range                                       |

| MAC  | Multiplicador–ACumulador                            |

| CRTf | Chinese Remainder Theorem with Fractional Values 27 |

| MDC  | Máximo Divisor Comum                                |

| DR   | Dynamic Range                                       |

| CSA  | Carry-Save Adders                                   |

| FC   | Final Converter                                     |

| CPA  | Carry-Propagate Adder                               |

| EAC  | End-Around Carry                                    |

| KSA  | Kogge-Stone Adder                                   |

| MSB  | Most Significant Bit                                |

| IEAC | Inverte End-Around Carry                            |

| ROL  | Rotation Left                                       |

| ADP  | Area-Delay-Product                                  |

| PPA  | Paralel-Prefix Adder                                |

| FA   | Full-Adder                                          |

# Lista de Equações

| 2.1  | Representação modular de um número $X \ldots \ldots \ldots \ldots$                          | 32 |

|------|---------------------------------------------------------------------------------------------|----|

| 2.2  | Equação de conversão de binário para RNS para o módulo $2^n$                                | 35 |

| 2.3  | Equação de conversão de binário para RNS para o módulo $2^n-1$                              | 35 |

| 2.4  | Equação de conversão de binário para RNS para o módulo $2^n+1$                              | 35 |

| 2.5  | Equação de conversão de binário para RNS para o módulo genérico                             | 35 |

| 2.3  | Equação de conversão de binário para RNS para o módulo $2^n-k$                              | 36 |

| 2.4  | Equação de conversão de binário para RNS para o módulo $2^n+k$                              | 36 |

| 2.9  | Equação de conversão reversa CRT genérica                                                   | 45 |

| 2.10 | Equação de conversão reversa MRC                                                            | 45 |

| 2.11 | Equação dos coeficientes $v$ da equação MRC                                                 | 45 |

| 2.12 | Equação de conversão reversa Novo CRT-I                                                     | 45 |

| 2.13 | Equações dos coeficientes $V_i$ da equação Novo CRT-I                                       | 46 |

| 4.1  | Redução do cálculo de $M$ para $\hat{\hat{m}}_1 = \hat{m}_1$ na equação do CRT (Eq. (2.9)). | 67 |

| 4.2  | Reescrita da Eq. (4.1) $$                                                                   | 68 |

| 4.3  | Segunda redução para o cálculo do módulo $\hat{\hat{m}}_2$                                  | 69 |

| 4.4  | Terceira redução para o cálculo do módulo $\hat{m}_3$                                       | 69 |

| 4.5  | Equações finais para o cálculo de $X$ , $X_1$ , $X_2$ e $X_3$                               | 70 |

| 4.6  | Restrições para $\phi_{3i}R_i$ e $\phi_{2i}R_i$ no intervalo $0 \le \beta \le n$            | 70 |

| 4.7  | Valores máximos de resíduos $R_i = m_i - 1, 1 \le i \le 3 \dots \dots \dots$                | 70 |

| 4.8  | Adição não modular dos termos $\phi_{3i}R_i$ e $\phi_{2i}R_i$                               | 70 |

| 4.9  | Reescrita da Eq. (4.5)                                                                      | 71 |

| 4.10 | Extensão da Eq. (4.9) para obter o valor binário de $X$                                     | 73 |

| 4.11 | Derivação dos parâmetros da Eq. (4.10) para a redução $(j+1)$ , $1 \le j \le t-1$           | 73 |

| 4.12 | Redução da Eq. (4.9) aplicando o <i>Lemma 2</i>                                                                | 74 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 4.13 | Termos $\beta_{Ai}R_i$ para o intervalo $0 \le \beta \le n$                                                    | 75 |

| 4.14 | Condição a ser satisfeita para garantir uma adição não modular, como apresentado na Eq. (4.12, com $\beta=n$ ) | 75 |

| 4.15 | Exemplo usando CRT                                                                                             | 77 |

| 4.16 | Exemplo usando MRC                                                                                             | 78 |

| 4.17 | Exemplo usando o novo CRT-I                                                                                    | 78 |

| 4.18 | Exemplo usando o método apresentado na Subseção 4.1.1                                                          | 78 |

| 4.19 | Exemplo usando o método Two-level                                                                              | 79 |

| 4.20 | Divisão por $M$ de ambos os lados da Eq. (2.9) do CRT                                                          | 82 |

| 4.21 | Conversão reversa do CRT-f proposta por [12]                                                                   | 82 |

| 4.22 | Constantes $c_i'$ apresentadas na Eq. (4.21)                                                                   | 82 |

| 4.23 | Quantidade de bits da divisão final                                                                            | 82 |

| 4.24 | Valor de M para o módulo genérico                                                                              | 82 |

| 4.25 | Valor de $X$ obtido a partir da substituição da Eq. (4.24) na Eq. (4.21) .                                     | 83 |

| 4.26 | Forma binária da Eq. (4.25) para qualquer valor de $f$ e $\beta$                                               | 83 |

| 5.1  | Equação de conversão reversa CRT para conjuntos de 5 módulos                                                   | 94 |

| 5.2  | Equação de conversão reversa CRT proposta por [21]                                                             | 94 |

| 5.3  | Equação de conversão reversa CRT usando operações ROL [21]                                                     | 94 |

| 5.4  | Conjunto de módulos aplicado à Eq.(5.2)                                                                        | 96 |

| 5.5  | Prova da Multiplicativa inversa $\left \hat{m}_1^{-1}\right _{m_1}$                                            | 97 |

| 5.6  | Prova da Multiplicativa inversa $\left \hat{m}_{2}^{-1}\right _{m_{2}}$                                        | 97 |

| 5.7  | Exemplo de conversão reversa                                                                                   | 97 |

|      |                                                                                                                |    |

## Sumário

| 1 | 1 Introdução |         |                                                                   |    |  |

|---|--------------|---------|-------------------------------------------------------------------|----|--|

|   | 1.1          | Objetiv | vos                                                               | 26 |  |

|   | 1.2          | Contri  | buições                                                           | 27 |  |

|   | 1.3          | Organi  | ização da Tese                                                    | 28 |  |

| 2 | Fun          | dament  | ação e Estado da Arte                                             | 31 |  |

|   | 2.1          | Introdu | ução do Sistema Numérico de Resíduos                              | 32 |  |

|   | 2.2          | Conju   | nto de Módulos                                                    | 33 |  |

|   | 2.3          | Conve   | rsores Diretos                                                    | 35 |  |

|   | 2.4          | Unidad  | des Aritméticas Modulares                                         | 38 |  |

|   |              | 2.4.1   | Somadores                                                         | 38 |  |

|   |              | 2.4.2   | Multiplicadores                                                   | 41 |  |

|   |              |         | 2.4.2.1 Multiplicação $\{2^n \pm 1\}$                             | 41 |  |

|   |              |         | 2.4.2.2 Multiplicação $\{2^n \pm k\}$                             | 42 |  |

|   | 2.5          | Conve   | rsores Reversos                                                   | 45 |  |

|   |              | 2.5.1   | Estado da Arte de Conversores Reversos                            | 47 |  |

|   | 2.6          | Conclu  | ısão                                                              | 49 |  |

| 3 | Otir         | nização | de Multiplicadores Modulares por Constante                        | 51 |  |

|   | 3.1          | Métod   | o de Otimização para Conversores Reversos                         | 52 |  |

|   |              | 3.1.1   | Pré-computação das Constantes                                     | 52 |  |

|   |              | 3.1.2   | Compactação Vertical                                              | 55 |  |

|   |              | 3.1.3   | Deslocamento Horizontal                                           | 56 |  |

|   | 3.2          | Otimiz  | zação lógica para multiplicação modular $\{2^n \pm k\}$ por cons- |    |  |

|   |              | tante   |                                                                   | 57 |  |

| 3.3 Resultados Experimentais |      |                                                                                      |            |                                                                                                | 59 |  |  |

|------------------------------|------|--------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------|----|--|--|

|                              |      | 3.3.1                                                                                | Compara    | ção entre Implementações Binária e RNS                                                         | 62 |  |  |

|                              | 3.4  | Concl                                                                                | usão       |                                                                                                | 63 |  |  |

| 4                            | Proj | postas d                                                                             | los Conver | sores Reversos Genéricos                                                                       | 65 |  |  |

|                              | 4.1  |                                                                                      |            | jetar Conversores Reversos de Dois Níveis para âmica                                           | 65 |  |  |

|                              |      | 4.1.1                                                                                |            | s Híbridas <i>Multi-Level</i> para o Conjunto de Três $\{2^n, 2^n \pm 1\}$                     | 65 |  |  |

|                              |      |                                                                                      | 4.1.1.1    | Conjunto de Módulos $\{2^{n+\beta}, 2^n \pm k_1, 2^n \pm 1\}$                                  | 66 |  |  |

|                              |      |                                                                                      | 4.1.1.2    | Conjunto de Módulos $\{2^{n+\beta}, 2^n \pm k_f, \dots, 2^n \pm k_2, 2^n \pm k_1, 2^n \pm 1\}$ | 71 |  |  |

|                              |      | 4.1.2                                                                                | Extensõe   | s híbridas de Dois Níveis do Conjunto $\{2^n, 2^n \pm 1\}$                                     | 74 |  |  |

|                              |      | 4.1.3                                                                                | Estimativ  | a de Desempenho: Um Estudo de Caso                                                             | 77 |  |  |

|                              | 4.2  | Conversão Reversa CRTf Usando Conjuntos de Módulos Genéricos Balanceados             |            |                                                                                                |    |  |  |

|                              | 4.3  |                                                                                      |            | imentais                                                                                       | 84 |  |  |

|                              |      | 4.3.1                                                                                | Resultado  | os e Discussão das Propostas <i>Two-level</i> e <i>Multi-</i>                                  | 85 |  |  |

|                              |      | 4.3.2                                                                                |            | os do CRTf Proposto e Análise do Impacto dos de Otimização                                     | 88 |  |  |

|                              | 4.4  | Concl                                                                                | usões      |                                                                                                | 91 |  |  |

| 5                            | Prop | posta de                                                                             | o Converso | or Reverso Dedicado com Faixa Dinâmica de 9 <i>n</i>                                           | 93 |  |  |

|                              | 5.1  | Conversor Reverso RNS para conjunto de módulos com faixa dinâmica de 9 <i>n bits</i> |            |                                                                                                |    |  |  |

|                              | 5.2  | Proposta do conjunto de módulos com $DR \simeq 9n$                                   |            |                                                                                                |    |  |  |

|                              | 5.3  | Análise Teórica do Conjunto de Módulos Proposto 98                                   |            |                                                                                                |    |  |  |

|                              | 5.4  | Análise Teórica dos Conversores Reversos                                             |            |                                                                                                |    |  |  |

|   | 5.5 | Discussão e Resultados Experimentais |

|---|-----|--------------------------------------|

|   | 5.6 | Conclusões                           |

| 6 | Con | clusões 105                          |

|   | 6.1 | Lista de Publicações                 |

|   | 6.2 | Trabalhos Futuros                    |

#### CAPÍTULO 1

### Introdução

Com a disseminação dos sistemas computacionais móveis de comunicação, o Processamento Digital de Sinal (DSP - Digital Signal Processing) tem migrado de poderosos servidores para unidades especialistas dentro de processadores embarcados. A cada dia essas aplicações exigem maior velocidade na manipulação aritmética de operandos com grande comprimento de palavra. Uma das maneiras de melhorar o desempenho desses sistemas é usar uma representação numérica alternativa em vez de usar a representação convencional binária de complemento de dois.

O Sistema Numérico por Resíduos (RNS - Residue Number Systems) tem sido utilizado para para melhorar o desempenho de sistemas digitais durante muitos anos [1]. RNS é um sistema numérico não-posicional, no qual um grande operando é decomposto em um conjunto de operandos menores (resíduos), cada um processado em um canal paralelo independente. Assim RNS permite uma abordagem aritmética livre de carry com características modulares que oferece o potencial para alta velocidade e computação paralela. Operações aritméticas, como adição, subtração e multiplicação, podem ser realizadas de forma mais eficiente do que nos sistemas binários convencionais [1], de forma independente e simultânea, em vários canais de resíduo. A adoção de RNS tem proporcionado melhorias significativas de eficiência para os diferentes tipos de aplicação de processamento digital de sinal [1], além de permitir escalar facilmente para aplicações com requisitos de grande faixa dinâmica, como filtragens adaptativas e criptografia [2].

Uma das operações mais complexas e custosas de uma unidade aritmética baseada em RNS é a conversão reversa (RNS para binário). Os algoritmos mais utilizados para a conversão reversa são o Teorema Chinês do Resto (CRT - Chinese Remainder Theorem) [1], a Conversão de Raiz Mista (MRC - Mixed-Radix Conversion) [3] e o novo CRT-I [4]. A complexidade desses algoritmos depende principalmente do tamanho do módulo e do número de canais. Por isso, a escolha do conjunto de módulos é essencial para que se obtenha implementações RNS eficientes.

Os conjuntos de módulos com uma grande quantidade de canais podem melhorar a computação aritmética ao custo do desempenho da conversão reversa.

1.1. Objetivos 26

Com conversores reversos eficientes, capazes de suportar conjuntos de módulos grandes, é possível compensar esse custo extra, especialmente quando várias operações aritméticas devem ser realizadas em série. Nesses casos, o uso de múltiplos canais modulares aritméticos pode levar à melhoria do desempenho. Além disso, o conjunto de módulos também define o intervalo para representação exclusiva de inteiros, chamado de faixa dinâmica (*DR - Dynamic Range*).

Dessa forma, a maioria das pesquisas sobre RNS está focada em propor conjunto de módulos e projetar conversores reversos eficientes [5], uma vez que essa etapa possui um custo alto no hardware. Assim, um projeto sem critério pode neutralizar o ganho da paralelização nas unidades aritméticas modulares. Em outras palavras, para aumentar a aplicabilidade das unidades baseadas em RNS é necessário melhorar o desempenho global, no qual o conversor reverso tem um grande peso.

O conjunto de módulos mais tradicional é o conjunto de 3 módulos proposto por [1]  $\{2^n, 2^n + 1, 2^n - 1\}$ , com uma faixa dinâmica de aproximadamente 3n-bit. No entanto, nem o nível de paralelismo nem a DR alcançado por esse conjunto são suficientes [6, 7]. Nesses casos, as extensões horizontais podem ser utilizadas para adicionar mais módulos ao conjunto de módulos, enquanto extensões verticais estendem um módulo, normalmente a potência de dois, aumentando a DR, mas sem aumentar o número de canais. Essas extensões tem um impacto na implementação e na eficiência da unidade completa em RNS. O importante é selecionar um conjunto de módulos equilibrado entre a faixa dinâmica requerida pela aplicação e o número de canais para paralelização das operações aritméticas.

### 1.1 Objetivos

O objetivo central desta tese é propor conjuntos de módulos e conversores reversos mais eficientes que os do estado da arte, levando em consideração aplicações de ampla faixa dinâmica e várias operações aritméticas por canal. Para atingir o objetivo principal, os seguintes objetivos específicos foram definidos:

Implementar unidades aritméticas modulares, mais especificamente MAC (Multiplicador–ACumulador), para avaliação do atraso no caminho crítico de canais com diferentes larguras de *bits* e módulos.

- Propor conjunto de módulos de forma a diminuir o número de bits por canal, aumentando o nível de paralelismo e diminuindo o atraso no caminho crítico das unidades aritméticas dos canais modulares. Além de alcançar a maior faixa dinâmica possível para beneficiar aplicações com essas características.

- Desenvolver conversores reversos baseados nos conjuntos de módulos propostos.

- Otimizar unidades recorrentes dentro dos conversores para alcançar melhor eficiência.

- Avaliar e comparar os conjuntos e os conversores propostos com o estado da arte.

#### 1.2 Contribuições

O escopo da tese limita-se à conversão RNS para binário, entretanto, além das contribuições na área dos conversores reversos, outros resultados foram alcançadas paralelamente ao objetivo principal. As contribuições desta tese são resumidamente as seguintes:

- Conversor reverso com maior DR para conjunto de módulos específico do

estado da arte (DR ~ 9n) [8]. Além disso, este conjunto de módulos específicos oferece operações modulares mais simples na conversão reversa,

em comparação com as abordagens genéricas [9] e [10]. O conversor proposto permite menos bits por canal em comparação com as soluções mais

eficientes com intervalos dinâmicos menores.

- Procedimento para otimizar as multiplicações modulares por constantes baseadas no módulo {2<sup>n</sup>}, {2<sup>n</sup> ± 1} e {2<sup>n</sup> ± k}. Tais operações demonstraram ser cruciais para o projeto conversores reversos eficientes.

- Proposta de arquitetura [11] para o conjunto modular genérico usando o Teorema Chinês do Resto Aproximado (CRTf - Chinese Remainder Theorem with Fractional Values) [12].

• Método composto de duas abordagens para projetar conversores reversos para conjunto de módulos genérico e escalável. A primeira abordagem é baseada em estágios iterativos usados para reduzir a complexidade da etapa final do conversor. A segunda abordagem minimiza o número de estágios iterativos necessários na conversão para apenas dois níveis, com custo mínimo de área em comparação com a solução de vários níveis e podendo escalar eficientemente com maiores conjunto de módulos e n [10].

### 1.3 Organização da Tese

Esta tese contém seis capítulos, incluindo esta introdução. Exceto pelo próximo capítulo, que fundamenta o assunto e sintetiza o estado da arte dos conversores reversos, e o último capítulo, que conclui a tese, os outros três capítulos tem uma relação direta com os artigos publicados/submetidos às revistas e conferências internacionais, o que facilita a compreensão de cada capítulo por si só. Embora esta abordagem de apresentação não convencional tenha sido adotada, os capítulos foram estruturados de forma consistente, a fim de garantir uma fácil leitura e compreensão de todas as idéias e soluções propostas como trabalho unificado. Isso traz para a tese duas características importantes: i) Clareza na apresentação de contribuições de pesquisa; ii) Uma compreensão mais fácil da análise entre as propostas de conjuntos de módulos/implementações/otimizações e os resultados experimentais, uma vez que são reunidos em cada capítulo. Escalarecido isso, abaixo é apresentada a descrição em detalhes do restante da tese:

- Capítulo 2 Este capítulo apresenta uma fundamentação básica sobre RNS; o processo de conversão binário para RNS (conversão direta); as unidades aritméticas modulares de multiplicação e soma; os algoritmos de conversão RNS para binário (conversão reversa). Em seguida apresenta e analisa os conjuntos de módulos usados nos conversores reversos mais eficientes do estado da arte.

- Capítulo 3 Este capítulo apresenta duas técnicas de otimização de unidades de multiplicação modular por constante. Tais operações são cruciais para o projeto de conversores reversos e unidades aritméticas eficientes. Ambos os métodos foram aplicadas em unidades MACs para diferentes módulos e larguras de operandos, com o objetivo de demonstrar seus ga-

nhos e limitações. Nos próximos capítulos, essas técnicas são aplicadas nas propostas e os resultados experimentais demostram que a otimização dos multiplicadores modulares tem um impacto na velocidade e na área dos conversores reversos com as maiores faixas dinâmicas do estado da arte.

- Capítulo 4 Neste capítulo são propostas extensões verticais e horizontais do conjunto tradicional de 3 módulos  $\{2^n, 2^n 1, 2^n + 1\}$ , com a faixa dinâmica equivalente a 3n-bit, para escalar a faixa dinâmica e melhorar o paralelismo de acordo com os requisitos. São apresentados dois métodos diferentes para projetar conversores reversos genéricos para conjuntos de módulos estendidos para os intervalos dinâmicos desejados. Os resultados experimentais demonstram que as abordagens propostas alcançam reduções significativas da área. Além disso, os resultados obtidos também validam a escalabilidade melhorada das abordagens propostas, permitindo melhores resultados com o aumento de n e da DR. Ainda é proposta uma arquitetura de hardware melhorada para o algoritmo de conversão reversa (CRTf), usando conjuntos de módulos genéricos balanceados.

- Capítulo 5 Este capítulo sintetiza uma das maiores contribuições da tese: Um método para projetar conversores reversos RNS eficientes, incluindo as técnicas citadas acima, usando um novo conjunto de módulos com a faixa dinâmica de 9n bits. Esse conjunto apresenta a maior faixa dinâmica do estado da arte, que até então restringia-se a implementações de conversores reversos eficientes até DR ~ 8n. A abordagem proposta resulta em maior paralelismo com um número menor de bits por canal.

- Capítulo 6 Finalmente, este capítulo apresenta as conclusões e considerações sobre as principais contribuições deste trabalho, além de sugerir novos desdobramentos na forma de trabalhos futuros.

## Fundamentação e Estado da Arte

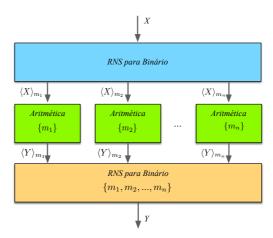

Uma sistema típico baseado em RNS, apresentado na Figura 2.1, possui quatro características principais relacionadas com a sua funcionalidade: i) conjunto de módulos, ii) conversão direta, iii) unidades aritméticas modulares e iv) conversão reversa. Cada unidade completa é baseada em um conjunto de módulos, os quais são inteiros primos entre si (co-primos). A faixa dinâmica é definida pelo produto de todos os módulos e define o intervalo de entrada. O conversor direto, também chamado de conversor binário para RNS, converte um número binário na para sua representação equivalente em RNS, baseada no conjunto de módulos. As unidades aritméticas modulares são os blocos que de fato executam paralelamente as operações de soma, subtração e multiplicação livres de carry. Por fim, o conversor reverso, também chamado de conversor RNS para binário, transforma os vários resíduos calculados pelos canais paralelos em um número binário equivalente. Esta seção apresentará de forma básica o sistema numérico residual, seleção do conjuntos de módulos, a etapa de conversão direta, as unidades aritméticas modulares de soma e multiplicação e, finalmente, a conversão reversa.

Figura 2.1: Diagrama de blocos de uma unidade aritmética completa baseada em RNS.

#### 2.1 Introdução do Sistema Numérico de Resíduos

A representação de um valor em RNS se dá por uma sequência de valores menores para uma determinada base. Essa base é formada por um conjunto de módulos  $\{m_1, m_2, ..., m_n\}$ . Os módulos devem ser co-primos, ou seja, o MDC (Máximo Divisor Comum) deve ser igual a 1, i.e.,  $MDC(m_i, m_j) = 1$ , onde  $i \neq j$ . Assim, um valor X representado em RNS tem a forma  $X = (R_1, R_2, ..., R_n)$ , onde:

$$R_i = X \mod m_i = |X|_{m_i}, \qquad 0 \le R_i < m_i.$$

(2.1)

Ou seja, o valor  $R_i$  é o resto da divisão inteira de X por  $m_i$ . Por exemplo, considerando um sistema RNS baseado no conjunto de módulos  $\{5,8,11\}$ . A representação dos valores 32 e 48 seria:

$$|32|_5 = 2,$$

$|32|_8 = 0,$   $|32|_{11} = 10$

$|48|_5 = 3,$   $|48|_8 = 0,$   $|48|_{11} = 4.$

Portanto, o valor 32 e 48 são representados em  $RNS_{(5,8,11)}$  como (2,0,10) e (3,0,4), respectivamente. Podemos fazer a soma desses dois números utilizando a representação por resíduo:

$$|2+3|_5 = |0|_5$$

,  $|0+0|_8 = |0|_8$ ,  $|10+4|_{11} = |3|_{11}$ .

O valor da soma é 80, equivalente à representação  $RNS_{(5,6,9)}$  (0,0,3). A verificação nos confirma a operação:

$$|80|_5 = 0,$$

$|80|_8 = 0,$   $|80|_{11} = 3.$

Isso demonstra como as operações de soma podem ser executadas paralelamente em diferentes canais residuais sem propagação de *carry*. O resto das operações segue o mesmo princípio.

Como citado anteriormente, o intervalo para representação exclusiva de inteiros é dada pelo DR (*Dynamic Range*) de cada conjunto de módulos, ou

seja, cada X terá uma representação RNS única desde que esteja no intervalo de [0,DR-1]. O DR é calculado multiplicando todos os módulos do conjunto:  $DR = m_1 \times m_2 \times ... \times m_n$ . Para o conjunto de módulos usado como exemplo  $\{5,8,11\}$  a faixa dinâmica é  $[0,(5\times8\times11-1)]=[0,439]$ . Outra forma de representar o DR aproximado de um conjunto de módulos é utilizando o número de *bits* do produto.

### 2.2 Conjunto de Módulos

Duas características importantes em unidades RNS são: i) O nível de paralelismo, ou seja, o número de canais modulares em que o operando será dividido e processado em paralelo; ii) A faixa dinâmica (DR), que é o intervalo para representação exclusiva de inteiros. Essas duas características são definidas pelo conjunto de módulos, bem como a complexidade das conversões. Está demonstrado no estado da arte que os conjuntos de módulos que são potência de dois  $\{2^n, 2^n \pm 1\}$  simplificam as operações aritméticas necessárias para as implementações RNS [5]. O conjunto de módulos mais tradicional é  $\{2^n, 2^n - 1, 2^n + 1\}$ , com três módulos e o DR por volta de 3n bits ( $DR \simeq 3n$ ) [6, 7]. Entretanto, esse DR não é o suficiente para aplicações que exigem uma faixa dinâmica maior e mais paralelismo. Dessa forma, novos conjuntos de módulos vêm sendo introduzidos nos últimos anos. Abaixo é apresentada uma lista de alguns conjuntos que propõem o aumento da faixa dinâmica e na Tabela 2.1 eles são organizados em uma matriz de número de módulos por DR. Estes conjuntos de módulos serão revisitados em detalhes no estado da arte dos conversores reversos (Subsecão 2.5.1).

**Tabela 2.1:** Principais conjuntos de módulos do estado da arte organizados com relação ao número de módulos vs. DR.

|    |            | Número de Módulos |                |                           |                                        |

|----|------------|-------------------|----------------|---------------------------|----------------------------------------|

|    |            | 3                 | 4              | 5                         | 6                                      |

|    | 4 <i>n</i> | [7]               | [13] [14] [15] | _                         | _                                      |

| DR | 5 <i>n</i> | _                 | [16] [17]      | [18] [19] [20]            | -                                      |

| DK | 6 <i>n</i> | _                 | [16] [17]      | [21] com ( $\beta = n$ )  | $[21] \operatorname{com} (\beta = 0n)$ |

|    | 7n         | _                 | _              | [21] com ( $\beta = 2n$ ) | [21] com ( $\beta = n$ )               |

|    | 8n + 1     | _                 | _              | -                         | [21] com ( $\beta = 2n$ )              |

- $\{2^n, 2^n \pm 1, \mathbf{2}^{n+1} + \mathbf{1}\}$  [13];

- $\{2^n, 2^n \pm 1, \mathbf{2}^{n+1} \mathbf{1}\}$  [14];

- $\{2^n, 2^n \pm 1, \mathbf{2}^{n-1} + \mathbf{1}\}\ e \{2^n, 2^n \pm 1, \mathbf{2}^{n-1} \mathbf{1}\}\ [15].$

- $\{2^{n+\beta}, 2^n \pm 1\}$  [7], onde  $0 \le \beta \le n$  é usado para extender o DR verticalmente até 4n-bits com o conjunto de 3 módulos. A sobrecarga do canal  $2^n$  até  $2^{2n}$  pode ser feito sem afetar o atraso nos canais aritméticos.

- $\{2^n, 2^n \pm 1, \mathbf{2}^{n\pm 1} \mathbf{1}\}$  [18];

- $\{2^{n+1}, 2^n \pm 1, \mathbf{2}^{n+1} \pm \mathbf{1}\}$  [19], os módulos considerados nesse trabalho são números co-primos para n par, porém, multiplicativas inversas complexas são necessárias, resultando em uma estrutura de conversão reversa bastante custosa;

- $\{2^n, 2^n \pm 1, 2^n \pm 2^{\frac{(n+1)}{2}} + 1\}$  [20], o qual é composto de módulos co-primos para n ímpar e foi revisitado por Hiasat em [22].

- $\{\mathbf{2}^{2n}, 2^n \pm 1, \mathbf{2}^n \pm \mathbf{2}^{\frac{(n+1)}{2}} + 1\}$ . Extensão puramente vertical proposta por [21], com  $(\beta = n)$ , do conjunto apresentando em [22].

- $\{2^{2n}, 2^n \pm 1, 2^{2n+1} 1\}$  [16], extensão vertical e horizontal ao custo de um conjunto de módulos desbalanceado.

- $\{2^{2n}, 2^n \pm 1, 2^{2n} + 1\}$  [17], extensão vertical e horizontal ao custo de um conjunto de módulos desbalanceado também.

- $\{2^{3n}, 2^n \pm 1, 2^n \pm 2^{\frac{(n+1)}{2}} + 1\}$ . Extensão puramente vertical proposta por [21], com  $(\beta = 2n)$ , do conjunto apresentando em [22].

- $\{\mathbf{2}^{\overbrace{3n}}, 2^n \pm 1, \mathbf{2}^n \pm \mathbf{2}^{\frac{(n+1)}{2}} + \mathbf{1}, \mathbf{2}^{n+1} + \mathbf{1}\}$ . Extensão vertical e horizontal proposta por [21], com  $(\beta = 2n)$ . Conjunto se mantém balanceado entre os canais

#### 2.3 Conversores Diretos

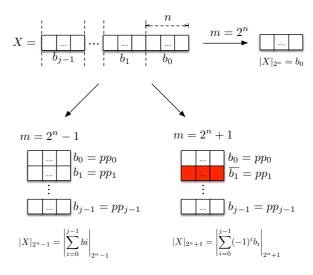

Apesar da complexidade dos conversores reversos ser maior e poder inviabilizar a aplicação de RNS na aceleração de algoritmos de processamento digitais, os conversores diretos, também chamados de conversores binários para RNS, tem um papel importante no objetivo de implementar uma unidade aritmética completa baseada em RNS. O conversor direto consiste em unidades independentes para cada módulo do conjunto de módulos definidos para transformar um número inteiro binário ponderado em sua representação equivalente RNS. A Figura 2.2 apresenta um esquema gráfico que representa a conversão de uma variável X para os módulos  $2^n, 2^n - 1, 2^n + 1$ . Considerando que a variável X tem m bits, ou seja,  $X = (x_{m-1}x_{m-2}...x_1x_0)_2$ , ela deve ser dividida em j blocos  $(b_i)$  de tamanho n. Para cálculo do valor  $|X|_{2^n}$  somente os n bits menos significativos são considerados, o resto dos bits são desprezados. Esse módulo proporciona uma conversão direta sem a necessidade de hardware, sendo representada matematicamente por:

$$|X|_{2^n} = b_0 = (x_{n-1}...x_1x_0)_2.$$

(2.2)

No processo de conversão para os módulos  $2^n \pm 1$  todos os blocos  $(b_i)$  são somados aplicando o módulo correspondente, com a diferença que para o módulo  $2^n + 1$  os blocos ímpares, destacado na Figura 2.2, são negativos. A Eq. (2.3) e a Eq. (2.4) apresentam o processo de conversão para os módulos  $2^n - 1$  e  $2^n + 1$ , respectivamente.

$$|X|_{2^{n}-1} = \left| \sum_{i=0}^{j-1} b_{i} \right|_{2^{n}-1}$$

(2.3)

$$|X|_{2^{n}+1} = \left| \sum_{i=0}^{j-1} (-1)^{i} b_{i} \right|_{2^{n}+1}$$

(2.4)

Abaixo a Eq. (2.5) converte um valor binário X de tamanho j bits, ou seja,  $X = (x_{j-1}x_{j-2}...x_1x_0)_2$ , em seu valor módulo m ( $|X|_m$ ):

$$|X|_{m} = \left| \sum_{i=0}^{j-1} 2^{i} x_{i} \right|_{m} = \left| \sum_{i=0}^{j-1} |2^{i}|_{m} x_{i} \right|_{m} = \left| \sum_{i=0}^{j-1} b_{i} \right|_{m}$$

(2.5)

**Figura 2.2:** Esquema de conversão direta para os módulos  $2^n, 2^n - 1, 2^n + 1$  de um valor X.

Se substituirmos os módulos m por  $2^n \pm k$  de forma genérica, com k ímpar, já que só números ímpares podem ser co-primos, temos:

$$|X|_{2^{n}-k} = \left| \sum_{i=0}^{j-1} k^{i} b_{i} \right|_{2^{n}-k} = \left| \sum_{i=0}^{j-1} |k^{i}|_{2^{n}-k} b_{i} \right|_{2^{n}-k}$$

(2.6)

$$|X|_{2^{n}+k} = \left| \sum_{i=0}^{j-1} (-k)^{i} b_{i} \right|_{2^{n}+k} = \left| \sum_{i=0}^{j-1} \left| -k^{i} \right|_{2^{n}+k} b_{i} \right|_{2^{n}+k}$$

(2.7)

Por exemplo, considerando n=3 para  $\{2^n\}$ ,  $\{2^n-1\}$  e  $\{2^n+1\}$ , temos o seguinte conjunto de módulos 8,7,9. Para calcular os resíduos do valor binário X=119 temos:

$$r_1 = |X|_{2^n} = |119|_8 = |(01110111)_2|_8 = (111)_2 = 7$$

$$r_2 = |X|_{2^n - 1} = |119|_7 = |(01110111)_2|_7 =$$

$$= |(01)_2 + (110)_2 + (111)_2|_7 = |1 + 6 + 7|_7 = 0$$

$$r_3 = |X|_{2^n + 1} = |119|_9 = |(01110111)_2|_9 =$$

$$= |(01)_2 - (110)_2 + (111)_2|_9 = |1 - 6 + 7|_9 = 2$$

Dessa forma, a representação residual de 119 para o conjunto de módulos (8,7,9) é (7,0,2).

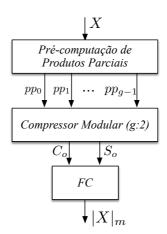

Existem vários trabalhos que propõem conversores diretos eficientes [23, 24, 25, 26], entretanto, as arquiteturas não se diferenciam muito da estrutura genérica apresentada na Figura 2.3. A pré-computação é uma etapa sem *hardware* que se encarrega de obter os produtos parciais  $|2^i|_m x_i$ ,  $0 \le i \le j-1$ . Depois os "g" produtos parciais são computados por somadores multi-operando, como árvores de somadores CSA (Carry-Save Adders) do módulo correspondente [23] ou compressores modulares, executando a operação  $\left|\sum_{i=0}^{j-1}|2^i|_m x_i\right|_m$  e obtendo dois vetores  $C_o$  e  $S_o$ , os quais são somados modularmente em um conversor final (FC - *Final Converter*). O FC é composto por somadores completos que executam uma soma modular e é detalhado na próxima seção.

Figura 2.3: Arquitetura genérica de conversor binário para RNS.

#### 2.4 Unidades Aritméticas Modulares

#### 2.4.1 Somadores

Para implementação dos conversores reversos e unidades aritméticas de soma modular eficientes é utilizado basicamente duas classes de somadores: i) Os somadores multi-operandos que não realizam a soma completa, evitando a propagação de *carry* e gerando ao final dois vetores, *carry* ( $C_o$ ) e soma ( $S_o$ ); ii) Os somadores de dois operandos que é o estágio final da soma, conhecido como conversor final (FC). Existem diversas propostas para essas duas classes, essa seção aborda rapidamente as estruturas utilizadas pelas propostas desta tese, ou seja, árvores CSA e compressores para somadores multi-operandos e conversor final paralelo para somadores de dois operandos.

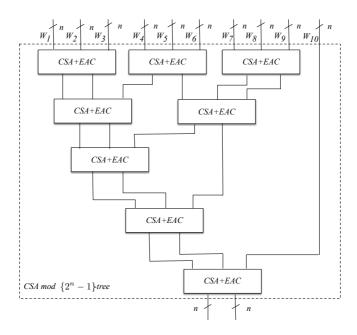

É possível escolher várias topologias de árvore CSA. Por exemplo, a árvore de Wallace é conhecida pelo seu ótimo tempo de computação, ao adicionar vários operandos. É a topologia com menor atraso entre as topologias, mas com a maior complexidade de roteamento das linhas de conexão. Já a árvore balanceada tem o menor número de linhas de interconexão, mas tem maior atraso. A Figura 2.4 mostra um exemplo de árvore de Wallace com CSA+EAC para soma modular  $\{2^n-1\}$  de 10 operandos.

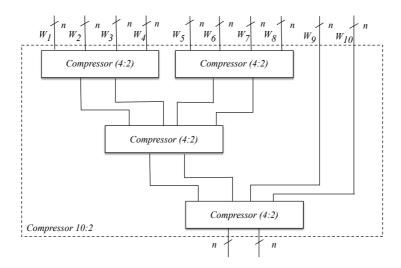

Já os compressores utilizam contadores paralelos que reduzem *bits* da mesma coluna. Um compressor maior pode ser gerados a partir de árvores de compressores menores e ainda tem uma estrutura mais regular com relação às árvores *CSA* porque os operandos são somados na forma de uma árvore binária. Conforme apresentado na Figura 2.5

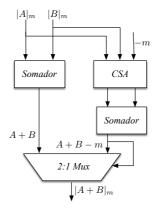

A soma modular de dois operandos  $|A+B|_m$  é calculada como A+B-m se  $A+B\geq m$  ou A+B caso contrário. A estrutura paralela apresentada na Figura 2.6 processa as duas operações juntas e é usado um multiplexador 2:1 para selecionar um dos resultados. O multiplexador é controlado pelo sinal da operação A+B-m.

A arquitetura geral pode ser especializada facilmente para  $\{2^n\}$  simplesmente implementando um somador binário (*CPA - Carry-Propagate Adder*) e ignorando as saídas de *carry*. Já para o módulo  $\{2^n + 1\}$  pode ser usado um *CPA* com EAC (*End-Around Carry*). Para aumentar a eficiência, os *CPAs* são substituídos por somadores mais eficientes na computação dos *carrys*; por exemplo, o

**Figura 2.4:** Árvore CSA para soma modular  $\{2^n - 1\}$  de 10 operandos.

somardor de prefixo paralelo KSA (Kogge-Stone Adder).

Para o módulo  $\{2^n+1\}$  as arquiteturas são mais complexas porque são necessários circuitos adicionais para tratar os *bits* com peso (n+1). Entretanto, o emprego do sistema numérico *diminished-one* é usado para evitar que o circuito de soma precise tratar esse bit adicional. O bit adicional somente é "1" para representar o valor 0, o que é facilmente alcançando subtraindo em 1 o valor binário normal. A vantagem desta representação é que o valor zero, para o qual todas as operações aritméticas são inibidas, é identificado de forma exclusiva com o valor 1 no *bit* mais significativo (MSB - *Most Significant Bit*). Por isso, para reduzir a complexidade e melhorar a eficiência, o sistema numérico *diminished-one* é usado juntamente com o *IEAC* (*Inverte End-Around Carry*) no projeto de somadores de módulo $\{2^n+1\}$ .

**Figura 2.5:** *Compressor* (10:2), a partir de compressores (4:2), para 10 operandos.

Figura 2.6: Estrutura Paralela do Conversor Final (FC)

#### 2.4.2 Multiplicadores

#### 2.4.2.1 Multiplicação $\{2^n \pm 1\}$

A multiplicação modular pode ser implementada colocando um circuito de redução modular na saída de um multiplicador binário comum. Entretanto, projetos mais eficientes são possíveis se a redução modular é combinada com a acumulação dos produtos parciais utilizando árvores multiníveis de *CSA* e uma soma final executada por *CPA* com *EAC*.

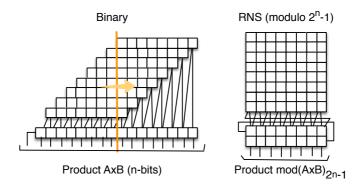

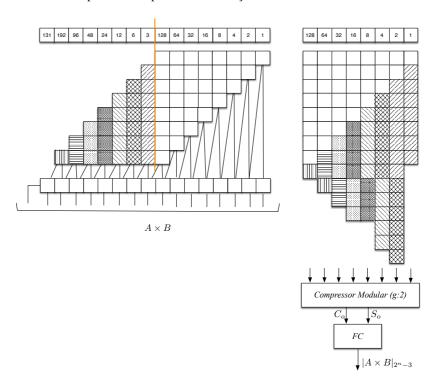

A Figura 2.7 mostra a estrutura da soma para um multiplicador módulo  $\{2^n-1\}$  com n=8 comparada com a implementação binária. Os pesos maiores do que  $2^n$  (lado esquerdo da linha vertical laranja na multiplicação binária) são divididos por  $2^n$ , ou seja, os *bits carry* de saída com peso  $\{2^{2n-2},...,2^n\}$  são inseridos na mesma linha com pesos  $\{|2^{2n-2}|_{2^n-1},...,|2^n|_{2^n-1}\} = \{2^{n-1},...,2^0\}$ . Portanto, a árvore *CSA* resultante é da forma  $n \times n$  (comprimento  $\times$  profundidade).

**Figura 2.7:** Multiplicação modular  $\{2^n - 1\}$  com n = 8 vs. multiplicação binária. Fonte: [27]

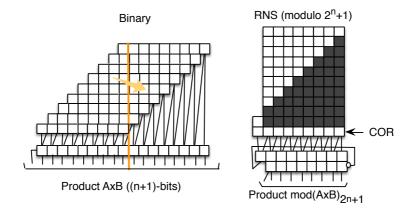

O produto do multiplicador  $\{2^n+1\}$  é calculado seguindo o mesmo método. As principais diferenças são que os *bits* com peso  $\{2^{2n-1},...,2^n\}$  são complementados e inseridos na próxima linha com pesos  $\{|2^{2n-1}|_{2^n+1},...,|2^n|_{2^n+1}\}=\{-2^{n-1},...,-2^0\}$ , indicados como valores complementados pelos quadrados es-

curecidos na Figura 2.8. Dessa forma, um estágio adicional é necessário na árvore *CSA* para soma do produto parcial complementado. Finalmente é adicionado um termo corretor (COR) para ajustar os *bits* complementados inseridos no ajuste de peso. A soma final também é executada por *CPA* com *IEAC* de módulo equivalente.

**Figura 2.8:** Multiplicação modular  $\{2^n + 1\}$  com n = 8 vs. multiplicação binária. Fonte: [27]

Essa técnica gera um multiplicador modular bastante otimizado para duas variáveis. Por exemplo, para o multiplicador módulo  $\{2^n-1\}$  com n=8 é necessária uma árvore de quatro níveis empregando seis módulos CSA ao todo. Entretanto, se um dos operandos é conhecido e constante, os produtos parciais podem ser compactados de forma a garantir uma diminuição na altura da árvore CSA e, consequentemente, no atraso causado pela operação.

## 2.4.2.2 Multiplicação $\{2^n \pm k\}$

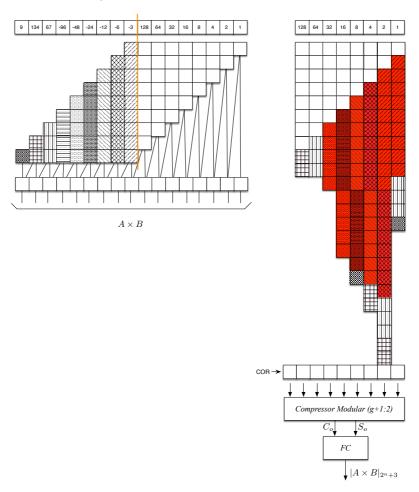

A multiplicação modular  $2^n \pm k$  também pode ser executada com a reinjeção dos *bits* para diminuir a complexidade da soma dos produtos parciais. O cálculo dos pesos de cada coluna para os módulos  $2^n - k$  é dado por  $W_i = |2^i|_{2^n + k}$ , com  $n \le i < 2n$ . A Figura 2.9 apresenta o processo para n = 8 e k = -3. É pos-

sível verificar os pesos calculados na primeira linha. Cada coluna à esquerda da linha vertical laranja tem seu peso decomposto em pesos equivalentes das colunas da direita e os *bits* equivalentes são reinseridos nos produtos parciais; por exemplo, os *bits* da coluna 3 são reinseridos na coluna com peso 2 e 1. Os quadrados que representam os *bits* com mesmo peso possuem o mesmo preenchimento para facilitar a compreensão do padrão de reinserção.

**Figura 2.9:** *Multiplicação modular*  $\{2^n - 3\}$  *com n* = 8.

Para a multiplicação modular  $2^n + k$ , o cálculo dos pesos é mais complicado e segue a Eq. (2.8). A Figura 2.10 apresenta o processo para n = 8 e k = -3. É possível perceber que existem colunas com pesos negativos. Os *bits* dessas colunas precisam ser complementados, representados em vermelho, e reinseridos à direita. Além disso, é preciso calcular um fator corretor (COR) para equalizar as

inversões dos bits.

$$W_{i} = \begin{cases} |2^{i}|_{2^{n}+k} - 2^{n} + k, & |2^{i}|_{2^{n}+k} > \frac{2^{n}+k-1}{2} \\ |2^{i}|_{2^{n}+k}, & |2^{i}|_{2^{n}+k} \le \frac{2^{n}+k-1}{2} \end{cases}, n \le i \le 2n$$

(2.8)

**Figura 2.10:** *Multiplicação modular*  $\{2^n - 3\}$  *com n* = 8.

**EAC**

#### 2.5 Conversores Reversos

O conversor reverso transforma os vários resíduos calculados pelos canais paralelos em um número binário equivalente. Para tal, vamos analisar os três algoritmos mais empregados na etapa de conversão CRT [1], MRC [3] e o novo CRT-I [4]. Por exemplo, considerando uma representação RNS baseado no conjunto de módulos  $(m_1, m_2, ..., m_n)$ , um valor representado  $(R_1, R_2, ..., R_n)$  pode ser convertido para binário (X) das seguintes forma:

#### A. Usando o CRT:

$$X = \left| \sum_{i=1}^{n} \hat{m}_{i} \left| \hat{m}_{i}^{-1} \right|_{m_{i}} \times R_{i} \right|_{M}. \tag{2.9}$$

A faixa dinâmica é igual ao produto de todos os módulos do conjunto  $(M = \prod_{i=1}^{n} m_i)$ ,  $\hat{m}_i = M/m_i$ , e  $\left| \hat{m}_i^{-1} \right|_{m_i}$  representa a multiplicativa inversa do  $\hat{m}_i$  com o respectivo módulo  $m_i$ .

#### B. *Usando o MRC*:

$$X = v_n \prod_{i=1}^{n-1} m_i + \dots + v_3 m_2 m_1 + v_2 m_1 + v_1$$

(2.10)

Os coeficientes  $v_1, v_2, ..., v_n$  podem ser obtidos dos resíduos por:

$$v_{n} = \left| \left( \left( (R_{n} - v_{1}) \times |m_{1}^{-1}|_{m_{n}} - v_{2} \right) \times \right. \\ \left. \times |m_{2}^{-1}|_{m_{n}} - \dots - v_{n-1} \right) \times |m_{n-1}^{-1}|_{m_{n}} \right|_{m_{n}}$$

(2.11)

#### C. Usando o Novo CRT-I [4]:

$$X = \left| \sum_{i=1}^{n} |V_i R_i|_{\hat{m}_1} \right|_{\hat{m}_1} m_1 + R_1$$

(2.12)

$$V_1 = \frac{\hat{m}_1 |\hat{m}_1^{-1}|_{m_1} - 1}{m_1} \tag{2.13}$$

$$V_{i} = \left| \hat{m}_{i}^{-1} \right|_{m_{i}} \frac{\hat{m}_{i}}{m_{1}}, \qquad 2 \le i \le n$$

(2.14)

Abaixo temos um exemplo numérico onde o valor representado em RNS (conjunto de módulos  $m_1, m_2, m_3 = 5, 8, 11$ ) como  $(R_1, R_2, R_3) = (3, 0, 4)$  é convertido com as Equações 2.9, 2.10 e 2.12, respectivamente.

CRT:

$$M = 5 \times 8 \times 11 = 440$$

$$\hat{m}_1 = 440/5 = 88 \quad \rightarrow \quad |\hat{m}_1^{-1}|_5 = 2$$

$$\hat{m}_2 = 440/8 = 55 \quad \rightarrow \quad |\hat{m}_2^{-1}|_8 = 7$$

$$\hat{m}_3 = 440/11 = 40 \quad \rightarrow \quad |\hat{m}_3^{-1}|_{11} = 8$$

$$X = |88 \times 2 \times 3 + 55 \times 7 \times 0 + 40 \times 8 \times 4|_{440} = 48$$

MRC:

$$v_1 = R_1 = 3$$

$v_2 = |(0-3) \times 5|_8 = 1$

$v_3 = |((4-3) \times 9 - 1) \times 7|_{11} = 1$

$X = 1 \times 5 \times 8 + 1 \times 5 + 3 = 48$

Novo CRT-I:

$$V_1 = \frac{\hat{m}_1 |\hat{m}_1^{-1}|_{m_1} - 1}{m_1} = \frac{88 \times 2 - 1}{5} = 35$$

$$V_2 = |\hat{m}_2^{-1}|_{m_2} \frac{\hat{m}_2}{m_1} = 7 \times \frac{55}{5} = 77$$

$$V_3 = |\hat{m}_3^{-1}|_{m_3} \frac{\hat{m}_3}{m_1} = 8 \times \frac{40}{5} = 64$$

$$X = |35 \times 3 + 77 \times 0 + 64 \times 4|_{88} \times 5 + 3 = 48$$

Apesar do algoritmo MRC ser bastante difundido e usado na área de conversores reversos, ele não apresenta boa eficiência para conjuntos modulares focados na obtenção de grandes faixas dinâmicas e aumento da paralelização devido à sua natureza recursiva e serial [10]. Baseados no CRT, ainda existe os algoritmos Novo CRT II e o CRTf, que são detalhados na Seção 4.2.

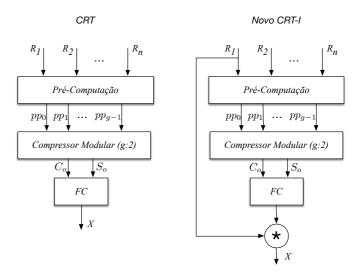

Para criação de fato do conversor reverso, é necessário levar em consideração as equações de conversão dos algoritmos, após serem simplificadas com a substituição dos valores do conjunto de módulos escolhido, e utilizar componentes de *hardware*, como somadores, multiplicadores, entre outros. Na Figura 2.11 são apresentadas arquiteturas genéricas para implementação do algoritmos CRT e o Novo CRT-I. A fase de pré-computação é executada em tempo de projeto e tem como objetivo gerar o menor número de produtos parciais da multiplicação modular das constantes geradas pelos algoritmos pelas variáveis ( $R_i$ ). A quantidade de produtos parciais é o maior impacto na eficiência dos conversores, uma vez que eles determinam a profundidade da árvore *CSA* ou do compressor que aparece como a segunda etapa. Depois disso, o conversor final faz a soma com propagação de *carry* e gera o valor binário X para o CRT. Enquanto que para completar o Novo CRT-I é necessária a concatenação com  $R_1$ , denotada pelo símbolo \*, conforme em [10, 22], sem custo em área ou atraso.

#### 2.5.1 Estado da Arte de Conversores Reversos

Este estado da arte se refere aos conversores reversos em função dos conjuntos modulares, uma vez que as estruturas reversas de conversão geralmente são apresentadas sempre que um novo conjunto de módulos é proposto.

Como comentado anteriormente, é possível usar extensões horizontais para adicionar mais módulos ao conjunto, enquanto as extensões verticais dos canais são usadas para aumentar o DR. Esta abordagem tem sido considerada e proposta no estado da arte, como os conjuntos de quatro módulos com um DR de cerca de 4n-bit:  $\{2^n, 2^n \pm 1, 2^{n+1} + 1\}$  e  $\{2^n, 2^n \pm 1, 2^{n+1} - 1\}$  [13], [14],  $\{2^n, 2^n \pm 1, 2^{n-1} + 1\}$  e  $\{2^n, 2^n \pm 1, 2^{n-1} - 1\}$  [15]. As extensões horizontais de conjuntos de cinco módulos com um DR de aproximadamente de 5n bits também foram propostas:  $\{2^n, 2^n \pm 1, 2^{n\pm 1} - 1\}$  [18],  $\{2^{n+1}, 2^n \pm 1, 2^{n+1} \pm 1\}$  [19], e  $\{2^n, 2^n \pm 1, 2^n \pm 2, 2^{\frac{(n+1)}{2}} + 1\}$  [20] que é composto por módulos co-primos para n ímpar e foi revisitado pela Hiasat em [22]. Os módulos considerados

Figura 2.11: Diagrama de blocos genéricos dos conversores reversos baseados no CRT e Novo CRT-I.

em [19] são números co-primos por n iguais, no entanto, são necessárias multiplicativas inversas complexas, resultando em estruturas de conversão reversa dispendiosas. Em [28], os autores propuseram um conjunto de oito módulos  $\{2^{n-5}-1,2^{n-3}-1,2^{n-3}+1,2^{n-2}+1,2^{n-1}-1,2^{n-1}+1,2^n,2^n+1\}$ . O conjunto de módulo proposto não é regular, apresentando canais com n até n-5 bits com módulos não co-primos, resultando em um baixo DR. Como em [19], multiplicativa inversas complexas são necessárias, resultando em estruturas de conversão inversa dispendiosas e hierarquicamente complicadas. Adicionalmente, extensões verticais têm sido propostas, como em [7] ( $\{2^{n+\beta},2^n\pm1\}$ ,  $0 \le \beta \le n$ ), no qual a variação de  $\beta$  é usado para aumentar o DR até 4n-bits com um conjunto de três módulos. Isso é alcançado em direção a um conjunto de módulos mais balanceado, uma vez que há diferença de desempenho entre as unidades  $2^n$  e as unidades aritméticas  $2^n \pm k$ . Portanto, a sobrecarga do canal  $\{2^n\}$  até  $\{2^{2n}\}$  pode ser feita sem afetar o atraso nos canais aritméticos.

Recentemente, foram propostos conjunto de módulos com ambas as extensões:  $\{\mathbf{2}^{2n}, 2^n \pm 1, \mathbf{2}^{2n+1} - \mathbf{1}\}$  [16],  $\{\mathbf{2}^{2n}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [17], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [17], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [17], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [17], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [17], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [17], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$  [18], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$ ], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n} + \mathbf{1}\}$ ], e  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^{2n$

2.6. Conclusão 49

$1, \mathbf{2}^n \pm \mathbf{2}^{\frac{n+1}{2}} + 1, \mathbf{2}^{n+1} + 1\}$  e) $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^n \pm \mathbf{2}^{\frac{n+1}{2}} + 1, \mathbf{2}^{n-1} + 1\}$  com  $-\frac{(n-1)}{2} \le \beta \le 3n$  [21]. As propostas [16] e [17] fornecem um DR de  $\simeq 6n$ -bits. A proposta [21] fornece um conjunto de módulos mais balanceado com um DR de (8n+1) bits.

O artigo [9] apresentou um método baseado no Novo CRT-I para projetar conversores reversos que usam conjunto de módulos estendidos, híbridos e genéricos na forma de  $\{\mathbf{2}^{n+\beta}, 2^n \pm 1, \mathbf{2}^n \pm \mathbf{k}_1, \mathbf{2}^n \pm \mathbf{k}_2, ..., \mathbf{2}^n \pm \mathbf{k}_f\}$ , com  $k_j$  sendo ímpar e  $0 \le \beta \le n$ . No entanto, esse método impõe uma seleção de peso modular complexa dos termos multiplicativos associada às entradas dos resíduos, que é uma desvantagem substancial. Além disso, a adição modular dessas entradas ponderadas requer um grande número de comparações e, consequentemente, um circuito dedicado é usado na arquitetura para reduzir a complexidade do passo de conversão final.

Por outro lado, os conversores reversos baseados no Teorema Chinês do Resto Aproximado (CRTf - Chinese Remainder Theorem with Fractional Values) apresentados por [12] oferecem melhorias em relação à implementação clássica do CRT. Essa abordagem propõe um novo formato para o CRTf, que permite uma conversão reversa sem erros. Comparado com o CRT clássico, que utiliza operações modulares mais complexas, o CRTf permite uma melhor implementação de hardware porque ele usa operações modulares mais simples. O gargalo dessa abordagem são as multiplicações por constantes, necessárias no processo de conversão.

Apesar das diferentes arquitetura apresentadas, os conversores reversos podem ser generalizados conforme a Figura 2.11 e analisadas com relação ao número de produtos parciais (g) na saída da pré-computação, como exemplo, na proposta de [7] temos g=4, somados por dois CSA e um somador completo, ambos módulo  $2^{2n}-1$ . Já [18], [22], [21], [9] e [17] propõem uma solução com g=5, g=8, g=10, g=9 e g=5, respectivamente.

#### 2.6 Conclusão

Esse capítulo apresentou as principais propostas no estado da arte para conjuntos de módulos e conversores. Existem diversas abordagens, mas o eixo central das soluções propostas baseadas no CRT, no Novo CRT-I e no CRTf bus-

**2.6. Conclusão 50**

cam conjuntos balanceados que permitam operações modulares mais simples no conversor reverso com a finalidade de diminuir a complexidade dessa etapa. Ao final, tudo indica que, apesar das diversas abordagens discutidas, a maior influencia está no número de produtos parciais (g). Existe um forte indício que, além da proposta de novos conjuntos balanceados, implementações focadas na otimização dos produtos parciais ("Pré-computação") e, consequentemente, na diminuição da complexidade da etapa de "compressão modular (g:2)", trazem avanço para área de conversão de RNS para binário.

# Otimização de Multiplicadores Modulares por Constante

No Capítulo 2, foram apresentados os algoritmos mais empregados na conversão da representação RNS para binário. Analisando as equações desses algoritmos, é possível perceber a repetição sistemática do multiplicador modular

por constante na Eq. (2.9) do algoritmo CRT

$$| \widehat{\hat{m}_i} | \widehat{m}_i^{-1} |_{m_i} \times R_i |$$

e na Eq. (2.12)

do Novo CRT-I

$$V_i \times R_i$$

. Além disso, no mesmo capítulo foi apresentada

a arquitetura de hardware genérica para implementação dos conversores reversos (Figura 2.11), baseados no CRT e Novo CRT-I. Destacou-se a etapa de compressão modular, que possui grande influência na eficiência da implementações dos conversores. Basicamente, essa etapa executa a soma dos produtos parciais gerados da multiplicação das várias constantes, dadas pelas equações dos algoritmos, com as variáveis, valores dos resíduos, para executar a conversão. Ao final da análise do estado da arte dos conversores reversos, percebe-se que, além da proposta de novos conjuntos de módulos, os trabalhos da área sempre visam diminuir a quantidade de produtos parciais, que entram no compressor, com as mais diversas estratégias.