# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

Tiago Augusto Fontana

AVALIAÇÃO QUANTITATIVA DO IMPACTO DA ORGANIZAÇÃO DOS DADOS NA EXECUÇÃO DE PROGRAMAS: ESTUDOS DE CASO NO CONTEXTO DA SÍNTESE FÍSICA

Florianópolis

2018

#### Tiago Augusto Fontana

# AVALIAÇÃO QUANTITATIVA DO IMPACTO DA ORGANIZAÇÃO DOS DADOS NA EXECUÇÃO DE PROGRAMAS: ESTUDOS DE CASO NO CONTEXTO DA SÍNTESE FÍSICA

Dissertação submetida ao Programa de Pós-Graduação em Ciência da Computação para a obtenção do Grau de Mestre em Ciência da Computação. Orientador: Prof. Dr. José Luís Almada Güntzel

Florianópolis

2018

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Fontana, Tiago Augusto

Avaliação quantitativa do impacto da organização dos dados na execução de programas: estudos de caso no contexto da Síntese Física / Tiago Augusto Fontana; orientador, José Luís Almada Güntzel, 2018. 106 p.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós Graduação em Ciência da Computação, Florianópolis, 2018.

Inclui referências.

1. Ciência da Computação. 2. Ciência da Computação. 3. Localidade da Cache. 4. Automação de Projeto Eletrônico (EDA). 5. Otimização de software. I. Güntzel, José Luís Almada. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Ciência da Computação. III. Título.

#### Tiago Augusto Fontana

# AVALIAÇÃO QUANTITATIVA DO IMPACTO DA ORGANIZAÇÃO DOS DADOS NA EXECUÇÃO DE PROGRAMAS: ESTUDOS DE CASO NO CONTEXTO DA SÍNTESE FÍSICA

Esta dissertação foi julgada adequada para obtenção do título de mestre e aprovada em sua forma final pelo Programa de Pós-Graduação em Ciência da Computação.

Florianópolis, 06 de Julho de 2018.

Prof. José Luís Almada Güntzel, Dr. Coordenador do Programa

Banca Examinadora:

Prof. José Luís Almada Güntzel, Dr. Universidade Federal de Santa Catarina

Orientador

Prof. Fernando Gehm Moraes, Dr.

Pontifícia Universidade Católica do Rio Grande do Sul

Prof<sup>a</sup>. Cristina Meinhardt, Dr<sup>a</sup>. Universidade Federal de Santa Catarina

Oniversidade rederal de Santa Catarina

Prof. Márcio Bastos Castro, Dr. Universidade Federal de Santa Catarina

#### **AGRADECIMENTOS**

Agradeço a meus pais Marli Dileta Secco Fontana (in memoriam) e Waldir Fontana, por todo amor, dedicação e apoio oferecidos até hoje, pois sem eles, nada disso teria acontecido.

Agradeço à minha namorada Thayrine Louise da Silva, por me acompanhar e apoiar nestes dois anos de mestrado.

Agradeço ao meu orientador José Luís Almada Güntzel, por todo o auxílio oferecido na execução deste trabalho e na escrita deste texto.

Agradeço aos membros da banca, por cederem seu tempo para a avaliação deste trabalho.

Por fim, agradeço aos colegas do ECL que de alguma forma participaram deste trabalho. Em particular aos colegas Chrystian de Sousa Guth, Renan Oliveira Netto, Sheiny Fabre Almeida e Vinícius dos Santos Livramento pela ajuda direta na realização deste trabalho.

Alguns homens vêem as coisas como são, e dizem 'Por quê?' Eu sonho com as coisas que nunca foram e digo 'Por que não?'

George Bernard Shaw

#### RESUMO

Em diversos domínios de aplicação, os programas precisam manipular grandes quantidades de dados e ao mesmo tempo, explorar a arquitetura de hardware da máquina hospedeira a fim de otimizar o desempenho. Por exemplo, game engines devem renderizar gráficos 3D com imagens de alta resolução, simular sistemas físicos realistas e também processar sistemas complexos de inteligência artificial num curto período de tempo. Para atender a esses requisitos, vários conceitos e padrões de projetos são aplicados durante o desenvolvimento de um jogo. Similarmente, as ferramentas de síntese física devem lidar com grandes quantidades de dados para resolver problemas relacionados ao projeto de circuitos com milhões de células. Os componentes pertencentes à síntese física podem ser representados utilizando-se o modelo de programação orientada a objetos (OOD). No entanto, usar esse modelo pode levar a objetos excessivamente complexos que resultam em desperdício de espaço de memória, o qual prejudica a exploração da localidade espacial na memória cache, consequentemente, degradando o tempo de execução do software. Este trabalho propõe uma organização eficiente dos dados para diferentes etapas da síntese física baseada no modelo orientado a dados (DOD). Diferentemente de OOD, o modelo DOD se concentra em como os dados são organizados na memória. Como consequência, DOD proporciona uma melhor exploração da localidade espacial da memória cache levando a uma redução no tempo de execução. Para avaliar o impacto da organização dos dados na memória cache, este trabalho compara o número de cache misses e o tempo de execução para quatro estudos de caso no contexto da síntese física. desenvolvidos com os modelos DOD e OOD, em versões sequenciais e paralelas. Os resultados experimentais mostraram que os estudos de caso usando DOD, e agrupamento dos dados quando apropriado, resultaram em reduções significativas em relação ao OOD no número de cache misses e no tempo de execução para 7 dos 8 cenários avaliados. No melhor cenário esta reducão foi de até cinco ordens de grandeza no número de cache misses. No cenário menos favorável, o estudo de caso modelado com DOD executou tão rápido quanto o modelado com OOD.

**Palavras-chave:** Otimização de Software; Localidade da Cache; Data-Oriented Design; *Electronic Design Automation*; Síntese Física.

#### ABSTRACT

In several application domains, programs have to deal with huge amount of data while exploiting the hardware architecture of the hosting machine. For example, modern game engines must render 3D graphics for high resolution images, model realistic physical systems, and also process complex artificial intelligence systems. To fulfill such requirements, several concepts and design patterns are applied during the game development. Similarly, physical design tools must handle huge amounts of data in order to solve problems for circuits with millions of cells. The physical design components may be represented by using the Object-Oriented Design (OOD) model. However, using this model may lead to overly complex objects that result in waste of cache memory space. This memory wasting harms the exploitation of locality by the cache memory and, consequently, degrades software runtime. This work proposes an efficient organization of the data for different physical design tasks based on the Data-Oriented Design (DOD) model. Unlike OOD, DOD model focuses on how the data is organized in the memory. As a consequence, DOD may better explore cache spatial locality and reduce the total runtime. In order to evaluate the impact of the data organization in the cache memory, this work compares the number of cache misses and runtime of four case studies in the context of physical design, developed with both the OOD and the DOD models, in sequential and parallel versions. The experimental results showed that the case studies using DOD, and data grouping when appropriate, resulted in significant reductions in comparison with OOD in the number of cache misses and runtime for 7 out of the 8 evaluated scenarios. In the best scenario, such reduction was up to five orders of magnitude in the number of cache misses. In the least favorable scenario, the case study modeled with DOD executed as fast as the one with OOD.

**Keywords:** Software Optimization; Cache Locality; Data-Oriented Design; Electronic Design Automation; Physical Design.

### LISTA DE FIGURAS

| Figura 1               | Exemplo de um circuito digital                          | 29 |

|------------------------|---------------------------------------------------------|----|

| Figura 2               | Hierarquia de classes                                   | 30 |

| Figura 3               | Hierarquia de memória                                   | 35 |

| Figura 4               | Exemplo de multiplicação de matrizes                    | 40 |

| Figura 5               | Exemplo de multiplicação de matrizes com particiona-    |    |

| $\mathrm{mento}\ldots$ |                                                         | 40 |

| Figura 6               | Etapas da síntese física                                | 47 |

| Figura 7               | Etapas do planejamento topológico                       | 49 |

| Figura 8               | Ilustração algoritmo Concentric Circles                 | 50 |

| Figura 9               | Comparação da utilização da cache                       | 56 |

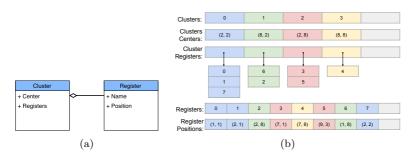

| Figura 10              | Modelagem dos dados para clusterização de registrado-   |    |

| res                    |                                                         | 57 |

| Figura 11              | Exemplo de uma entidade                                 | 59 |

| Figura 12              | Arquitetura do computador utilizado nos experimentos.   | 65 |

| Figura 13              | Exemplo de posicionamento de células sobre um circuito. | 66 |

| Figura 14              | Organização dos dados estudo de caso $1 \dots \dots$    | 67 |

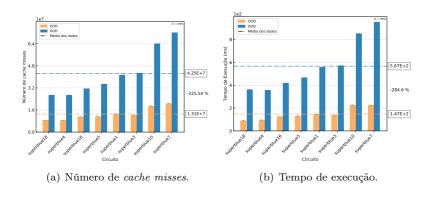

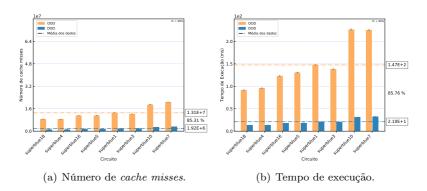

| Figura 15              | Resultados experimentais para a execução sequencial do  |    |

| estudo de              | caso 1                                                  | 69 |

| Figura 16              | Resultados do estudo de caso 1 com execução paralela    | 70 |

| Figura 17              | Exemplo do cálculo de HPWL                              | 72 |

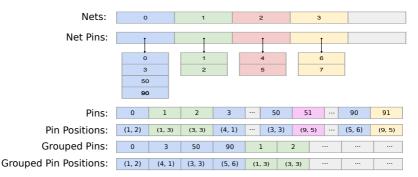

| Figura 18              | Organização dos dados estudo de caso $2 \dots \dots$    | 73 |

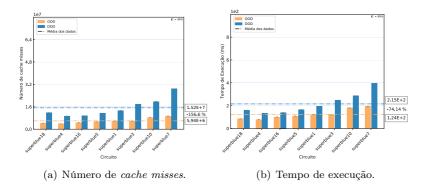

| Figura 19              | Resultados estudo de caso 2 com execução sequencial     | 74 |

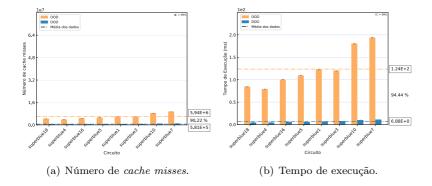

| Figura 20              | Resultados estudo de caso 2 com execução paralela       | 76 |

| Figura 21              | Agrupamento dos dados para o estudo de caso 2           | 77 |

| Figura 22              | Resultados do estudo de caso 2 com execução sequencial  |    |

| e agrupam              | ento de propriedades                                    | 77 |

| Figura 23              | Resultados do estudo de caso 2 com execução paralela e  |    |

| agrupamer              | nto de propriedades                                     | 78 |

| Figura 24              | Organização dos dados estudo de caso $3 \dots \dots$    | 81 |

| -                      | Resultados para a execução sequencial do estudo de caso |    |

|                        |                                                         | 82 |

| Figura 26              | Resultados para a execução paralela do estudo de caso   |    |

| 3                      |                                                         | 83 |

| Figura 2 | 27 | Exemplo da execução do algoritmo $A^*$                  | 85 |

|----------|----|---------------------------------------------------------|----|

| Figura 2 | 28 | Organização dos dados estudo de caso $4 \dots$          | 88 |

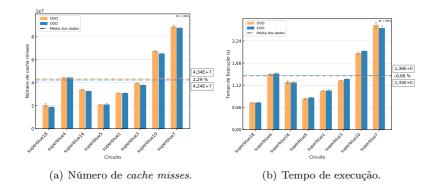

| Figura 2 | 29 | Resultados para a execução sequencial do estudo de caso |    |

| 4        |    |                                                         | 89 |

### LISTA DE TABELAS

| Tabela 1   | Eventos presentes PAPI                                    | 36 |

|------------|-----------------------------------------------------------|----|

| Tabela 2   | Características mais relevantes das ferramentas para ava- |    |

| liar o núm | ero de cache misses                                       | 38 |

| Tabela 3   | Resumo dos trabalhos correlatos                           | 45 |

| Tabela 4   | Caracterização de algoritmos e técnicas da síntese física | 53 |

| Tabela 5   | Notações utilizadas no $Entity$ -Component $System$       | 60 |

| Tabela 6   | Circuitos ICCAD 2015 CAD Contest                          | 64 |

| Tabela 7   | Comparativo da organização dos dados                      | 92 |

### LISTA DE ABREVIATURAS E SIGLAS

| AoS Array of Structures                                                       | 41 |

|-------------------------------------------------------------------------------|----|

| <b>API</b> Application Programming Interface                                  | 36 |

| CA Compressed-Array                                                           | 44 |

| CI Circuito Integrado                                                         | 31 |

| <b>DME</b> Deferred-Merge Embedding                                           | 52 |

| <b>DOD</b> Data-Oriented Design                                               | 28 |

| EDA Electronic Design Automation                                              | 28 |

| FM Fiduccia-Mattheyses                                                        | 48 |

| GE Grammatical Evolution                                                      | 42 |

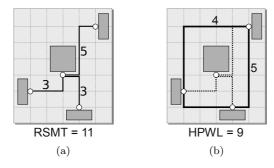

| $\mathbf{HPWL} \ \mathit{Half-Perimeter} \ \mathit{Wirelength} \ldots \ldots$ | 71 |

| ILP Programação Linear Inteira                                                | 52 |

| ITDP Incremental Timing-Driven Placement                                      | 30 |

| KL Kernighan-Lin                                                              | 48 |

| LLC Last Level Cache                                                          | 37 |

| OOD Object-Oriented Design                                                    | 27 |

| PDG Program Dependence Graph                                                  | 43 |

| RSMT Rectilinear Steiner Minimum Tree                                         | 71 |

| SA Simulated Annealing                                                        | 49 |

| SIMD Single Instruction Multiple Data                                         | 27 |

| SISD Single Instruction Single Data                                           | 68 |

| SoA Structure of Arrays                                                       | 41 |

| STA Static Timing Analysis                                                    | 31 |

| TRG Temporal-Relation Graph                                                   | 43 |

# LISTA DE SÍMBOLOS

| gcell        | porção da área do circuito                                          | 52  |

|--------------|---------------------------------------------------------------------|-----|

| S            | sistema de entidades $S$                                            | 59  |

| e            | entidade $e$                                                        | 59  |

| $id_e$       | índice $(id)$ da entidade $e$                                       | 59  |

| $E_S$        | vetor de entidades pertencente ao sistema de entidade $S\dots$      | 59  |

| $E_S(i)$     | entidade armazenada na i-ésima posição do vetor $E\ldots\ldots$     | 59  |

| $\Pi_S$      | conjunto de propriedades associadas a $S\ldots\ldots$               | 59  |

| $\Pi_S^i$    | i-ésima propriedade $\Pi$ do sistema de entidades $S$               | 59  |

| $\Pi^i_S(j)$ | valor armazenado na j-ésima posição de $\Pi_S^i \dots \dots$        | 59  |

| C            | conjunto de células $C$ do circuito                                 | 65  |

| $c_i$        | i-ésima célula do conjunto ${\cal C}$                               | 65  |

| $x(c_i)$     | posição no eixo $x$ da célula $c_i$                                 | 65  |

| $y(c_i)$     | posição no eixo $y$ da célula $c_i$                                 | 65  |

| N            | conjunto de interconexões $N$ do circuito                           | 72  |

| $n_i$        | i-ésima interconexão do conjunto $N \dots \dots$                    | 72  |

| pins(n       | $u_i)$                                                              |     |

| pin          | nos pertencentes a interconexão $n_i$                               | 72  |

| P            | conjunto de pinos $P$ do circuito                                   | 72  |

| $p_j$        | j-ésimo pino do conjunto $P\dots$                                   | 72  |

| $x(p_j)$     | posição no eixo $x$ do pino $p_j$                                   | 72  |

| $y(p_j)$     | posição no eixo $y$ do pino $p_j$                                   | 72  |

| $\mathcal R$ | conjunto de registradores $\mathcal R$ do circuito                  | 79  |

| Γ            | conjunto de <i>clusters</i> do circuito                             | 79  |

| $\gamma_i$   | i-ésimo $clister$ do conjunto $\Gamma$                              | 79  |

| h(s,t)       |                                                                     |     |

| het          | urística entre as $gcell\ s$ e $t$                                  | 85  |

| $g\_sco$     | ` '                                                                 |     |

|              | sto para percorrer o caminho entre $s$ e $x$                        | 85  |

| $f\_sco$     |                                                                     |     |

|              | imativa do custo total entre $s$ e $t$ , que passe pelo vértice $x$ | 85  |

| _            | bors(curr)                                                          | 0.5 |

| vér          | tices vizinhos ao vértice curr                                      | 85  |

### LISTA DE ALGORITMOS

| 1 | Entity Create                                      | 60 |

|---|----------------------------------------------------|----|

| 2 | Entity_Destroy                                     | 61 |

| 3 | Verificação dos Limites do <i>chip</i>             | 66 |

| 4 | Verificação dos Limites do <i>chip</i> em Paralelo | 70 |

| 5 | Half-Perimeter Wirelength (HPWL)                   | 72 |

| 6 | Half-Perimeter Wirelength (HPWL) em Paralelo       | 75 |

| 7 | K-means                                            | 80 |

| 8 | K-means em paralelo                                | 83 |

| 9 | $A^*$                                              | 86 |

# SUMÁRIO

| 1 INTRODUÇÃO                                        | 27 |

|-----------------------------------------------------|----|

| 1.1 JUSTIFICATIVA                                   | 31 |

| 1.2 OBJETIVOS E CONTRIBUIÇÕES ALCANÇADAS            | 31 |

| 1.3 CONTRIBUIÇÕES CIENTÍFICAS E TECNOLÓGICAS        | 32 |

| 1.4 ORGANIZAÇÃO DESTE TRABALHO                      | 32 |

| 2 CONCEITOS FUNDAMENTAIS                            | 35 |

| 2.1 ARQUITETURA DO SISTEMA DE MEMÓRIA               | 35 |

| 2.2 FERRAMENTAS PARA AVALIAR O NÚMERO DE <i>CA-</i> |    |

| CHE MISSES                                          | 36 |

| 3 TRABALHOS CORRELATOS                              | 39 |

| 3.1 TRABALHOS QUE ADOTAM A ABORDAGEM <i>CACHE</i> - |    |

| AWARE                                               | 39 |

| 3.1.1 Majeti et al. (2013)                          | 41 |

| 3.1.2 Álvarez et al. (2016)                         | 41 |

| 3.2 TRABALHOS QUE ADOTAM A ABORDAGEM <i>CACHE</i> - |    |

| OBLIVIOUS                                           | 42 |

| 3.2.1 Li et al. (2014)                              | 42 |

| 3.2.2 Tang et al. (2015)                            | 43 |

| 3.2.3 Qasem, Aji e Rodgers (2017)                   | 44 |

| 3.3 ANÁLISE QUALITATIVA DOS TRABALHOS CORRELA-      |    |

| TOS                                                 | 44 |

| 4 SÍNTESE FÍSICA COMO ESTUDO DE CASO                | 47 |

| 5 EXPLORANDO A LOCALIDADE ESPACIAL DOS              |    |

| DADOS                                               | 55 |

| 5.1 ENTITY-COMPONENT SYSTEM                         | 58 |

| 5.1.1 Entidades e Componentes                       | 58 |

| 5.1.2 Sistema de Entidades                          | 59 |

| 6 RESULTADOS EXPERIMENTAIS                          | 63 |

| 6.1 METODOLOGIA EXPERIMENTAL                        | 63 |

| 6.2 INFRAESTRUTURA E CONFIGURAÇÃO EXPERIMEN-        |    |

| TAL                                                 | 63 |

| 6.3 ESTUDO DE CASO 1: VERIFICANDO OS LIMITES DO     |    |

| CHIP                                                | 65 |

| 6.3.1 Modelagem dos Dados                           | 66 |

| 6.3.2 Avaliação                                     | 68 |

| 6.4 ESTUDO DE CASO 2: ESTIMATIVA DO COMPRIMENTO     |    |

| DE INTERCONEXÕES                                    | 71 |

| 6.4.1 Modelagem dos Dados                     | 73  |

|-----------------------------------------------|-----|

| 6.4.2 Avaliação                               | 74  |

| 6.5 ESTUDO DE CASO 3: CLUSTERIZAÇÃO DE REGIS- |     |

| TRADORES                                      | 79  |

| 6.5.1 Modelagem dos Dados                     | 80  |

| 6.5.2 Avaliação                               | 81  |

| 6.6 ESTUDO DE CASO 4: ROTEAMENTO GLOBAL       | 84  |

| 6.6.1 Modelagem dos Dados                     | 87  |

| 6.6.2 Avaliação                               | 89  |

| 6.7 AVALIAÇÃO GLOBAL DOS RESULTADOS           | 90  |

| 7 CONCLUSÕES E TRABALHOS FUTUROS              | 93  |

| REFERÊNCIAS                                   | 95  |

| APÊNDICE A - Lista de Publicações e Prêmios   | 103 |

### 1 INTRODUÇÃO

O paradigma de Object-Oriented Design (OOD) surgiu no final da década de 80 e início dos anos 90. Este paradigma teve como enfoque o aumento na produtividade de software por meio da facilidade no mapeamento dos objetos do mundo real para suas abstrações. Este modelo é baseado em objetos, e não em dados e processamento como na programação estruturada. Os objetos são organizados em classes de objetos e são associados a comportamentos. Cada objeto é autocontido e possui todas as informações pertinentes para a realização das ações que ele representa/possui. Este encapsulamento de informações facilita por sua vez a manutenção do código fonte e possibilita o desenvolvimento de software em larga escala.

Embora o código orientado a objetos tenha seu lugar, ele tem sido a causa de muito tempo e esforço desperdiçados durante sua vida relativamente curta em nossa indústria de desenvolvimento de software e desenvolvimento de jogos em particular (FABIAN, 2013). O modelo OOD começa a mostrar suas fraquezas quando os projetos sofrem alterações. Quando os dados pertencentes ao software sofrem algum tipo de alteração, muitas vezes é necessário que todo o software seja reescrito para suportar estas alterações. Estas refatorações, que seriam grandes e difíceis no modelo OOD, tornam-se muitas vezes triviais quando os dados são isolados das implementações (FABIAN, 2013).

Outro problema enfrentado pela orientação a objetos é a aplicação de uma mesma transformação (instrução) num grande conjunto de objetos. Armazenando contiguamente os dados pertencentes ao mesmo domínio é possível aplicar esta transformação através de uma instrução Single Instruction Multiple Data (SIMD). Já no modelo orientado a objetos faz-se necessário iterar sobre cada objeto e aplicar a transformação por meio de uma chamada de função pertencente a este objeto. Uma forma de utilizar instruções SIMD com orientação a objetos é armazenar os dados do mesmo domínio em uma estrutura contínua (como por exemplo um vetor) e cada objeto possuir uma referência para seu atributo nesta estrutura. Porém, este modelo traria complicações na manutenção adequada do objeto e pode vir a causar problemas no desenvolvimento, como por exemplo o acesso livremente a atributos que deveriam ser privativos de um objeto.

Instruções SIMD viabilizam que aplicações operem eficientemente sob um grande conjunto de dados. Um exemplo destas aplicações são as *Game engines* contemporâneas que devem renderizar gráficos 3D

em imagens de altíssima resolução, modelar sistemas físicos realistas e também processar sistemas complexos de inteligência artificial num curto espaco de tempo. Para atender a esses requisitos, vários conceitos e padrões de projetos são aplicados durante o desenvolvimento de um jogo para explorar as arquiteturas modernas de computadores, onde o acesso a memória representa o principal gargalo. Um dos conceitos empregados durante o desenvolvimento de game engines é chamado de Data-Oriented Design (DOD). Este modelo de programação foca em como os dados serão organizados na memória visando um processamento mais eficiente e explora os recursos disponíveis no computador, como por exemplo os recursos do subsistema de memória, a capacidade de multiprocessamento e a execução de instruções SIMD. Da mesma forma que as game engines, as ferramentas de Electronic Design Automation (EDA) devem ser capazes de lidar com um grande volume de dados com um curto tempo de execução. Adicionalmente, o prazo entre o projeto e a fabricação de um chip é cada vez mais limitado para que um novo produto eletrônico possa garantir o mercado (timeto-market) (PAPA et al., 2011).

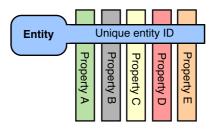

O modelo OOD faz uso intensivo de herança entre as classes de objetos. Esta herança tende a criar hierarquias de classes complexas, dificultando a manutenção do software (NYSTROM, 2014). Embora o modelo DOD possa diminuir essas limitações, a modelagem das estruturas e relações complexas não são tão naturais quanto no modelo OOD. Por este motivo, um padrão de projeto chamado Entity-Component System é amplamente adotado no desenvolvimento de game engines para lidar eficientemente com a criação e destruição de entidades, e também para gerenciar seus dados subjacentes (denominados de propriedades) (WIEBUSCH; LATOSCHIK, 2015; BERGE et al., 2014). Este sistema também pode substituir árvores de herança por relações simples, como agregação e composição, para construir um software mais robusto e modular.

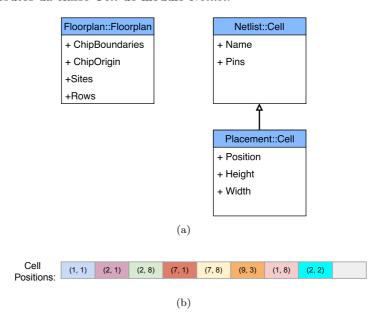

Para ilustrar algumas dificuldades decorrentes do uso intensivo de herança proporcionado pelo modelo OOD, consideremos o desenvolvimento de uma biblioteca de software para resolver problemas relacionados à síntese física ( $Physical\ Design$ ) de circuitos integrados seguindo a metodologia  $standard\ cells^1$ . Dentre tais problemas está a estimativa

<sup>&</sup>lt;sup>1</sup>A metodologia standard cell baseia-se na utilização de leiautes pré-projetados, referenciados por células, a serem usados na fabricação em silício das portas lógicas e outros elementos mais complexos. As informações geométricas (dimensões, posições dos pinos, bloqueios para roteamento etc) e as informações elétricas de cada célula (atraso, potência etc), necessárias para garantir o sucesso da síntese física, são reunidas num repositório denominado de biblioteca de células (KAHNG et al., 2011).

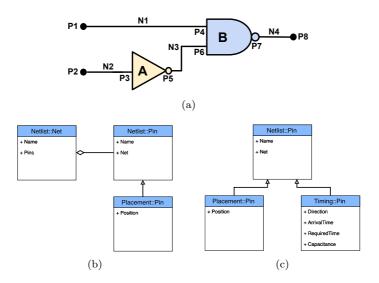

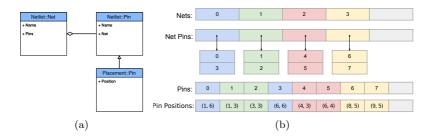

do comprimento de uma interconexão entre duas portas lógicas (células). Neste contexto, considere a Figura 1(a), a qual apresenta um exemplo do um circuito digital contendo duas portas lógicas (A e B), quatro interconexões (N1 a N4) e oito pinos (P1 a P8).

Figura 1 – Exemplo de um circuito digital (a) e dois possíveis diagramas de classe (b) (c) para o problema de estimar o comprimento de uma interconexão.

A Figura 1(b) apresenta o diagrama de classes para uma modelagem, segundo o modelo OOD, da estimativa do comprimento de interconexão que considera dois módulos: netlist e placement. O módulo netlist possui as classes net e pin para descrever as interconexões do circuito e os pinos associados, respectivamente. Para a classe pin, o módulo netlist caracteriza apenas o nome do pino e a interconexão à qual esse pino pertence, sem nenhuma informação de posicionamento. O módulo placement, por sua vez, descreve as posições dos pinos. A seta com ponta de losango entre as classes pin e net representa uma relação de agregação, o que significa que uma interconexão possui referência aos seus pinos, enquanto um pino possui referência à interconexão à qual ele pertence. A seta de ponta triangular entre as duas classes pin representa um relacionamento de hierarquia, o que significa que a classe pin do módulo placement estende os atributos da classe pin no módulo netlist.

Porém, quando as informações da temporização dos pinos forem necessárias, a classe pin do módulo netlist apresentada na Figura 1(b) deverá ser estendida por uma nova classe Pin pertencente ao módulo Timing, conforme mostrado na Figura 1(c). Contudo, problemas que necessitem de informações de posicionamento e temporização (como por exemplo algoritmos de  $Incremental\ Timing$ - $Driven\ Placement\ (ITDP)$ ) deverão possuir informações de posicionamento e tempo. Seguindo o modelo OOD, isso pode ser feito através de herança múltipla, onde uma nova classe pin estende as classes pin dos módulos placement e timing. No entanto, a herança múltipla não é suportada por todas as linguagens de programação e, mesmo quando suportada, não é recomendada porque isso pode levar a problemas na modelagem do  $software\ (NYSTROM,\ 2014)$ .

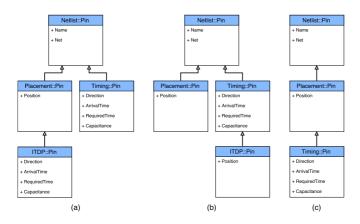

Figura 2 – Possível hierarquia de classes para suportar informações de posicionamento e tempo para um algoritmo de *timing-driven placement* utilizando o modelo OOD.

Sem recorrer à herança múltipla, a solução consiste em criar uma nova classe pin que se estende a partir do módulo placement ou timing e possui repetição do código da outra classe (que não foi estendida). As Figuras 2 (a) e (b) mostram essas duas soluções. De qualquer forma, não há maneira simples de reutilizar informações de posicionamento e tempo sem ocorrer replicação de informações. A única opção que resta é juntar todas as informações na classe pin do módulo timing fazendo com que estenda a classe pin do módulo placement. Esta solução é ilustrada na Figura 2 (c). No entanto, nem sempre é necessário ter informações de posicionamento no módulo timing. Por exemplo, uma

ferramenta de *Static Timing Analysis* (STA) pode não precisar de informações de posicionamento durante as primeiras etapas de projeto. Portanto, a adoção da última solução levaria ao desperdício da localidade espacial da memória *cache*, já que informações desnecessárias seriam recuperadas juntamente com informações úteis.

Para garantir tempos de execução aceitáveis, as ferramentas de EDA devem explorar ao máximo as otimizações de software, como por exemplo: o uso de estruturas de dados otimizadas, paralelização e exploração da localidade da memória cache. Se examinarmos as ferramentas atuais de EDA disponibilizadas pela academia, como por exemplo aquelas descritas por Michigan (2010), Kahng, Lee e Li (2014), Jung et al. (2016), Flach et al. (2017), Initiative (2018), todas elas realizam uma série de otimizações de software, mas nenhuma se concentra na organização de dados para explorar a localidade espacial da memória cache. Já os trabalhos que focam na exploração da localidade espacial e temporal dos dados, como os de Li et al. (2014), Tang et al. (2015), Qasem, Aji e Rodgers (2017), não realizam avaliações no contexto da síntese física. O presente trabalho se concentra na discussão e aplicação desses conceitos modernos de engenharia de software no desenvolvimento de ferramentas para a síntese física de Circuitos Integrados (CIs).

#### 1.1 JUSTIFICATIVA

Apesar de vários trabalhos encontrados na literatura fazerem otimizações de *software* mencionadas na seção anterior, nenhum deles avalia o impacto destas diferentes estratégias quando aplicadas no contexto da síntese física.

Portanto, é desejável uma análise quantitativa do impacto da organização dos dados no contexto da síntese física, sobretudo, com um estudo de problemas reais utilizando entradas realistas para a experimentação.

#### 1.2 OBJETIVOS E CONTRIBUIÇÕES ALCANÇADAS

Este trabalho possui como objetivo a avaliação quantitativa do impacto da organização dos dados em algoritmos de síntese física. A fim de tentar permitir uma extrapolação das conclusões de tal avaliação para algoritmos semelhantes em outros domínios de aplicação, este trabalho também sistematiza as principais características e estruturas

de dados dos algoritmos aqui avaliados.

Os objetivos específicos deste trabalho são:

- Avaliar as organizações de dados propostas, comparando-as com a modelagem baseada em orientação a objetos. A comparação é realizada avaliando-se o número de cache misses gerados pelas implementações dos algoritmos, bem como os tempos de execução associados;

- Investigar possíveis otimizações na organização dos dados para cada algoritmo implementado;

- Avaliar o desempenho da paralelização dos algoritmos implementados com as diferentes organizações dos dados.

#### 1.3 CONTRIBUIÇÕES CIENTÍFICAS E TECNOLÓGICAS

Este trabalho traz as seguintes contribuições científicas e tecnológicas:

- Implementação de um sistema de componentes e entidades. Estes conceitos serão detalhados na Seção 5.1;

- Avaliação quantitativa do desempenho resultante da modelagem dos dados em algoritmos utilizados na síntese física;

- Resultados experimentais utilizando casos de uso realistas. Como dados de entrada são utilizados circuitos industriais oriundos da competição ICCAD CAD Context 2015 (KIM et al., 2015);

- Comparação quantitativa do número de *cache misses* e do tempo de execução para quatro algoritmos da síntese física.

#### 1.4 ORGANIZAÇÃO DESTE TRABALHO

O Capítulo 2 revisa alguns conceitos fundamentais para a melhor compreensão deste trabalho. No Capítulo 3 são apresentados os trabalhos correlatos na otimização da organização dos dados para uma melhor utilização da memória *cache*. O Capítulo 4 apresenta, de forma sintética, as etapa pertencentes à síntese e caracteriza os algoritmos envolvidos em cada etapa. O Capítulo 5 descreve a proposta de organização dos dados e seus possíveis impactos no contexto da síntese física.

No Capítulo 6 são apresentadas as organizações dos dados utilizadas em cada estudo de caso e os respectivos resultados experimentais. Por fim, o Capítulo 7 apresenta as conclusões obtidas com a realização deste trabalho e os possíveis desdobramentos futuros.

#### 2 CONCEITOS FUNDAMENTAIS

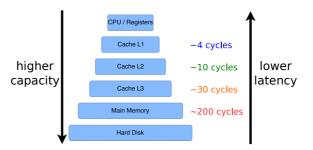

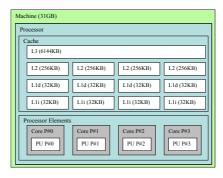

## 2.1 ARQUITETURA DO SISTEMA DE MEMÓRIA

A arquitetura de memória de computadores modernos é tipicamente hierárquica, como mostrado na Figura 3, onde os níveis mais baixos na hierarquia (disco rígido e memória principal) têm maior maior capacidade de armazenamento, mas apresentam maior latência. Por outro lado, os níveis mais altos (memória cache e registradores da CPU) são rápidos, mas possuem capacidade de armazenamento limitada. Quando um determinado programa precisa de um dado, mas o mesmo não se encontra nos registradores da CPU, será realizada uma busca por este dado nos níveis mais altos da hierarquia da memória, iniciando pela cache de primeiro nível. Enquanto o dado não for encontrado, a busca vai seguindo pelos níveis superiores, eventualmente chegando no último nível. O evento de encontrar este dado em algum dos níveis de cache é denominado cache hit. Já um cache miss ocorre quando o dado somente é encontrado nos níveis inferiores da hierarquia (memória principal e disco rígido). No pior caso, este dado somente será encontrado no disco rígido e então será copiado para todos os níveis da hierarquia. Quando o dado buscado é recuperado para a cache de mais alto nível e posteriormente armazenado num registrador da CPU, o programa que estava acessando tal dado volta a executar. Se este dado for necessário novamente e o bloco que o contém ainda estiver presente em algum nível da memória cache, sua busca resultará em cache hit quando do acesso ao primeiro dos níveis de cache que o contém (PATTERSON; HENNESSY, 2013).

Figura 3 – Hierarquia de memória presente em computadores modernos. Adaptada de Patterson e Hennessy (2013).

A localidade espacial (spatial locality) é uma propriedade importante dos sistemas hierárquicos de memória. Esta propriedade afirma que a probabilidade de acessar uma posição da memória é maior se uma posição próxima já foi referenciada (PATTERSON; HENNESSY, 2013). O sistema de cache explora esta propriedade armazenando os dados em blocos (cache blocks). Assim, sempre que algum dado é acessado a partir da memória principal, ele é recuperado para a cache juntamente com outros dados que estavam armazenados próximos a ele. Consequentemente, se os dados próximos forem acessados posteriormente, resultarão em cache hits.

# $2.2\,$ FERRAMENTAS PARA AVALIAR O NÚMERO DE CACHE MISSES

A ferramenta Performance Application Programming Interface (PAPI) (TERPSTRA et al., 2010) é desenvolvida pelo Innovative Computing Laboratory da University of Tennessee. Esta ferramenta fornece ao programador uma interface para o uso de contadores de hardware presentes nos processadores. Ela permite estabelecer uma relação entre o desempenho do software e os eventos do processador. A instrumentação do código fonte é realizada por meio da inclusão da Application Programming Interface (API) da ferramenta PAPI e da inicialização de suas estruturas. Com isso, é possível avaliar apenas uma porção do código fonte e retirar interferências indesejadas, como por exemplo aquelas oriundas das leituras de arquivos (parsing).

A Tabela 1 apresenta algum dos eventos que podem ser avaliados com a ferramenta PAPI e que estão disponíveis para a máquina utilizada nos experimentos deste trabalho, cuja configuração é descrita na

| Nome          | Código     | Derivado             | Descrição                        |

|---------------|------------|----------------------|----------------------------------|

| PAPI_L1_DCM   | 0x80000000 | Não                  | Level 1 data cache misses        |

| PAPI_L1_ICM   | 0x80000001 | Não                  | Level 1 instruction cache misses |

| PAPI_L1_TCM   | 0x80000006 | $\operatorname{Sim}$ | Level 1 cache misses             |

| PAPI_L2_DCM   | 0x80000002 | $\operatorname{Sim}$ | Level 2 data cache misses        |

| $PAPI_L2_ICM$ | 0x80000003 | Não                  | Level 2 instruction cache misses |

| PAPI_L2_TCM   | 0x80000007 | Não                  | Level 2 cache misses             |

| PAPI_L3_TCM   | 0x80000008 | Não                  | Level 3 cache misses             |

| PAPI_PRF_DM   | 0x8000001c | Não                  | Data prefetch cache misses       |

Tabela 1 – Eventos presentes PAPI

Seção 6.2. Estes eventos variam de acordo com os contadores presentes em cada máquina e podem ser listados com o comando "papi\_avail -a". Um evento pode estar diretamente disponível como um único contador, ou pode ser derivado usando uma combinação de contadores ou ainda pode não estar disponível. A terceira coluna indica se o evento utiliza ou não uma combinação de contadores de *hardware*.

Devido ao fato de depender dos contadores da máquina hospedeira, uma análise que considere diferentes organizações de memória exige, necessariamente, a realização de experimentos em máquinas com características distintas, o que se constitui em dificuldade extra em termos de infraestrutura experimental.

Perf (Linux profiling with performance counters (PERF, 2018)) é uma ferramenta de análise de desempenho do Linux capaz de criar um perfil estatístico de todo o sistema (tanto o kernel quanto o código do usuário) utilizando os contadores de hardware. Portanto, esta ferramenta também é limitada pela arquitetura presente na máquina hospedeira. Além disso, com Perf não é possível limitar-se a análise a somente parte do código fonte, uma vez que o relatório gerado somente realiza estatísticas no nível de funções do código fonte, não medindo as informações internas a elas (por linhas de código fonte). Apesar de tais limitações, em 2012 dois engenheiros da IBM reconheceram Perf como sendo uma das ferramentas mais utilizadas no Linux (ZANELLA, 2012).

O framework Valgrind (NETHERCOTE; SEWARD, 2007) possibilita a construção de ferramentas de análise dinâmica. Existem ferramentas Valgrind que podem detectar automaticamente muitos bugs de gerenciamento de memória. Dentre estas ferramentas, Cachegrind (SEWARD; NETHERCOTE; FITZHARDINGE, 2004) possibilita a simulação da execução de um binário sobre diversas configurações de arquiteturas de cache. Sua execução é dada com o comando "valgrind – tool=cachegrind prog" onde "prog" representa o executável desejado. A configuração da simulação permite definir o tamanho da memória cache, sua associatividade, o tamanho de suas linhas e a política de escrita (por exemplo, quando um miss de escrita ocorre, o bloco escrito é colocado na cache D1). Tal flexibilidade permite a esta ferramenta simular uma infinidade de arquiteturas existentes ou até mesmo novas arquiteturas. Porém, a simulação somente reporta resultados referentes ao primeiro (L1) e ao último nível da arquitetura de memória (Last Level Cache (LLC)).

Já a ferramenta Intel VTune Amplifier (ZONE, 2018) possibilita uma análise entre múltiplas CPUs e utiliza os contadores de *hardware*. Para utilizar esta ferramenta é preciso compilar a aplicação que será

testada com o compilador ICC (Intel C++ Compiler) (INTEL, 2018). O ponto negativo desta ferramenta é o fato da licença de uso ser paga.

A Tabela 2 reúne as principais características de cada ferramenta de avaliação do número de cache misses aqui apresentadas. As ferramentas encontram-se ordenadas pelo método utilizado na avaliação do número de cache misses e também se sua licença é gratuita ou paga. Pode-se notar que a principal diferença entre todas as ferramentas é a instrumentação, do código fonte, possível na sua utilização. Ferramentas como Perf e Valgrind — Cachegrind permitem avaliar o número de cache misses para cada função do código fonte, ao passo que, a ferramenta PAPI permite que esta avaliação seja realizada internamente a uma determinada função, sendo assim mais detalhada e precisa. Este trabalho utilizou a ferramenta PAPI para realizar a avaliação do número de cache misses e assim analisar quantitativamente o impacto da organização dos dados na execução de programas.

Tabela 2 – Características mais relevantes das ferramentas para avaliar o número de *cache misses*

| Ferramenta                    | Método de avaliação                              | Níveis da memória $\mathit{cache}$ | Instrumentação          | Licença          |

|-------------------------------|--------------------------------------------------|------------------------------------|-------------------------|------------------|

| PAPI                          | contadores de hardware                           | L1, L2 e L3                        | linhas do código fonte  | gratuita         |

| Perf<br>Intel VTune Amplifier | contadores de hardware<br>contadores de hardware | L1, L2 e L3<br>L1, L2 e L3         | funções do código fonte | gratuita<br>paga |

| Valgrind - Cachegrind         | simula arquitetura                               | L1 e LLC                           | funções do código fonte | gratuita         |

#### 3 TRABALHOS CORRELATOS

Este capítulo revisa os principais trabalhos correlatos em otimização do uso da memória cache. A Seção 3.1 abordada os trabalhos que realizam otimizações tirando proveito de informações da arquitetura da memória cache, referenciados na literatura por cache-aware. Posteriormente, na Seção 3.2, são abordados os trabalhos que propõem técnicas que independem da arquitetura de memória cache na qual o programa será executado, denominados de cache-oblivious. Por fim, na Seção 3.3, são apresentados um resumo do estado da arte e as oportunidades de contribuições científicas. É importante ressaltar que este capítulo não faz uma análise exaustiva de cada trabalho citado, mas busca apresentar as características mais relevantes das principais abordagens para otimização do uso da memória cache.

# $3.1\,$ TRABALHOS QUE ADOTAM A ABORDAGEM CACHE-AWARE

Algoritmos cache-aware são aqueles que possuem informações, a priori, sobre a arquitetura da cache. Com estas informações eles buscam otimizar seus comportamentos para extrair o máximo de desempenho de uma dada arquitetura.

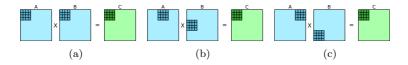

Para exemplificar isso considere o algoritmo de multiplicação de duas matrizes. A Figura 4 apresenta como é feita a multiplicação de duas matrizes utilizando a abordagem sem otimizações. Neste exemplo é realizado a multiplicação da matriz A pela matriz B, o que resulta na matriz C. Quando a iteração da multiplicação de matrizes for carregando as linhas/colunas em sequência, a memória cache será preenchida gradualmente (Figura 4 (a)). Supondo que o tamanho das matrizes (A e B) seja significativamente grande, as linhas destas serão longas o que fará com que a memória cache descarte o que já foi carregado inicialmente para liberar espaço para os novos itens a serem processados (células em vermelho da Figura 4 (b)).

Ao chegar no final da multiplicação de um par de linha/coluna (o que fara o produto de um único elemento da matriz C) e iniciar o próximo, alguns dados que estavam recentemente na memória cache serão novamente necessários. Porém, como estes foram substituídos, a multiplicação terá de esperar para que estes retornem à memória cache (Figura 4 (c)). Assim, esta abordagem desperdiça a localidade espacial fornecida pela memória cache.

Figura 4 – Exemplo de multiplicação de matrizes sem otimizações.

Um algoritmo cache-aware para a multiplicação de matrizes pode tirar proveito do conhecimento do tamanho do bloco da memória cache executando as operações em uma submatriz que acomode-se totalmente nesta memória. Assim, este algoritmo evita que os blocos sejam substituídos e portanto explora a localidade espacial fornecida pela memória cache. A multiplicação de matrizes em blocos (submatrizes) é possível porque tal operação é composta pelo somatório dos produtos dos elementos das matrizes e a ordem como são feitas as adições não é relevante. O único cuidado que se deve tomar neste caso é para que todos os produtos sejam realizados corretamente e contribuam para as somas adequadas.

A Figura 5 ilustra a execução de um algoritmo cache-aware de multiplicação de matrizes. Neste exemplo, as matrizes são particionadas em matrizes menores (submatrizes de tamanho  $4\times 4$  na Figura 5) a fim de que estas possam ser recuperadas totalmente pela memória cache. Esta otimização faz com que o número de cache misses seja reduzido drasticamente, uma vez que as submatrizes recuperada para a cache são totalmente utilizadas antes de recuperar uma nova submatriz.

Figura 5 – Exemplo da multiplicação de matrizes grandes através do particionamento em submatrizes.

## 3.1.1 Majeti et al. (2013)

O trabalho de Majeti et al. (2013) possui como objetivo principal determinar o melhor leiaute dos dados para um determinado programa computacional. Segundo o autor, o leiaute ideal para um programa depende se o mesmo é executado em um núcleo de CPU, em uma GPU dedicada (externa ao processador), ou em uma GPU integrada ao processador. Com isso, para obter programas que extraíssem todo o potencial de uma arquitetura, seria necessário reescrever o código-fonte para cada arquitetura de CPU/GPU.

Para sanar o problema da reescrita do código para cada arquitetura, Majeti et al. (2013) propuseram a inserção de metadados nos códigos-fonte. Estes metadados guiariam um compilador a selecionar as melhores estruturas de dados para uma dada arquitetura de CPU/GPU. Com isso, o compilador é capaz de escolher e converter os dados de Array of Structures (AoS) para Structure of Arrays (SoA) e vice-versa. Majeti et al. ainda ressaltam que os metadados se fazem necessários pois a escolha de um leiaute de dados que maximize o número de acessos coalescidos (acessos que utilizam o mesmo bloco da cache e, portanto, minimizam o número de cache misses) para uma GPU é NP-completo. A prova de que esta escolha é da classe NP-completo foi realizada por Wu et al. (2013).

Para avaliar a eficiência da técnica de compilação proposta, os autores geraram benchmarks sintéticos e avaliaram a execução compilando esses códigos com e sem os metadados. Em algumas arquiteturas como AMD 4-core A10-5880K CPU e NVIDIA Tesla M2050 GPU foram obtidos  $speedups^1$  de até  $27,11\times$  e  $29,50\times$ , respectivamente.

# 3.1.2 Álvarez et al. (2016)

O trabalho de Álvarez et al. (2016) visa encontrar a melhor configuração de uma arquitetura cache para um conjunto predefinido de aplicações. O contexto deste trabalho inclui aplicações para dispositivos móveis e portanto, operados a bateria. Seu principal objetivo é reduzir o tempo de execução das aplicações, bem como, o consumo energético demandado pelas mesmas. Para determinar as arquiteturas, este trabalho visa encontrar a capacidade, tamanho do bloco e associatividade da cache.

$<sup>^1{\</sup>rm A}$ métrica speedup corresponde à relação entre o tempo de execução da solução sequencial e o tempo da solução paralela, para um determinado número de threads.

Álvarez et al. (2016) tomaram como base o trabalho de Wang, Mishra e Gordon-Ross (2012). Wang, Mishra e Gordon-Ross (2012) realizaram uma análise combinando análise estática e dinâmica para determinar as configurações da cache para sistemas embarcados de tempo real. Com isso, Wang, Mishra e Gordon-Ross (2012) minimizam o consumo de energia em até 74%.

Para determinar as arquiteturas, Álvarez et al. (2016) encontraram os parâmetros da cache baseados em *Grammatical Evolution* (GE) (DEMPSEY; O'NEILL; BRABAZON, 2009) utilizando tracers e determinando a configuração baseado-se no tempo de execução e consumo de energia. Esta técnica garante uma redução no tempo de execução pois o algoritmo meta-heurístico converge mesmo com um curto número de gerações e tamanho da população: a técnica adiciona um hash para armazenar os valores objetivos de cada cache avaliada. Para avaliar o trabalho, foram utilizados os benchmarks Mediabench (LEE; POTKONJAK; MANGIONE-SMITH, 1997). Esta técnica conseguiu reduzir o tempo de execução em 75%, em média, e obteve 96% de redução de consumo de energia, em média.

# 3.2 TRABALHOS QUE ADOTAM A ABORDAGEM CACHE-OBLIV-IOUS

Algoritmos cache-oblivious (também chamdos de cache-transcendent) são projetados para explorar a memória cache de uma CPU sem ter o tamanho da mesma (ou o tamanho das linhas, etc.) como um parâmetro explícito (FRIGO et al., 1999). Assim, um algoritmo cache-oblivious é concebido para funcionar otimizadamente, sem modificação, em inúmeras arquiteturas com diferentes tamanhos de cache, ou para uma hierarquia de memória com diferentes níveis de cache e tamanhos variados.

# 3.2.1 Li et al. (2014)

O trabalho de Li et al. (2014) tem como enfoque o gerenciamento da cache compartilhada em processadores multi-core. Segundo os autores, a gestão do compartilhamento de cache não é apenas para alcançar um bom desempenho, mas também para garantir um desempenho estável em um ambiente dinâmico, considerando não apenas programas paralelos, mas também programas sequenciais executando simultanea-

mente em núcleos distintos de uma arquitetura de cache compartilhada.

Para identificar onde o gerenciamento da cache pode incidir, os autores descrevem um método para reorganizar o código para um leiaute ideal com base no Program Dependence Graph (PDG). Com estas informações, é construído um Temporal-Relation Graph (TRG) (GLOY; SMITH, 1999) para otimizar o leiaute do código em tempo de compilação. A otimização realiza duas transformações: reordenamento global das funções e/ou reordenamento dos blocos inter-procedurais. Estes reordenamentos são baseados na afinidade do acesso à cache.

Para mensurar suas otimizações, os autores utilizaram os benchmarks SPEC CPU 2006 (HENNING, 2006), realizando os experimentos tanto em uma máquina real como em um simulador de instruções da cache. Para medir a proporção de cache misses, utilizaram contadores de desempenho de hardware. O método melhorou o desempenho de todos os programas em até 3% quando estes foram executados separadamente (somente um programa por processador). Quando executados mais de um programa por processador, este método obteve até 10,3% de melhoria. Ao melhor utilizar a cache compartilhada, o método amplia a melhoria da transferência de hyper-threading em 8%.

## 3.2.2 Tang et al. (2015)

O trabalho de Tang et al. (2015) visa preservar a localidade da cache em algoritmos de Programação Dinâmica no contexto de algoritmos cache-oblivious paralelos. Estes algoritmos geralmente subdividem o problema em instâncias menores, o que assintoticamente atinge o uso ótimo da localidade temporal de uma cache sequencial. No entanto, o escalonamento das tarefas pela granularidade de suas dependências limita o paralelismo ao introduzir dependências artificiais entre subtarefas recursivas, além das decorrentes das equações de recorrência (TANG et al., 2015).

Para realizar as otimizações, Tang et al. (2015) removeram as dependências artificiais. Com isso, foi possível agendar as tarefas prontas para execução assim que todas as restrições reais de dependência eram satisfeitas (instruções atômicas foram usadas para identificar e iniciar tarefas prontas). Assim, eles conseguiram preservar a otimização da cache herdada da estratégia de dividir e conquistar. Com a paralelização e remoção das dependências artificiais, este trabalho atingiu uma melhoria de 3 a 5 vezes no tempo absoluto de execução.

# 3.2.3 Qasem, Aji e Rodgers (2017)

Segundo os autores, este é o primeiro trabalho a considerar a organização dos dados juntamente com o leiaute da memória. Qasem, Aji e Rodgers (2017) caracterizam os problemas de desempenho com a organização de dados em arquiteturas de memória heterogêneas, visando descobrir os cenários aos quais seria rentável reorganizar as estruturas de dados compartilhadas para melhorar o desempenho. Segundo os autores, a eficiência do acesso aos dados é impactada pelos padrões de acesso à memória, leiaute da estrutura de dados e características do caminho sobre o qual os dados serão transferidos entre o processador e a unidade de memória.

Com base no estudo realizado sobre os efeitos das organização de dados tradicionais para sistemas de memória heterogêneos, como AoS e SoA, os autores propõem uma nova estrutura de dados denominada Compressed-Array (CA). Esta estrutura de dados se comporta tanto como AoS ou SoA, dependendo do tipo de acesso a dados que está sendo realizado. As decisões sobre a organização dos dados considera três atributos principais: register pressure, intensidade aritmética e esparsidade no acesso aos dados.

O estudo realizado por Qasem, Aji e Rodgers (2017) demonstrou que a abordagem utilizando SoA nem sempre é lucrativa e que a escolha da organização dos dados deve considerar uma variedade de fatores, incluindo intensidade aritmética e esparsidade no acesso aos dados. A nova estratégia de organização dos dados (CA), que aborda as limitações das abordagens atuais (AoS e SoA), atingiu uma aceleração de uma ordem de magnitude em algumas arquiteturas.

# 3.3 ANÁLISE QUALITATIVA DOS TRABALHOS CORRELATOS

Esta seção apresenta uma comparação qualitativa dos trabalhos correlatos citados neste capítulo. A Tabela 3 classifica os trabalhos correlatos de acordo com o modelo de memória *cache* considerado (*Cache-Aware* ou *Cache-Oblivious*) e o momento em que a otimização ocorre. Ela também identifica os casos de usos que foram utilizados em cada um dos trabalhos.

Diversos métodos de otimizações já foram avaliados, dentre os quais se destacam: heurísticas para selecionar estrutura de dados (MA-JETI et al., 2013), reorganização das instruções baseando-se em grafo de dependências (LI et al., 2014) e conversão de estruturas de dados

Trabalho Consideração da Cache Momento da Otimização Casos de Uso Majeti, 2013 Cache-Aware Compilação sintéticos Álvarez, 2016 Cache-Aware Compilação Mediabench Li, 2014 Cache-Oblivious Compilação SPEC2006 CPU Tang, 2015 Cache-Oblivious Pós-Compilação sintéticos Qasem, 2017 Cache-Oblivious Pós-Compilação sintéticos algoritmos de Este Trabalho Cache-Oblivious Pré-Compilação síntese física\*

Tabela 3 – Resumo dos trabalhos correlatos

para aumentar a utilização da *cache* compartilhada empregando transformações em tempo de compilação (SUNG; STRATTON; HWU, 2010). Porém, a grande maioria destes trabalhos avalia seus resultados com *benchmarks* sintéticos.

Particularmente, não foram localizados trabalhos que considerassem otimizações de software cache-oblivious de algoritmos para a síntese física. Portanto, o presente trabalho possui como principal diferencial a aplicação de técnicas de otimizações no contexto da síntese física. Estas otimizações foram implementadas com uma biblioteca open source para ensino e pesquisa de síntese física chamada Ophidian (Embedded Computing Lab, 2018). Como desejava-se incorporar na biblioteca Ophidian os artefatos implementados no contexto do presente trabalho, optou-se pelo modelo Cache-Oblivious uma vez que neste as otimizações são independentes das arquiteturas, ficando-se assim fiel à filosofia open source. Para avaliar os algoritmos de síntese física considerando um cenário realista, os experimentos realizados utilizaram circuitos industriais providos para a análise do problema C da competição ICCAD 2015 CAD Contest (KIM et al., 2015).

<sup>\*</sup> Casos de uso realistas que consideram dados oriundos de circuitos industriais providos pela competição ICCAD2015.

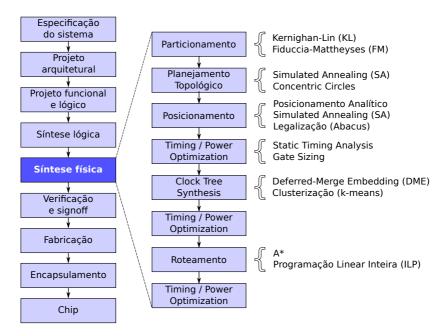

### 4 SÍNTESE FÍSICA COMO ESTUDO DE CASO

Este capítulo caracteriza os algoritmos empregados na etapa de síntese física do fluxo de projeto de CIs segundo a metodologia standard cells, enfatizando a organização dos dados de cada algoritmo. A Figura 6 apresenta o fluxo de projetos de um CI com um maior detalhamento para a etapa de síntese física. Note que apesar do fluxo apresentado ser linear por simplicidade, é comum que durante a sua execução seja necessário retornar para uma ou mais etapas anteriores o que dá origem a ciclos de iteração. Como exemplo, suponha que a etapa de roteamento da síntese física não consiga encontrar rotas para finalizar todas as interconexões dos sinais. Neste caso, a síntese deverá retornar à etapa de posicionamento a fim de que as posições de algumas células sejam alteradas, na expectativa de que uma nova execução do roteamento logre sucesso.

A síntese física é responsável por instanciar todos os elementos

Figura 6 – Etapas da síntese física com seus respectivos algoritmos/-técnicas. Figura adaptada de Kahng et al. (2011).

(células) do circuito com suas respectivas informações geométricas, posicionar estes em uma região 2-D e realizar as interconexões necessárias. O resultado da síntese física é um conjunto de especificações que serão posteriormente verificadas, antes de serem utilizadas na fabricação do CIs (KAHNG et al., 2011). O **particionamento** é a primeira etapa da síntese física e tem como objetivo dividir o CI em sub-circuitos para minimizar o número de interconexões entre estas partições (KAHNG et al., 2011). Para resolver este problema de particionamento, existem dois algoritmos clássicos: Kernighan-Lin (KL) (KERNIGHAN; LIN, 1970) e Fiduccia-Mattheyses (FM) (FIDUCCIA; MATTHEYSES, 1988).

Os dois algoritmos, KL e FM, representam o circuito através de um grafo G(V,E), onde os nodos  $v \in V$  representam as células e as arestas  $e \in E$  modelam as conexões entre as células. Dado este grafo G, cujo |V|=2n, onde  $n\in\mathbb{N}$ , e cada aresta e possui o mesmo peso, o algoritmo KL particiona o conjunto de nodos V em dois conjuntos disjuntos  $(A \in B)$  de mesmo tamanho, isto é, |A| = |B| = n. Para realizar este particionamento, o algoritmo KL realiza a troca de dois nodos  $v_1 \in A$  e  $v_2 \in B$  entre as partições, com objetivo de minimizar o número de arestas intersectadas pelas partições. Após esta troca, os nodos  $(v_1 e v_2)$  são fixados para prevenir movimentos reversos. O algoritmo FM oferece melhorias significativas perante o algoritmo KL. Nele, uma única célula pode ser movida entre as particões, o que facilita o particionamento de conjuntos de tamanhos distintos ( $|A| \neq |B|$ ). O algoritmo FM utiliza a área da célula no cálculo do peso das arestas do grafo. Esta consideração leva a mover primeiro as células com menor área e visa reduzir a perturbação gerada pelo particionamento. A complexidade do algoritmo FM é  $\mathcal{O}(n)$ , onde n=|V|, ao passo que a complexidade do algoritmo KL é  $\mathcal{O}(n^2 \log n)$ , onde n = |V|.

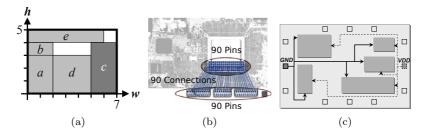

Na etapa de **planejamento topológico** são definidas as localizações e formas dos módulos pertencentes ao circuito. Com estas informações, é possível realizar estimativas precoces do comprimento das interconexões (wirelength) e atraso. Esta análise inicial permite identificar quais blocos precisam de maior otimização nas etapas posteriores do fluxo de projeto do CI. A etapa de planejamento topológico é tipicamente dividida em três subetapas, quais sejam: floorplanning, pin assignment e power planning. A subetapa de floorplanning determina as localizações e dimensões, com base nas áreas e relações dos módulos, de modo a otimizar o tamanho do chip, reduzir as interconexões e otimizar a temporização do circuito. Para isso, esta etapa avalia diferentes posicionamentos dos módulos pertencentes ao circuito. O resultado final desta etapa pode ser observado na Figura 7(a), onde a área total do

chip foi minimizada e possui 35 unidades. Um possível algoritmo para esta etapa é o Simulated Annealing (SA) (RUSSELL; NORVIG, 2009).

O algoritmo SA é iterativo - parte de uma solução inicial  $(s_i)$  e busca incrementalmente melhorar a função objetivo F. A cada iteração, soluções vizinhas  $(S_v)$  são consideradas. Estas soluções vizinhas são obtidas com uma pequena perturbação na solução atual  $(S_v = s_a \pm \alpha)$ . Para cada  $s \in S_v$ , se s for melhor que a solução atual  $(F(s) < F(s_a)$  assumindo um objetivo de minimização da função objetivo F) esta solução é tomada como nova solução atual  $(s_a = s)$ . Senão, existe uma probabilidade t (chamada de temperatura, por analogia ao processo metalúrgico de recozimento) da solução s ser tomada como solução atual. Esta probabilidade s0 e reduzida à medida que o algoritmo executa, de forma que o mesmo sempre possui convergência para uma solução ótima local.

Figura 7 – Etapas do planejamento topológico. Etapa de *floorplanning* em (a); etapa de *pin assignment* em (b) e etapa de *power planning* em (c). Figura retirada de Kahng et al. (2011).

A subetapa de pin assignment conecta as redes de sinais de interface (entradas e saídas) do CI com os pinos pertencentes aos blocos internos ao CI. O resultado final desta etapa pode ser observado na Figura 7(b). A Figura 8 apresenta os principais passos do algoritmo Concentric Circles (KOREN, 1972; BRADY, 1984), um dos principais algoritmos para esta etapa. Este algoritmo assume que todos os pinos externos (pinos fora do bloco atual) possuem localizações fixas (representados pelos círculos em verde na Figura 8(a)). O algoritmo utiliza dois círculos concêntricos - o círculo interno mapeia os pinos do bloco atual (fontes dos sinais), ao passo que o círculo externo mapeia os pinos dos demais blocos conectados a este (destinos dos sinais). Para cada pino, é traçada uma linha do centro do círculo até sua posição, e sua posição é projetada para o respectivo círculo. Este mapeamento pode ser observado pelos pontos em vermelho na Figura 8(b). O ma-

peamento inicial é determinado interconectando-se um dado pino fonte e um destino (linha trastejada da Figura 8(c)) e mapeando os demais pinos no sentido horário. O mapeamento de todos os pinos pode ser observado na Figura 8(d). Este processo é repetido para cada combinação de fonte/destino, sendo o melhor mapeamento determinado pela menor distância Euclidiana entre todos os fontes/destinos. Neste exemplo, o melhor mapeamento para os pinos é o mostrado pela Figura 8(e). Após determinar o mapeamento, este algoritmo conecta os pinos do bloco atual (fontes dos sinais) com os pinos dos demais blocos conectados a este (destinos dos sinais), Este passo é ilustrado pela Figura 8(f).

Figura 8 – Exemplo da execução do algoritmo *Concentric Circles*. Adaptado de Kahng et al. (2011).

Na subetapa de power planning constrói-se a rede de distribuição de energia, isto é, as redes de VDD e de ground, de modo a assegurar que cada bloco seja alimentado com a tensão apropriada. A Figura 7(c) apresenta o resultado desta etapa.

A etapa de **posicionamento** (placement) é responsável por encontrar as posições e orientações de todos os elementos do circuito numa superfície planar. Este posicionamento deve respeitar uma série de restrições (as células não podem se sobrepor, todas as células devem estar alinhadas com as linhas e colunas do circuito, as células devem respeitar a linha de alimentação, sendo rotacionadas quando necessário) e minimizar uma gama de objetivos (comprimento das interconexões, densidade do circuito). A etapa de posicionamento é dividida em três sube-

tapas: posicionamento global, legalização e posicionamento detalhado. O posicionamento global negligencia algumas restrições (sobreposição e alinhamento das células) para simplificar o problema e viabilizar o posicionamento de CIs com milhões de células. O principal objetivo nesta etapa é a redução das interconexões, enquanto procura equalizar a densidade de portas pelo circuito. Para encontrar o local ideal de cada célula no circuito, são utilizadas técnicas analíticas para minimizar a função objetivo (TSAY; KUH; HSU, 1988; EISENMANN; JOHANNES, 1998; LIN et al., 2013), como por exemplo programação quadrática e programação geométrica.

Como as técnicas de posicionamento global negligenciam algumas métricas, a etapa subsequente, denominada **legalização**, tem como propósito resolver as violações introduzidas pelo posicionamento global, tais como: sobreposições de células, e alinhamento das células com a grade de alimentação, linhas e colunas do circuito. Existem diversos algoritmos para a legalização de CIs, sendo o Abacus (SPINDLER; SCH-LICHTMANN; JOHANNES, 2008) um dos mais utilizados. Abacus é um algoritmo de programação dinâmica que legaliza as células do circuito uma de cada vez, posicionando-as nas linhas que minimizam seu deslocamento com relação às posições encontradas pelo posicionamento global.

A etapa de legalização pode perturbar a solução encontrada pelo posicionamento global. Então, após a legalização é aplicada uma etapa de posicionamento detalhado. Esta etapa reposiciona algumas células do circuito, otimizando métricas específicas, como por exemplo, atraso do circuito e densidade das células. Para esta etapa são utilizados algoritmos iterativos que refinam incrementalmente o posicionamento das células críticas do circuito.

Com todas as células do circuitos posicionadas e legalizadas a etapa de **clock tree synthesis** (geração da árvore de relógio) irá agrupar elementos sequenciais sincronizados pelo menos sinal de relógio e planejar a rede de relógio do CI. Um dos algoritmos clássicos para o agrupamento de elementos conectados pela mesma rede de relógio é denominado K-means (SELIM; ISMAIL, 1984). O algoritmo inicia criando k clusters (grupos) com centros aleatórios. Em seguida, na etapa de assinalamento, todos os elementos sequenciais são assinalados para o cluster mais próximo. Após assinalar todos os elementos, o centro do cluster é ajustado para que corresponda ao centro de massa dos elementos que o pertencem. Estas duas etapas são repetidas por um número fixo de vezes ou até que os centros dos clusters convirjam.

Para gerar a rede de relógio, dentre os algoritmos clássicos temos

como exemplo o  $Deferred-Merge\ Embedding\ (DME)\ (BOESE;\ KAHNG,\ 1992).$  Este algoritmo é baseado no conceito de divisão e conquista e em tempo linear constrói, a topologia de conexão no plano de Manhattan para criar uma árvore de relógio com  $clock\ skew\ zero$ , minimizando o comprimento de fio das interconexões de relógio.  $Clock\ Skew\$ é a máxima diferença, no tempo de chegada  $(arrival\ time)$  do sinal de relógio, entre todos os elementos sequenciais. Se t(u,v) representa o atraso na chegada do sinal de relógio entre os elementos sequenciais  $u\ ev$ , o skew de uma rede de relógio T é calculado segundo a Equação 4.1.

$$skew(T) = \max_{S_i, S_j \in S} |t(S_0, S_i) - t(S_0, S_j)|$$

(4.1)

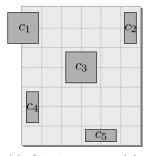

A etapa de **roteamento** é responsável por criar todas as interconexões de sinais (nets) do CI. Esta etapa é subdividida em dois passos: 1) roteamento global: 2) roteamento detalhado. No roteamento global a área do circuito é dividida segundo uma grade, sendo cada divisão da grade referenciada por gcell. A capacidade de cada gcell corresponde ao número de interconexões que podem ser roteadas na porção do circuito por ela representada. O modelo utilizado para representar estas informações de forma computacional é um Grafo G(V, E) no qual cada vértice  $v \in V$  representa uma gcell e cada aresta  $(u, v) \in E$  representa a capacidade da gcell u rotear um sinal para a gcell vizinha v. Então, um algoritmo de busca em grafo, como por exemplo o algoritmo A\* (RUS-SELL; NORVIG, 2009), é usado para identificar as gcells pelas quais a interconexão irá passar, a fim de modelar uma conexão entre um par de pinos. Na etapa de roteamento detalhado são definidas as trilhas de roteamento, vias e camadas de metal para cada segmento de interconexão do circuito. Estas definições devem respeitar todas as regras de desenho do leiaute estabelecidas para uma dada tecnologia de fabricação (KAHNG et al., 2011). Para isso, é definido um conjunto de equações a serem solucionadas por meio de Programação Linear Inteira (ILP). Entre os roteadores clássicos baseados em ILP estão Sidewinder (HU; ROY; MARKOV, 2008) e BoxRouter (CHO; PAN, 2007).

Ao longo do fluxo de projeto do CI, a etapa de timing/power optimization é responsável por garantir o atendimento da especificação de consumo de energia e da frequência de operação alvo, o que requer estimativas precisas de atraso. Para estimar o atraso do circuito, a  $Static\ Timing\ Analysis\ (STA)\ (SRIVASTAVA;\ SYLVESTER;\ BLAAUW,\ 2006;\ CHADHA;\ BHASKER,\ 2009)\ propaga os atrasos das células e interconexões para identificar os locais com violações temporais. Para isto, o circuito é modelado como um grafo <math>G(V,E)$  no qual cada vér-

tice  $v \in V$  representa uma célula do circuito e cada aresta  $(u,v) \in E$  representa a interconexão entre a célula u e a célula v. Uma vez identificadas as violações temporais, diferentes heurísticas são aplicadas para resolvê-las.

A Tabela 4 enumera as etapas da síntese física e caracteriza os algoritmos e as técnicas empregadas em cada etapa. Ela também relaciona as estruturas de dados usadas pelos referidos algoritmos e técnicas. Note que diversos algoritmos/técnicas utilizam estruturas de dados elementares, como por exemplo: arranjos, pilhas, filas, conjuntos, entre outras. Algumas outras etapas representam as informações do circuito por meio de grafo. Também existem etapas que fazem uso de outros métodos de programação, tais como: Programação Linear, Programação Quadrática e Programação Dinâmica.

| Etapa                          | Algoritmo / Técnica                                            | Estrutura de Dados / Método                                 |  |  |

|--------------------------------|----------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Particionamento                | Kernighan-Lin (KL)<br>Fiduccia-Mattheyses (FM)                 | Grafo Grafo Elementar Elementar                             |  |  |

| Planejamento Topológico        | Simulated Annealing (SA)<br>Concentric Circles                 |                                                             |  |  |

| Posicionamento                 | Posicionamento Analítico<br>Simulated Annealing (SA)<br>Abacus | Programação Quadrática<br>Elementar<br>Programação Dinâmica |  |  |

| Timing / Power<br>Optimization | Static Timing Analysis (STA)<br>Gate Sizing                    | Grafo<br>Grafo                                              |  |  |

| Clock Tree Synthesis           | Deferred-Merge Embedding (DME)<br>K-means                      | Elementar<br>Elementar                                      |  |  |

| Roteamento                     | A*<br>Sidewinder                                               | Grafo<br>Programação Linear Inteira (IL                     |  |  |

Tabela 4 – Caracterização de algoritmos e técnicas da síntese física

Com isso é possível eleger um subconjunto, dentre os algoritmos/técnicas empregados no fluxo da síntese física, que cubra as características mais relevantes de todos os problemas encontrados em tal fluxo. Desta forma, para este trabalho os seguintes algoritmos/técnicas foram escolhidos como estudos de caso:

- 1. Verificação dos limites do *chip*: pertencente à etapa de legalização do posicionamento de um CI. Este estudo de caso representa tarefas simples e com estruturas de dados elementares. Porém, estas são executadas muitas e muitas vezes durante o fluxo de projeto.

- 2. Estimativa do comprimento de interconexões: pertencente às etapas de posicionamento e timing/power optimization. Esta

tarefa depende de diversas informações, tradicionalmente separadas em diversos módulos. Possui baixa intensidade aritmética e utiliza estrutura de dados elementares.

- 3. Clusterização de registradores: Pertencente à etapa de Clock Tree Synthesis. Esta tarefa necessita de poucas informações e utiliza estruturas de dados elementares. Porém, realiza um alto número de operações aritméticas.

- Roteamento global: pertencente à etapa de roteamento do CI.

Esta etapa opera sobre um grafo que representa o leiaute do circuito e visa determinar o percurso de cada interconexão do circuito.

Não foram analisadas tarefas que utilizam Programação Linear e Programação Quadrática pois grande parte do esforço nestes modelos concentra-se na solução de um sistema de equações matemáticas. Estas equações são resolvidas por meio de solucionadores matemáticos externos, os quais possuem como entrada estruturas de dados previamente definidas. Isto torna impossível aplicar outra organização (por exemplo DOD) nos dados internos destes resolvedores. Com isso, alterar a organização dos dados numa pequena parcela da tarefa provavelmente não surtiria efeito sobre o contexto global da tarefa.

Por limitação do escopo deste trabalho, não foram analisadas tarefas que fazem uso de Programação Dinâmica. Por outro lado, as características encontradas nos algoritmos/técnicas selecionados também estão presentes em algoritmos que resolvem problemas de diversos outros domínios de aplicação, o que permite, em certa medida, especularse sobre a generalização das conclusões a serem obtidas por meio dos experimentos realizados neste trabalho e apresentados no Capítulo 6.

# 5 EXPLORANDO A LOCALIDADE ESPACIAL DOS DADOS

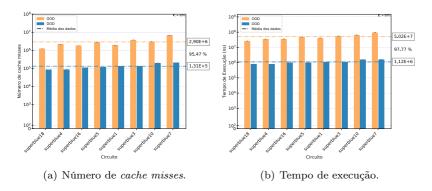

Este capítulo apresenta a proposta de organização dos dados para melhorar o desempenho de algoritmos. Inicialmente, são discutidas as limitações do modelo OOD e o de como o modelo DOD pode sanar as mesmas. Então, na Seção 5.1 é apresentado um padrão de projeto que segue o modelo DOD e otimiza a localidade espacial dos dados, otimizando assim os acessos à memória realizados pelas tarefas.

Como revisado na Seção 2.1, a arquitetura de computadores modernos possui um hierarquia de memória. Esta hierarquia de memória possui algumas propriedades, sendo uma delas a localidade espacial. É possível explorar esta propriedade mudando a forma como os dados são organizados em um determinado software, até mesmo quando não se possui informação da arquitetura na qual este software irá executar. Isto é possível, uma vez que, ao armazenar dados de uma mesma categoria de forma contígua estamos aumentando a probabilidade de um acesso gerar um cache hit.

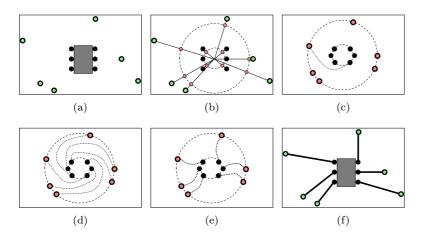

Por exemplo, no contexto da síntese física, um algoritmo de Clusterização de Registradores executa operações em todas as posições dos registradores de um circuito. Ao armazenar todas as posições destes registradores em um único vetor contíguo, este algoritmo irá incorrer em um número inferior de cache misses para recuperar todos os dados. Como consequência, o tempo de acesso aos dados é reduzido e o desempenho do software é melhorado. Esta organização de dados nem sempre é eficientemente feita pelo modelo de programação OOD. Neste modelo de programação, os dados são armazenados agrupando-se todas as informações de um mesmo objeto num único registro. Observe que com esta abordagem, quando os objetos são recuperados para a cache, alguns dados inúteis (atributos do objeto) são carregados junto. Portanto, parte do espaço da memória cache é desperdiçado com dados que não serão utilizados pelo algoritmo.

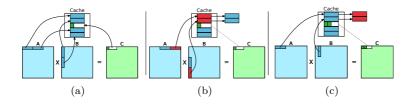

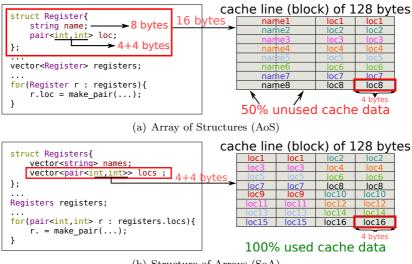

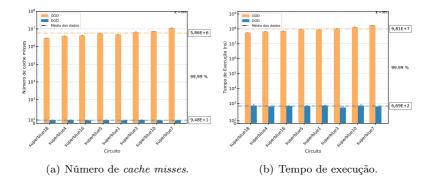

Com o objetivo de explanar como a organização dos dados pode impactar na utilização da memória cache, a Figura 9 apresenta um comparativo entre duas organizações de dados para a mesma funcionalidade. Nesta figura são apresentados trechos de códigos (lado esquerdo) para cada organização e um bloco da cache após a execução (lado direito). A Figura 9 (a) representa a modelagem dos dados seguindo a abordagem AoS, que é utilizada na orientação a objetos (OOD). A Figura 9 (b) representa a abordagem SoA, utilizada no modelo orientado

a dados (DOD). Admita que, para ambos os casos, a *cache* apresentada possui blocos com tamanho de 128 *bytes*, cada número inteiro ocupa 4 *bytes* e, por motivos de simplicidade, cada palavra (*string*) ocupa 8 *bytes*.

(b) Structure of Arrays (SoA)

Figura 9 – Comparação da utilização da cache para diferentes modelos de organização dos dados.

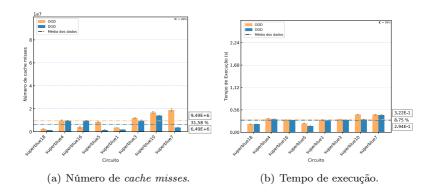

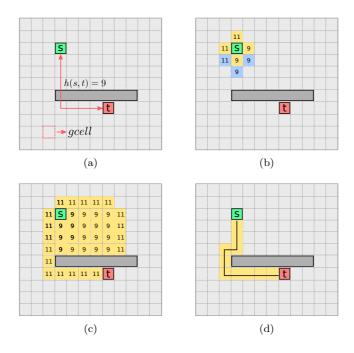

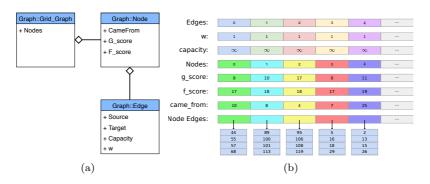

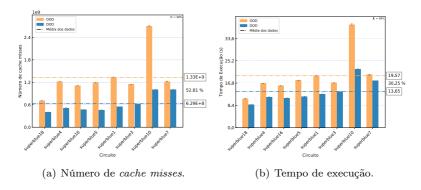

Pode-se notar que no modelo OOD, quando ocorre um cache miss, todo o objeto precisa ser recuperado para a cache. Ao recuperar todas as informações do objeto, desperdiça-se espaço com atributos/informações que não serão utilizados na solução do problema. No exemplo da Figura 9 (a) são carregados para a cache os nomes e as posições dos registradores (Struct Register). Porém, considerando que se desejasse alterar somente as posições dos registradores, 50% dos dados recuperados por um cache miss seriam desperdiçados.