Universidade Federal de Santa Catarina Centro de Blumenau Departamento de Engenharia de Controle e Automação e Computação

André Luiz de Sousa Marcondes Reuter

## Application of the embedded component technology in highly compact inverters

Blumenau 2018

### André Luiz de Sousa Marcondes Reuter

## Application of the embedded component technology in highly compact inverters

Final paper submitted in partial fulfillment of the requirements for the degree of BEng. in Automation and Control Engineering of the Universidade Federal de Santa Catarina. Advisor: Prof. Dr. Tiago Davi Curi Busarello

Universidade Federal de Santa Catarina Centro de Blumenau Departamento de Engenharia de Controle e Automação e Computação

> Blumenau 2018

André Luiz de Sousa Marcondes Reuter

## Application of the embedded component technology in highly compact inverters

Final paper submitted in partial fulfillment of the requirements for the degree of BEng. in Automation and Control Engineering of the Universidade Federal de Santa Catarina.

**Examination** Committee

Prof. Dr. Tiago Davi Curi Busarello Universidade Federal de Santa Catarina Orientador

anama Us Ci

Prof. Dra. Janaina Gonçalves Guimarães Universidade Federal de Santa Catarina

Prof. Dr. Adriano Péres Universidade Federal de Santa Catarina

Blumenau, May 8, 2019

Dedico este trabalho a minha família, meus amigos e todos meus professores e mestres.

## Acknowledgements

I would like to thank, above all, my family, specially my parents, Tatiana and Rubens Reuter that stood by my side through my entire life and without their support and love none of what I've accomplished would be possible. Also, my friends that made joyful and unforgettable one of the most difficult times of my life, and have been and always will be there whether for a sad cry or a good laugh. Finally, I would like to deeply thank my professors at the university that really made the difference and my supervisor, Gilles Rouffaud, and the whole team at Fraunhofer ISE, that made this beautiful work possible and my time in Freiburg a wonderful experience so far.

"It is not despair, for despair is only for those who see the end beyond all doubt." (J.R.R. Tolkien)

## Resumo

O setor de energia renovável testemunha um crescimento contínuo desde o começo do século, especialmente o ramo fotovoltaico (PV). Paralelamente ao crescimento em capacidade instalada, há também os avanços em pesquisa e desenvolvimento na área. A questão mais preocupante com os módulos PV é sua baixa eficiência, apenas entre 14%e 18%. Logo, deve haver desenvolvimento de novas tecnologias para elevar a eficiência dos sistemas. Um dos componentes chave em instalações fotovoltaicas são os sistemas de eletrônica de potência (conversores CC-CC e CC-CA), portanto, a eficiência de tais equipamentos deve ser a maior possível. Nesse sentido o microinversor HiGaN foi desenvolvido no Fraunhofer ISE. Esse protótipo atingiu alta eficiência com uma alta compacidade e avaliou o uso de transistores GaN nessa aplicação. Entretanto, de modo a ser ainda mais competitivo, o volume e o peso podem ser reduzidos. Uma estratégia compatível para atingir redução de tamanho é o uso da tecnologia de componentes embarcados (TCE), que é uma técnica de fabricação de placas de circuito impresso (PCI) em que os componentes são integrados dentro do substrato. Esse trabalho traz uma revisão e a formação de uma base de dados sobre a TCE e sua aplicação em uma tentativa de reduzir o tamanho da placa mãe do microinversor HiGaN. Uma metodologia de design é desenvolvida e aplicada e cinco novas versões da placa mãe são projetadas, além de cinco diferentes sub módulos. Os projetos são comparados com suas versões originais e uma análise econômica é feita em torno de ofertas enviadas por fabricantes. Simulações térmicas de transistores GaN embarcados foram conduzidas para avaliar outras capacidades da TCE e fornecer um ponto de vista mais amplo sobre a tecnologia. Os resultados indicam que foi possível atingir uma redução em área de no máximo 27.1% em uma das versões da placa mãe. Um dos sub módulos projetados atingiu uma redução em área de 65% confirmando que a TCE permite reduções mais substanciais em placas de baixa potência. Os resultados das simulações térmicas demostraram que a TCE pode ser uma ferramenta útil para melhorar o comportamento térmico de componentes ativos de potência. O trabalho mostra que o desenvolvimento da tecnologia deve ser continuado e devem existir mais aplicações em eletrônica de potência usando substratos orgânicos, de modo a explorar todas as facetas da tecnologia.

Palavras-Chave: 1. Tecnologia de Componentes Embarcados. 2. Microinversor. 3.

HiGaN. 4. PCI.

## Abstract

The renewable energy sector witness continuous growth since the start of the century, specially the photovoltaic (PV) branch. Parallel to the growth in installed capacity there is also advances in research and development in this area. The most significant issue with PV modules is the low efficiency, only between 14% and 18%. Therefore, there must be development of new technologies to increase the systems' efficiency. One of the key components in the PV systems is the power electronic systems (DC-DC and DC-AC converters) therefore the efficiency of such devices must be the highest possible. In this sense the HiGaN microinverter was developed at the Fraunhofer ISE. This prototype achieved very high efficiency with a compact form factor and evaluated the use of GaN transistors in this application. However, in order to be even more competitive the volume and weight can be further reduced. A suitable strategy to achieve size reduction is using the embedded component technology (ECT), which is a printed circuit board (PCB) manufacturing technique where the components are integrated inside the substrate. This work brings an overview and a database formation on the ECT and the application of the technology in an attempt to reduce the HiGaN microinverter motherboard size. A design methodology is developed and applied and five new versions of the motherboard are designed alongside five new submodules. The designs are compared with their original versions and an economic analysis is made around offers provided by manufacturers. Although none of the designs are realized, thermal simulations of embedded GaN transistors are performed to evaluate other capabilities of the ECT and provide a wider look into the technology. The results indicate that it was possible to achieve a maximum size reduction of 27.1% on one of the motherboard designs. One of the microcontroller modules designed achieved 65% of area reduction confirming that the ECT allows for more substantial size reduction when applied in low power boards. The thermal simulations demonstrated that the ECT can be a useful tool to improve thermal behavior of power active components. This work shows that the technology development must be continued and there must be more applications of the ECT in power electronics using organic substrates in order to explore all the facets of the technology.

Keywords: 1. ECT. 2. Microinverter. 3. HiGaN. 4. PCB.

# List of figures

| Figure 1 –  | Global total installed capacity 2000-20017 [1]                          | 14 |

|-------------|-------------------------------------------------------------------------|----|

| Figure 2 –  | Global annual installed capacity 2000-20017 [1]                         | 15 |

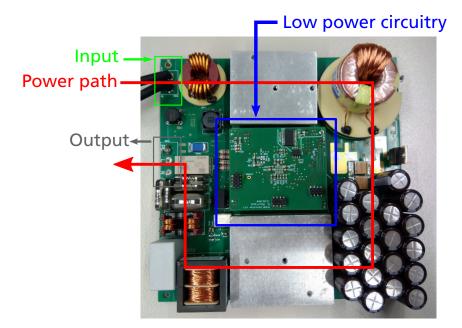

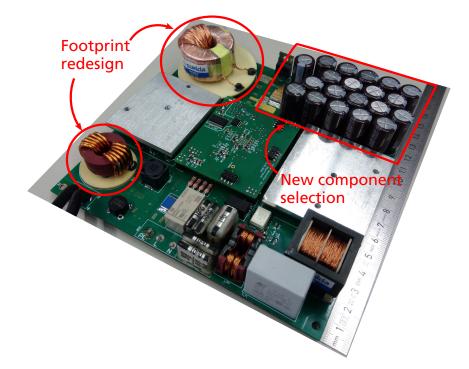

| Figure 3 –  | HiGaN v2.2 microinverter.                                               | 18 |

| Figure 4 –  | DC-DC Stage of the $HiGaN$ microinverter                                | 19 |

| Figure 5 –  | DC-AC Stage of the $HiGaN$ microinverter                                | 20 |

| Figure 6 –  | Simplified block diagram of the <i>HiGaN</i> microinverter              | 20 |

| Figure 7 –  | Power-to-weight and power-to-volume ratio microinverters rank           | 21 |

| Figure 8 –  | KMR210008A memory module [2].                                           | 24 |

| Figure 9 –  | MGJ1 5.7kVDC isolated 1 W gate drive DC-DC converter [3]                | 24 |

| Figure 10 – | Graphical representation of the PCB production process flow using the   |    |

|             | Ohmega Ply technology.                                                  | 26 |

| Figure 11 – | Parallel plate capacitor.                                               | 27 |

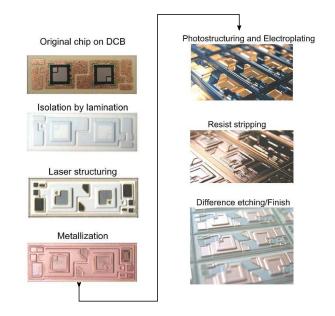

| Figure 12 – | EPC process flow [4]                                                    | 30 |

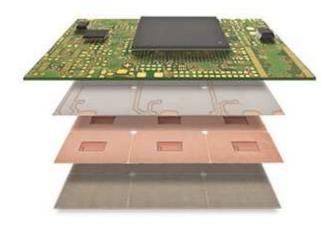

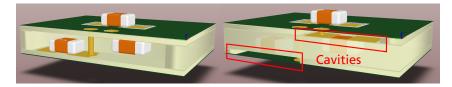

| Figure 13 – | Graphical representation of a PCB with two EPC cores and components     |    |

|             | assembled on the outer layers [5]                                       | 31 |

| Figure 14 – | Graphical representation of the cross section of a PCB using the Multi- |    |

|             | Mix technology [6]                                                      | 32 |

| Figure 15 – | IMB manufacturing process flow [7].                                     | 33 |

| Figure 16 – | Examples of manufacturing process flows offered by Amkor Technology     |    |

|             | [8]                                                                     | 33 |

| Figure 17 – | Process flow of the SiPLIT process applied in a thyristor module [9].   | 34 |

| Figure 18 – | Chip mounted to the interposer in one of the steps of manufacturing     |    |

|             | using the $i^2$ Board technology [10]                                   | 35 |

| Figure 19 – | Illustration of the $p^2$ Board technology process flow [10]            | 35 |

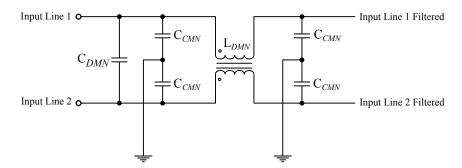

| Figure 20 – | Example of input EMI filter                                             | 38 |

| Figure 21 – | Power path in the $HiGaN$ v2.2.                                         | 47 |

| Figure 22 – | Examples of modifications in the current design to optimize space       | 49 |

| Figure 23 – | Comparison of possible DC link capacitors combination.                  | 49 |

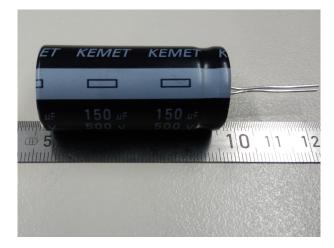

| Figure 24 – | KEMET ESG157M500AQ5AA 150 $\mu {\rm F}$ @500V 22 x 45 mm capacitor      | 50 |

| Figure 25 – | Areas in the current version of the design containing most of the com-  |    |

|             | ponents selected to be embedded                                         | 51 |

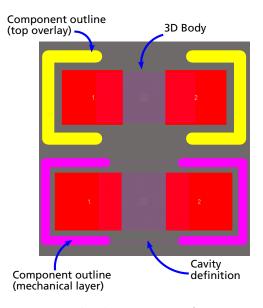

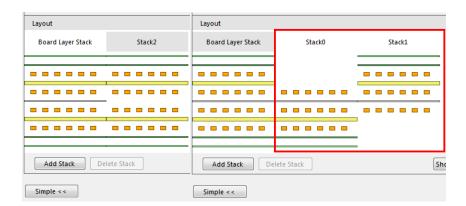

| Figure 26 – | Parameters to define a cavity in the Altium Region modification dialog. | 52 |

| Figure 27 – | Differences between standard component footprint and embedded com-      |    |

|             | ponent footprint.                                                       | 52 |

| Figure 28 – | Different alterations in the Altium Layer Stack Manager.                | 53 |

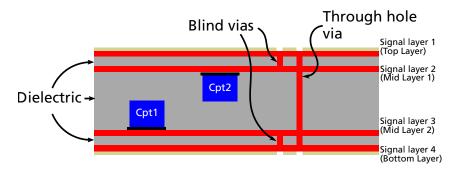

| Figure 29 – | Example of ECT layer stack                                                          | 54 |

|-------------|-------------------------------------------------------------------------------------|----|

| Figure 30 – | The effect of the footprint 3D body placement. Correct placement (left)             |    |

|             | and wrong placement (right).                                                        | 54 |

| Figure 31 – | Generated layer stacks for different 3D body placement. Correct layer               |    |

|             | stack (left) and incorrect layer stack (right). $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 54 |

| Figure 32 – | Size reduction approach used illustration                                           | 55 |

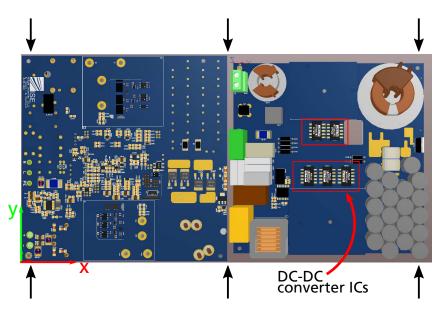

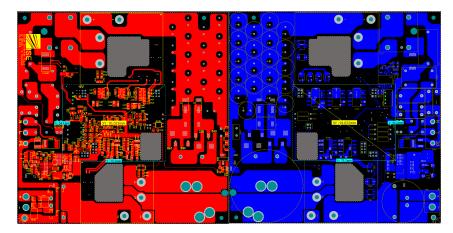

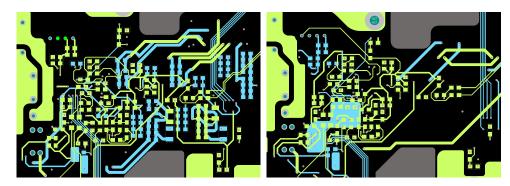

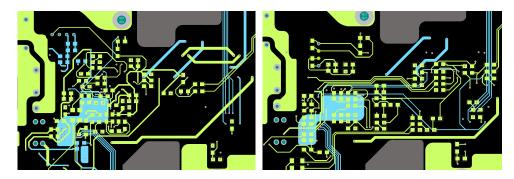

| Figure 33 – | HiGaN motherboard's central area. Left: top layer. Right: bottom layer.             | 56 |

| Figure 34 – | Controller module v2.1 (left) compared with Controller module v2.1.1                |    |

|             | (right)                                                                             | 59 |

| Figure 35 – | DC link capacitors submodule.                                                       | 62 |

| Figure 36 – | Space suitable for mounting the new microcontroller module defining                 |    |

|             | the design dimensions requirements                                                  | 62 |

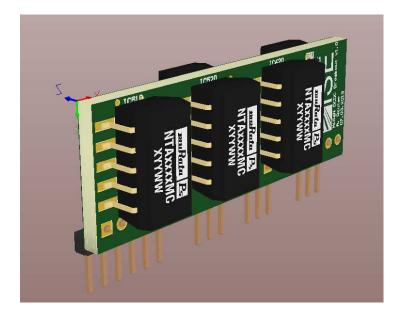

| Figure 37 – | HiGaN Controller v3.0                                                               | 63 |

| Figure 38 – | HiGaN v3.0.1.                                                                       | 64 |

| Figure 39 – | Empty areas in the $HiGaN$ v3.0.1.                                                  | 65 |

| Figure 40 – | HiGaN DCDC Breakout v0.2                                                            | 65 |

| Figure 41 – | HiGaN v3.0.2.                                                                       | 66 |

| Figure 42 – | Comparison between the inner layers of the $HiGaN$ versions 3.0.1 (left)            |    |

|             | and 3.0.2 (right)                                                                   | 67 |

| Figure 43 – | Comparison between the inner layers of the $HiGaN$ versions 3.0.2 (left)            |    |

|             | and 3.0.3 (right)                                                                   | 67 |

| Figure 44 – | Power sub modules. Input module (left) and output module (right)                    | 69 |

| Figure 45 – | HiGaN version 3.0.4                                                                 | 71 |

| Figure 46 – | HiGaN Controller v3.1                                                               | 72 |

| Figure 47 – | HiGaN DCDC Breakout v1.0                                                            | 73 |

| Figure 48 – | HiGaN version 3.0.5                                                                 | 73 |

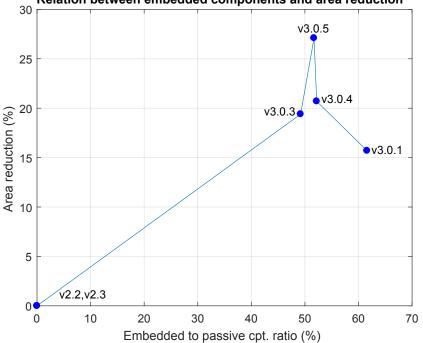

| Figure 49 – | Area reduction versus embedded components for all motherboard ver-                  |    |

|             | sions                                                                               | 76 |

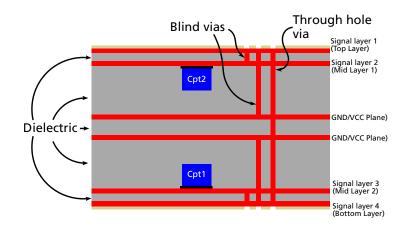

| Figure 50 – | Minimal layer stack in order to have embedded components above each                 |    |

|             | other                                                                               | 79 |

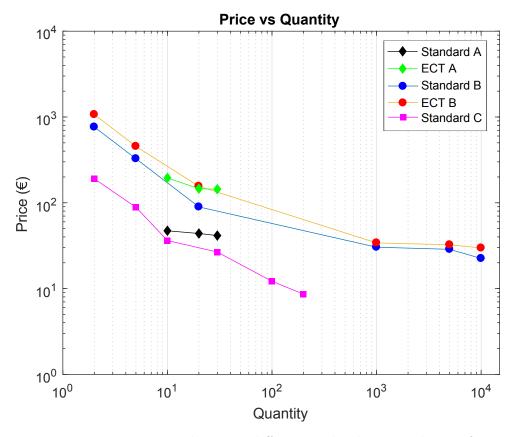

| Figure 51 – | Price comparison between different technologies and manufacturers                   | 80 |

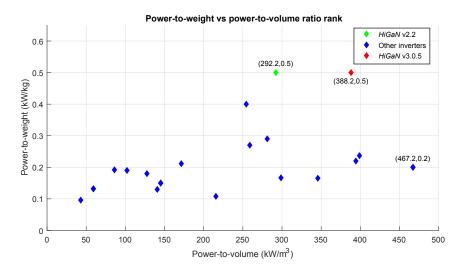

| Figure 52 – | Updated power-to-weight and power-to-volume ratio microinverters rank.              | 81 |

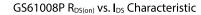

| Figure 53 – | GS61008P $R_{DSon}$ versus drain-to-source current for different junction           |    |

|             | temperatures [11]                                                                   | 84 |

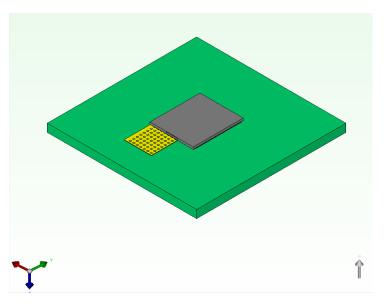

| Figure 54 – | Isometric view of the model in opposite direction to gravity. $\ldots$              | 87 |

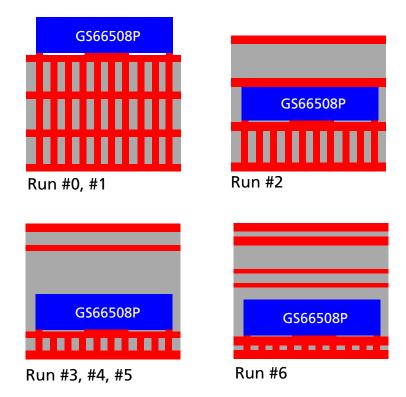

| Figure 55 – | Layer stack configurations used for each run of the simulation                      | 88 |

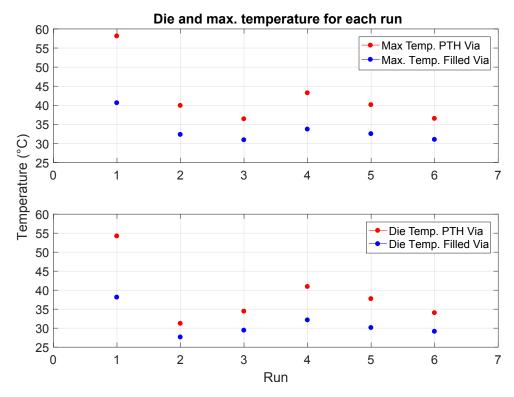

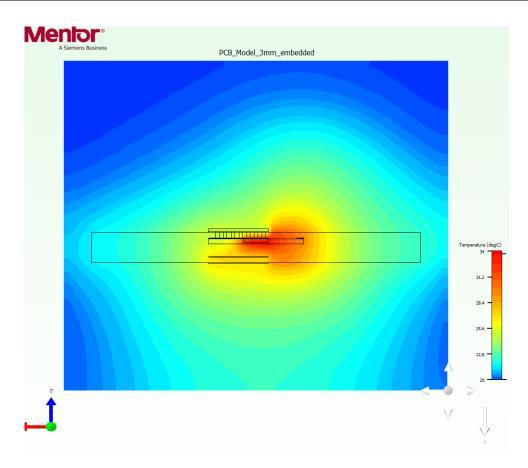

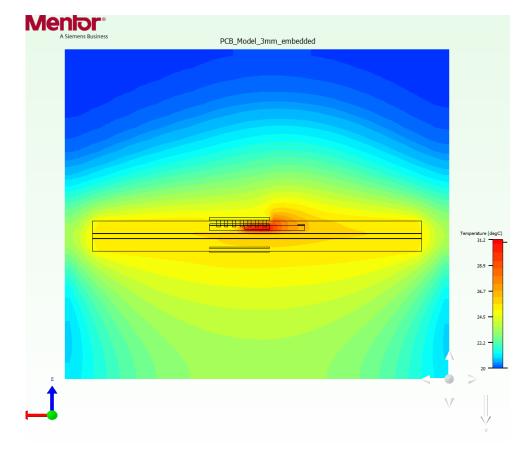

| Figure 56 – | Thermal simulation results plot                                                     | 90 |

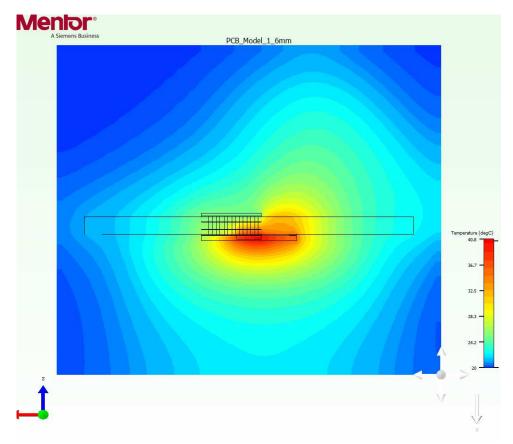

| Figure 57 – | Surface temperature plot in cross section for run 1                                 | 91 |

| Figure 58 – | Surface temperature plot in cross section for run 4                                 | 92 |

Figure 59 – Surface temperature plot in cross section for run 6. . . . . . . . . . . . 92

# List of tables

| Table 1 – I   | Final specifications of the $HiGaN$ prototype                              | 16 |

|---------------|----------------------------------------------------------------------------|----|

| Table 2 – I   | List of selected manufacturers and their capabilities                      | 58 |

| Table 3 – I   | Information on the components and size reduction of the $HiGaN$ v3.0.1.    | 64 |

| Table 4 – I   | Information on the components and size reduction of the $HiGaN$ v3.0.2.    | 66 |

| Table 5 – I   | Information on the components and size reduction of the $HiGaN$ v3.0.4.    | 71 |

| Table 6 $-$ 0 | Comparison of all boards designed and the original versions (mother-       |    |

| ł             | $\operatorname{poards}$ )                                                  | 74 |

| Table 7 $-$ 0 | Comparison of all boards designed and the original versions (modules).     | 75 |

| Table $8 - 0$ | Costs of the $HiGaN$ motherboard version 3.0.3 by different manufacturers. | 78 |

| Table 9 $-$ 0 | Costs of the $HiGaN$ motherboard version 2.3 by different manufacturers.   | 80 |

| Table 10 – M  | Model parameters for initial calculation                                   | 87 |

| Table 11 – M  | Material properties                                                        | 87 |

| Table 12 – I  | Parameters of each simulation run                                          | 88 |

| Table 13 – I  | Results for each run                                                       | 89 |

# Table of contents

| 1     | INTRODUCTION                                         | 14        |

|-------|------------------------------------------------------|-----------|

| 1.1   | Motivation and context                               | 14        |

| 1.2   | Objectives                                           | 18        |

| 1.3   | Presentation of the current prototype                | 18        |

| 2     | LITERATURE REVIEW                                    | 22        |

| 2.1   | Overview                                             | 22        |

| 2.2   | Examples and fields of application of the ECT        | 23        |

| 2.3   | Embedded formed components                           | 25        |

| 2.4   | Embedded Placed Components                           | 28        |

| 2.4.1 | AML Technology                                       | 29        |

| 2.4.2 | HERMES Project                                       | <b>29</b> |

| 2.4.3 | Multi-Mix                                            | 31        |

| 2.4.4 | IMB Technology                                       | 32        |

| 2.4.5 | Embedded Passives and Dies by Amkor                  | 32        |

| 2.4.6 | SiPLIT                                               | 33        |

| 2.4.7 | Schweizer's Technologies                             | <b>34</b> |

| 2.5   | Advantages of the ECT                                | 35        |

| 2.5.1 | Size reduction                                       | 36        |

| 2.5.2 | Improved Signal integrity                            | 36        |

| 2.5.3 | Improved EMI and EMC aspects                         | <b>37</b> |

| 2.5.4 | Protection against radiation                         | 39        |

| 2.5.5 | Improved Thermal management                          | 41        |

| 2.5.6 | Improved reliability                                 | 42        |

| 2.6   | Disadvantages                                        | 43        |

| 2.6.1 | Specific disadvantages of embedded formed components | 44        |

| 2.6.2 | Specific disadvantages of embedded placed components | 45        |

| 3     | DESIGN AND DEVELOPMENT METHODOLOGY FOR ECT           |           |

|       | APPLICATION                                          | 46        |

| 3.1   | Requirements for the new prototype                   | 46        |

| 3.1.1 | Use of same components                               | 46        |

| 3.1.2 | Power path                                           | 46        |

| 3.1.3 | Dimensions                                           | 47        |

| 3.1.4 | Embed only passive components                        | <b>47</b> |

| 3.1.5 | Embedding method to be used                                                             | <b>48</b> |

|-------|-----------------------------------------------------------------------------------------|-----------|

| 3.2   | Design workflow                                                                         | 48        |

| 3.2.1 | Optimization of the current design, without ECT                                         | 48        |

| 3.2.2 | Selection of components to be embedded                                                  | 50        |

| 3.2.3 | Altium Designer configurations                                                          | 51        |

| 3.2.4 | Size reduction approach                                                                 | 55        |

| 3.3   | Comparison and selection of PCB manufacturers                                           | 57        |

| 4     | RESULTS AND DISCUSSION                                                                  | 61        |

| 4.1   | HiGaN version 3.0.1                                                                     | 61        |

| 4.2   | HiGaN versions 3.0.2 and 3.0.3                                                          | <b>65</b> |

| 4.3   | HiGaN version 3.0.4                                                                     | 68        |

| 4.3.1 | The $HiGaN$ power sub modules $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 68        |

| 4.3.2 | The integration of the modules to the motherboard $\ldots$                              | 70        |

| 4.4   | HiGaN version 3.0.5                                                                     | 71        |

| 4.5   | Comparison of all the designs realized                                                  | <b>74</b> |

| 4.6   | Costs of the technology                                                                 | 77        |

| 5     | THERMAL BEHAVIOUR OF EMBEDDED POWER TRAN-                                               |           |

|       | SISTORS                                                                                 | 83        |

| 5.1   | Thermal simulation methodology                                                          | 85        |

| 5.1.1 | Thermal simulation results                                                              | 89        |

| 6     | CONCLUSIONS                                                                             | 93        |

| 6.1   | Final considerations                                                                    | 93        |

| 6.2   | Main contributions                                                                      | 95        |

| 6.3   | Future works                                                                            | 95        |

|       | REFERENCES                                                                              | 96        |

## 1 Introduction

### **1.1** Motivation and context

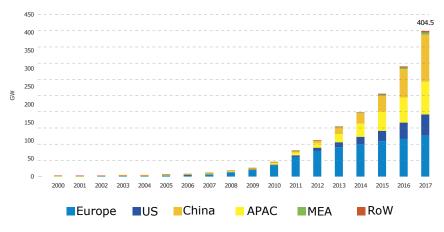

The renewable energy sector grows each year both in generation installed capacity and research and development of new technologies, especially the photovoltaic (PV) power generation branch. The total installed capacity raised 4300% in 2017 compared to 2007 and it is now 404.5 GW globally [1]. This remarkable expansion is leaded mostly by the Chinese market which in 2017 reached 32.3% of the total global share and the global forecast is very optimistic [1]. Figure 1 presents the evolution of the global total installed capacity since the beginning of the century. In Figure 1 *APAC* stands for Asia-Pacific excluding China; *MEA* stands for Middle East-Africa and *RoW* stands for rest of the world.

Figure 1 – Global total installed capacity 2000-20017 [1].

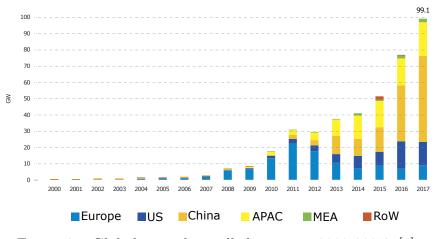

Besides the strong dominance of China and the Asia-Pacific region as a whole, the markets are expanding globally. In 2017 the EU market saw a 30% increase in yearly installed capacity compared to 2016, installing 9.2 GW and finally recovering from a five-year downturn. The EU bloc is still the second largest market. The US market, besides a slight decrease in yearly installed capacity still holds the third position and should be a strong market in the next years due to new legislation [1]. The Latin America market stood out in 2017 with Brazil installing for the first time over 1 GW in one year, although solar energy represents just 0.01% of the country's energy production [1][12]. Figure 2 presents the evolution of the global annual installed capacity. The acronyms are the same as in Figure 1.

Beyond the increasing installed capacity there is also the advance in research and development of the PV systems. The most significant issue with PV modules is the low efficiency, only between 14% and 18% though there are new technologies being developed

Figure 2 – Global annual installed capacity 2000-20017 [1].

in academic research [13][14][15] capable of reaching efficiencies of over 40% and even 50%. Despite the advances in the academia, the commercial available high efficiency modules aren't competitive enough yet, being more expensive and not providing expressive gains in efficiency [16]. It must be observed that the global efficiency of a PV system does not rely exclusively on the panel efficiency itself. One of the key components in a PV system are the power electronics systems (DC-DC and DC-AC converters) therefore the efficiency of such systems must be as high as possible.

In the inverters area (DC-AC converters), the microinverters, also referred as MLPE (Module Level Power Electronics) are rapidly gaining market share [17]. It is expected that the worldwide energy production by microinverters reach 2 GW in 2018 and the market value is projected to worth US\$ 990.3 million by 2022 [18][19].

Solar microinverters are power electronic devices that convert DC power from a low power source, such as a PV module to AC power and are commonly constituted of two stages: 1) a DC-DC boost converter to step up the input voltage and guarantee operation at a maximum power point and, in some cases, provide galvanic isolation, and 2) a DC-AC converter to finally deliver the AC power with acceptable index of energy quality to an appliance or directly to the grid [20]. These devices are commonly rated to handle the power of a single PV module and in a system using microinverters each PV module has its own converter [17].

There are many intrinsic advantages of using microinverters such as the reduction of mismatch losses and partial shading losses, more modularity and flexibility on system level, the possibility of module disconnection since they are isolated [21] and the possibility of having multiple panel types and different orientations in the same system [17]. Furthermore, moving from centralized inverters to microinverters is proven to result in higher harvested energy and longer lifetimes [22]. More importantly, in specific configurations, using microinverters could lead to overall system efficiency improvement and lower installation costs [23]. Microinverters are technically challenging systems due to high specific costs ( $\in$ /W) because of the low power processed (typically 250-400W); size and weight are critical because the installation is done beside or underneath the PV modules, thus requiring high power density PCBs (Printed Circuit Board) and the device have to be capable of operating in harsh environmental conditions (rain, dust, high and low temperature, etc.) [21]. Furthermore, the commercially available options still present high failure rates compared to centralized inverters [17].

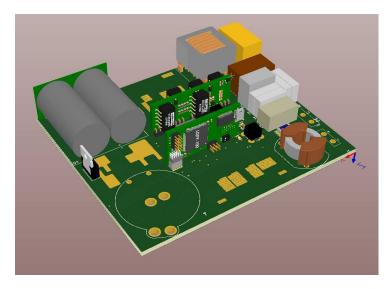

Considering the challenges cited above the HiGaN microinverter, a prototype of a microinverter was developed at the Fraunhofer ISE (Institute for Solar Energy systems), as part of an industrial project. The main objectives of the prototype are reduction in weight and volume compared to commercial available solutions as well as high efficiency, while evaluating the use of GaN (gallium nitride) transistors for this application. The particularity of this prototype is that it is capable of processing reactive power and it is galvanically isolated, which means that the DC link can be completely disconnected in case of e.g. fires or power outages. A galvanic isolation is particularly required in order for the device to be in compliance with new grid codes that are, for example, currently used in USA and Austria [21].

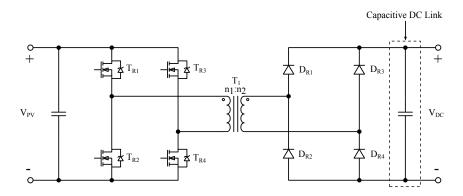

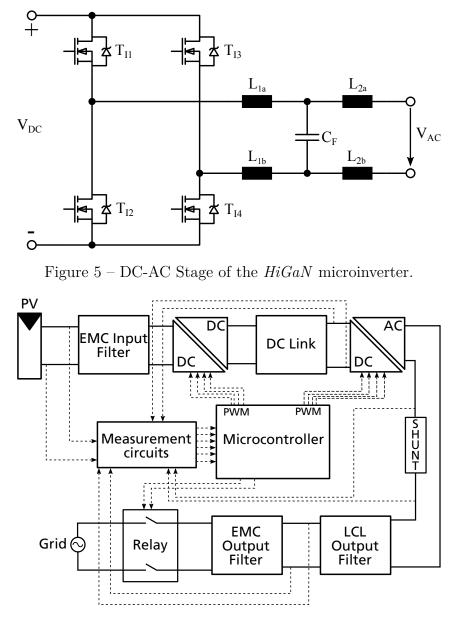

The inverter has two stages: an isolated DC-DC converter that uses a fullbridge pushpull topology with a fullbridge rectifier and a DC-AC converter based on a H4 bridge topology with a LCL output filter. The DC link between the two stages is only capacitive (refer to Section 1.3 and Figure 4 and Figure 5). The general specifications of the final prototype are presented in Table 1.

| Paramenter                   | Value               |

|------------------------------|---------------------|

| Input voltage                | 15-60 $V_{DC}$      |

| Output voltage               | $230 V_{AC}$        |

| DC-Link voltage              | $350-400 V_{DC}$    |

| Max. output Power            | 350W                |

| Max. efficiency whole system | 92.4%               |

| Switching frequency DC-DC    | $150 \mathrm{~kHz}$ |

| Switching frequency DC-AC    | $50 \mathrm{~kHz}$  |

| Dimensions                   | 150 x 150 x 30 mm   |

| Weight                       | 488 g               |

Table 1 – Final specifications of the HiGaN prototype

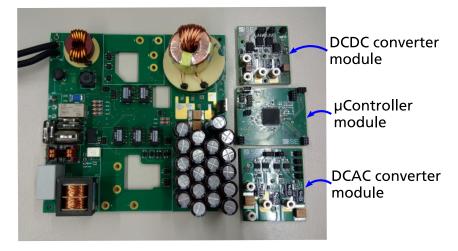

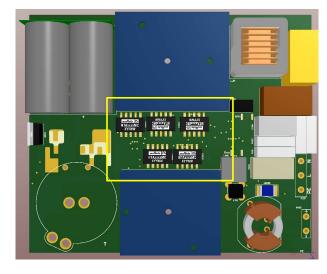

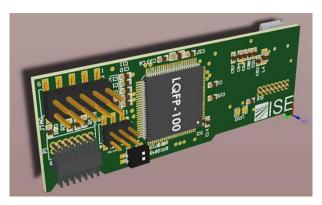

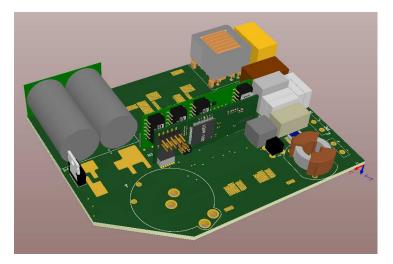

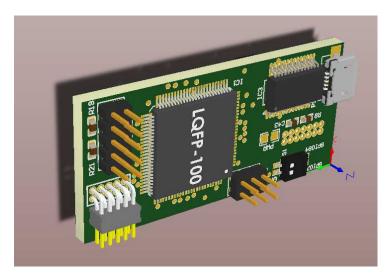

The HiGaN prototype is modular meaning that the power circuits (DC-DC and DC-AC converters) as well as the microcontroller circuit are built in separate PCBs and connected to the motherboard using header connectors.

As seeing in Table 1, the global efficiency of the inverter (considering the two stages and the auxiliary power supply) is 92.4% and is reached when the output power is approximately 150 W, without MPPT (Maximum Power Point Tracking). In order to achieve this efficiency some design and hardware choices are worth to be noted. The key component used in both power stages are the high efficiency and very low gate on resistance GaN (gallium nitride) transistors. Also, the rectifier is built using SiC (silicon carbide) diodes, which are also very efficient. The modulation technique used is bipolar PWM and the switching frequencies used are 150 kHz for the DC-DC converter and 50 kHz for the DC-AC converter. A higher switching frequency is used in the DC-DC converter in order to reduce the size of the transformer.

The current version of the prototype fulfilled the requirements of the project and showed good results in the conducted tests. Nonetheless, the prototype could be improved in some aspects. There were some issues with the thermal performance, especially with the power transistors reaching high temperatures. The efficiency could be improved as well. But the most important improvement to be made is size reduction. As mentioned the production cost of microinverters are high (especially if GaN transistors are used), therefore the cost per volume and cost per weight has to be as small as possible in order for the device to be more commercially attractive.

Size reduction in PCBs can be achieved by various different ways, mainly by layout optimization, of course, by combining different functions and components or using smaller component packages. Another way to reduce the PCB size is to use different fabrication technologies. One option suited for this purpose is the ECT (Embedded Component Technology) which is a type of PCB manufacturing technology known and used through more than thirty years. In this technology the passive and/or active components are embedded in the PCB substrate, meaning that the components are buried inside the core material of the PCB.

Nowadays there are a variety of methods to embed components and, independently of the method used, the ECT can deliver very desirable features. Some electronics manufacturers such as Motorola and Nortel have reported size reductions of 40% up to 50% respectively and some even reported costs reductions of 14% (Motorola) up to 40% (Inboard) [24]. Besides size reduction, there are other benefits in using ECT, such as reliability improvement since the components are inside the PCB substrate, therefore more protected from the environment and the mechanical stresses; faster signal speed due to component proximity; signal integrity is raised and interferences reduced; design is also improved as the components are integrated to the PCB, parasitic losses can be minimized mainly in high frequency applications [24].

It must be noted that the ECT has been successfully applied in many fields of the electronic industry, mainly in consumer electronics [2], as well as in more critical application like military and aerospace [25][26]. However, the use of this technology in power electronics has yet to be fully investigated and therefore the effects, advantages and disadvantages can be different compared with other field of applications.

### 1.2 Objectives

Considering the motivation and context exposed the objectives of this thesis are:

- 1. Review the current state of the art of the ECT as well as comparing different methods and techniques.

- 2. Develop a design process for PCBs with ECT.

- 3. Develop and design a more compact version on the HiGaN prototype using the ECT.

- 4. Investigate the use of the ECT specifically for power electronics.

- 5. Deepen the knowledge in advanced PCB manufacturing technologies and high efficient microinverters and components.

### **1.3** Presentation of the current prototype

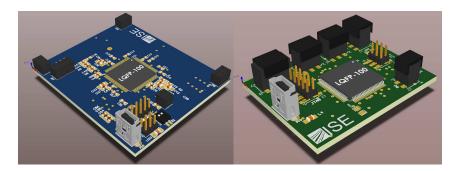

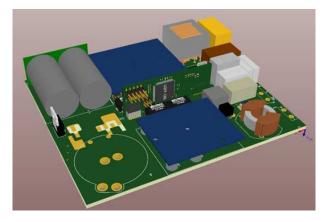

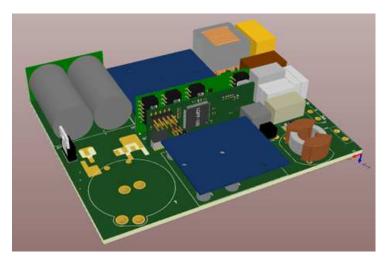

The *HiGaN* prototype, current version 2.2, which is the starting point of this project, is a galvanically isolated two stage single phase microinverter rated for maximum power output of 350 W. The two stages consists of a) a DC-DC converter stage to boost up to the required DC link voltage and galvanically isolate the inverter and b) an inverter stage that feed the energy to the public grid. One of the advantages of this concept is that the MPP (Maximum Power Point) tracking can be realized independently from the control loop of the grid [21]. A picture of the version 2.2 of the prototype with a description of the modules can be seen in Figure 3.

Figure 3 – *HiGaN* v2.2 microinverter.

The DC-DC converter stage circuit schematic can be seen in Figure 4 and can be separated in two parts the primary and the secondary. The primary side (input side,  $V_{PV}$ ) is a fullbridge push-pull converter. Using this topology the transformer is simpler, the transistor blocking voltage is lower and the overall efficiency is higher compared to other boost converter topologies. GaN transistors are used in the converter, which present very low switching losses (compared to Si devices), therefore a higher switching frequency can be used and thus the size of the transformer is reduced. It is advantageous to use WBG (Wide Bandgap) devices such as GaN or SiC instead of Si switches due to their better switching characteristics which leads to less losses and overall increased efficiency[27].

Figure 4 – DC-DC Stage of the *HiGaN* microinverter.

In the secondary part there is a fullbridge rectifier using SiC diodes that are also more efficient than the Si counterparts and the topology grants a more simpler transformer, a lower diode blocking voltage and a lower diode current consumption hence a higher overall efficiency. The DC link is capacitive and acts as an energy buffer and a 100 Hz ripple filter.

The DC-AC or inverter stage circuit schematic can be seen in Figure 5. The topology used is a H4 bridge with a LCL output filter and in this stage the GaN transistors are also used. This topology is classical and it is one of the most commonly used in commercial inverters. The switching strategy used is bipolar PWM for both the DC-DC and DC-AC stages due to the parasitic capacitance of the PV module [21].

To have a global overview on the functioning of the prototype a simplified block diagram is seen in Figure 6.

The overall specifications are seen in Table 1. The LCL output filter is further hybridized with the EMC output filter which reduces the size of the filter inductors used. The output of the HiGaN also contains a grid disconnection system with an electromechanical relay, as seen in Figure 6, therefore the microinverter can be fully isolated from the grid.

As seen in Table 1 the maximum output efficiency is high. The DC-DC stage maximum efficiency was 97.7% and the DC-AC stage maximum output efficiency was 98.5%. Although the efficiency could be increased by improving the auxiliary power supply circuit and the microcontroller power consumption should be reduced. Unipolar switching

Figure 6 – Simplified block diagram of the *HiGaN* microinverter.

strategy and bootstrapping circuit could also be implemented in order to achieve higher efficiency in the DC-AC stage.

One of the issues with the final demonstrator built is thermal management, mainly in the DC-DC module. Measurements using infrared thermography conducted during test phases showed that, for a power output of 250 W, the junction temperature of the transistors in the DC-DC module was approximately 85 °C and for a power output of 350 W the temperature was 110 °C, being already close to the maximum junction temperature of the GaN transistors used (150 °C). This operation temperatures can significantly reduce the lifetime and affect the efficiency of the device. One of the reasons why the thermal performance is not optimal is because the board is passive cooled to reduce the volume of the final product, therefore the cooling strategy could be improved.

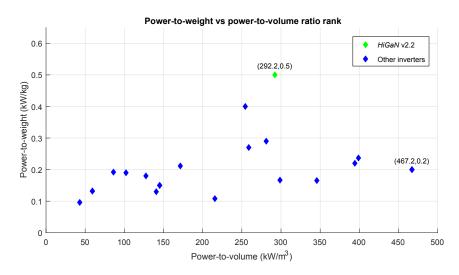

The final external dimensions and weight are 185 x 185 x 35 mm and 0.7 kg respectively

(PCB plus the case developed for the demonstrator). If compared to commercial available microinverters, the HiGaN project can be considered a competitive solution in terms of power to weight ratio (W/kg) (Figure 7) although outperformed by other microinverters in terms of power to volume ratio (W/m<sup>3</sup>) (Figure 7). Nevertheless the prototype is galvanically isolated and can process reactive power, capabilities that aren't commonly available. It is also worth to note that some of the microinverters in the comparison process power in the range of kW.

Figure 7 – Power-to-weight and power-to-volume ratio microinverters rank.

From Figure 7 it is clear that reducing the size of the inverter would substantially increase the commercial competitiveness since using WBG (Wide Band-gap) devices such as the GaN transistors is still very expensive, but if the device developed compensates for the extra cost being extremely compact and efficient it could be more easily accepted in the market. This means, essentially, that a displacement in the X-axis is already enough.

## 2 Literature review

### 2.1 Overview

The embedded components technology (ECT) is an advanced printed circuit board (PCB) manufacturing technology applied and used by the industry through more than thirty years [24]. The development of this technology was initiated with the goal to have smaller and lighter products with the same or lower costs and to add functionality and value to the PCBs. As the consumer electronics industry refined the process of embedding components throughout the years and the products realized started to be more reliable and with increased quality, sectors with critical and specific applications such as automotive, aerospace, communications and military begun to use this technology [26].

The usage of this technology started in in the late '70s by hybrid PCBs (PCBs composed by both organic and inorganic materials) manufacturers. Initially only passive components were embedded to the PCB substrate. Passive components being components that do not cause a gain neither in voltage nor current in the circuit [28]. In the '90s the AML technology patented by Hoffman Leiterplaten GmbH and the SIMOV by Siemens AG enabled the embedding of active components and semiconductors packages in organic substrates [25]. The Japanese market was one of the first to witness large scale productions of devices using ECT with Murata Manufacturing in 1997 shipping antenna switching modules using the technology [24]. In parallel, the advances in packaging technologies that, combined with the ECT, started to increase the range of solutions for designers and electronics manufacturers [5]. The production of devices with embedded passives rapidly increased due to the series of advantages provided by such manufacturing process, but the technology usage stagnated in the last ten years mostly due to the lack of incentive coming from the manufacturers.

Despite the constant decrease in consumption of passive devices in the past seven years mainly in the consumer market (namely the largest market) [29] and the global trend towards the so called SiP (system in package) market, the amount of passive components in PCBs is still huge and certainly much greater than when the ECT was being first explored. This is one of the factors that kept the ECT as an economical attractive technology during the recent evolutions of electronics devices. Generally speaking, the demand for passive components usually increases proportionally with the power installed on the boards. Therefore, as a high component count demands more space on the PCBs, embedding passives is very attractive to the manufacturers in order to keep devices with a small form factor. This is particularly important in the mobile segment, one of the markets that witness constant growth [29], but also in industrial and specialty segments like renewable energy, medical, aerospace and military applications.

Embedding passive components seems to be attractive due to the passive/active components ratio in PCBs, however this ratio is decreasing gradually over the years and although more expensive, more and more in-chip solutions are developed. It is important to note the constant global decline of the PCB industry in the last 20 years and in the opposite side the constant growth of the semiconductors industry with the yearly revenue of this branch being over four times the PCB branch [25]. This is one of the reasons why the ECT may not be as attractive to large scale consumer electronics since this segment is looking for the desired embedded solutions directly in package or SiP technologies. On the other hand, specialty segments (military, aerospace, medical, etc.) have a fair smaller demand of PCBs and generally needs that are not attractive for semiconductors manufacturers to fulfill since the start-up costs are too high for small to medium scale production and generally the solutions required are much more complex, thus this segments can take advantage of the ECT.

The ECT could drive the evolution of PCB manufacturing towards the next level of miniaturization with the board being faced as one large component and thus leading to solutions where the final product is capable of handling all sorts of conditions while having the desired features. The industry is taking advantage of the ECT not only for miniaturization but also for delivering new capabilities on the products with the same or small form factors [30]. Therefore, the limits and constraints of the technology as well as how it can be used to fulfill the requirements of the design in the most optimized way must be investigated and documented.

The IPC standard IPC-7092 - Design and Assembly Process Implementation for Embedded Components offers guidance for designers and manufacturers describing the different techniques and challenges of the technology. However, it doesn't standardize a unique methodology nor design rules enabling the existence of multiple methods of manufacturing and consequently different requirements and particularities requiring designers to deeply understand about PCB manufacturing.

The ECT can be divided in embedded formed components and embedded discrete components. Each method is distinct in the manufacturing process and the final properties of the PCB and it is up to the designer to choose which method to use depending on manufacturers capabilities and desired features or requirements of the project.

## 2.2 Examples and fields of application of the ECT

As a manufacturing technique, theoretically, the ECT could be applied in any PCB. As described earlier, this technology started its evolution in the area of consumer electronics. In fact nowadays it is most predominantly used in the smartphone industry where the companies have developed their own methods of fabrication and the use of ECT is well justified since the PCBs used in such application have high component density and must accommodate a great amount of functionality in a small form factor. The company Samsung, currently the worldwide smartphone sales leader [31], uses very advanced embedded components solutions and since 2015 is selling memory modules using PoP (Package on Package) technology [2]. In a single package a 3 GB DDR3 RAM memory, 32 GB eMMC (embedded multimedia card) and a controller are integrated with the external dimensions being only 15 x 15 mm and the estimated area savings compared to standard solutions are up 40% [2]. Figure 8 presents the KMR210008A memory module which is one of the commercial available modules using ECT.

Figure 8 – KMR210008A memory module [2].

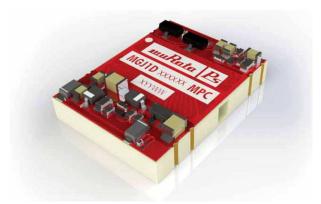

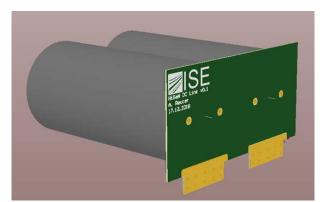

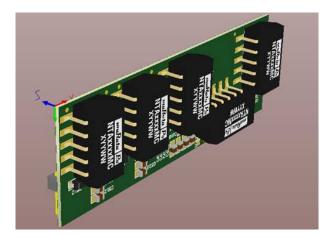

The ECT is also applied in very critical applications such as radar modules and military communication equipment [32] [33]. Another area where high reliability is required is in powering transistors gate drivers and a good example is provided by the company Murata with the MGJ1 Series which is a highly compact isolated DC-DC converter and has embedded, among other components, the isolation transformer. The module is seen in Figure 9, the dimensions are 20 x 15 mm which makes for one of the smallest modules with the same parameters in the market.

Figure 9 – MGJ1 5.7kVDC isolated 1 W gate drive DC-DC converter [3].

In the power electronics field however there aren't many applications examples of standalone ECT. Instead, in this field, the integration is generally tied with the use of different substrates such as in the case of the SiPLIT technology for example [9] or as presented by Charboneau et al. where power MOSFETS are integrated in a ceramic substrate to evaluate properties of different liquid cooling methods [34]. One good example is described by Biela, et al. where a higher power density is achieved in a EMI filter but there is also use of ferritic layers [35]. The integration of power devices is also described by Schindler, et al., again to evaluate liquid cooling solutions [36].

One industry that started to take advantage of embedding power devices is the automotive with the increasing need of miniaturization and the rise of electric vehicles. Ostmann, et al. describes a new embedding process as well as its application on high power inverter applicable in a hybrid vehicle [37]. Also, Al et al. shows the development of a embedded die packaging technology specifically for power devices applied directly to the automotive industry [38].

## 2.3 Embedded formed components

The ECT can be separated into two main methods: embedded formed components and embedded placed components. Embedding formed components means that the components are formed during the fabrication of the board, in other words, the components are manufactured together with the PCB. This method is well established and there are a great number of different techniques to achieve it. Formed components are attractive due to mass production cost reduction compared to standard PCB manufacturing and this method offers the least level of risk, although the tolerances and components value range are limited and stability over time is a concerning point. Another point to be noted in the manufacturing level is that manufacturers of standard multilayer PCBs are capable of using this technique without greater further investments.

Forming components is the oldest ECT method and its first use was in hybrid PCBs as mentioned previously. This method literally prints the component inside the PCB substrate using a variety of techniques. It is used only for embedding passive components since forming semiconductors is too expensive and complex and does not provide good results. The fabricator manufactures the component in the primary interconnect substrate and the formed components are made from raw materials at same time as the board [28].

For both resistors and capacitors, different materials can be used like ink formulations, copper foil based materials, dielectric composites as well as various deposition and curing processes namely screen printing, sputtering, ink jet printing, electroless copper deposition, among others [39][24].

The process of forming can be subtractive or additive. In the subtractive process a layer of the material that composes the component to be formed is deposited over the whole surface of the board, then a chemical etching or mechanical removing method is used to shape the components in their precise locations, this method of forming components is also known as thin film technology.

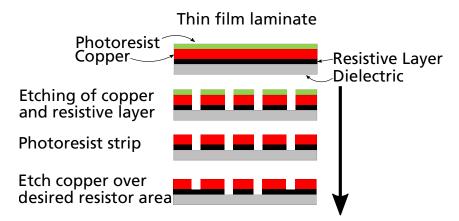

One good example of subtractive process is the OhmegaPly formed resistors developed in 1970. In this technology a 0.1 to 0.4  $\mu$ m layer of NiP (nickel-phosphorous) is electroplated over a standard thickness copper foil, this results in a composite called RCM (Resistive Conductive Material). Then the RCM is laminated upside down on the polymer base, usually FR-4, this results in the OhmegaPly Laminate. Finally, the resistor is realized through subtractive means and if done by etching, both the copper and the resistive material can be etched depending on the chemical used in the process [24][40]. Figure 10 presents the Ohmega Ply process flow.

Figure 10 – Graphical representation of the PCB production process flow using the Ohmega Ply technology.

The process is composed of two standard print and three etch cycles. The first step is to apply a photoresist to the OhmegaPly laminate. The second step is the first print and consists of developing the composite image. The third step is the first etching process and this removes the unwanted copper. The fourth step is the second etch and removes the unwanted resistive areas. One can use an etching chemical to remove both resistive material and copper in a single step. The fifth step is to strip the photoresist leading to the sixth step that is applying a new photoresist to print the conductor protective image, being the second print. The seventh step is the third and final etch and consists of selectively removing the copper over the designed area of the resistor. The eighth and final step is to strip away the photoresist [41].

The maximum resistance reliably achievable with the OhmegaPly method is  $250 \ \Omega/in^2$ . There are other thin film technologies that uses the same process flow but with minor differences like other plating methods such as electroless selective plating (M-Pass) or other resistive materials like doped platinum or NiCr [24].

To form capacitors the process is essentially the same changing only the material and the thickness. Essentially what is being produced is a parallel plate capacitor as in Figure 11, and the capacitance of such capacitor is given by Equation 2.1.

$$C = \frac{\epsilon_0 \cdot \epsilon_r \cdot L \cdot W}{d}$$

$$W \int_{C}^{VCC} \underbrace{Dielectric}_{E_r}$$

$$E_r$$

Figure 11 – Parallel plate capacitor.

This way the capacitance value C is inversely proportional to d that is the distance between plates or in this case the thickness of the dielectric material layer, and directly proportional to the permittivity of the material ( $\epsilon_0$ ,  $\epsilon_r$ ) and the length and width (L, W) of the printed capacitor.

There are a variety of materials to laminate capacitors ranging from barium-titanite to epoxy matrix based materials. Basically, to achieve higher capacitance, thinner layers or higher permittivities are desired since increasing the overall dimensions has no point if the purpose of embedding components is to reduce space.

The additive technology performs the opposite of the subtractive technology, the material is precisely added directly on the required position. To form components the material can be made of organic or inorganic pastes and it is deposited as a thick layer (> 1 $\mu$ m) thus this method is also known as thick film technology. The pastes are added to the substrate and then thermally treated or cured (usually in a conveyor belt furnace at a temperature of 850 °C). The most common method of depositing the pastes is screen printing [24] [42].

Usually thick film components are used with ceramic substrates. For resistors to be printed in copper foils usually the material used is lanthanum-boride and for capacitors the pastes are based on  $BaTiO_3$ . The manufacturing process uses prefabricated copper foils with the attached components and laminates this foils with prepress, like the standard procedure for manufacturing multilayer boards [24].

One critical step in the manufacturing of thick film components is the adhesion of the paste to the copper foil. Usually to increase the reliability of the adhesion the copper foils are coated with a copper/glass thermally cured ink [24]. This ink cures at a much lower temperature but this pre-thermal treatment/cure provides a better surface for depositing the pastes and avoids high shrinkage of the copper during the cure of the pastes thus increasing the component adhesion.

This method provides a maximum resistance of 10 k $\Omega/in^2$  and usually in the range of 100  $pF/mm^2$  for capacitors.

(2.1)

In general terms the embedded formed components method is cheaper compared to other methods and its usage is widely accepted in the industry of PCB manufacturing mainly because of its main strong point that is the reliability. Industrial reports states formed components being used in highly critical application without failure [24] and tests in extreme conditions with resistance changes of only 1% [40]. Another interesting advantage is the possibility to make components in custom shapes to achieve different objectives such as better thermal performance or EMI reduction. From a manufacturer point of view this method demands considerably low investments since the process of embedding does not require different types of machinery other than those used in the standard manufacturing procedures, in other words, the components are fabricated alongside the board.

One of the weaknesses of this method is the components tolerances, generally being between 15% and 30% which for the majority of modern applications is not suitable. This happens because the values of the components relies almost exclusively in the final dimensions. Therefore, minimal errors in the manufacturing process results in a large inaccuracy in the components values. Tighter tolerances are achievable using laser trimming but this incurs in higher production costs and times.

Formed components are mainly applied in high frequency circuits and products that doesn't require tight tolerances but work in harsh environmental conditions.

### 2.4 Embedded Placed Components

Embedding placed components is a newer technique compared to embedded formed components, however the first attempts of integrating bare dies in the substrate date back to the mid '80s [8]. This methodology uses discrete components which can be understood as components in standard SMT/SMD packages, including active components as well and bare dies. The technology is also known as 3D packaging and the development began from the need of more functionality in the same or less space therefore the main focus was in embedding semiconductors [25][6].

This method requires manufacturers to change their production workflow since manufacturing and assembly are done together. As discrete standard components are being embedded the tolerances and stability are not a concern but the manufacturing process could subject components to conditions that may result in physical damage [39]. Although SMD packages are becoming smaller each year, embedding certain components like larger values capacitors could lead to thicker PCBs [43].

Throughout the years many were the methods developed for embedding placed components. Following, an overview of some patented methods available in the market is presented.

### 2.4.1 AML Technology

Developed by the company Hofmann Leiterplatten, is the first patent of embedded placed components, filled in 1996 and granted to the company in 2004. The process is named AML (Advance Multi Layer) and was the base for other methods.

The patent DE 19627543 describes the basic process flow. The substrate of the board includes multiple surface insulation layers connected with at least one of the inner insulation layers as a distance frame with a window (cavity) where the component is placed and both sides of the window are closed by further layers whose thickness equals at least the height of the component. The contact faces/conductive tracks (copper layers) are on at least one substrate face side and between the insulation layers. It is also described that the prepreg has special cavities that are used as a separator (the spacer prepregs) between the layers of the PCB enabling the manufacturers to use standard technologies without damaging sensitive components during lamination and pressing [33]. In the fabrication, the components are placed on an inner layer and the connection between the components and the layer is made using different methods according to the designer needs or manufacturing capabilities.

The process is very much like standard multilayer PCB manufacturing with the difference of the added windows in the prepress and isolation layers. Basically the groundbreaking invention or method is how to fill this window or cavity correctly. This specific window technology is used in order to have a stress free embedding of different components/packages in one single press operation. The resin flow as well as the correct resin composition along with the correct opening in the spacer prepreg will fully and safely embed the components [33].

Some attempts of standardization of embedded components techniques entered in conflict with the AML patent, like the attempt of the Japanese JPCA-EB01 that describes a similar process flow and therefore could not be accepted neither by the IEC nor ISO. The standard IPC-7092 is in accordance with the patent regulations and there are specific instructions to negotiate licenses with the company in order not to have patent infringement issues [33].

#### 2.4.2 HERMES Project

In 2008 an EU funded industry and academia consortia, the HERMES project (High density integration by Embedding chips for Reduced size Modules and Electronic Systems) was started. This consortia consisted of eleven partners from PCB design and fabrication industries and applied research and academic institutions and was the successor of the HIDING Dies project that was responsible for developing the technology used by the HERMES project. The main objective was to industrialize a new method of embedding active and passive devices. The company that coordinated the project was AT&S and the

project lasted until 2012. The main result of the project was a method of embedding that has both the acceptance of the industry and academia because of improved properties, cost effectiveness and added value [44].

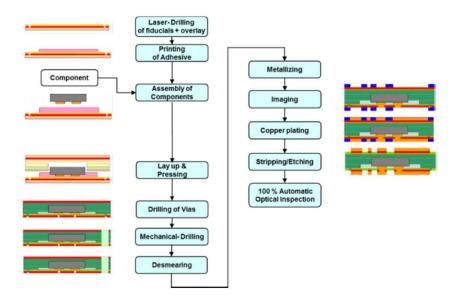

The technology developed is named ECP (Embedded Components Packaging, patent of the company AT&S) being essentially a laminate-based chip embedding technology that uses core principles of PCB manufacturing. It is a fusion of HDI (High Density Integration/Interconnections) technology, ultra-fine line technology based on a semi-additive technology and a component assembly technology adapted for discrete passive and modified active components [4].

In regular PCB manufacturing the process flow is usually called chip last, meaning that the components placement and assembly is accomplished after the board is completed. The ECP technology is a chip first method in which the chip/component is embedded first in a PCB creating an embedded core that can be built in a multilayer board [4].

The first step of the process is to laser cut registration marks in the ultra-thin copper foil that will be used as guides in the component placement step. The second step is to print conductive adhesive material in the copper foil and then the discrete components are placed face down in the adhesive. The adhesive is cured for a solid bond between the component and the copper foil in order for the components not to move in the following steps [39][5][4].

Figure 12 – EPC process flow [4].

The third step is the lamination process. The copper foil with the components firmly bounded by the cured adhesive, the FR-4 prepress with openings corresponding to the components areas, a regular prepres without openings serving as a distance frame and a further copper foil are laminated together in a single press cycle. This creates the embedded core. Then via holes are laser drilled and cleaned followed by electroless copper plating. After that a photoresist is applied using the modified semi-additive process followed by the imaging of the copper pattern. The process is called semi-additive because the exposed copper areas by the photoresist are built by galvanic plating and after the photoresist stripping the remaining copper is removed by flash etching [39][4]. The process steps are seeing in Figure 12.

Figure 13 – Graphical representation of a PCB with two EPC cores and components assembled on the outer layers [5].

After all the steps the core pass through an automated optical inspection. It is possible to manufacture a PCB with multiple ECP cores due to the fact that the core can now be viewed as a layer in a multilayer PCB. The restriction is the interconnection between cores that must be made using micro vias and galvanic via plating which can be quite challenging requiring new plating concepts and equipment [4]. Figure 13 presents an example of PCB with more than one EPC core.

The components can also be placed facing up and this creates a distinct way of interconnecting the embedded components with the outer layers and therefore different characteristics from the face-down method described. The face-up approach offers good thermal properties being suited for power components embedding. In the other hand, since components have different thickness, the dielectric thickness will not be constant as well, and this could make the subsequent via drilling and plating process more complex [5].

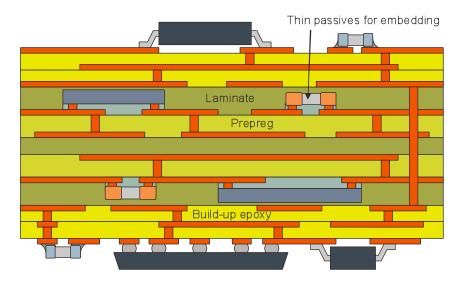

#### 2.4.3 Multi-Mix

Patented by Crane Aerospace and Electronics, this process is for fusing microwave multilayer integrated circuits and what the company calls micro-multifunctional modules. The technology is based on fluoropolymer composite substrates, which are bonded together into a multilayer structure using a fusion bonding process allowing the integration of active and passive functions into self-contained modules [32]. This yields to embedded EMI shielding and the PCB itself is a package unit, in most cases even dispensing the usage of an enclosure.

Figure 14 – Graphical representation of the cross section of a PCB using the Multi-Mix technology [6].

The bonding process embeds not only the active components but the passives as well and it even can be used in configurations with formed components. The main advantage of this process is the elimination of the prepress as can be seeing in Figure 14[6]. The result is a low profile and light weight PCB and the process itself allows for a low cost approach and reduced engineering cycles. This technology is manly suited for highly critical applications such as radars and satellites due to the high reliability and performance [32].

#### 2.4.4 IMB Technology

The Integrated Module Board (IMB) patented by Imbera Electronics is an laminated embedding technology feasible for low- to mid-range I/O count components. The process started development in 1997 at the Helsinki University of Technology [7]. The process itself is very similar to the EPC process described earlier, as is possible to see in Figure 15. The main difference is that the EPC uses ultra-thin copper foil. The IMB process is more focused in the integration of whole systems in the PCB the so called SiB (Systems in Board) and SiP (System in Package) and also BGA (Ball Grid Arrays) packages, and is applicable in many areas.

#### 2.4.5 Embedded Passives and Dies by Amkor

Amkor Technology is also in the embedding market. The company offers embedding in FO-WLP (Fan-Out Wafer Level Packaging) or die-first process. The first step is to

Figure 15 – IMB manufacturing process flow [7].

place a singulated die on a wafer carrier. After that the package infrastructure is built around the die to create a reconstitute molded wafer thus eliminating the need for die attach reflow [8].

Other process are offered such as die embedded in laminate (EPC-like process, or diefirst/mid [8]) and the modular embedding, or die-last. In this process flow the top and bottom substrates are prefabricated so the die can be embedded as one of the final process steps. It is also described a process called PoP (Package on Package) where the process flows described can be used to stack packages to create high density I/O [8]. Figure 16 shows samples of each process.

Figure 16 – Examples of manufacturing process flows offered by Amkor Technology [8].

#### 2.4.6 SiPLIT

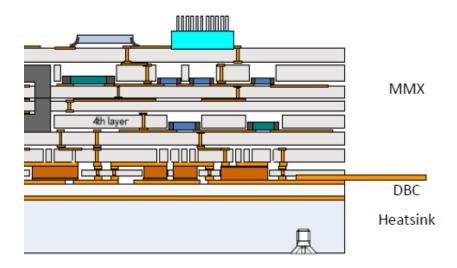

The SiPLIT (Siemens Planar Interconnect Technology) patented by Siemens is another embedding in laminate process. This technology was developed mainly focusing in power modules systems integration specifically trying to create a better solution than the thick aluminum wire bonds commonly used in power modules packages [9].

The process can use solder, silver sintering or conductive adhesives to attach the dies in the substrate that can be either organic or inorganic (DCB (Direct Copper Bonding) with ceramic substrates). The entire structure (substrate with the dies attached) is covered by a soft epoxy-based insulation film and laminated using vacuum press. After that the contact areas are ablated in the surface of the chip and the substrate using high power pulsed laser, similarly with the ECP process. A sputtered seed layer (photoresist) is then used as a metallization base for the subsequent photo-structuring process. In this step the interconnects are defined according with the layout. Then, like in the EPC process, copper is deposited galvanically and in the final step the seed layer is stripped by chemical etching [9]. The described process flow can be seeing in Figure 17.

Figure 17 – Process flow of the SiPLIT process applied in a thyristor module [9].

With this process it is possible to use chips with thickness up to  $700\mu$ m. Since the DCBs have larger cross sections and better heat conductivity as well as smaller heat expansion coefficients it is possible to integrate high power demand circuits such as rectifiers and inverters.

### 2.4.7 Schweizer's Technologies

Schweizer AG offers some interesting patented embedding technologies. The  $i^2$ Board (Integrated Interposer Board) is the company's solution for logic components embedding. Essentially the connections with the semiconductor are made directly to the interposer and it is basically a flip-chip method. This technology allows embedding of both passive and active components and is suitable for logic circuits typically with high I/O counts, although it can be used in a variety of applications since a power dissipation of up to 10W is possible [10]. Figure 18 shows one of the steps of fabrication where the chip is already mounted to the interposer.

The  $p^2$ Pack is the company's solution for power electronics. It can be understood more like a packaging technology. Basically power semiconductors (e.g. MOSFET and IGBT) are laminated to a substrate using cavities in the same way as in the ECP technology. Then vias are drilled and galvanically filled with copper to make the connection with the outer layers. The technology offers a symmetric solution meaning that are copper layers both in the top and the bottom of the integrated package, allowing for better thermal

Figure 18 – Chip mounted to the interposer in one of the steps of manufacturing using the  $i^2$ Board technology [10].

Figure 19 – Illustration of the  $p^2$ Board technology process flow [10].

management. Since the final package is flat it can be further embedded in a logic board eliminating the need of other means of connection. This technology is mainly suited for power converters (AC-DC, DC-DC, 3-phase drivers) [10]. Figure 19 illustrates the process flow of the technology.

The  $\mu^2$ Pack is suited for micro thin, micro pitch applications and is meant to be use in a modular way, that is, different functionalities are built onto a base PCB. The technology can be understood as a PoP method and allows the construction of very thin modules [10].

## 2.5 Advantages of the ECT

The ECT brings some very desirable characteristics to the PCBs. Alongside size reduction, there are some intrinsic advantages in integrating the components in the inner layers of the board. Following, the main advantages are presented and described. The advantages presented here corresponds to both embedded placed components and embedded formed components.

#### 2.5.1 Size reduction

Size reduction is one of the main subjects in research in electronics in the past decades and one of the most common reasons why the ECT is chosen by the designers. Generally in standard PCBs, size reduction is achieved using components with smaller packages.

One of the smallest packages available in the market is the 0201 (metric package 0603, 0.6 x 0.3 mm). This package usually replaces the 0402 (metric package 1005, 1.0 x 0.5 mm) yielding in a size reduction of 36% in unit area. Although, when considering design rules and pad spacing the reduction is much smaller and the fabrication issues usually are more relevant (handling, assembling equipment, testing) generating reliability issues. Now if embedding the component is possible to achieve 100% of unit surface are savings. It is estimated that the savings in area achieved by reducing the components packages to 0201 is equivalent to embedding the 0402 devices [43].

There are multiple ways of using the ECT to achieve size reduction. If embedding only passive components it is possible to make layouts where the embedded components are directly underneath the active components thus freeing outer layers surface area [30]. If also embedding the active components more functionality can be added with the same space, meaning higher density in the PCB. A smaller surface area also means less material thus material cost reduction. In the case of power electronics size reduction is important because of power density  $(W/mm^3)$  [6].

Still, size reduction is highly dependent on the application, the method used and the overall design requirements. For example, Motorola claims that a RF module redesigned using formed embedded components had a space reduction of 44% and the company Nortel, also using formed components reported space savings up to 50% in an emulator product [24].

Another great example is an active hybrid 300W EMI filter designed using embedded discrete components, planar inductors and embedded ferrite core to achieve an approximate 40% size reduction [35]. Crane Aerospace and Electronics claims that their technology Multi-Mix reduces overall weight and volume up to a factor of 10 in filtering applications [32].

#### 2.5.2 Improved Signal integrity

Signal integrity is closely tied with aspects related to transmission lines effects found in the PCB traces. The important aspects are signal speed and propagation time, impedance, reflections, terminations, cross talk, differential signals, return current and loop areas. This aspects are usually critical in logic circuits such as Random Access Memories (RAMs), clock circuits, high frequency switching pattern generators and so forth. In that type of circuits timing is crucial [45]. In power electronics the high frequency signals are usually the switching patterns and are generally within the 500 kHz range. In order to avoid signal reflections preserving the logic circuits and the switches gates, it is needed that the traces have proper terminations and the lowest impedance changes as possible. As well as avoiding parallel traces to overcome the cross talk issue [45].

The key point is protecting the traces against noise and interference and most importantly ensuring that the traces itself aren't causing the issues. The rule of thumb is keeping the traces lengths as small as possible. Sometimes is also critical to maintain some traces lengths equal to each other to avoid problems with differential signals and timing issues. Another important feature to pay attention is power and ground planes, those are essential in high frequency applications to avoid interference. The overall component proximity and decoupling capacitors are important aspects to be noted as well [45][46].

Using ECT the designer is able to significantly reduce the traces lengths and increase component proximity. Another advantage is that the traces and the component itself are surrounded by a single dielectric making it simpler to calculate propagation delays and avoid this issue, as well as increasing the overall signal speed and reducing the noise acquirement from the ambient [30][45]. Still, the connection between the components and power and ground planes could be done more efficiently and it is possible to avoid impedance variations in the traces more easily [30].

An intrinsic advantage of small traces is the reduction of parasitic losses due to smaller trace inductance and capacitance. This parasitic effects are more evident in high frequency switching applications thus using the ECT might be a suitable solution to minimize this problem.

#### 2.5.3 Improved EMI and EMC aspects

In electronic devices, as the frequency of operation increases, the devices start to act as generators of radio frequency signals. The radio energy produced interferes with the neighbour devices and such interference is called electromagnetic interference (EMI). This effect can be really harmful to components in the same circuit and in other equipment. This must be avoided and prevented and the capability of a device of operating without being susceptible to EMI and do not cause EMI is called electromagnetic compatibility (EMC). The device's EMC must be in compliance with the CISPR (International Special Committee on Radio Interference) regulations [28][45].

EMC covers the whole electromagnetic frequency spectrum from DC (0 Hz) to 20 GHz and encompasses the control and reduction of the already mentioned EMI and also electromagnetic fields (EMF) and radio frequency interference (RFI) [28]. Generally designers are more concerned with a specific type of EMI noise, the conductive EMI.

To ensure that the device is not susceptible to and isn't a source of conductive EMI,

input and output filters are applied. These filters are designed to attenuate the two modes of conducted EMI noise: common mode noise (CMN) and differential mode noise (DMN). CMN is the line to ground noise and the noise current flows in the same direction of the signal, returning through the ground. It can be suppressed using inductors in series in each power line and capacitors that are placed in parallel with each power line and ground [47]. DMN is the line-to-line noise where the noise current flows through one line conductor and returns through another without flowing to ground. It is suppressed using capacitors in parallel with the line conductors [47]. An example of input EMI filter is seen in Figure 20, a similar arrange is used as the input EMI filter on the HiGaN version 2.2.

Figure 20 – Example of input EMI filter.

If the input and output filters are realized correctly the EMI noise should be attenuated with a gain below the required by the standards through all the specified spectrum, which is generally between 150 kHz to 30 MHz [47]. However, even though the device is in compliance with the regulations, meaning that the conducted emissions are bellow a certain level, there could still be self deterioration within the device's circuits.

Concerning power electronics, the main source of conductive EMI noise is the switching characteristics of the converters circuits. The EMI noise is usually related to high voltage and high current peaks during switching. The fast variation of voltage over time, or high dv/dt, due to the switching of a transistor, generates high current peaks and create high leakage current in magnetic elements [48]. High di/dt on the other hand, creates voltage peaks due to the stray inductance of current loops [48]. To reduce these effects the dv/dt and di/dt must be reduced, this means reducing the switching frequency and thus increasing losses.

Another consequence from switching is a voltage and current oscillation around the desired level, also known as ringing that happens due to sudden change from both high to low or low to high levels. This transient oscillation has a high frequency and a fast high amplitude peak (also known as overshoot) generating EMI noise. To reduce the ringing effect a damping circuit is generally used, for example a RL or RC snubber circuit in series with the switch. Often the capacitors ESR are also used to attenuate the oscillations [49]. However this also brings losses to the system and a compromise must be made between efficiency and EMI reduction.

An alternative to reduce EMI emissions that affect other circuits within the same board is in the layout level. The key points are reducing the loop stray inductance by shortening signal and power paths, layout optimization for geometric design strategy, use of coupling and filter capacitors [49], use of solid ground planes, isolate signal from power paths and shielding. Those are all good design practices that basically mitigate parasitic effects and thus reduce the EMI emissions. With a good layout and low EMI emissions is sometimes possible to reduce the output EMI filter.