# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Rafael Sanchotene Silva

PROJETO, FABRICAÇÃO E MEDIÇÃO DE UM CHIP DEDICADO À CARACTERIZAÇÃO DA TECNOLOGIA CMOS 130nm

#### Rafael Sanchotene Silva

# PROJETO, FABRICAÇÃO E MEDIÇÃO DE UM CHIP DEDICADO À CARACTERIZAÇÃO DA TECNOLOGIA CMOS 130nm

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica para obtenção do grau de "Mestre em Engenharia Elétrica".

**Orientador**: Prof. Dr. Carlos Galup Montoro.

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Silva, Rafael Sanchotene Projeto, fabricação e medição de um chip dedicado à caracterização da tecnologia CMOS 130nm / Rafael Sanchotene Silva; orientador, Carlos Galup Montoro, 2018. 111 p.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós Graduação em Engenharia Elétrica, Florianópolis, 2018.

Inclui referências.

1. Engenharia Elétrica. 2. Estruturas de teste CMOS. 3. Tecnologia CMOS 130nm. 4. Circuitos Integrados. 5. Associações de transistores. I. Montoro, Carlos Galup. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

#### Rafael Sanchotene Silva

#### PROJETO, FABRICAÇÃO E MEDIÇÃO DE UM CHIP DEDICADO À CARACTERIZAÇÃO DA TECNOLOGIA CMOS 130nm

Esta dissertação foi julgada aprovada para a obtenção do grau de "Mestre em Engenharia Elétrica" e aceita em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica.

Florianópolis, SC., 23 de Fevereiro de 2018.

| melli.                                                          |

|-----------------------------------------------------------------|

| Prof. Dr. Marcelo Lobo Heldwein                                 |

| Coordenador do Programa de Pós-Graduação em Engenharia Elétrica |

|                                                                 |

| Prof. Dr. Carlos Galup Montoro                                  |

| Orientador                                                      |

|                                                                 |

| Banca Examinadora:                                              |

| Prof. Dr. Carlos Galup (Montoro                                 |

| Presidente — UFSC                                               |

| Useau C Go-co- t                                                |

| Prof. Dr. Oscar da Costa Gouveia Filho                          |

| Examinador — UFPR                                               |

| Geran Carloz                                                    |

| MSc, Juan Carlos Mateus Ardila                                  |

| Examinador — Chipus Microeletrônica S.A.                        |

Este trabalho é dedicado aos meus pais Rubens e Iára, e aos meus irmãos Rubens Filho e Rodrigo pelo apoio incondicional em todos os momentos de minha vida.

## Agradecimentos

A minha família e a minha namorada Victoria pelo apoio, incentivo, paciência e compreensão durante a realização deste trabalho.

A Oscar Pinto (in memoriam), Vera e Veraci (Bila), família especial que sempre me apoiou e esteve presente em todas as minhas conquistas.

Aos meus amigos e colegas de mestrado, em especial, a Andrés Ordoñes, Deni Alves, Edgar Maurício, Eduardo Brandão, Evandro Bolzan, Franciele Nornberg, Jefferson Ribeiro, João Vitor, Luís Henrique, Mariana Siniscalchi, Rodrigo Wrege e Thiago Darós pelo companheirismo e amizade.

Aos professores Carlos Galup Montoro e Márcio Cherem Schneider pela oportunidade e orientação durante a realização do trabalho no Laboratório de Circuitos Integrados (LCI). Agradeço em especial a Nazide Martins pela amizade e pelo suporte oferecido no LCI.

Gostaria de agradecer à Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES) e ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) pela concessão da bolsa de estudos durante os dois anos de mestrado e ao serviço da Metal-Oxide-Semiconductor Implementation Service (MOSIS) pela fabricação do circuito integrado proposto no trabalho.

Para mudar o mundo, você precisa antes mudar a sua cabeça.

– Jimi Hendrix

#### Resumo

O presente trabalho de dissertação apresenta um chip teste projetado e validado em tecnologia CMOS 130nm. O circuito foi construído através de uma matriz de transistores MOS LVT (Low Voltage Threshold) conectados em associações série/paralelo, com um total de 226 transistores. Para otimizar o número limitado de pinos e possibilitar diversas funcionalidades na extração de parâmetros, foi necessário o compartilhamento de terminais de substrato, fonte e dreno entre transistores. Através das associações série foi possível analisar o impacto do comprimento do canal nas características do dispositivo além de peculiaridades da tecnologia utilizada. A validação do circuito proposto se deu por meio de simulações em ambiente Cadence Virtuoso® e experimentalmente através das amostras fabricadas. Para a extração dos parâmetros foram utilizadas as metodologias  $g_m/I_D$  e  $3I_S$  permitindo o funcionamento do transistor na região linear e de saturação, respectivamente. As dispersões das características extraídas foram comparadas às simulações de Monte Carlo, assim como os modelos ACM e BSIM4 que foram comparados em relação aos dados experimentais. O circuito proposto também foi utilizado na avaliação do descasamento (mismatch) da tensão de limiar  $(V_{T0})$  entre transistores similares. Com isso, permite-se concluir que o circuito proposto não somente tem a finalidade de testes e verificações, mas também é uma importante ferramenta de análise tanto para uso no meio acadêmico/científico, auxiliando aos estudantes e novos projetistas na área de circuitos integrados, como também para o meio industrial permitindo a verificação de inconsistências relacionadas aos modelos BSIM.

Palavras-chave: Estruturas de teste CMOS, Tecnologia CMOS 130nm, Associações de transistores.

#### Abstract

The present text presents a test chip designed and validated in 130nm CMOS technology. The circuit was built as an array of LVT (Low Threshold Voltage) MOS transistors, associated in series/parallel, constituting a total of 226 transistors. In order to optimize the limited number of pins and to enable various parameters extraction, it was necessary to share some common connections for substrate, source and drain terminals. Through the series associations it was possible to analyze the impact of the increase of channel length on the characteristics of the device. The validation of the proposed circuit was done through simulations in the Cadence Virtuoso® environment and experimentally through the measurements of the manufactured samples. For the extraction of the parameters the methodologies  $g_m/I_D$ and  $3I_S$  were used allowing the operation of the transistor in the linear and saturation regions, respectively. The dispersions in the extracted parameters were compared to the Monte Carlo simulations carried out in the electric simulator. Thus, the ACM and BSIM4 models were compared with the obtained results. The proposed circuit also allowed an evaluation of the threshold voltage  $(V_{T0})$  mismatch between similar transistors. We conclude that the proposed circuit is useful not only for tests and verifications, but also as an analysis tool for use in the academic/scientific environment, helping students and new designers in the area of integrated circuits, as well as for the industrial environment allowing the verification of inconsistencies of BSIM models.

**Keywords:** CMOS Test Structures. 130 nm CMOS Technology . Associations of transistors.

# Lista de Figuras

| 2.1 | Transistor com implantes <i>pocket</i> envolvendo as regiões de fonte e dreno | 5  |

|-----|-------------------------------------------------------------------------------|----|

| 0.0 |                                                                               |    |

| 2.2 | Diagrama do transistor MOS canal N                                            | 6  |

| 2.3 | Associações de transistores                                                   | 9  |

| 2.4 | Associação série tipo T [1]                                                   | 10 |

| 3.1 | Método da Extrapolação Linear: a) Medição de $\mathbf{V}_{T0}$ na             |    |

|     | região triodo e b) região de saturação                                        | 12 |

| 3.2 | Método $Match-Point$ : a) Extração de $V_{T0}$ na região li-                  |    |

|     | near e b) região de saturação                                                 | 13 |

| 3.3 | Aproximações de inversão forte e fraca da característica                      |    |

|     | $I_D$ - $V_G$ do transistor                                                   | 14 |

| 3.4 | Configuração fonte comum de um transistor canal N para                        |    |

|     | realização do método $g_m/I_D$                                                | 15 |

| 3.5 | Corrente de dreno e transcondutância por unidade de                           |    |

|     | corrente de um transistor canal N                                             | 16 |

| 3.6 | Configuração de um transistor canal N para realização                         |    |

|     | do método $3I_S$                                                              | 16 |

| 3.7 | Extração da tensão de limiar através do método $3I_S.$                        | 17 |

| 3.8 | Extração do fator de inclinação através do método $3I_S.$                     | 18 |

| 4.1 | Tensão de limiar em função do comprimento do canal                            | 20 |

| 4.2 | Corrente específica de folha em função do comprimento                         |    |

|     | do canal                                                                      | 21 |

| 4.3 | Fator de inclinação em função do comprimento do canal.                        | 22 |

| 4.4 | Mobilidade efetiva em função do comprimento do canal.                         | 23 |

| 4.5 | Tensão de limiar em função da largura do canal                                | 24 |

| 4.6 | Corrente específica de folha em função da largura do canal.                   | 25 |

| 4.7 | Curva da variação do fator de inclinação em função da                         |    |

| ••  | largura do canal                                                              | 25 |

|     |                                                                               |    |

| 4.8  | Curva da variação da mobilidade de portadores efetiva em função da largura do canal | 26  |

|------|-------------------------------------------------------------------------------------|-----|

| 4.9  | Tensão de limiar pelo método $3I_S$ em função de diferen-                           | 20  |

| 4.3  | tes razões de aspecto                                                               | 27  |

| 4.10 |                                                                                     |     |

|      | com o método $3I_S$ em função de diferentes razões de                               |     |

|      | aspecto                                                                             | 27  |

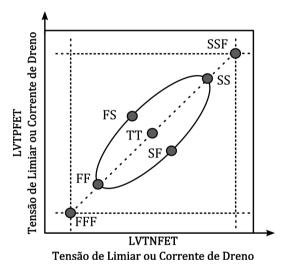

| 4.11 | Disposição dos corners na tecnologia GlobalFoundries                                |     |

|      | CMOS 130nm                                                                          | 28  |

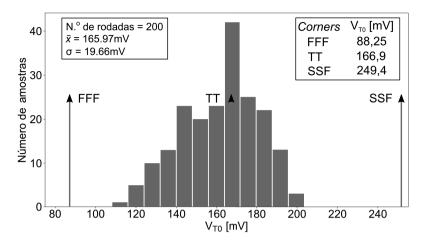

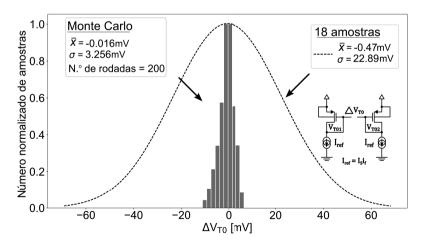

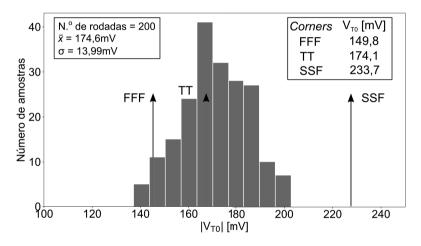

| 4.12 | Monte Carlo de processo e descasamento da tensão de                                 |     |

|      | limiar com o método $3I_S$                                                          | 30  |

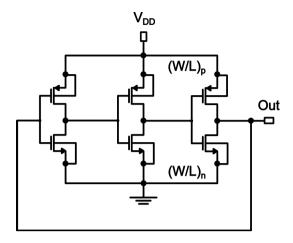

|      | Oscilador em anel de três estágios                                                  | 31  |

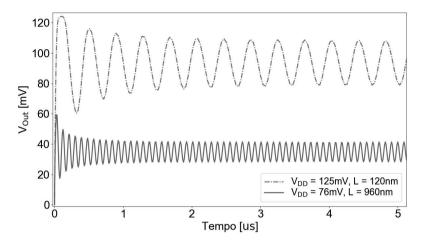

| 4.14 | Sinais de saída dos osciladores em anel                                             | 32  |

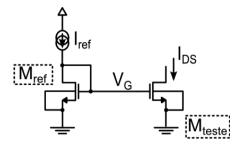

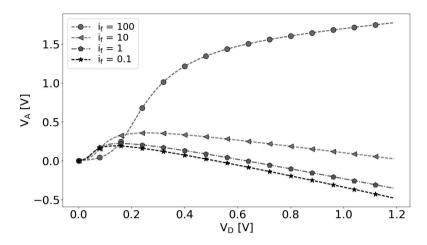

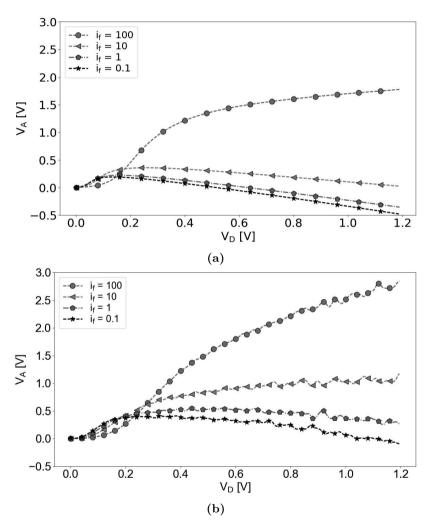

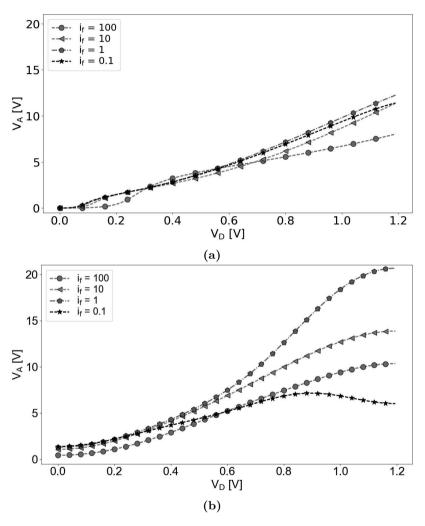

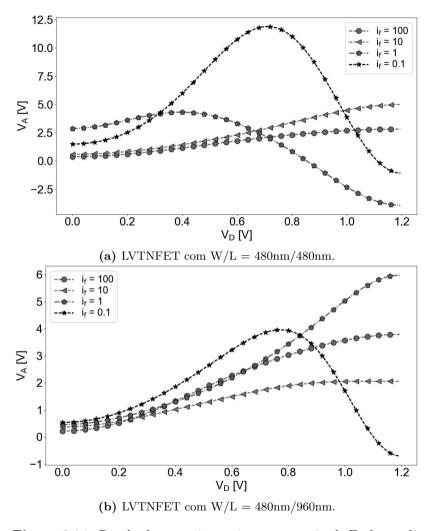

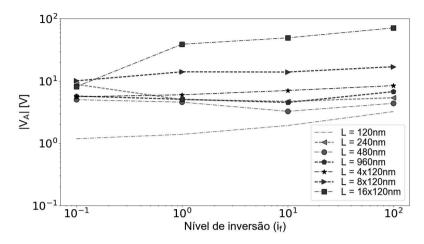

|      | Diagrama esquemático para extração da tensão de Early.                              | 33  |

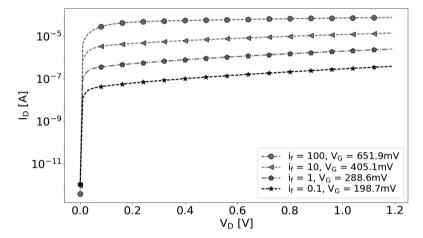

| 4.16 | Característica de saída do transistor de $W/L = 480 \text{nm}/120 \text{n}$         |     |

|      | para diferentes níveis de inversão                                                  | 33  |

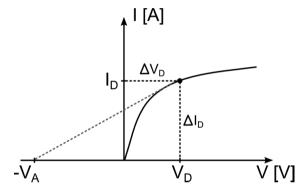

|      | Característica $I_D - V_D$                                                          | 34  |

| 4.18 | Tensão de Early para diferentes níveis de inversão do                               |     |

|      | transistor com dimensões $W/L = 480 \text{nm}/120 \text{nm}$                        | 35  |

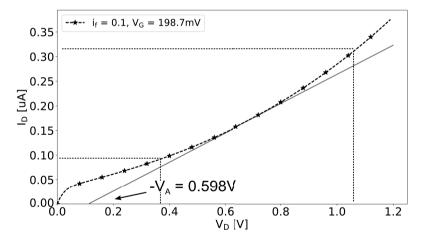

| 4.19 | Característica $I_D - V_D$ para $i_f = 0.1$ do transistor com                       |     |

|      | $W/L = 480 \text{nm}/120 \text{nm}. \dots \dots \dots \dots \dots \dots$            | 35  |

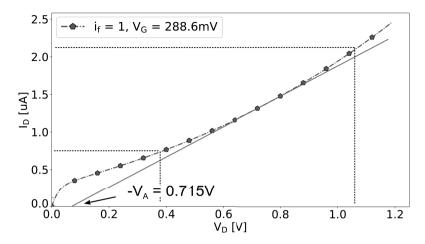

| 4.20 | Característica $I_D - V_D$ para $i_f = 1$ do transistor com                         | 0.0 |

|      | $W/L = 480 nm/120 nm. \dots \dots \dots \dots \dots \dots$                          | 36  |

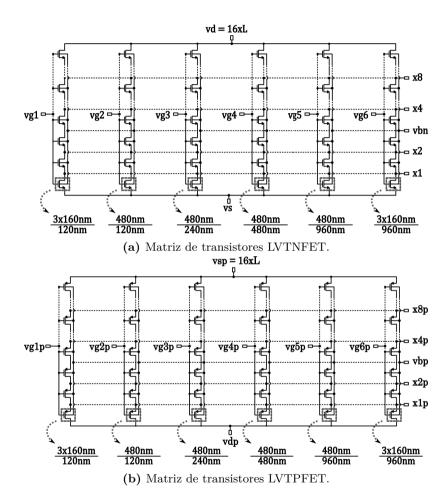

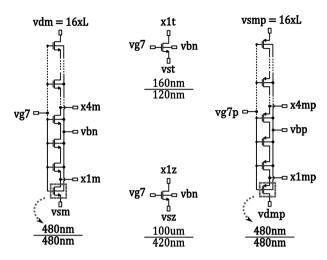

| 5.1  | Diagramas esquemáticos do circuito proposto                                         | 38  |

| 5.2  | Diagramas esquemáticos do transistor unitário (LVT),                                |     |

|      | nativo (ZVT) e associações série de transistores para                               |     |

|      | análises de descasamento (MIS)                                                      | 39  |

| 6.1  | Analisador de parâmetros Agilent 4156C                                              | 43  |

| 6.2  | a) Módulo de Test-Fixture Agilent 16442A e b) Chip teste.                           | 44  |

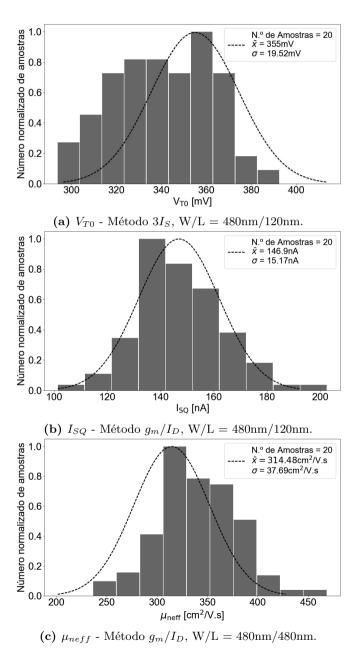

| 6.3  | Comparativo entre dispersões de 20 amostras LVTNFET                                 | 44  |

| 0.5  | e 200 rodadas de Monte Carlo (processo e descasamento).                             | 46  |

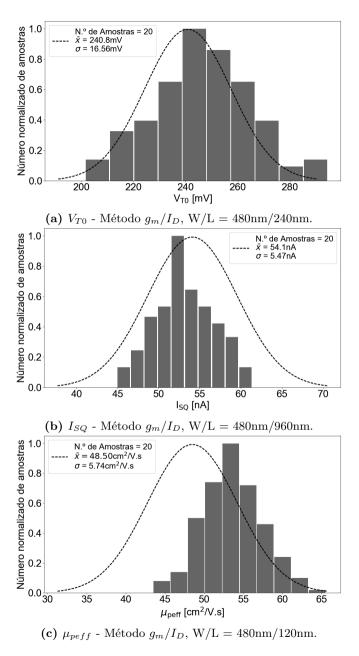

| 6.4  | Comparativo entre dispersões de 20 amostras LVTPFET                                 | 10  |

| 0.4  | e 200 rodadas de Monte Carlo (processo e descasamento).                             | 47  |

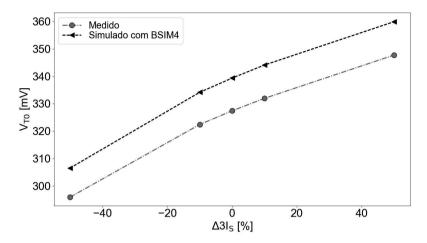

| 6.5  | Variação da tensão de limiar com a corrente específica                              |     |

|      | de um transistor LVTNFET de $W/L = 480$ nm/120nm.                                   | 52  |

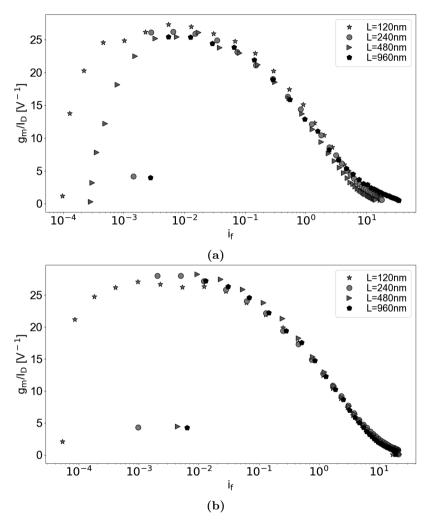

| 6.6  | Característica $g_m/I_D$ em função do nível de inversão                             |     |

|      | para diferentes comprimentos de canal para (a) LVTN-                                |     |

|      | FET e (b) LVTPFET                                                                   | 53  |

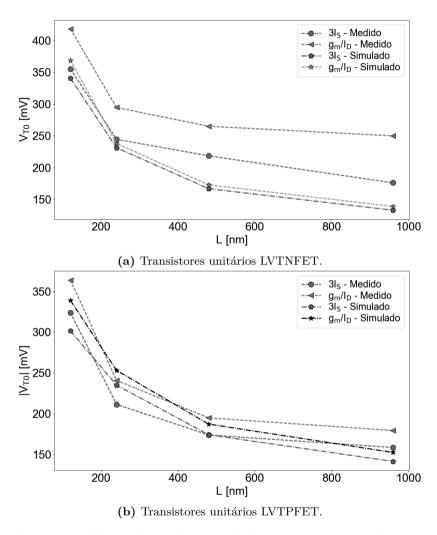

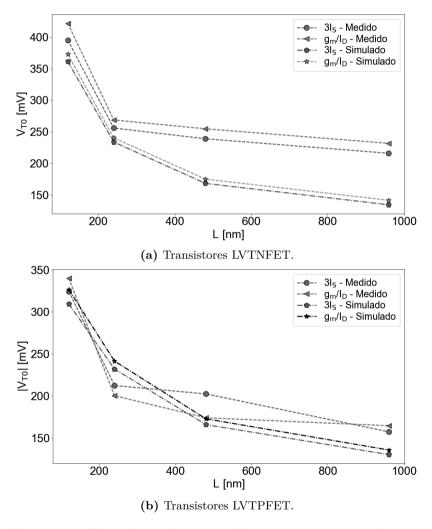

| 6.7  | Dependência da tensão de limiar com o aumento do com-                                                                                                    |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | primento de canal para transistores unitários                                                                                                            | 55  |

| 6.8  | Dependência da tensão de limiar com o aumento do comprimento de canal utilizando quatro transistores em série.                                           | 56  |

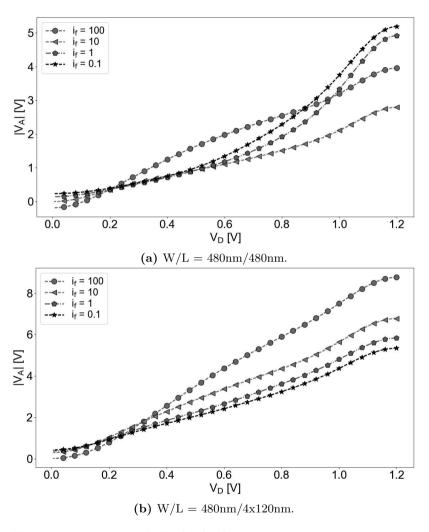

| 6.9  | Tensões de Early de um transitor LVTNFET unitário com $W/L = 480 \text{nm}/120 \text{nm}$ , em (a) curvas simuladas e                                    |     |

|      | (b) curvas experimentais                                                                                                                                 | 65  |

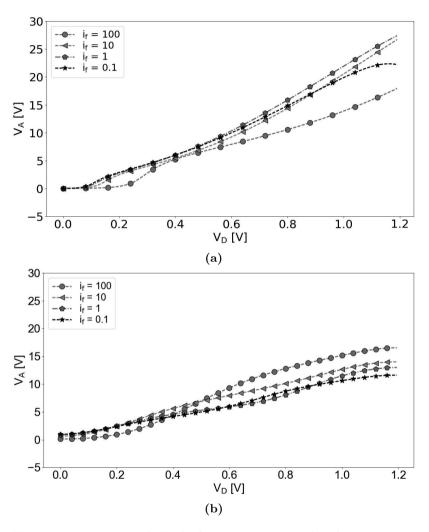

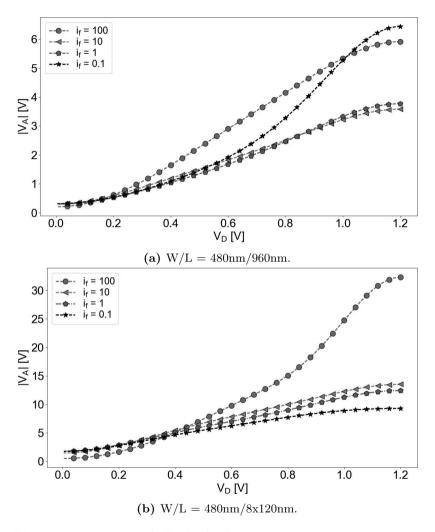

| 6.10 | Tensões de Early de uma associação série de quatro transistores LVTNFET com $W/L=480 nm/120 nm$ , em (a) curvas simuladas e (b) curvas experimentais     | 66  |

| 6.11 | Tensões de Early de uma associação série de oito transistores LVTNFET com $W/L=480 nm/120 nm$ , em (a)                                                   |     |

|      | curvas simuladas e (b) curvas experimentais                                                                                                              | 67  |

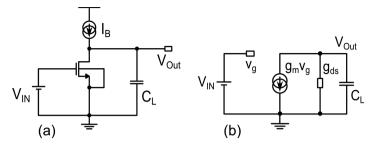

|      | (a) Amplificador Fonte Comum e (b) Circuito de pequenos sinais                                                                                           | 68  |

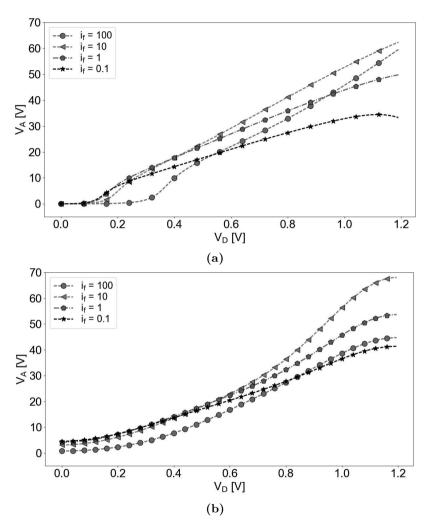

| 6.13 | Variação da tensão de Early em diferentes níveis de inversão para associações série LVTNFET com W/16xL = 480nm/16x120nm, em (a) dados simulados e em (b) |     |

|      | dados amostrais.                                                                                                                                         | 70  |

| 6.14 | Resultados experimentais para a tensão de Early em diferentes níveis de inversão utilizando transistores unitários                                       |     |

|      | LVTNFET                                                                                                                                                  | 71  |

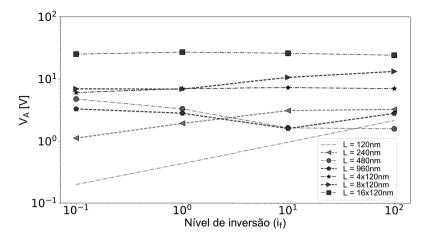

| 6.15 | Tensões de Early em função do nível de inversão para transistores unitários e associações série LVTNFET                                                  | 72  |

| 6.16 | Tensões de Early obtidas por experimento com um transistor unitário LVTPFET e associação série de quatro                                                 |     |

|      | transistores                                                                                                                                             | 73  |

| 6.17 | Tensões de Early obtidas por experimento com um transistor unitário LVTPFET e associação série de oito trans                                             |     |

|      | sistores.                                                                                                                                                | 74  |

| 6.18 | Tensões de Early em função do nível de inversão para transistores unitários e associações série LVTPFET                                                  | 76  |

| 6.19 |                                                                                                                                                          | •   |

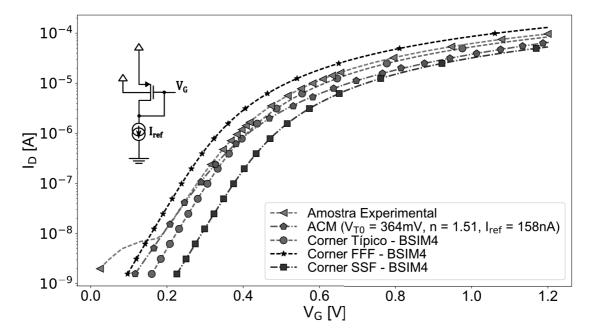

|      | 3 parâmetros medidos e curva experimental de transistor LVTNFET com $W/L = 480 nm/120 nm.$                                                               | 77  |

| 6.20 | Comparativo entre corners do modelo BSIM4, ACM com                                                                                                       | • • |

|      | 3 parâmetros medidos e curva experimental de transistor                                                                                                  |     |

| C 01 | LVTPFET com W/L = $480 \text{nm}/120 \text{nm}$                                                                                                          | 79  |

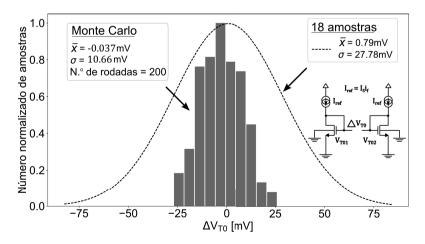

| 6.21 | Histograma $\Delta V_{T0}$ da análise de Monte Carlo e gaussiana dos dados obtidos com amostras LVTNFET de W/L =                                         |     |

|      | 480nm/480nm                                                                                                                                              | 82  |

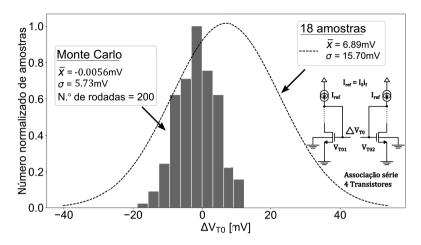

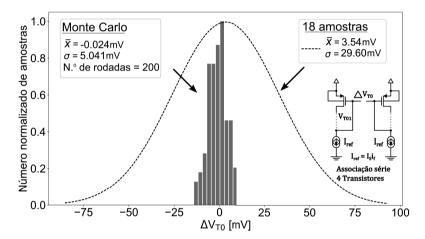

| 6.22 | Histograma $\Delta V_{T0}$ da análise de Monte Carlo (descasamento) e gaussiana dos dados obtidos com LVTNFET  | 0.0 |

|------|----------------------------------------------------------------------------------------------------------------|-----|

| 6.23 | de W/L = $480$ nm/ $4x480$ nm                                                                                  | 83  |

|      | samento) e gaussiana dos dados obtidos com amostras LVTPFET de W/L = $480 \text{nm}/480 \text{nm}$             | 85  |

| 6.24 | Histograma $\Delta V_{T0}$ da análise de Monte Carlo (descasamento) e gaussiana dos dados obtidos com amostras |     |

|      | LVTPFET de W/L = $480 \text{nm}/4 \text{x} 480 \text{nm}$                                                      | 86  |

| A.1  | Configuração Fonte Comum para realização do método $g_m/I_D$                                                   | 95  |

| A.2  | $g_m/I_D$                                                                                                      | 96  |

| A.3  | Tensão de limiar em função do comprimento do canal                                                             | 96  |

| A.4  | Dependência da corrente específica em função do au-                                                            | 90  |

| 11.4 | mento do comprimento do canal                                                                                  | 97  |

| A.5  | Dependência do fator de inclinação em função do au-                                                            |     |

|      | mento do comprimento do canal de transistores LVTP-                                                            |     |

|      | FET simulados com o modelo BSIM4                                                                               | 98  |

| A.6  | Dependência da mobilidade dos portadores em função                                                             |     |

|      | do comprimento do canal de transistores LVTPFET si-                                                            |     |

|      | mulados com o modelo BSIM4                                                                                     | 98  |

| A.7  | Configuração para extração de parâmetros do LVTP-FET através do método $3I_S$                                  | 99  |

| A.8  | Variação da tensão de limiar para diferentes comprimen-                                                        |     |

|      | tos de canal utilizando o método $3I_S$                                                                        | 100 |

| A.9  | Variação do fator de inclinação para diferentes compri-                                                        |     |

|      | mentos de canal utilizando o método $3I_S$                                                                     | 100 |

| A.10 | Histograma das dispersões da tensão de limiar obtidas                                                          | 101 |

|      | pelo método $3I_S$                                                                                             | 101 |

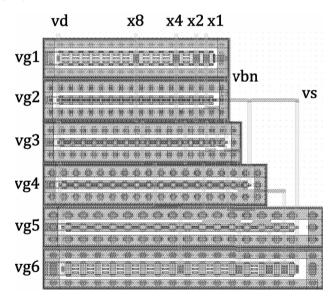

| B.1  | Leiaute da matriz de transistores LVTNFET                                                                      | 103 |

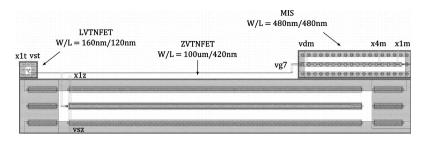

| B.2  | Leiaute de configurações adicionais contendo o transistor                                                      |     |

|      | de dimensões mínimas (LVT), transistor nativo (ZVT) e                                                          |     |

|      | transistores para avaliação de descasamento (MIS)                                                              | 104 |

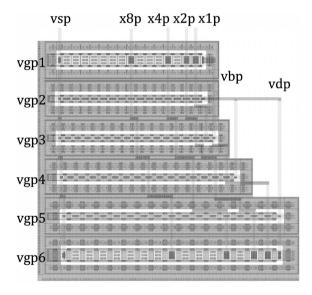

| B.3  | Leiaute da matriz de transistores LVTPFET                                                                      | 104 |

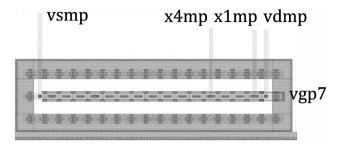

| B.4  | Leiaute da configuração adicional contendo transistores                                                        |     |

|      | para avaliação de descasamento (MIS)                                                                           | 105 |

| B.5  | Leiaute do topo do chip enviado para fabricação com                                                            |     |

|      | detalhes sobre os terminais e partes referentes aos tran-                                                      | 40= |

|      | sistores canal N e P                                                                                           | 105 |

| B.6 | Diagrama representativo do encapsulamento DIP40               | 106 |

|-----|---------------------------------------------------------------|-----|

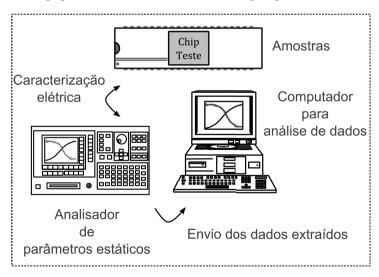

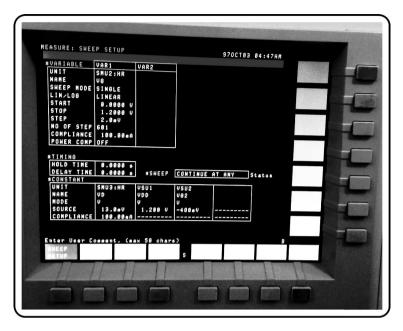

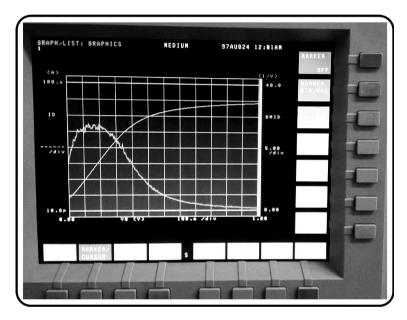

| C.1 | Processo de caracterização das amostras                       | 107 |

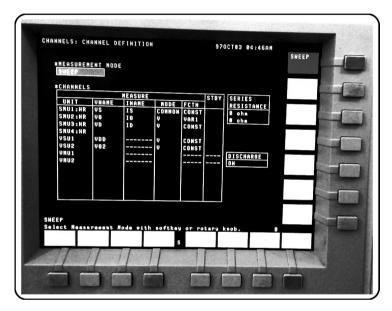

| C.2 | Passo 1 - seleção dos pinos para excitação elétrica           | 108 |

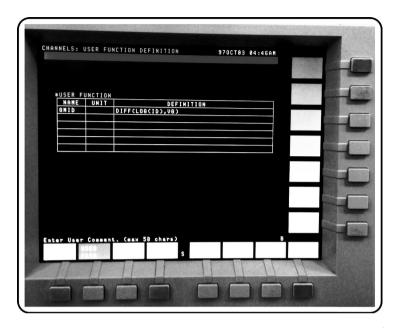

| C.3 | Passo 2 - equação para extração da característica $g_m/I_D$ . | 109 |

| C.4 | Passo 3 - parâmetros de variação para extração da ca-         |     |

|     | racterística $I_D - V_G$                                      | 110 |

| C.5 | Passo 4 - extração das curvas do transistor                   | 111 |

|     |                                                               |     |

# Lista de Tabelas

| Parâmetros básicos da Tecnologia CMOS 130nm                     | 19                                                                  |

|-----------------------------------------------------------------|---------------------------------------------------------------------|

| •                                                               | 20                                                                  |

|                                                                 | 29                                                                  |

|                                                                 | 29                                                                  |

| *                                                               | 31                                                                  |

| - *                                                             | 34                                                                  |

|                                                                 |                                                                     |

| Descrição dos pinos utilizados no chip teste                    | 41                                                                  |

| Dignarçãos nos parâmetros de transisteros unitérios LVTN        |                                                                     |

|                                                                 | 48                                                                  |

|                                                                 | 10                                                                  |

|                                                                 | 50                                                                  |

|                                                                 |                                                                     |

| transistores unitários                                          | 59                                                                  |

| Parâmetros em função do comprimento do canal para               |                                                                     |

| associações de 4 transistores                                   | 61                                                                  |

|                                                                 |                                                                     |

| 3                                                               | 62                                                                  |

|                                                                 | co                                                                  |

|                                                                 | 63                                                                  |

| v i                                                             |                                                                     |

| • •                                                             | 75                                                                  |

|                                                                 | 10                                                                  |

|                                                                 | 81                                                                  |

|                                                                 | _                                                                   |

| de transistores LVTNFET                                         | 82                                                                  |

| Sumário das extrações experimentais de $\Delta V_{T0}$ de tran- |                                                                     |

| sistores LVTPFET                                                | 84                                                                  |

|                                                                 | Sumário sobre os $corners$ da tecnologia GlobalFoundries CMOS 130nm |

| 6.11 | Dados estatísticos do descasamento da tensão de limiar de transistores LVTPFET | 85  |

|------|--------------------------------------------------------------------------------|-----|

| A.1  | Resumo dos resultados obtidos com <i>corners</i> e Monte Carlo. 1              | .02 |

## Lista de Abreviaturas e Siglas

Sigla Descrição

ACM Advanced Compact MOSFET Model

CA Corrente Alternada

BSIM Modelo MOSFET da University of California - Berkeley

CC Corrente Contínua

CMOS Complementary Metal-Oxide-Semiconductor

DIBL Drain-Induced Barrier Lowering

EL Extrapolação Linear

EKV Enz-Krummenacher-Vittoz

FC Fonte Comum

${\it LVT} \qquad \qquad {\it Low \ Voltage \ Threshold}$

$\begin{array}{ll} {\rm MOSFET} & {\it Metal-Oxide-Semiconductor\ Field-Effect\ Transistor} \\ {\rm MOSIS} & {\it Metal-Oxide-Semiconductor\ Implementation\ Service} \\ \end{array}$

MP Match Point

RSCE Reverse Short Channel Effect

SCE Short Channel Effect

UICM Unified Current-Control Model

# Lista de Símbolos

| Símbolo      | Descrição                                       | Unidade          |

|--------------|-------------------------------------------------|------------------|

| $A_V$        | Ganho de tensão                                 | [V/V]            |

| $C_{b}^{'}$  | Capacitância de depleção por unidade de área    | $[F/m^2]$        |

| $C_L$        | Capacitância de carga                           | [F]              |

| $C_{ox}^{'}$ | Capacitância de óxido por unidade de área       | $[F/m^2]$        |

| $g_{ds}$     | Condutância de saída                            | [A/V]            |

| $g_{mb}$     | Transcondutância de substrato                   | [A/V]            |

| $g_{md}$     | Transcondutância de dreno                       | [A/V]            |

| $g_{mg}$     | Transcondutância de porta                       | [A/V]            |

| $g_{ms}$     | Transcondutância de fonte                       | [A/V]            |

| $I_B$        | Corrente de polarização                         | [A]              |

| $I_D$        | Corrente de dreno                               | [A]              |

| $i_f$        | Corrente normalizada direta                     | _                |

| $I_F$        | Corrente de saturação direta                    | [A]              |

| $i_r$        | Corrente normalizada reversa                    | _                |

| $I_R$        | Corrente de saturação reversa                   | [A]              |

| $I_{ref}$    | Corrente de referência                          | [A]              |

| $I_S$        | Corrente específica                             | [A]              |

| $I_{SQ}$     | Corrente específica de folha                    | [A]              |

| k            | Constante de Boltzmann $(1,38 \times 10^{-23})$ | $[\mathrm{J/K}]$ |

| L            | Comprimento do canal                            | [m]              |

| $m_p$        | Número de transistores associados em paralelo   | _                |

| $N_A$        | Dopantes aceitadores no semicondutor            | $[m^{-3}]$       |

| $n_s$        | Número de transistores associados em série      |                  |

| n            | Fator de inclinação (rampa)                     | _                |

| q               | Carga elementar do elétron $(1.6 \times 10^{-19})$ | [C]                           |

|-----------------|----------------------------------------------------|-------------------------------|

| T               | Temperatura absoluta                               | [K]                           |

| $t_{ox}$        | Espessura do óxido de porta                        | [m]                           |

| $\mu$           | Mobilidade de portadores                           | $[\mathrm{m}^2/\mathrm{V.s}]$ |

| $\mu_{eff}$     | Mobilidade efetiva de portadores                   | $[\mathrm{m}^2/\mathrm{V.s}]$ |

| $V_A$           | Tensão de Early                                    | [V]                           |

| $V_B$           | Tensão de substrato                                | [V]                           |

| $V_D$           | Tensão de dreno                                    | [V]                           |

| $V_{DD}$        | Tensão de alimentação                              | [V]                           |

| $V_{D_{SAT}}$   | Tensão de saturação                                | [V]                           |

| $V_G$           | Tensão de porta                                    | [V]                           |

| $V_{IN}$        | Tensão de entrada                                  | [V]                           |

| $V_{Out}$       | Tensão de saída                                    | [V]                           |

| $V_P$           | Tensão de pinch-off                                | [V]                           |

| $V_S$           | Tensão de fonte                                    | [V]                           |

| $V_{T0}$        | Tensão de limiar                                   | [V]                           |

| W               | Largura do canal                                   | [m]                           |

| $\Delta L$      | Comprimento das difusões laterais                  | [m]                           |

| $\Delta V_{T0}$ | Descasamento da tensão de limiar                   | [V]                           |

| $\Delta W$      | Largura da invasão do óxido nas regiões ativas     | [m]                           |

| $\epsilon_s$    | Permissividade elétrica do semicondutor            | [F/m]                         |

| $\phi_s$        | Potencial de superfície                            | [V]                           |

| $\phi_{sa}$     | Potencial de superfície em inversão fraca profunda | [V]                           |

| $\phi_t$        | Tensão térmica                                     | [V]                           |

# Sumário

| 1 | Inti | rodução                                                  | 1  |

|---|------|----------------------------------------------------------|----|

|   | 1.1  | Objetivos                                                | 2  |

|   | 1.2  | Organização                                              | 2  |

| 2 | Bre  | ve revisão dos modelos de transistores MOS               | 3  |

|   | 2.1  | Classificação dos modelos teóricos do MOSFET             | 3  |

|   | 2.2  | Modelo ACM                                               | 5  |

|   |      | 2.2.1 Equações básicas utilizadas no modelo ACM          | 5  |

|   | 2.3  | Modelagem das associações de transistores MOS $\ \ .$    | 8  |

| 3 | Mé   | todos para extração da tensão de limiar                  | 11 |

|   | 3.1  | Métodos convencionais                                    | 11 |

|   |      | 3.1.1 Método da Extrapolação Linear (EL)                 | 11 |

|   |      | 3.1.2 Método <i>Match-Point</i> (MP)                     | 12 |

|   | 3.2  |                                                          | 14 |

|   | 3.3  | Método $3I_S$                                            | 16 |

| 4 | Sim  | ulações com LVTNFET utilizando o modelo BSIM4 1          | 19 |

|   | 4.1  | Extração de parâmetros com o método $g_m/I_D$            | 20 |

|   |      | 4.1.1 Tensão de limiar                                   | 20 |

|   |      | 4.1.2 Corrente específica de folha                       | 21 |

|   |      | 4.1.3 Fator de inclinação                                | 21 |

|   |      | 4.1.4 Mobilidade de portadores                           | 22 |

|   |      | 4.1.5 Avaliação do impacto da largura do canal nos pa-   |    |

|   |      | râmetros dos transistores                                | 23 |

|   | 4.2  | Extração de parâmetros com o método $3I_S$               | 26 |

|   |      | 4.2.1 Tensão de limiar                                   | 26 |

|   |      | 4.2.2 Fator de inclinação                                | 27 |

|   | 4.3  | 3                                                        | 28 |

|   | 4.4  | Impacto da redução de $V_{T0}$ em função de L no projeto |    |

|   |      |                                                          | 30 |

|   |      |                                                          |    |

|                                                                             | 4.5   | Extraç         | ão da tensão de Early                                                                                                        | 31              |

|-----------------------------------------------------------------------------|-------|----------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 5                                                                           | Pro   | jeto do        | chip teste                                                                                                                   | 37              |

| 6                                                                           | Ext   | ração d        | de parâmetros                                                                                                                | 43              |

|                                                                             | 6.1   | Result         | ados e discussão                                                                                                             | 44              |

|                                                                             |       | 6.1.1<br>6.1.2 | Análise comparativa entre dispersões das amostras e simulações de Monte Carlo Dependência da tensão de limiar com a corrente | 45              |

|                                                                             |       | 0.1.2          | específica no método $3I_S$                                                                                                  | 51              |

|                                                                             |       | 6.1.3          | Dependência dos parâmetros em função do comprimento do canal                                                                 | 52              |

|                                                                             |       | 6.1.4          | Análise comparativa da tensão de Early de transistores unitários e associações série de transistores                         |                 |

|                                                                             |       | 6.1.5          | Importância da extração experimental dos parâ-                                                                               | 04              |

|                                                                             |       | 6.1.6          | metros                                                                                                                       | 75              |

|                                                                             |       | 0.1.0          | dos transistores                                                                                                             | 80              |

| 7                                                                           | Con   | sidera         | ções finais e trabalhos futuros                                                                                              | 87              |

| Re                                                                          | eferê | ncias          |                                                                                                                              | 89              |

|                                                                             |       |                | Extração de parâmetros simulados do tran-                                                                                    |                 |

| $\mathbf{sis}$                                                              |       | VTPF           |                                                                                                                              | 95              |

|                                                                             | A.1   |                | ao pelo método $g_m/I_D$                                                                                                     | 95              |

|                                                                             |       |                | Tensão de limiar                                                                                                             | 96              |

|                                                                             |       |                | Corrente específica de folha                                                                                                 | 97              |

|                                                                             |       |                | Fator de inclinação                                                                                                          | 97              |

|                                                                             |       | A.1.4          | Mobilidade de portadores                                                                                                     | 97              |

|                                                                             | A.2   |                | $\tilde{a}$ o pelo método $3I_S$                                                                                             | 99              |

|                                                                             |       | A.2.1          |                                                                                                                              | 99              |

|                                                                             |       | A.2.2          | Fator de inclinação                                                                                                          | 99              |

|                                                                             | A.3   | Compa          | arativo entre análises de <i>corners</i> e Monte Carlo                                                                       | 101             |

| Aı                                                                          | oênd  | ice B          | Leiautes e diagramas do chip teste                                                                                           | 103             |

| Apêndice C Procedimentos experimentais para extra-<br>ção de parâmetros 107 |       |                |                                                                                                                              | 10 <del>7</del> |

## Capítulo 1

## Introdução

Na área de circuitos integrados, o trabalho dos projetistas é diretamente impactado pela eficiência dos simuladores elétricos de circuitos. Circuitos com alta sensibilidade às variações de processo, tais como alguns blocos analógicos, digitais e de rádio-frequência realizados na tecnologia CMOS (Complementary Metal Oxide Semiconductor) devem ser exaustivamente verificados antes e após sua concepção. Para esta finalidade, os ambientes de simulação elétrica são os melhores recursos disponíveis atualmente, possibilitando um rápido fluxo de projeto, economizando tempo e custo no desenvolvimento de novos circuitos. Por outro lado, falhas nos modelos elétricos dos componentes utilizados por estas ferramentas podem levar o projeto ao fracasso com grande prejuízo a todos os envolvidos no trabalho. Neste sentido e com a finalidade de delimitar ou evitar tais imprevistos, foram desenvolvidos circuitos de teste com inúmeras aplicações que vão da verificação do descasamento (mismatch) e das dispersões de parâmetros até a estimativa do rendimento de produção de um circuito para uma determinada tecnologia. Exemplos de circuitos testes são dados nos trabalhos [2–4] em que são apresentados osciladores em anel para caracterizações dinâmicas da tecnologia, sendo um importante recurso em projetos de blocos digitais e de radio-frequência. Em [5,6] são apresentados circuitos dedicados à caracterização e avaliação dos efeitos do descasamento de transistores em circuitos analógicos e mistos. Não menos importante que os trabalhos citados, os estudos apresentados em [7-12] revelam uma grande diversidade de aplicações para os chips teste, incluindo a avaliação do rendimento de produção (yield) de circuitos.

Através de todos os trabalhos citados pode-se observar que os circuitos dedicados à caracterização de parâmetros são cada vez mais necessários tanto no meio científico quanto no industrial.

## 1.1. Objetivos

O objetivo principal deste trabalho de dissertação é o projeto, a fabricação e a validação de um chip dedicado à extração de parâmetros. Para isto serão utilizados e analisados os transistores de baixa tensão de limiar da tecnologia GlobalFoundries CMOS 130nm. Dentre as funcionalidades do chip proposto estão a caracterização e verificação estática (CC) através de dispositivos unitários e associações série de transistores. Além disso serão analisadas as possíveis falhas dos modelos comportamentais utilizados nos modernos simuladores elétricos no nível de transistores. Os possíveis benefícios do circuito proposto são a prevenção e correção de falhas nos circuitos simulados antes da prototipação e verificação, reduzindo o custo global de projetos de grande escala comercial.

## 1.2. Organização

Este trabalho de dissertação está organizado em mais seis capítulos os quais são sumarizados abaixo:

- $\bullet$  Capítulo 2: Neste capítulo são revisados os conceitos básicos do funcionamento do MOSFET (Metal Oxide Semiconductor Field Effect Transistor) e ao final apresentado o modelo adotado para uso neste trabalho.

- Capítulo 3: Este capítulo apresenta os métodos utilizados para extração de parâmetros do transistor, servindo de suporte ao desenvolvimento de simulações e caracterizações experimentais dos dispositivos.

- $\bullet$  Capítulo 4: Neste capítulo são apresentadas as simulações realizadas com o modelo BSIM4 aplicando os métodos estudados no terceiro capítulo.

- Capítulo 5: Apresenta o circuito teste e suas funcionalidades, incluindo os diagramas esquemáticos do mesmo.

- Capítulo 6: Este capítulo mostra os resultados experimentais e de simulação do chip teste, além de comparativos entre os métodos de extração de parâmetros e também dos resultados obtidos com os modelos BSIM4 e ACM.

- Capítulo 7: Neste último capítulo são sumarizados os resultados obtidos assim como possíveis aplicações do circuito, além de sugestões para trabalhos futuros.

## Capítulo 2

# Breve revisão dos modelos de transistores MOS

Atualmente é grande o número de ferramentas para simulação de circuitos integrados. A mais difundida entre elas é o simulador elétrico SPICE®, escrito em linguagem FORTRAN na década de 70 por um grupo de pesquisadores da Universidade de Berkeley. Como naquela época a tecnologia MOS ainda era pouco desenvolvida e muito limitada, esta ferramenta utilizava um modelo rudimentar de transistor, batizado de SPICE LEVEL 1. Em sua terceira versão, SPICE utilizou no seu modelo do MOSFET equações que incorporavam diversos fenômenos físicos e efeitos causados pela redução nas dimensões dos dispositivos. Contudo, essas melhorias não foram suficientes para caracterizar o dispositivo em todas as regiões de operação. Diversas descontinuidades foram observadas entre as regiões de funcionamento e consequentemente falhas graves durante a simulação do transistor, limitando seu uso à simulações em regiões específicas e bem definidas. Por esses motivos, diversos modelos do MOSFET foram propostos ao longo dos anos com a finalidade de aproximar as simulações elétricas aos comportamentos reais dos transistores MOS. Estes modelos serão brevemente comentados na próxima seção.

## 2.1. Classificação dos modelos teóricos do MOSFET

Os modelos podem ser classificados a partir dos conceitos utilizados para sua elaboração resultando em três grandes grupos de modelos compactos [13].

O primeiro grupo de modelos é baseado na análise física do dispositivo. O trabalho pioneiro desta classe de modelos foi desenvolvido no final da década de 80 por Maher e Mead e foi denominado de Modelo

de Carga [14]. Este modelo permite a representação das características do transistor MOS através de expressões únicas e de fácil compreensão.

O segundo grupo de modelos compactos é chamado de empírico sendo o principal modelo desta classe o EKV proposto em [15]. Este modelo foi o primeiro a preservar a simetria do transistor MOS e a representar de forma contínua as características nas diferentes regiões de operação. O modelo utiliza funções empíricas que aproximam as curvas características do dispositivo nas diferentes regiões de operação, porém falha na modelagem de cargas o que limita seu uso à circuitos não chaveados.

Por último, os modelos baseados em tabelas de dados conforme apresentados em [16], fazem uso de resultados previamente obtidos através de extrações de dispositivos reais ou de algoritmos numéricos utilizados nos simuladores. Essas tabelas são armazenadas em arquivos que posteriormente serão lidos pelo simulador elétrico.

A evolução no processamento computacional permitiu que os modelos físicos ganhassem destaque com uma maior complexidade em suas expressões. O aumento em sua complexidade é o resultado da incorporação dos fenômenos físicos apresentados nos dispositivos de canal reduzido como no caso da tecnologia CMOS 130nm utilizada neste estudo.

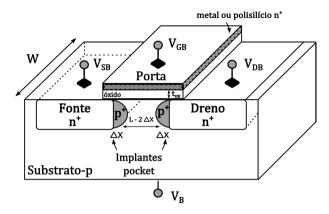

A tecnologia CMOS 130nm emprega no processo de fabricação implantes altamente dopados com o mesmo tipo de material do substrato dos transistores. Tais dopagens são localizadas nas proximidades de fonte e dreno, e são chamadas de implantes de bolso ou pocket (halo) sendo representadas na Figura 2.1. Os implantes pocket são utilizados para diminuir o efeito de redução de barreira induzida pelo dreno (DIBL) e estão na origem do efeito de canal curto reverso (RSCE - Reverse Short Channel Effect) [17,18]. O efeito RSCE é mais intenso na região de inversão fraca (subthreshold) devido a dependência exponencial da corrente de dreno com as tensões neste regime de operação do transistor.

Retornando aos aspectos que contribuiram pela preferência dos modelos físicos temos o fato dos modelos empíricos e tabelados não permitirem a avaliação individual de cada efeito físico o que dificulta o acompanhamento pelo modelo do escalonamento da tecnologia [16].

Resumindo, um modelo para ser consistente e eficiente em simulação necessita de equações únicas e simples válidas em todas as regiões de operação do transistor (inversão fraca, moderada e forte).

A aproximação teórica fundamental é a de canal gradual que reduz um problema bidimensional a dois problemas unidimensionais

**Figura 2.1:** Transistor com implantes *pocket* envolvendo as regiões de fonte e dreno.

acoplados [19]. Como explicado anteriormente, existem diversos modelos compactos do transistor MOS. Dentre os modelos mais populares, temos os baseados na tensão de limiar (BSIM3, BSIM4, MM9, etc.) e os chamados modelos compactos de nova geração, que utilizam seja a carga ou o potencial de superfície como variável principal. Porém os diferentes modelos compactos de nova geração são derivados do mesmo modelo físico de Pao-Sah [20].

Neste trabalho adotamos um modelo de carga chamado de Advanced Compact Model ou simplesmente ACM [19]. Este modelo é fundamentado na aproximação linear entre carga de portadores e potencial de superfície ao longo do canal [14] e preserva a simetria do dispositivo assim como o modelo EKV.

#### 2.2. Modelo ACM

O desenvolvimento do modelo ACM em meados dos anos 90 foi baseado nas mesmas aproximações físicas utilizadas por Maher e Mead [14, 19].

## 2.2.1. Equações básicas utilizadas no modelo ACM

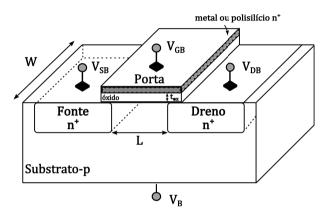

O diagrama do transistor MOS canal N está ilustrado na Figura 2.2 com seus quatro terminais característicos. A caracterização em todas as regiões de operação é simplificada graças ao conceito de nível de inversão [21]. A corrente de um transistor de canal longo é decomposta

em duas componentes, a direta  $(I_F)$  e a reversa  $(I_R)$  representadas na expressão abaixo

$$I_D = I_F - I_R = I(V_G, V_S) - I(V_G, V_D) = I_S(i_f - i_r)$$

(2.1)

onde os potenciais de fonte  $V_S$ , de dreno  $V_D$  e de porta  $V_G$  estão referenciados ao substrato.

Figura 2.2: Diagrama do transistor MOS canal N.

Para um transistor operando em região de saturação  $(I_F \gg I_R)$ , a expressão (2.1) reduz-se à

$$I_D \approx I_F = I_S i_f \tag{2.2}$$

onde  $I_S$  é chamada de corrente específica e  $i_f$  representa a corrente normalizada direta ou nível de inversão do transistor. A corrente específica é definida por [19]

$$I_S = I_{SQ} \left( \frac{W}{L} \right) \tag{2.3}$$

em que W e L são respectivamente a largura e comprimento do canal do transistor. Por sua vez, o parâmetro  $I_{SQ}$  representa a corrente específica de folha definida como a corrente específica para um transistor de W/L = 1, e expressa por

$$I_{SQ} = \frac{1}{2}\mu C'_{ox} n\phi_t^2 \tag{2.4}$$

onde  $\mu$  é a mobilidade dos portadores no canal de condução,  $C_{ox}^{'}$  a capacitância do óxido por unidade de área e  $\phi_t$  é a tensão térmica cujo valor é de 26mV para a temperatura de 300K. A variável "n"é chamada de fator de inclinação (rampa), definida como

$$n = 1 + \frac{C_b'}{C_{or}'} \tag{2.5}$$

em que  $C_b^{'}$  representa a capacitância de depleção por unidade de área .

A relação entre correntes e tensões no modelo ACM para todas as regiões de operação do transistor é dada pela expressão

$$V_P - V_{S(D)} = \phi_t \left[ \sqrt{1 + i_{f(r)}} - 2 + \ln \left( \sqrt{1 + i_{f(r)}} - 1 \right) \right]$$

(2.6)

em que a tensão de pinch-off  $(V_P)$  é aproximada por [19]

$$V_P \approx \frac{V_{GB} - V_{T0}}{n} \tag{2.7}$$

sendo  $V_{T0}$  a tensão de limiar do transistor. Este parâmetro é fundamental para modelagem e caracterização dos transistores MOS.

As transcondutâncias do transistor são definidas como

$$g_{mg} = \frac{\partial I_D}{\partial V_G}, g_{ms} = -\frac{\partial I_D}{\partial V_S}, g_{md} = \frac{\partial I_D}{\partial V_D}, g_{mb} = \frac{\partial I_D}{\partial V_B}.$$

(2.8)

Consequentemente

$$\Delta I_D = g_{mg} \Delta V_G - g_{ms} \Delta V_S + g_{md} \Delta V_D + g_{mb} \Delta V_B. \tag{2.9}$$

A partir de (2.9) podemos facilmente verificar que [19]

$$g_{ms} = g_{mq} + g_{md} + g_{mb}. (2.10)$$

As transcondutâncias de dreno e fonte podem ser calculadas a partir de  $\left[21\right]$

$$g_{ms(d)} = \frac{2I_S}{\phi_t} \left( \sqrt{1 + i_{f(r)}} - 1 \right).$$

(2.11)

A expressão (2.11) é de suma importância no projeto de circuitos integrados por mostrar uma relação compacta e universal para os transistores MOS. O único parâmetro dependente da tecnologia apresentado nesta equação é a corrente específica que está diretamente ligada as dimensões (W e L) do dispositivo. Em [21] demonstra-se que

$$g_{mg} = \frac{g_{ms} - g_{md}}{n}. (2.12)$$

Além disso temos que um transistor MOS de canal longo e operando em região de saturação apresenta  $i_r \ll i_f$  e portanto  $g_{mg} \approx g_{ms}/n$ .

A transcondutância de substrato pode ser calculada a partir de (2.10) e (2.12)

$$g_{mb} = (n-1) g_{ma}. (2.13)$$

Outra expressão importante para o projeto de circuitos integrados e que será largamente aplicada nas extrações de parâmetros deste trabalho é a transcondutância por unidade de corrente,  $g_m/I_D$ . Este parâmetro mede a eficiência da conversão de potência (corrente) em amplificação (transcondutância). Além disso, este parâmetro permite uma avaliação do nível de inversão do transistor que por sua vez é diretamente relacionado ao desempenho do dispositivo, permitindo seu dimensionamento no projeto de diversos circuitos [21].

Para calcular  $g_{ms(d)}/I_{F(R)}$  em termos da corrente específica, combinamos (2.1) e (2.11) resultando

$$\frac{g_{ms(d)}}{I_{F(R)}} = \frac{2}{\phi_t \left(\sqrt{1 + i_{f(r)}} - 1\right)}.$$

(2.14)

Através de (2.12) e (2.14) obtemos

$$\frac{g_{mg}}{I_D} = \frac{2}{n\phi_t \left(\sqrt{1 + i_f} + \sqrt{1 + i_r}\right)}.$$

(2.15)

Por simplicidade chamaremos  $g_{mg}$  apenas de  $g_m$  como a transcondutância ligada ao terminal de porta.

### 2.3. Modelagem das associações de transistores MOS

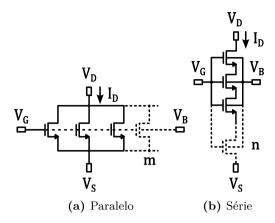

É possível observar na Figura 2.2 que a simetria intrínseca do transistor MOS é apropriada para a realização de associações equivalentes à um único dispositivo. Tais associações podem ser do tipo série ou paralelo conforme mostra-se na Figura 2.3.

Figura 2.3: Associações de transistores.

As associações de "m"transistores de mesmo comprimento de canal e terminais interligados em paralelo possibilitam a construção de um dispositivo equivalente a um transistor simples. A largura W deste dispositivo é resultante da soma das larguras de canal unitárias e com um comprimento L. Por outro lado, em associações série de "n"transistores de mesma largura de canal obtemos um dispositivo com comprimento equivalente à soma dos comprimentos unitários e uma largura W.

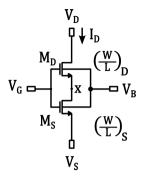

Para a modelagem das associações série na região triodo consideramos o diagrama apresentado na Figura 2.4. Esta configuração é chamada de trapezoidal tipo T [1] sendo inspirada no trabalho realizado por Riccó em [22].

A composição apresentada aqui consiste de dois transistores canal N conectados a partir do nó "X"ligando dreno e fonte de  $M_S$  e  $M_D$ , respectivamente, sendo os terminais de porta e substrato comuns à ambos os dispositivos.

Como pode ser observado em (2.1), a aproximação por canal gradual permite-nos escrever a corrente de dreno em função dos potenciais aplicados nos terminais de porta-fonte  $(I_F)$  e porta-dreno  $(I_R)$ . Para uma composição de transistores tal como a ilustrada na Figura 2.4 obtemos para o nó "X"

$$I(V_G, V_X) = \frac{\left(\frac{W}{L}\right)_S I(V_G, V_S) + \left(\frac{W}{L}\right)_D I(V_G, V_D)}{\left(\frac{W}{L}\right)_S + \left(\frac{W}{L}\right)_D}$$

(2.16)

Através de (2.16) e utilizando o modelo ACM temos que a cor-

Figura 2.4: Associação série tipo T [1].

rente de dreno para uma composição série de dois transistores é

$$I_D = \left(\frac{W}{L}\right)_{eq} [I(V_G, V_S) - I(V_G, V_D)]$$

(2.17)

em que

$$\left(\frac{W}{L}\right)_{eq} = \frac{\left(\frac{W}{L}\right)_S \left(\frac{W}{L}\right)_D}{\left(\frac{W}{L}\right)_S + \left(\frac{W}{L}\right)_D}.$$

(2.18)

A expressão (2.18) mostra que a corrente obtida através da associação série para transistores em região linear é similar à obtida com um transistor unitário cuja razão de aspecto seja equivalente. Para que fique mais claro podemos escrever a largura e comprimento de canal equivalentes

$$W_{eq} = W_D \tag{2.19}$$

е

$$L_{eq} = L_D + kL_S \tag{2.20}$$

em que  $k=W_D/W_S$ . Substituindo as expressões (2.18) e (2.19) em (2.20) obtemos

$$\left(\frac{W}{L}\right)_{eq} = \frac{W_D}{L_D + kL_S}.$$

(2.21)

### Capítulo 3

## Métodos para extração da tensão de limiar

Diversas metodologias foram propostas a partir dos anos 60 para extração da tensão de limiar  $(V_{T0})$ . A seguir são sumarizados alguns critérios a serem respeitados por parte dos métodos de caracterização [23]:

- 1) Ser válido em todas as tecnologias;

- **2)** Determinar a tensão de porta  $(V_G)$  onde a camada de inversão começa a ser criada;

- 3) Ser simples e de fácil aplicação.

Além do mais, em [24] há uma reformulação do item (2) onde acrescenta-se que a extração da tensão de limiar deve ser associada a uma definição clara de  $V_{T0}$  baseada em princípios físicos.

### 3.1. Métodos convencionais

Nesta seção são apresentadas as principais características bem como inconvenientes dos métodos convencionais utilizados na extração de parâmetros. Fazendo uso da característica de transferência  $(I_D - V_G)$  os métodos permitem a utilização do transistor em região triodo ou em saturação.

### 3.1.1. Método da Extrapolação Linear (EL)

O método de extrapolação na região linear é um dos métodos mais conhecidos e utilizados para medição da tensão de limiar [25]. Apresentado na Figura 3.1, este método é realizado a partir da extrapolação linear da curva de tranferência  $(I_D-V_G)$  do transistor. A tensão de limiar é determinada pela intersecção da tangente a curva no ponto de maior inclinação com  $I_D=0$  [26,27].

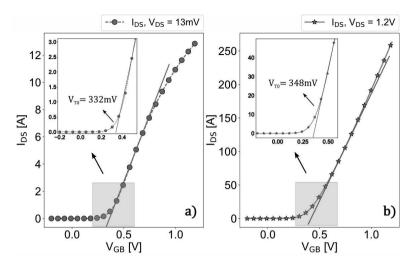

**Figura 3.1:** Método da Extrapolação Linear: a) Medição de  $V_{T0}$  na região triodo e b) região de saturação.

O grande incoveniente desta técnica está na determinação do valor máximo de transcondutância que é afetado pela degradação da mobilidade no canal e a presença de resistências parasitas em série nos terminais de dreno e fonte [28], sendo portanto não dependente só dos parâmetros intrínsecos do transistor. Com isso, a tensão de limiar fica dependente de efeitos de segunda ordem, tais como a degradação da mobilidade e as resistências série. Este resultado pode ser observado na Figura 3.1 que apresenta o método aplicado com o transistor operando na região de saturação ( $V_{DS}=1,2V$ ), obtendo um valor em torno de 20mV acima do encontrado com o mesmo dispositivo operando na região triodo.

### 3.1.2. Método Match-Point (MP)

Este método foi proposto na década de 90 em [29] e é pouco utilizado atualmente. O valor da tensão de limiar é obtido conforme o valor da tensão de porta correspondente à 6% de desvio na extrapolação de  $I_D-V_G$  no regime de inversão fraca. A Figura 3.2 apresenta a curva de transferência em escala semi-logarítmica tanto para a operação do transistor em região linear quanto na saturação.

Conforme observado, o método enfatiza o regime de inversão fraca, sendo o ponto negativo da técnica a dependência de tensão de

**Figura 3.2:** Método Match-Point: a) Extração de  $V_{T0}$  na região linear e b) região de saturação.

limiar com o desvio arbitrário, da curva  $I_D-V_G$  em relação a extrapolação no regime de inversão fraca.

Informações mais detalhadas sobre outros métodos de extração da tensão de limiar podem ser encontrados em [25]. Os métodos apresentados são o de derivada segunda (SD - Second Derivative) [30], derivada terceira (TD - Third Derivative) [31], razão da raiz de transcondutância por corrente (CsrTR - Current-to-square-root-of-the-Transconductance Ratio) [32], método de transição [33] entre outros. A maior parte desses métodos utilizam a expressão quadrática para corrente de dreno [21]

$$I_D = \frac{\mu C'_{ox} W (V_{GS} - V_{T0})^2}{2nL}$$

(3.1)

que por sua vez é definida somente no regime de inversão forte onde o mecanismo de deriva é predominante. Por outro lado, como a tensão de limiar ocorre no regime de inversão moderada onde tanto o mecanismo de difusão quanto o de deriva são importantes, os métodos analisados apresentam grandes imprecisões na determinação da tensão de limiar.

O maior inconveniente encontrado nos métodos tradicionais que utilizam os modelos baseados no regime de inversão forte está na falta de precisão no cálculo do potencial de superfície  $(\phi_s)$  [25]. Esses métodos adotam  $\phi_s$  constante quando a tensão de porta é maior que a

tensão de limiar  $(V_G > V_{T0})$  e da função linear de  $V_G$  quando  $V_G < V_{T0}$ , sendo necessário ajustes para relacionar as diferentes regiões de operação do transistor.

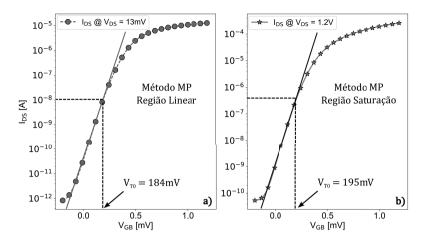

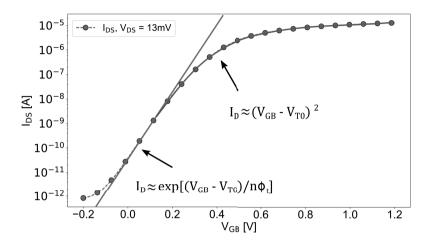

**Figura 3.3:** Aproximações de inversão forte e fraca da característica  $I_D$  -  $V_G$  do transistor.

Neste trabalho utiliza-se o modelo ACM, o qual permite a caracterização do transistor em todas as regiões de inversão [21]. Com isso, mostra-se a seguir dois métodos para extração dos parâmetros do transistor baseados no modelo ACM.

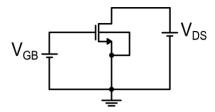

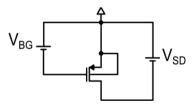

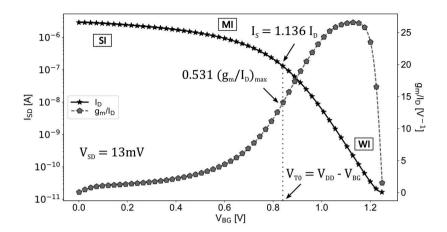

### 3.2. Método $g_m/I_D$

Este método utiliza o transistor operando em região triodo. A partir disto, evita-se os possíveis efeitos causados pela saturação da velocidade dos portadores e da modulação do comprimento de canal. Para realização do método é utilizada a configuração fonte comum representada na Figura 3.4 para transistores canal N.

O método utiliza-se da expressão (2.6), onde fica evidente que para  $i_f = 3$  e  $V_S = 0$  a tensão de *pinch-off* é nula e consequentemente  $V_{GB} = V_{T0}$ . A partir das expressões (2.1), (2.12) e (2.15) temos que

$$\frac{g_m}{I_D} = \frac{1}{I_D} \frac{\partial I_D}{\partial V_G} = \frac{g_{ms} - g_{md}}{nI_D} = \frac{2}{n\phi_t \left(\sqrt{1 + i_f} + \sqrt{1 + i_r}\right)}.$$

(3.2)

**Figura 3.4:** Configuração fonte comum de um transistor canal N para realização do método  $g_m/I_D$ .

De (3.2) é claro que o máximo valor de transcondutância por unidade de corrente ocorre no regime de inversão fraca profunda, tanto  $i_f$  como  $i_r \ll 1$

$$\left. \frac{g_m}{I_D} \right|_{\text{max}} = \frac{1}{n\phi_t}.\tag{3.3}$$

Considerando a tensão  $V_{DS}=\phi_t/2$  e aplicando-a em (2.6) obtémse  $i_r=2,\!1196$  para  $i_f=3$ . Substituindo estes valores em (3.2) calculase

$$\frac{g_m}{I_D} = \frac{2}{n\phi_t \left(\sqrt{1+3} + \sqrt{1+2,1196}\right)} = \frac{0,531}{n\phi_t} = 0,531 \left. \frac{g_m}{I_D} \right|_{\text{max}}. \quad (3.4)$$

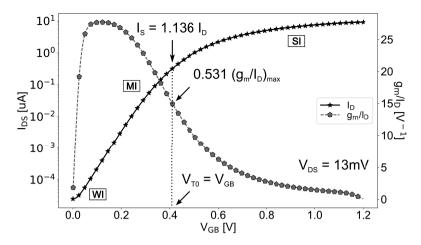

O resultado obtido com (3.4) permite a conclusão de que para um nível de inversão  $i_f=3$  e uma tensão  $V_{DS}=\phi_t/2,\ g_m/I_D$  atinge 53,1% do seu valor máximo. Também se pode comprovar em (2.1) que a corrente específica ( $I_S$ ) é igual à 1,136 vezes  $I_D$  ( $i_f=3$  e  $i_r=2,1196$ ). Este método pode ser resumido através do gráfico mostrado na Figura 3.5. O eixo-y esquerdo ilustra a corrente de dreno em função da tensão de porta, para os diferentes regimes de inversão. Neste mesmo gráfico, o lado direito do eixo-y representa a transcondutância por unidade de corrente calculada como a derivada logarítmica da corrente em relação a tensão de porta ( $\partial ln\ I_D/\partial\ V_G$ ) do transistor. Com isso, os pontos de extração da tensão de limiar e corrente específica do transistor estão ilustrados na curva seguindo as definições do método.

Os parâmetros de tensão de limiar e corrente específica são muito importantes para o projeto de circuitos e para a caracterização da tecnologia. Adicionalmente, estes parâmetros servirão de base para a extração de outras características do transistor tais como a mobilidade efetiva de portadores  $(\mu_{eff})$  e o fator de inclinação (n).

Figura 3.5: Corrente de dreno e transcondutância por unidade de corrente de um transistor canal N.

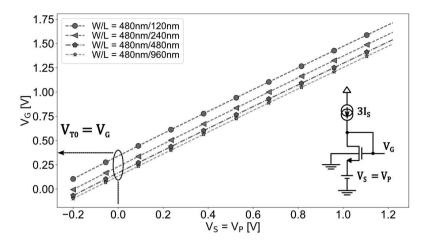

### 3.3. Método $3I_S$

O método adotado neste trabalho utiliza uma corrente igual a  $3I_S$  [19] que é função dos principais parâmetros do transistor e que  $I_S$  é a corrente específica obtida no método  $g_m/I_D$ .

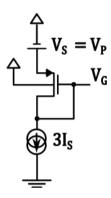

**Figura 3.6:** Configuração de um transistor canal N para realização do método  $3I_S$ .

A diferença com o método de corrente constante amplamente difundido na indústria é que este último utiliza uma corrente escolhida arbitrariamente e portanto se aplica sem modificações a qualquer tecnologia MOS. Para a realização do método  $3I_S$  será utilizada a configu-

ração ilustrada na Figura 3.6 permitindo o funcionamento do transistor em região de saturação. Tendo em vista que na saturação a corrente direta  $(I_F)$  é muito maior que a corrente reversa  $(I_R)$ , se pode escrever o nível de inversão como  $i_f = I_D/I_S = 3$  e consequentemente de (2.6),  $V_P = V_S$ .

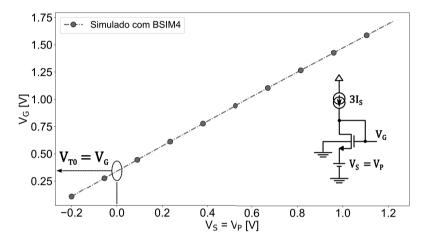

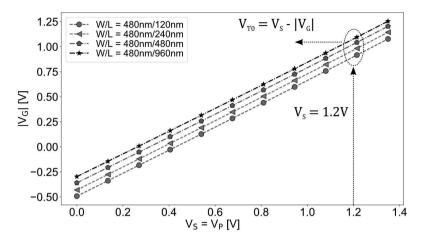

A tensão de limiar é obtida novamente para  $V_P = 0$  ( $V_G = V_{T0}$ ) conforme ilustrado na Figura 3.7.

**Figura 3.7:** Extração da tensão de limiar através do método  $3I_S$ .

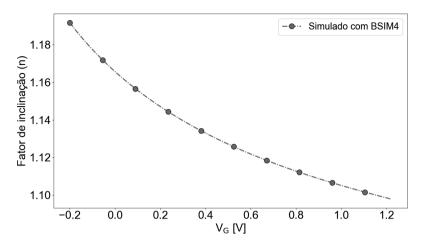

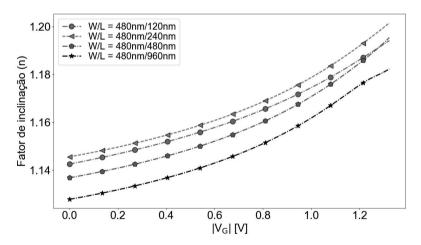

O fator de inclinação (rampa) é obtido com o método  $3I_S$  por meio da expressão [19]

$$n = \frac{1}{\left(\frac{\partial V_P}{\partial V_G}\right)}. (3.5)$$

A extração do fator de inclinação em função da tensão de porta é mostrado na Figura 3.8.

Como pôde ser observado, as vantagens no uso deste método está na rápida e direta extração da tensão de limiar e do fator de inclinação. Uma possível desvantagem do método devido a operação do transistor em região de saturação é a sensibilidade aos efeitos de canal curto [34]. Porém como os transistores operam muitas vezes na saturação, o método extrai os parâmetros na região apropriada.

No próximo capítulo são apresentadas as simulações realizadas com o modelo BSIM4. A partir das extrações poderão ser observadas as dependências dos parâmetros em função do comprimento do canal e

Figura 3.8: Extração do fator de inclinação através do método  $3I_S$ .

também realizar comparações entre os métodos estudados neste capítulo.

### Capítulo 4

# Simulações com LVTNFET utilizando o modelo BSIM4

Os transistores com baixa tensão de limiar (LVT - Low Voltage Threshold) disponibilizados pela GlobalFoundries CMOS 130nm utilizam o modelo BSIM4 no simulador elétrico de circuitos Spectre<sup>®</sup>. Este modelo compacto é baseado no conceito de tensão de limiar sendo aplicado nas mais diversas tecnologias nanométricas [35].

A Tabela 4.1 apresenta parâmetros relevantes da tecnologia CMOS 130nm os quais foram extraídos do documento de informações do processo de fabricação, PDK (*Process Design Kit*).

| Tabela 4.1: | Parâmetros | básicos | da | Tecnologia | CMOS | $130 \mathrm{nm}$ . |

|-------------|------------|---------|----|------------|------|---------------------|

|-------------|------------|---------|----|------------|------|---------------------|

| Transistor                                  | LVT                                                  |

|---------------------------------------------|------------------------------------------------------|

| Alim. [V]                                   | $1,\!2~(n\'ucleo)$ - $1,\!5~({\rm entrada/sa\'ida})$ |

| $W_{min}$ [nm]                              | 160                                                  |

| $\Delta W [\mathrm{nm}]$                    | 10 (NFET) - 40 (PFET)                                |

| $L_{min}$ [nm]                              | 120                                                  |

| $\Delta L \text{ [nm]}$                     | 28                                                   |

| $t_{ox}$ [nm]                               | $2,2\pm0,15$                                         |

| $C_{ox}^{'}~[\mathrm{fF}/\mu~\mathrm{m}^2]$ | 15,97                                                |

Conforme ilustrado na Tabela 4.1, as tensões de alimentação disponíveis são de 1,2V e 1,5V. A largura e comprimento mínimo do canal dos transistores é representada por  $W_{min}$  e  $L_{min}$  respectivamente.  $\Delta W$  é a variação da largura do canal em função da invasão do óxido de porta nas regiões ativas do transistor e  $\Delta L$ , a variação do comprimento do canal com as difusões laterais resultantes do processo de fabricação.

A espessura do óxido de porta é dada por  $t_{ox}$  e  $C'_{ox}$ , a capacitância do óxido por unidade de área.

# 4.1. Extração de parâmetros com o método $g_m/I_D$

A seguir são mostrados os resultados obtidos através das simulações em ambiente Cadence Virtuoso Spectre Regional Para estas análises foram considerados transistores canal N simulados em temperatura de 26°C. Os resultados adquiridos aqui podem ser estendidos aos transistores canal P cujas análises estão sumarizadas no  $Apêndice\ A$  -  $Extração\ de\ parâmetros\ simulados\ do\ transistor\ LVTPFET$ .

A partir da característica de transcondutância por unidade de corrente  $(g_m/I_D)$  ilustrada na Figura 3.5 calcula-se o valor da tensão de limiar  $(V_{T0})$  e a corrente específica correspondente a uma determinada razão de aspecto geométrico W/L.

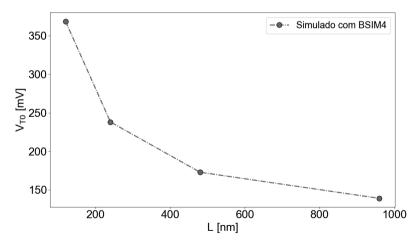

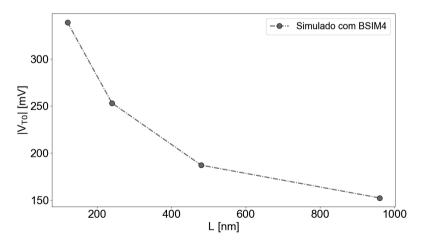

#### 4.1.1. Tensão de limiar

Na Figura 4.1 é apresentada a tensão de limiar, obtida pelo método  $g_m/I_D$ , onde o transistor opera em região linear. Para esta simulação são utilizados transistores unitários tipo N de diferentes comprimentos de canal com  $3W_{min}=480 \mathrm{nm}$ .

Figura 4.1: Tensão de limiar em função do comprimento do canal.

Através da simulação realizada observa-se um decréscimo de 230mV na tensão de limiar para um aumento de oito vezes do comprimento do

canal em relação ao comprimento mínimo. Este resultado mostra que o modelo BSIM4 leva em consideração os efeitos de canal curto reverso (RSCE) originados pelo uso dos implantes *pocket*.

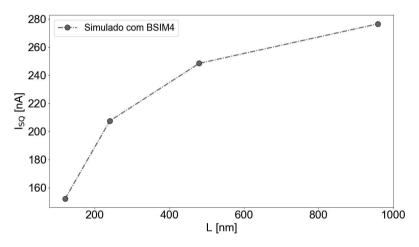

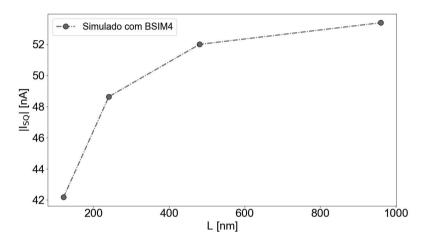

### 4.1.2. Corrente específica de folha

A seguir é apresentada na Figura 4.2 a corrente específica de folha obtida pelo método  $g_m/I_D$ , para diversos comprimentos de canal.

Figura 4.2: Corrente específica de folha em função do comprimento do canal.

Observa-se através da curva que há um aumento de 55% na corrente específica de folha com o comprimento do canal. Este resultado pode ser explicado por um aumento da mobilidade com o incremento do comprimento do canal, o que é razoável. Com efeito para canais curtos a dopagem dos implantes *pocket* é predominante mas para canais longos a dopagem mais baixa do substrato prevalece. Como a mobilidade é uma função decrescente da dopagem, os transistores com canais mais longos apresentam uma mobilidade efetiva mais elevada.

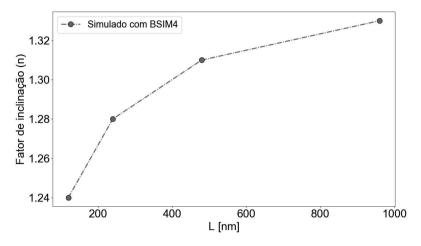

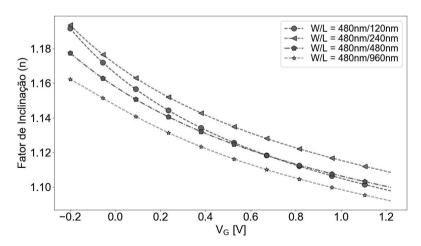

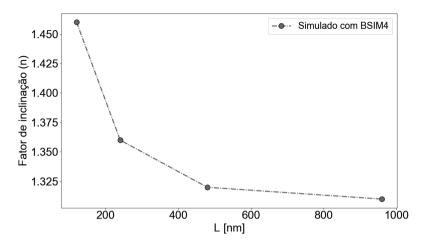

### 4.1.3. Fator de inclinação

Outro importante parâmetro a ser caracterizado através do método  $g_m/I_D$  é o fator de inclinação. Esta característica pode ser extraída através de (3.3). Sendo assim, a Figura 4.3 mostra a variação de n em função do comprimento do canal.

Figura 4.3: Fator de inclinação em função do comprimento do canal.

Pode-se observar uma diferença no fator de inclinação de mais de 8% a partir da variação do canal. O aumento deste parâmetro com o comprimento do canal e consequentemente com a diminuição de dopagem medida não tem um significado físico já que  $n=1+C_b^\prime/C_{ox}^\prime$  e a capacitância de depleção por unidade de área é uma função crescente de dopagem como pode ser verificado através de

$$C_b' = \frac{\sqrt{2q\epsilon_s N_A}}{2\sqrt{\phi_{sa} - \phi_t}} \tag{4.1}$$

em que q representa a carga elementar do elétron que equivale a  $1,6 \times 10^{-19} \mathrm{C}$ ,  $\epsilon_s$  é a permissividade do semicondutor,  $N_A$  a concentração de dopantes aceitadores no semicondutor,  $\phi_{sa}$  é o potencial de superfície no semicondutor em inversão fraca profunda e  $\phi_t$  a tensão térmica.

Como há um forte impacto da dopagem utilizada nos implantes pocket em comprimentos mais curtos de canal (isto é, L = 120nm e L = 240nm) e em contrapartida, uma maior uniformidade da dopagem em comprimentos mais longos, a curva extraída através da simulação deveria apresentar característica oposta à obtida.

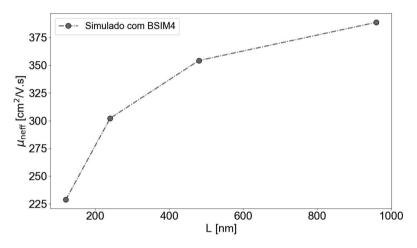

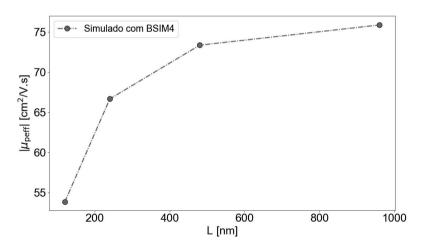

### 4.1.4. Mobilidade de portadores

Através da tensão de limiar  $(V_{T0})$ , corrente específica  $(I_S)$  e fator de inclinação (n), extraídos através do método  $g_m/I_D$ , pode-se obter a

mobilidade efetiva de portadores  $(\mu_{neff})$  com

$$\mu_{neff} = \frac{2I_{SQ}}{nC_{ox}'\phi_t^2}. (4.2)$$

A Figura 4.4 ilustra o comportamento obtido em relação à dependência da mobilidade efetiva de elétrons (isto é, referindo-se a transistores canal N) com o comprimento do canal.

Figura 4.4: Mobilidade efetiva em função do comprimento do canal.

Como esperado, a mobilidade dos portadores aumenta na mesma taxa que a corrente específica de folha.

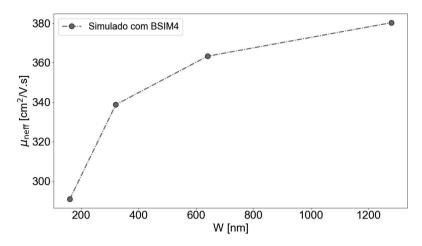

# 4.1.5. Avaliação do impacto da largura do canal nos parâmetros dos transistores

Até o presente momento compreendeu-se apenas os efeitos causados pelo aumento do comprimento do canal nos diversos parâmetros do transistor, mantendo  $3W_{min}=480 \mathrm{nm}$ . As próximas análises tem o objetivo contrário, ou seja, são observados os impactos causados pela variação na largura do canal mantendo  $4L_{min}=480 \mathrm{nm}$ .

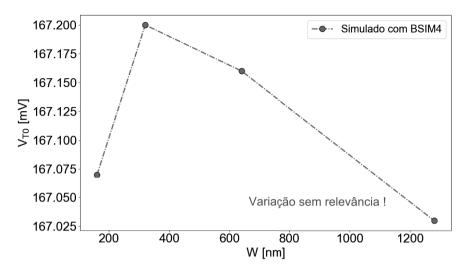

#### 4.1.5.1. Tensão de limiar

A Figura 4.5 mostra a dependência da tensão de limiar com a largura do canal.

Figura 4.5: Tensão de limiar em função da largura do canal.

Ao contrário do resultado obtido na análise da variação do comprimento do canal, observamos na Figura 4.5 que a tensão de limiar não é praticamente afetada com o aumento da largura do canal.

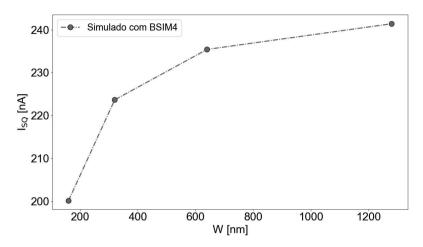

### 4.1.5.2. Corrente específica de folha

O gráfico da corrente específica de folha em função da largura do canal é mostrado na Figura 4.6. Pode-se observar que ocorre um aumento em torno de 17% na corrente específica de folha medida entre a largura mínima e máxima simuladas.

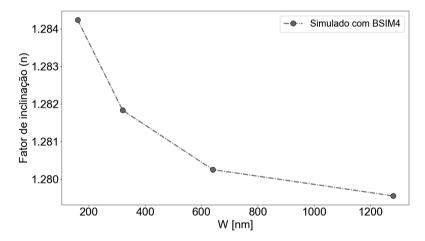

### 4.1.5.3. Fator de inclinação

O fator de inclinação obtido em simulação é mostrado na Figura 4.7. Em contrapartida ao apresentado com o aumento do comprimento do canal, observa-se aqui que este parâmetro não muda praticamente com a variação da largura do canal.