## UNIVERSIDADE FEDERAL DE SANTA CATARINA DEPARTAMENTO DE INFORMÁTICA E ESTATÍSTICA

Gabriel Arthur Gerber Andrade

# ANÁLISE COMPARATIVA ENTRE DOIS VERIFICADORES DE CONSISTÊNCIA E DE COERÊNCIA DE MEMÓRIA

Florianópolis - Santa Catarina

### Gabriel Arthur Gerber Andrade

# ANÁLISE COMPARATIVA ENTRE DOIS VERIFICADORES DE CONSISTÊNCIA E DE COERÊNCIA DE MEMÓRIA

Trabalho de Conclusão de Curso submetido ao Curso de Bacharelado em Ciências da Computação da Universidade Federal de Santa Catarina para a obtenção do Grau de Bacharel em Ciências da Computação. Orientador: Prof. Dr. Luiz Cláudio Villar dos Santos Universidade Federal de Santa Catarina

Florianópolis - Santa Catarina

| Prog | Ficha de identificação da obra elaborada pelo autor através do rama de Geração Automática da Biblioteca Universitária da UFSO |

|------|-------------------------------------------------------------------------------------------------------------------------------|

| Prog |                                                                                                                               |

| Prog | rama de Geração Automática da Biblioteca Universitária da UFSO  A ficha de identificação é elaborada pelo próprio autor       |

| Prog | rama de Geração Automática da Biblioteca Universitária da UFSO                                                                |

### Gabriel Arthur Gerber Andrade

# ANÁLISE COMPARATIVA ENTRE DOIS VERIFICADORES DE CONSISTÊNCIA E DE COERÊNCIA DE MEMÓRIA

Este Trabalho de Conclusão de Curso foi julgado aprovado para a obtenção do Título de "Bacharel em Ciências da Computação", e aprovado em sua forma final pelo Curso de Bacharelado em Ciências da Computação da Universidade Federal de Santa Catarina.

Prof. Dr. Renato Cislaghi

Universidade Federal de Santa Catarina

Coordenador

Banca Examinadora:

Prof. Dr. Luiz Cláudio Villar dos Santos

Universidade Federal de Santa Catarina

Orientador

Prof. Dr. José Luís Almada Güntzel

Universidade Federal de Santa Catarina

Prof. Dr. José Luís Almada Güntzel

Universidade Federal de Santa Catarina

Universidade Federal de Santa Catarina

### **AGRADECIMENTOS**

À minha família, pelo apoio incondicional e pelo incentivo em concluir esta etapa da minha vida.

Aos meu amigos, por todo o suporte nas pequenas e grandes causas.

Ao meu orientador, Prof. Dr. Luiz Cláudio Villar dos Santos, pelas significativas sugestões e contribuições.

Aos membros da banca, Prof. Dr. José Luís Almada Güntzel e Prof. Dr. Djones Vinicius Lettni, pelas diversas contribuições recebidas na avaliação do trabalho.

Aos colegas do ECL e NIME. Em especial a Eberle A. Rambo, Leandro S. Freitas e Olav P. Henschel por todas as contribuições diretas na realização deste trabalho.

Ao CNPq, pela bolsa de iniciação científica.

### RESUMO

Quanto antes um erro de projeto for detectado, menor será seu impacto no custo de desenvolvimento de um sistema computacional. Por isso, é necessário iniciar-se o processo de verificação antes mesmo de ser produzido um protótipo do sistema, ou seja, durante a etapa pré-silício. Nesta etapa, a verificação é realizada em uma representação do sistema sob projeto. O subsistema de memória compartilhada usado em multicores é extremamente complexo e sujeito a erros de projeto. A verificação deste subsistema busca averiguar se, para uma dada execução de um programa concorrente, o comportamento observado no hardware obedece à sua especificação, i.e. a um modelo de memória formalmente especificado, que captura aspectos de consistência e coerência da memória compartilhada. A complexidade desse problema de verificação depende da observabilidade de eventos em memória. Quando a verificação é feita em protótipo, a observabilidade é limitada pelo hardware a um único trace por processador. Assim, o problema de verificação é intratável no caso geral. Entretanto, como a observabilidade é virtualmente ilimitada em representações executáveis, a verificação pré-silício recai em problemas mais simples. Por isso, técnicas de verificação pré-silício são mais eficientes e eficazes do que técnicas pós-silício, como foi comprovado, durante os últimos anos, através da comparação experimental entre verificadores pré-silício desenvolvidos por mestrandos da UFSC (e.g. Rambo (2012), Freitas (2012)) e outros que representam o estado da arte em verificação pós-silício (e.g. Shacham et al. (2008)). A presente monografia relata uma comparação experimental da técnica proposta por Freitas com a implementação realizada, em conjunto com Olav Philipp Henschel, do verificador XCHECK (HU et al., 2012) – o estado da arte dos verificadores pós-silício baseados em inferência.

Palavras-chave: Verificação. Consistência de Memória. Sistema multi-core.

### **ABSTRACT**

The sooner a design error is detected, the lower the impact on the cost of developing a computer system. Therefore, it is necessary to begin the verification process even before it is produced a prototype of the system, i.e. during the pre-silicon stage. At this stage, the checking is performed on a representation of the design under verification. The shared memory subsystem used in multicores is extremely complex and subject to design errors. The verification of this subsystem seeks to confirm whether, for a given execution of a concurrent program, the behavior observed in the hardware obeys its specification, i.e. to a formally specified memory model that captures aspects of consistency and coherence of the shared memory. The complexity of this problem depends on the verification observability of events in memory. When the verification is done on the prototype, the observability is limited by the hardware to a single trace per processor. In this case, the verification problem is intractable for the general case. However, as the observability is virtually unlimited into executable representations, pre-silicon verification lies on simpler problems. Therefore, techniques for pre-silicon verification are more efficient and effective than post-silicon techniques, as evidenced, in recent years, by experimental comparison between pre-silicon checkers developed by masters of UFSC (e.g. Rambo (2012), Freitas (2012)) and others representing state of the art post-silicon checkers (eg Shacham et al. (2008)). This monograph presents a experimental comparation between the technique developed by Freitas with the implentation done in conjunction with Olav Philipp Henschel of the checker XCHECK (HU et al., 2012) – the state of the art of post-silicon cherckers based on inference.

**Keywords:** Verification. Memory Consistency. Multi-core system.

# LISTA DE FIGURAS

| -                      | Exemplo ilustrativo para diferentes modelos de memória (HENS 14, p. 20)                                                                                                                                                                                       |    |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                        | Um programa, seus traces e dois comportamentos atômicos IEL, 2014, p. 30)                                                                                                                                                                                     | 40 |

| -                      | Ordenamento de eventos sob forte atomicidade de escrita (HENS 14, p. 30)                                                                                                                                                                                      |    |

| _                      | Um modelo genérico de sistema memória compartilhada (HENS 14, p. 32)                                                                                                                                                                                          |    |

| Figura 5               | Um comportamento                                                                                                                                                                                                                                              | 52 |

| -                      | Os dois recursos do XCHECK para ordenar as operações de do comportamento da Figura 5                                                                                                                                                                          | 53 |

| Figura 7               | As ordens necessárias para garantir a leitura de um dado valor                                                                                                                                                                                                | 54 |

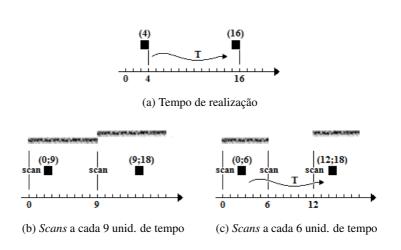

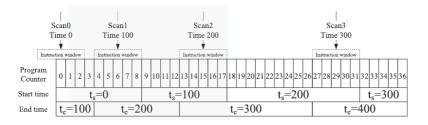

| rações rea<br>Figura 9 | Três cenários sobre ordens temporais, considerando duas opelizadas globalmente nas unid. de tempo 4 e 16, respectivamente Os instantes de tempo $\tau_s$ e $\tau_e$ das operações de memória baserogram counter e no tamanho da janela de instruções (igual a | 57 |

| _                      | al., 2012, p. 511)                                                                                                                                                                                                                                            | 60 |

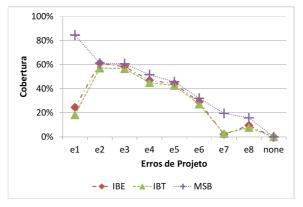

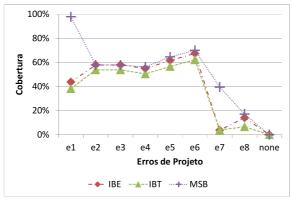

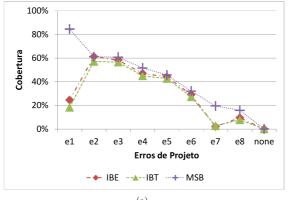

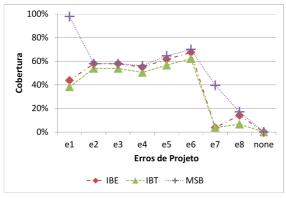

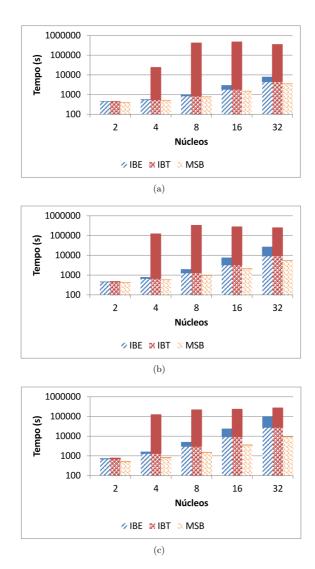

| Figura 10              | Eficácia por erro de projeto                                                                                                                                                                                                                                  | 88 |

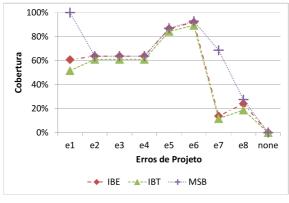

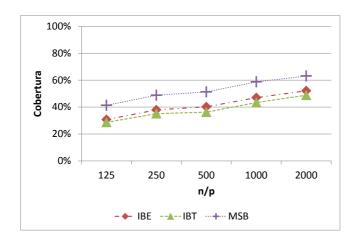

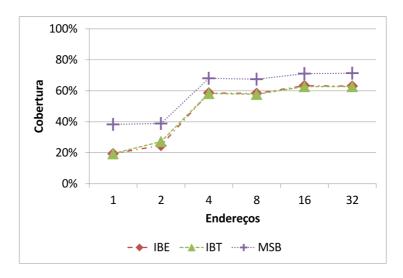

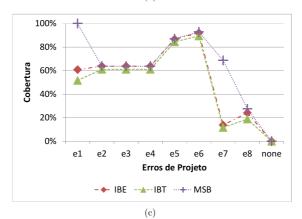

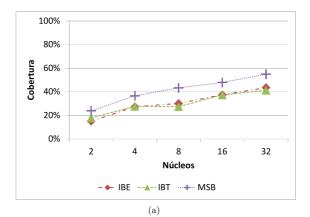

| Figura 11              | Eficácia para casos de testes com tamanho crescente                                                                                                                                                                                                           | 90 |

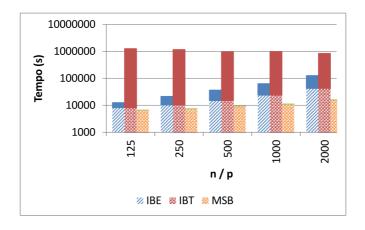

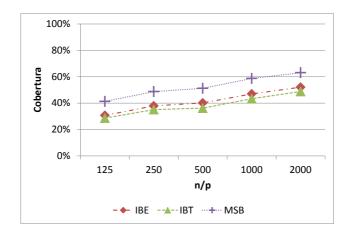

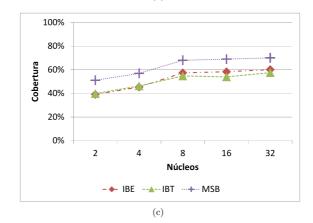

| Figura 12              | Eficiência para casos de testes com tamanho crescente                                                                                                                                                                                                         | 90 |

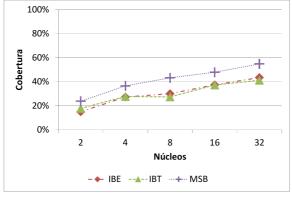

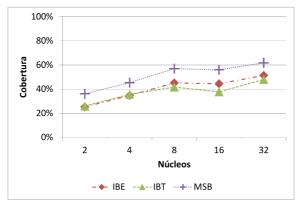

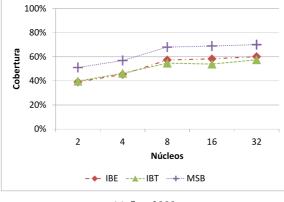

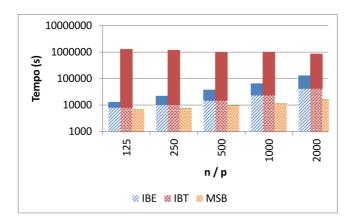

| Figura 13              | Eficácia pelo número de núcleos de processamento                                                                                                                                                                                                              | 92 |

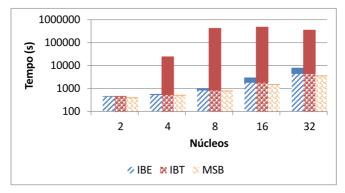

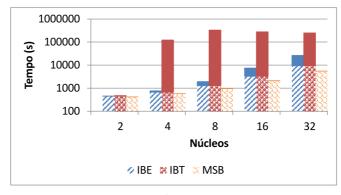

| Figura 14              | Eficiência pelo número de núcleos de processamento                                                                                                                                                                                                            | 93 |

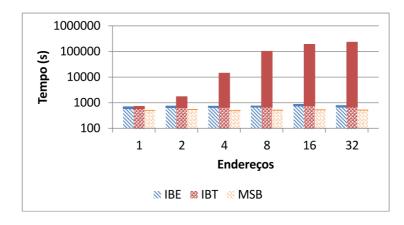

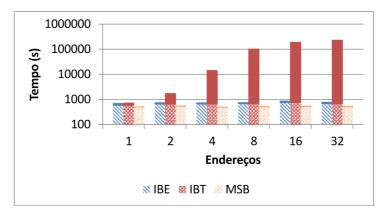

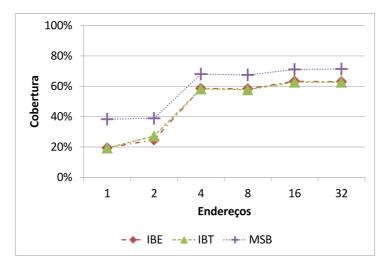

| Figura 15              | Eficiência pelo número de endereços                                                                                                                                                                                                                           | 95 |

| Figura 16              | Eficácia pelo número de endereços                                                                                                                                                                                                                             | 95 |

# LISTA DE TABELAS

|            | Categorização simples dos modelos relaxados (ADVE; GHA-         |     |

|------------|-----------------------------------------------------------------|-----|

| RACHOR     | LOO, 1996, p. 12)                                               | 34  |

| Tabela 2   | Principais características dos verificadores dinâmicos (HENS-   |     |

| CHEL, 20   | 14)                                                             | 46  |

| Tabela 3   | Caracterização dos erros de projeto inseridos, propositalmente, |     |

| durante os | experimentos (HENSCHEL, 2014, p. 47)                            | 82  |

| Tabela 4   | Proporções para cada tipo de operação (HENSCHEL, 2014) .        | 86  |

| Tabela 5   | Responsáveis pelas implementações dos verificadores utiliza-    |     |

| dos        |                                                                 | .00 |

| Tabela 6   | Contribuições para a implementação de IBE e IBT 1               | 00  |

| Tabela 7   | Os erros de projeto e os seus respectivos responsáveis 1        | 00  |

|            |                                                                 |     |

# LISTA DE ABREVIATURAS E SIGLAS

| DUV     | Design Under Verification                                     | 25  |

|---------|---------------------------------------------------------------|-----|

| ISA     | Instruction Set Architecture                                  | 25  |

| MM      | Modelo de Memória                                             | 25  |

| ECL     | Embedded Computing Lab                                        | 29  |

| UFSC    | Universidade Federal de Santa Catarina                        | 29  |

| MM      | Modelo de Memória                                             | 31  |

| RMW     | Read-modify-write                                             | 33  |

| SC      | Sequential Consistency                                        | 33  |

| TSO     | Total Store Order                                             | 34  |

| PC      | Processor Consistency                                         | 34  |

| Partial | Store.Ordering                                                | 34  |

| Weak O  | rderjing                                                      | 34  |

| ROB     | Reorder Buffer                                                | 41  |

| PC      | Program Counter                                               | 59  |

| CPU     | Unidade Central de Processamento                              | 73  |

| ICT     | Institute of Computing Technology                             | 73  |

| CAS     | Chinese Academy of Sciences                                   | 73  |

| WWA     | Weak Write Order                                              | 79  |

| HTML    | HyperText Markup Language                                     | 81  |

| MSB     | Multi-ScoreBoard, apelido para a técnica de (FREITAS; RAME    | 3O; |

|         | SANTOS, 2013)                                                 | 87  |

| IBT     | Inference with BackTracking, apelido para a técnica de (HU et |     |

|         | al., 2012)                                                    | 87  |

| IBE     | Inference Best Effort, apelido para a versão simplificada da  | 07  |

|         | técnica de (HU et al., 2012)                                  | 87  |

# LISTA DE SÍMBOLOS

| *         | Monitor no buffer de reordenamento (ROB) de algum processa- |    |

|-----------|-------------------------------------------------------------|----|

|           | dor                                                         | 41 |

| $\oplus$  | Monitor na saída da unidade de commit de algum processador  | 41 |

| $\ominus$ | Monitor na interface da cache privada de algum processador  | 41 |

| p         | número de unidades processantes                             | 42 |

| n         | número total de operações de memória                        | 42 |

# SUMÁRIO

| 1     | INTRODUÇAO                                               | 25 |

|-------|----------------------------------------------------------|----|

| 1.1   | MOTIVAÇÃO PARA A VERIFICAÇÃO                             | 25 |

| 1.2   | O QUE VERIFICAR                                          | 25 |

| 1.3   | QUANDO VERIFICAR                                         | 27 |

| 1.4   | JUSTIFICATIVA E ESCOPO DESTA MONOGRAFIA                  | 29 |

| 1.5   | ORGANIZAÇÃO DESTA MONOGRAFIA                             | 29 |

| 2     | MODELOS DE MEMÓRIA (MM)                                  | 31 |

| 2.1   | EXEMPLO ILUSTRATIVO                                      | 32 |

| 2.2   | A COLETÂNIA DE MODELOS DE MEMÓRIA                        | 33 |

| 2.3   | O DILEMA                                                 | 35 |

| 2.4   | AS ORDENS ENTRE OPERAÇÕES DE MEMÓRIA                     | 35 |

| 2.4.1 | Ordem de programa                                        | 36 |

| 2.4.2 | Ordem de processador                                     | 36 |

| 2.4.3 | Ordem de execução                                        | 37 |

| 2.4.4 | Ordem global                                             | 37 |

| 2.4.5 | Ordem temporal                                           | 38 |

| 3     | PROBLEMA-ALVO                                            | 39 |

| 3.1   | A OBSERVABILIDADE NA PLAFATORMA                          | 41 |

| 3.2   | FORMULAÇÃO DO PROBLEMA                                   | 42 |

| 4     | TRABALHOS CORRELATOS                                     | 45 |

| 4.0.1 | Verificação post-mortem                                  | 45 |

| 4.0.2 | Verificação on-the-fly                                   | 47 |

| 4.1   | O INTERESSE NA COMPARAÇÃO QUANTITATIVA EN-               |    |

|       | TRE AS TÉCNICAS DE VERIFICAÇÃO                           | 48 |

| 5     | XCHECK                                                   | 51 |

| 5.1   | EXEMPLO ILUSTRATIVO                                      | 52 |

| 5.2   | ORDEM DE TEMPO FÍSICO                                    | 56 |

| 5.2.1 | A Ordem de Tempo Físico                                  | 56 |

| 5.2.2 | Intervalo de Espera                                      | 58 |

| 5.2.3 | Obtendo os intervalos de tempo                           | 59 |

| 5.3   | GRAFO DE FRONTEIRAS                                      | 60 |

| 5.3.1 | Fronteira de Memória                                     | 61 |

| 5.3.2 | Extensão de fronteira                                    | 62 |

| 5.3.3 | Formulação do Grafo de Fronteiras                        | 63 |

| 5.3.4 | Como o XCHECK utiliza o conceito de Grafo de Fronteiras? | 64 |

| 5.4   | CONSTRUÇÃO DO GRAFO DE EXECUÇÃO                          | 66 |

| 5.5   | INFERÊNCIA                                               | 67 |

| 5.6   | CHECAGEM DE CICLOS                           | 69  |

|-------|----------------------------------------------|-----|

| 5.7   | VISÃO GERAL SOBRE OS DETALHES DE IMPLEMEN-   |     |

|       | TAÇÃO                                        | 71  |

| 5.7.1 | Expansão do Grafo de Fronteiras              | 73  |

| 5.7.2 | Decisão sobre inferência                     | 74  |

| 5.7.3 | Implementação do Grafo de Fronteiras         | 74  |

| 5.7.4 | Refinamento dos traces e o pré-processamento | 75  |

| 5.7.5 | Processamento das operações especiais        | 77  |

| 6     | INFRAESTRUTURA EXPERIMENTAL E RESULTADOS     |     |

|       | OBTIDOS                                      | 79  |

| 6.1   | A PLATAFORMA DE TESTES                       | 79  |

| 6.1.1 | Visão geral acerca do gem5                   | 80  |

| 6.1.2 | Etapa 1: Compilação dos módulos do gem5      | 82  |

| 6.1.3 | Etapa 2: Geração dos casos de teste          | 83  |

| 6.1.4 | Etapa 3: Experimentos                        | 84  |

| 6.1.5 | Etapa 4: Síntese                             | 85  |

| 6.2   | CONFIGURAÇÃO EXPERIMENTAL                    | 86  |

| 6.3   | SENSIBILIDADE AO TIPO DE ERRO                | 87  |

| 6.4   | IMPACTO DO NÚMERO CRESCENTE DE OPERAÇÕES     | 89  |

| 6.5   | IMPACTO DO NÚMERO CRESCENTE DE PROCESSADO-   |     |

|       | RES                                          | 91  |

| 6.6   | IMPACTO DO NÚMERO CRESCENTE DE ENDEREÇOS     | 94  |

| 7     | CONCLUSÃO                                    | 97  |

| 7.1   | ÚLTIMAS CONSIDERAÇÕES                        | 97  |

| 7.2   | TRABALHOS FUTUROS                            | 99  |

| 7.3   | RECONHECIMENTOS                              | 100 |

|       | REFERÊNCIAS                                  | 101 |

|       |                                              | 109 |

|       | ^                                            | 127 |

|       |                                              |     |

# 1 INTRODUÇÃO

# 1.1 MOTIVAÇÃO PARA A VERIFICAÇÃO

Todo projeto de *hardware* é construído em cima da sua especificação realizada entre uma fabricante e o seu cliente. Nela estão descritas todas as características e os comportamentos que o cliente deseja para o *hardware*, o qual, por sua vez, a fabricante se compromete a desenvolver.

Este compromisso significa que, caso a fabricante quebre esta especificação (ou se preferir, contrato), não apenas terá que compensar, de alguma forma, o seu cliente como, também, que a sua reputação terá sido prejudicada.

Por estes motivos existe, durante o projeto de criação do *hardware*, atividades que verificam a conformidade do sistema em desenvolvidamento (DUV) com a sua especificação (e.g. ISA e MM).

Toda causa de algum comportamento indesejado pelo sistema com relação à sua especificação é denominada por "erro de projeto".

### 1.2 O QUE VERIFICAR

Todos os componentes do DUV são sujeitos a verificação de três características: (1) funcionalidade (feita pela verificação funcional). Diz respeito a saber se o seu comportamento ocorre de acordo com a expectativa desejada; (2) restrições de desempenho (verificação de desempenho). Concernente aos recursos (e.g. tempo, memória) utilizados pelo seu comportamento; e (3) restrições de prazo (verificação de temporização). Relacionadas à apresentação de certos resultados em um tempo especificado. Para mais informações, o leitor pode consultar tanto o site www.sei.cmu.edu/cyber-physical/index.cfm quanto o livro de Baier e Katoen (2008).

Repare que a verificação descrita até então diz respeito a todo o sistema do hardware desenvolvido. Assim, naturalmente, esta verificação também deve ser aplicada aos seus módulos internos como, por exemplo, o sistema de memória, um elemento central que aparece em grande parte dos projetos desta natureza.

Nos últimos anos, a complexidade da memória impeliu pesquisas sobre técnicas específicas para a sua verificação, denominada de verificação de memória em referência a sua especificação ser o modelo de memória (MM). Os resultados de tais pesquisas estão disponibilizados na literatura atual.

No entanto, esta mesma complexidade afeta de tal modo a sua

verificação funcional que as técnicas até então desenvolvidas não têm se mostrado capazes de tratar a contento o problema ideal de sua corretude (CHATTERJEE; SIVARAJ; GOPALAKRISHNAN, 2002 apud HENSCHEL, 2014, p. 37): dado um modelo de memória (o qual é a especificação do sistema de memória) e uma implementação de um sistema com múltiplos processadores, verifique se todas as execuções geradas por este sistema satisfazem o modelo para qualquer programa paralelo.

Desta forma, existem duas linhas alternativas: a verificação estática e a verificação dinâmica.

De acordo com HENSCHEL, a verificação estática (ou abordagem matemática) (HENZINGER; QADEER; RAJAMANI, 1999; CHATTERJEE; SIVARAJ; GOPALAKRISHNAN, 2002; ABTS; SCOTT; LILJA, 2003) trata instâncias simplificadas deste problema: busca provar matematicamente a corretude de uma **abstração** da real implementação com a especificação do modelo de memória. Esta abordagem é estática e capaz de encontrar erros nos estágios iniciais do projeto (e.g. erros de protocolo). Entretanto, ela deixa escapar erros de projeto originados durante os estágios posteriores: na implementação (HENSCHEL, 2014, p. 37).

A verificação dinâmica (ou baseada em simulação) limita-se em demonstrar a incorretude do sistema por meio de um contra-exemplo. Ou seja, busca encontrar alguma execução (estimulada por algum programa paralelo, caso de teste) em que o comportamento do sistema é contraditório ao especificado. O leitor pode encontrar mais informações sobre este tipo verificação no livro de Lee e Seshia (2011).

Assim, o ponto forte da verificação dinâmica, segundo HENSCHEL, está na capacidade de exercitar todos os detalhes do sistema: o *hardware* real (e.g. Hangal et al. (2004), Roy et al. (2006), Manovit (2005), Manovit e Hangal (2006), Chen et al. (2009), Hu et al. (2012)), um protótipo (e.g. Lenoski et al. (1990)), e sua representação executável (e.g. Shacham et al. (2008), Rambo, Henschel e Santos (2012), Freitas, Rambo e Santos (2013)) (HENSCHEL, 2014, p. 37).

O seu ponto fraco está na dificuldade em alcançar a completude, i.e. em garantir a inexistência de erros de projeto. Afinal, o resultado de sua verificação diz respeito somente às execuções exercitadas (pelos programas paralelos). E, normalmente, estas últimas são apenas uma amostragem do universo de todas as execuções possíveis do sistema.

Alguns métodos dinâmicos utilizam uma versão confiável do DUV, com relação ao especificado, para facilitar a sua verificação. Esta versão, denominada por modelo de referência, é executada junto com o DUV, permitindo que a verificação se transforme em um teste de equivalência: os resultados obtidos pelo DUV são equivalentes aos obtidos pelo modelo de

#### referência?

Porém, quando o modelo de referência não está disponível, os métodos necessitam avaliar o conjunto de todas as execuções possíveis do programa paralelo (caso de teste) que são permitidas pelo modelo de memória (especificação). As vezes, o modelo é rígido o suficiente para permitir uma única execução para um certo programa. No entanto, quando isto não ocorre, os métodos necessitam detalhar uma execução e evidenciar a sua conformidade com o especificado no modelo. Caso contrário, os métodos estariam a mercê da possibilidade de esta liberdade dada à memória ter ocultado alguma decisão incorreta por sua parte (i.e. um comportamento indesejado).

O detalhamento de uma execução é feito por meio de uma busca heurística sobre toda execução possível que não omite nenhuma decisão feita pelo sistema de memória.

A fim de reduzir esta busca, algumas técnicas de verificação dinâmica (os verificadores por inferência) utilizam-se do método de inferências, i.e. sempre que pressupõem alguma nova decisão, tomada unicamente pelo sistema de memória, usam as regras especificadas pelo modelo para explorá-la o máximo possível.

Por fim, as características complementares e as desvantagens inerentes às abordagens formais e aos métodos dinâmicos motivam a sua combinação (ABTS; SCOTT; LILJA, 2003) como estratégia para reduzir o esforço total de verificação (HENSCHEL, 2014, p. 37).

Apresentado o contexto acima, há que se esclarecer que esta monografia irá lidar apenas com a verificação funcional do sistema de memória, objeto de seu estudo.

### 1.3 QUANDO VERIFICAR

O custo para corrigir um erro de projeto e, consequentemente, o custo do próprio projeto, aumenta conforme mais tarde este primeiro for detectado ao longo do seu processo de desenvolvimento do produto. Logo, há o interesse em realizar as técnicas de verificação durante o *design* do sistema (fase pré-silício).

Por outro lado, após o *hardware* ser fabricado em silício (i.e. na fase pós-silício) a verificação se torna tão difícil que não há técnica para esta fase que garanta a inexistência de erros de projeto. É por esta razão que a verificação nesta fase é degradada a um "teste de verificação".

A maioria das técnicas para a verificação funcional da memória são projetadas para a fase pós-silício e, quando necessário, são adaptadas para a pré-silício. Afinal, por muito tempo houve a tentativa de reduzir a complexi-

dade da verificação para pós-silício. Isto é, houve uma busca por uma complexidade linear no tempo de verificação com relação ao número de operações de memória, as quais compõem os programas paralelos (os casos de teste).

"Alguns dos verificadores projetados para o uso pós-silício necessitam de modificações no *hardware* do subsistema de memória" (HENSCHEL, 2014, p. 38). E, assim, conseguem alcançar a complexidade linear desejada. Conforme o próprio exemplo que o referido autor cita, DEORIO; WAGNER; BERTACCO (DEORIO; WAGNER; BERTACCO, 2009) modifica a hierarquia de memória e a interconexão para observar o mapeamento entre leituras e escritas e a ordem total de escritas.

Entretanto, corroborando com HENSCHEL, "alguns projetos industriais podem não prever o uso dedicado de *hardware* para a verificação de memória. O que significa que a utilização das técnicas anteriores impactaria em um custo maior para o projeto. É por isto que diversos verificadores póssilício são inteiramente baseados em *sotfware* (HANGAL et al., 2004; ROY et al., 2006; MANOVIT; HANGAL, 2006, 2006) ou com uma instrumentação trivial do *hardware* (CHEN et al., 2009; HU et al., 2012)" (HENSCHEL, 2014, p. 38)

Dentre estes últimos verificadores, Hu et al. (2012) foi a primeira publicação em que um verificador baseado em *sotfware* atingiu uma complexidade linear no seu tempo de verificação, a qual era exclusiva para os verificadores baseados em *hardware*.

Resumindo, é possível adicionar recursos no sistema de hardware para permitir a realização de técnicas exclusivas para pré-silício na fase pós-silício. Entretanto, quando estes recursos não estão inclusos no projeto do *hardware*, então ocorre o aumento do custo do projeto. No fim, o cliente estaria pagando pelo desenvolvimento do desejado sistema de *hardware*, junto com o custo para assegurar que a sua especificação foi seguida. Uma atitude indesejada, considerando as noções de competição no mercado.

Mais recentemente, foi observado o desenvolvimento de técnicas específicas para a fase pré-silício em que a verificação pode alcançar uma eficiência maior (ou seja, o problema de verificação possui uma menor complexidade). Um resultado obtido por meio da exploração do fato de que esta fase lhes oferece mais informações sobre a execução do sistema de memória, sem incidir no custo do projeto (i.e. a fase possui maior "observabilidade").

A literatura reporta para a verificação pré-silício diversos tipos de técnicas (HENSCHEL, 2014, p. 38): formais (e.g. Henzinger, Qadeer e Rajamani (1999), Chatterjee, Sivaraj e Gopalakrishnan (2002)), dinâmicas (e.g. Shacham et al. (2008), Rambo, Henschel e Santos (2012), Freitas, Rambo e Santos (2013) e híbridas (e.g. Abts, Scott e Lilja (2003)).

#### 1.4 JUSTIFICATIVA E ESCOPO DESTA MONOGRAFIA

Durante os últimos cinco (5) anos, uma equipe do laboratório ECL da UFSC (o mesmo laboratório em que o autor desta monografia realizou a sua bolsa de iniciação científica) pesquisou as vantagens em desenvolver um verificador específico para a fase pré-silício. Uma atitude pioneira, já que a maioria dos verificadores dinâmicos eram desenvolvidos para pós-silício.

Os resultados da pesquisa demonstraram que, infelizmente, uma simples adaptação de um verificador pós-silício para a fase pré-silício é realmente incapaz de explorar completamente a queda de complexidade presente entre estas duas fases.

A fim de quantificar a vantagem em desenvolver técnicas específicas para pré-silício em relação à adaptação de técnicas pós-silício, os pesquisadores deste laboratório passaram a realizar experimentos com a finalidade de comparar as técnicas de verificação dinâmica da literatura com os seus verificadores, considerando duas características: a eficácia e a eficiência. Isto significou a necessidade de implementar localmente verificadores do estado da arte propostos por outros autores.

Uma das técnicas importantes para esta comparação é o estado da arte dentre os verificadores por inferência: o verificador XCHECK desenvolvido por HU et al., publicado em Hu et al. (2012).

Portanto, o objetivo deste trabalho foi o de implementar para a plataforma de teste do ECL, o verificador XCHECK, possibilitando, assim, que os colegas comparassem-na com outras técnicas. Outro compromisso, foi o de apresentar a comparação entre o XCHECK e a última técnica desenvolvida pelo laboratório, o MSB (FREITAS; RAMBO; SANTOS, 2013).

# 1.5 ORGANIZAÇÃO DESTA MONOGRAFIA

O restante desta monografia é organizado da seguinte forma.

O Capítulo 2 apresenta o cerne da verificação de memória: os modelos de memória. Primeiramente, será apresentado um exemplo para ilustrar a função destes elementos formais. Em seguida, será relatada a coletânea de modelos de memória presente na literatura, enquanto se evidenciam os debates acerca de quanto um modelo de memória deveria ser relaxado. No final deste capítulo são definidas as ordens básicas entre operações de memória.

O Capítulo 3 formula o problema de verificação de memória para diferentes graus de observabilidade da plataforma.

O Capítulo 4 realiza uma revisão crítica da literatura, esclarecendo a relevância do XCHECK, verificador de interesse desta monografia.

O Capítulo 5 descreve o verificador da forma como este autor, em conjunto com Olav Philipp Henschel, deduziu pelas seguintes publicações: Gibbons e Korach (1994), Chen et al. (2009), Hu et al. (2012). No final do capítulo, são apresentados os aspectos da adaptação deste verificador para um modelo de memória altamente relaxado (Alpha).

O Capítulo 6 descreve brevemente a plataforma de testes, os experimentos realizados e analisa os resultados obtidos, comparando os dois verificadores com as mesmas condições.

Enfim, o Capítulo 7 apresenta as conclusões e as possibilidades de trabalhos futuros.

# 2 MODELOS DE MEMÓRIA (MM)

Quando lidamos com uma memória é natural nos perguntarmos qual o valor que uma leitura irá retornar. Logicamente, este deve ser o último valor escrito no seu endereço correspondente. Uma questão trivial, no caso da leitura ser originada de um programa sequencial executado em um único processador. Entretanto, tal trivialidade desaparece na situação em que processadores distintos executam, independentemente, operações de programas paralelos que compartilham endereços de memória. Assim, como a memória está distribuída em *caches* locais e memória global, pode haver o armazenamento de cópias de um dado endereçado com valores distintos (HENSCHEL, 2014, p. 19).

Para definir o comportamento correto neste último caso deve haver, segundo (HENSCHEL, 2014, p. 19), uma especificação, formulada pelos projetistas da interface *hardware-sotfware*, que defina como e quando o valor de uma operação de escrita pode ser observado por uma operação de leitura. Isto implica em uma abstração da memória compartilhada que, além de integrar parte do modelo de programação de multiprocessadores, combina as regras de consistência e os requisitos de coerência suportados em *hardware*.

Alguns autores reconhecem esta especificação como modelo de consistência de memória (ADVE; GHARACHORLOO, 1996). Outros o denominam apenas de modelo de memória (MM), (DEVADAS, 2013), em razão de que o mesmo captura tanto as regras de consistência quanto os requisitos de coerência.

Portanto, um modelo de memória captura essencialmente dois aspectos de um sistema de memória compartilhada: a relaxação da ordem de programa entre operações de leitura e de escrita (para endereços distintos) e o grau de atomicidade das operações de escrita (para o mesmo endereço) – Adve e Gharachorloo (1996), Arvind e Maessen (2006) apud Henschel (2014, p. 19). O primeiro aspecto define as regras de consistência e o segundo os requisitos de coerência.

Como o leitor pode ver, atualmente, o modelo de memória é bem pertinente. E, de acordo com a literatura disponível (MARTIN; HILL; SORIN, 2012; DEVADAS, 2013), é provável que a programação de propósitos gerais continue a requerê-lo no contexto de multiprocessadores, mesmo em uma escala de centenas de processadores.

No decorrer deste capítulo, o leitor perceberá uma menção corriqueira a dois aspectos dos modelos de memória. O primeiro aspecto diz respeito às ordens entre operações de memória, as quais resultam da especificação dada pelo modelo. O segundo é a questão de quanta liberdade o modelo oferece ao

sistema de memória que o adota, através da relaxação de sua especificação. Isto é, o modelo deixa indefinidas algumas ordens, permitindo, assim, que o próprio sistema de memória as decida (durante sua execução).

A próxima seção traz um exemplo de HENSCHEL onde, dentre outras coisas, ilustra o por quê da relaxação do modelo de memória ter sido evitada por muito tempo pelos projetistas: relaxar o modelo aumentava o trabalho exercido pelos programadores. Em seguida, é apresentada, rapidamente, uma coletânia dos modelos de memória que surgiram ao longo dos anos.

Na seção 2.3 é apresentado o relacionamento entre a relaxação do modelo com a eficiência dos verificadores de memória.

Por fim, este capítulo termina apresentando, na seção 2.4, as cinco categorias de ordem entre as operações de memória.

### 2.1 EXEMPLO ILUSTRATIVO

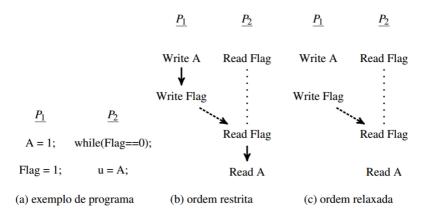

Ilustrando o efeito do modelo sobre a interface *hardware-sotfware*, a Figura 1 mostra como as operações de um programa paralelo (Figura 1a) são ordenadas por dois modelos diferentes: um que conserva a ordem de programa (Figura 1b) e outro que a relaxa para operações com endereços distintos (Figura 1c). Repare, na explicação a seguir (dada por HENSCHEL), como muda a percepção que o programa possui com relação à execução do sistema memória, conforme é adotado um modelo mais relaxado: adiciona-se a possibilidade do valor escrito em *u* ser 0.

Figura 1 – Exemplo ilustrativo para diferentes modelos de memória (HENS-CHEL, 2014, p. 20)

O programa referencia duas variáveis compartilhadas (A e Flag), alocadas em memória, e uma variável primitiva (u), alocada em registrador, onde deseja-se fazer com que o segundo processador ( $P_2$ ) leia o valor escrito pelo primeiro ( $P_1$ ) na variável A. Para tanto, o segundo processador ( $P_2$ ) só realiza a sua leitura quando a variável Flag assume um valor diferente do seu padrão de inicialização (i.e. 0). Complementarmente, o outro processador ( $P_1$ ) realiza a sua escrita em A para, em seguida e só então, liberar o seu parceiro por meio da escrita do valor 1 em Flag. No exemplo, a precedência entre as operações de memória sobre Flag é ilustrada pelas setas tracejadas.

Quando executado sob um modelo restrito (Figura 1b), o programa certamente resulta no comportamento planejado. Efeito destes modelos imporem ordem entre operações com endereços diferentes, seguindo a ordem de programa (ilustradas pelas setas contínuas). No entanto, note que conservar estas ordens tende a degradar o desempenho de programas em processadores que admitam execução fora de ordem.

A adoção de um modelo relaxado evita que esta degradação de desempenho impacte em todos os programas, mas também torna menos agradável o modelo de programação (Figura 1c). Como a ordem de programa é revogada na especificação, o programador deveria notar que as suas medidas são insuficientes e permitem dois valores (u == 0 ou u == 1).

Para resolver esta ambiguidade, o programador necessita restituir as ordens de programa desejadas (como as setas contínuas na Figura 1b). Cada modelo de memória possui o seu próprio mecânismo para alcançar este objetivo: denominado por *safety net*. Por exemplo a utilização de instruções especiais, como as barreiras de memória, os pares *load-acquire/store-release* e *read-modify-write* (RMW) (ADVE; GHARACHORLOO, 1996).

# 2.2 A COLETÂNIA DE MODELOS DE MEMÓRIA

Para evitar sobrecarregar os programadores com questões de sincronização (como ilustrado na Figura 1c), a preocupação principal dos projetistas foi, inicialmente, manter o modelo de programação o mais simples possível. Com este objetivo em mente, o modelo de consistência sequencial (*Sequential Consistency - SC*) (LAMPORT, 1979) foi adotado para conservar integralmente a ordem de programa. Mesmo que a intenção em utilizar *threads* seja em permitir reordenar operações do mesmo processador (quando não existe alguma dependência de dados, ou seja, mantém apenas as ordens entre operações conflitantes).

Procurando aumentar o desempenho, adotaram-se modelos de memória com pouca relaxação em suas ordens: algumas arquiteturas permitiram

que operações de leitura passassem na frente de operações de escrita, levando a diversos modelos de memória. Exemplos são IBM 370 (MAY, 1983), *Total Store Ordering* (TSO) (GARNER et al., 1992), *Processor Consistency* (PC) (GHARACHORLOO et al., 1990; GHARACHORLOO; GUPTA; HENNESSY, 1993), Intel 64 (INTEL, 64) e Godson-3 (CHEN et al., 2009)<sup>1</sup>. Outras arquiteturas também possibilitaram o reordenamento entre operações de escrita, como *Partial Store Ordering* (PSO (SINDHU; FRAILONG; CEKLEOV, 1992; GARNER et al., 1992).

Finalmente, algumas arquiteturas relaxaram todas as ordens, exceto para as operações conflitantes (operações para o mesmo endereço, onde ao menos uma seja escrita) da mesma *thread*. Situação em que estaria sendo alterada a semântica do próprio programa. Esta alta relaxação levou ao modelo *Weak Ordering* (WO (DUBOIS; SCHEURICH; BRIGGS, 1986) e suas variações (ADVE; GHARACHORLOO, 1996), sendo suportada, por exemplo, pelos processadores Alpha (SITES, 1992), PowerPC (MATEOSIAN, 1994), ARMv7 (ARM, 2012) e ARMv8 (ARM, 2013).

Esta atitude resulta do suporte oferecido pelas bibliotecas padrão aos programadores, com relação à sincronização com estes modelos. Portanto, a maioria dos programadores não tiveram mais que se preocupar com as regras de consistência (HENNESSY; PATTERSON, 2012).

O leitor pode encontrar mais informações acerca dos modelos de memória no tutorial de Adve, publicado em (ADVE; GHARACHORLOO, 1996). A Tabela 1, retirada desta referida fonte, apresenta um resumo das relaxações adotadas por alguns modelos de memória. O símbolo √ indica que a relaxação

| Relaxação | $\begin{matrix} \textbf{Ordem} \\ \textbf{W} {\rightarrow} \textbf{R} \end{matrix}$ | Ordem<br>W→W | Ordem<br>R→RW | Ler outras<br>escrita<br>mais cedo | Ler escrita<br>mais cedo | Safety net                      |

|-----------|-------------------------------------------------------------------------------------|--------------|---------------|------------------------------------|--------------------------|---------------------------------|

| SC        |                                                                                     |              |               |                                    | ✓                        |                                 |

| IBM 370   | <b>√</b>                                                                            |              |               |                                    |                          | Serializar instruções           |

| TSO       | <b>√</b>                                                                            |              |               |                                    | ✓                        | RMW                             |

| PC        | <b>√</b>                                                                            |              |               | <b>√</b>                           | <b>√</b>                 | RMW                             |

| PSO       | <b>√</b>                                                                            | <b>√</b>     |               |                                    | <b>√</b>                 | RMW, STBAR                      |

| WO        | <b>√</b>                                                                            | <b>√</b>     | <b>√</b>      |                                    | <b>√</b>                 | Sincronização                   |

| RCsc      | <b>√</b>                                                                            | ✓            | ✓             |                                    | ✓                        | Release, acquire, nsync,<br>RMW |

| RCpc      | <b>√</b>                                                                            | <b>√</b>     | ✓             | ✓                                  | ✓                        | Release, acquire, nsync,<br>RMW |

| Alpha     | <b>√</b>                                                                            | <b>√</b>     | <b>√</b>      |                                    | <b>√</b>                 | MB, WMB                         |

| RMO       | <b>√</b>                                                                            | <b>√</b>     | <b>√</b>      |                                    | <b>√</b>                 | Vários MEMBAR's                 |

| PowerPC   | <b>√</b>                                                                            | <b>√</b>     | <b>√</b>      | ✓                                  | ✓                        | Sync                            |

Tabela 1 – Categorização simples dos modelos relaxados (ADVE; GHARA-CHORLOO, 1996, p. 12)

<sup>&</sup>lt;sup>1</sup>Este modelo também permite o reordenamento entre operações de leitura.

correspondente é permitida por implementações simples do modelo correspondente. Em alguns casos, este símbolo também indica que a relaxação pode ser detectada pelo programador (devido a afetar os resultados do programa), as duas excessões são explicadas a seguir. A relaxação "Ler a própria escrita mais cedo" não é detectada com os modelos SC, W, Alpha e PowerPC. A relaxação "Ler outras escritas mais cedo" pode ser detectada com implementações complexas de RCsc (ADVE; GHARACHORLOO, 1996, p. 12).

#### 2.3 O DILEMA

Como visto na seção anterior, respaldada em Henschel (2014), as bibliotecas padrão mitigaram um dos limitadores da utilização de modelos de memória com alta relaxação: a necessidade dos programadores em adaptar os seus programas de acordo com as regras de consistência e coerência. Entretanto, ainda há um dilema a ser explicitado.

Relaxar um modelo de memória significa permitir que o próprio sistema de memória decida algumas ordens entre as operações de leitura e de escrita. Afinal, eventualmente, durante qualquer execução, todas as operações de memória serão ordenadas.

Isto, infelizmente, conflita com a motivação da verificação de memória: durante o desenvolvimento, todo o sistema é inconfiável e, portanto, é necessário comprovar que todo o seu comportamento está como o desejado. E a memória não é exceção.

Assim, sempre que as regras de um modelo de memória são relaxadas, aumenta-se o trabalho de verificação. Esta ficará encarregada de testar um comportamento adicional relacionado à falta daquela regra relaxada.

Portanto, a utilização de modelos de memória também é limitada pela complexidade dos verificadores de memória. Quanto mais estes últimos se desenvolverem e abaixarem as suas complexidades de verificação, mais acessível ficará a utilização da relaxação.

# 2.4 AS ORDENS ENTRE OPERAÇÕES DE MEMÓRIA

A partir deste ponto, espera-se que o leitor tenha percebido que tanto o modelo de memória quanto a sua própria verificação lidam com as ordens entre as operações de memória. É em volta destas ordens que todo o problema de verificação se passa.

O modelo de memória remove algumas ordens a fim de dar liberdade para a execução de operações no sistema de memória, enquanto que a verificação avalia as decisões tomadas por este último (acerca destas mesmas ordens).

Assim, este capítulo termina apresentando, brevemente, cinco ordens tradicionais entre as operações de memória.

## 2.4.1 Ordem de programa

A ordem de programa é aquela determinada puramente pelo programa.

**Definição 1** (*Ordem de Programa*). Dadas duas operações diferentes ( $u_1$  e  $u_2$ ) no mesmo processador,  $u_1$  precede  $u_2$  pela ordem de programa (formalmente,  $u_1 \stackrel{P}{\longrightarrow} u_2$ ) se e somente se  $u_1$  precede  $u_2$  na sequência do programa executado no processador. Hu et al. (2012, p. 505)

As explicações dadas até este ponto da monografia podem ter levado o leitor a acreditar que, na prática, muitos modelos de memória utilizam esta ordem para um grupo específico de operações de memória, permitindo a sua violação em outros casos. Entretanto, como HU et al. formula, a relaxação desta ordem é capturada por meio da definição de uma outra ordem entre as operações de memória: a ordem de processador.

# 2.4.2 Ordem de processador

**Definição 2** (*Ordem de Processador*). Dadas duas operações diferentes ( $u_1$  e  $u_2$ ) **no mesmo processador**,  $u_1$  precede  $u_2$  pela ordem de processador (formalmente  $u_1 \xrightarrow{PO} u_2$ ) se e somente se  $u_1$  precede  $u_2$  pela perspectiva de todos os processadores. Hu et al. (2012, p. 505)

Portanto, esta ordem necessita, também, da definição de como um processador enxerga as ordens entre as operações.

**Definição 3** (Realização de uma Operação de Memória). Uma leitura r é considerada "realizada" com respeito ao processador  $\mathcal{P}$  (durante um instante de tempo no relógio local de  $\mathcal{P}$ ) quando  $\mathcal{P}$  emite uma operação de escrita para o mesmo endereço que não afeta o valor retornado por r. Analogamente, uma escrita w é considerada "realizada" com respeito ao processador  $\mathcal{P}$  (durante um instante de tempo no seu relógio local) quando  $\mathcal{P}$  emite uma operação de leitura, para o mesmo endereço, que retorna o valor definido por w (ou por alguma escrita subsequente). Assim, uma operação  $u_1$

precede  $u_2$  pela perspectiva do processador  $\mathscr{P}$  se  $u_1$  é realizada, pela perspectiva de  $\mathscr{P}$ , em um instante de tempo anterior ao que do que  $u_2$  é realizada (no relógio local de  $\mathscr{P}$ ).

# 2.4.3 Ordem de execução

Dentre todas as ordens vistas até este ponto, a ordem de execução é a primeira que pode ordenar operações de diferentes processadores. Além do mais, ela pode ser interpretada como a Consistência de Cache ou a Ordem de Coerência (*write-before* e *read-before* orders).

A ordem de execução é estabelecida com respeito, apenas, pelo influência entre as operações de memória, isto é, ordena as "operações conflitantes".

Para o caso das operações de leitura e de escrita, duas operações de memória são consideradas conflitantes se acessam o mesmo endereço e ao menos uma delas é uma escrita.

**Definição 4** (*Ordem de Execução*). Dadas duas operações diferentes e **conflitantes** ( $u_1$  e  $u_2$ ),  $u_1$  precede  $u_2$  pela ordem de execução (formalmente,  $u_1 \xrightarrow{E} u_2$ ) se e somente se  $u_1$  precede  $u_2$  pela perspectiva de todos os processadores. Hu et al. (2012, p. 505)

(HU et al., 2012) observa que a ordem de execução não ordena operações (mesmo que conflitantes) observadas por outras no mesmo processador antes mesmo das primeiras terem sido executadas globalmente. Um comportamento que é permitido por alguns modelos de memória.

# 2.4.4 Ordem global

Enfim, a ordem global combina as ordens de processador e de execução.

**Definição 5** (Ordem Global). Uma operação  $(u_1)$  precede outra operação  $(u_2)$  pela ordem global se e somente se  $u_1$  precede  $u_2$  pela ordem de processador, ou  $u_1$  precede  $u_2$  pela ordem de execução, ou por meio da transitividade, isto é,  $u_1$  precede alguma operação (u) pela ordem globa,l a qual precede  $u_2$  pela ordem global. Formalmente,

$$(u_1 \xrightarrow{GO} u_2) \iff (u_1 \xrightarrow{PO} u_2) \lor (u_1 \xrightarrow{E} u_2)$$

$$\lor (\exists u \in \mathbb{O} : u_1 \xrightarrow{GO} u \land u \xrightarrow{GO} u_2)$$

## 2.4.5 Ordem temporal

A ordem temporal entre operações de memória é obtida através do tempo (exato ou aproximado) em que elas foram executadas globalmente no sistema de memória.

Devido à complexidade dos sistemas de memória (hierarquia de memória, emissão de operações por diversos processadores, exercício do adiantamento de resultados, etc), nem sempre é possível obter os meios necessários para estabelecer esta ordem. Por este motivo, ela é utilizada por poucas técnicas de verificação de memória, a maior parte delas projetada para as etapas pré-silício.

Note, no entanto, que caso esta ordem fosse obtida, se reduziria significativamente a complexidade do problema de verificação. Afinal, neste caso, já se teria a ordem total das operações.

#### 3 PROBLEMA-ALVO

Para os verificadores dinâmicos, uma instância do problema de verificação de memória trata da combinação de um programa paralelo, um sistema de memória (DUV) e um modelo de memória. O sistema deve executar o programa conforme o modelo especifica.

As informações de uma instância (execução) qualquer, pertinentes para a verificação, são capturadas por um conjunto de *traces* dos eventos de memória observados durante a execução. Por exemplo, saber qual foi o resultado da operação de memória executada. Estas informações podem ser sintetizadas por meio de um grafo direcionado que representa as relações de ordem entre as operações de memória realizadas.

Este grafo é uma interpretação do problema. Portanto, outra utilidade sua está em identificar a ocorrência de violações de uma instância do problema com relação ao seu modelo de memória. Toda aresta representa uma ordem entre duas operações (os vértices) que, necessariamente, deve acontecer a fim de que estas mesmas operações apresentem os seus resultados observados pelos *traces* por meio de um comportamento permitido pelo modelo de memória. Assim, a única justificativa para a presença de algum ciclo, nestes tipos de grafos, é que o sistema de memória quebrou alguma(s) regra(s) do modelo durante a execução das operações deste ciclo.

Alguns verificadores utilizam a presença de algum ciclo nestes grafos para indicar (como contra-exemplo) a existência de erros de projeto (com relação a uma certa execução).

No entanto, utilizar *traces* que notificam apenas o resultado das operações pode resultar em falsos negativos. Logo, toda técnica construída em cima destes últimos necessita de atitudes adicionais para alcançar a sua completude: a busca heurística, mencionada na introdução desta monografia (seção 1.2), em conjunto com *backtracking* (MANOVIT; HANGAL, 2006).

Infelizmente o *backtracking* resulta em grandes tempos de análise, somados aos já altos tempos de simulação de uma representação de projeto. Ademais, o *backtracking* também limita a escalabilidade a longo prazo para um crescente número de processadores.

A fim de contornar esta limitação, algumas técnicas aumentam os *traces*, realizando o monitoramento em mais de um ponto do sistema de memória.

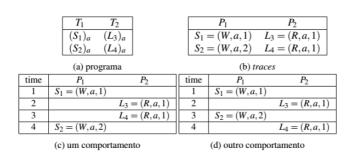

A tese de mestrado de HENSCHEL, por meio das Figuras 2, "Um programa, seus *traces* e dois comportamentos atômicos", e 3, "Ordenamento de eventos sob forte atomicidade de escrita", presentes no Capítulo 2 (HENSCHEL, 2014, p. 30), ilustra de forma clara e didática estas noções acima

mencionadas. Estas são as principais noções usadas em sua formulação para o problema de verificação de memória, a qual esta monografia reutiliza.

Figura 2 – Um programa, seus traces e dois comportamentos atômicos (HENSCHEL, 2014, p. 30)

Figura 3 – Ordenamento de eventos sob forte atomicidade de escrita (HENS-CHEL, 2014, p. 30)

A seguir, este capítulo vai transcrever a formalização do problema cuja autoria é de HENSCHEL.

Desta forma, a próxima seção determina a observabilidade da plataforma sob verificação, que distingue os diferentes problemas (HENSCHEL, 2014, p. 31). Na seção seguinte, serão definidos formalmente os problemasalvo, independentemente do modelo de memória (HENSCHEL, 2014, p. 33). Diferentes modelos definem diferentes instâncias do problema.

#### 3.1 A OBSERVABILIDADE NA PLAFATORMA

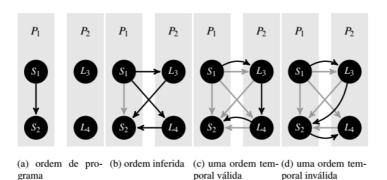

Figura 4 – Um modelo genérico de sistema memória compartilhada (HENS-CHEL, 2014, p. 32)

Como HENSCHEL explicou durante a sua dissertação, a Figura 4 apresenta um diagrama esquemático genérico para um multiprocessador com memória compartilhada. Ela ilustra uma arquitetura com p elementos de processamento  $(P_1,\ldots,P_i,\ldots,P_p)$  que acessam os seus dados através de sua respectiva cache privativa. Assume-se que um buffer de reordenamento  $(reorder\ buffer\ -\ ROB)$  (HENNESSY; PATTERSON, 2012) ou uma estrutura similar é usada para garantir a consolidação das instruções em ordem de processador. Buffers de entrada e de saída são destacados nas fronteiras da cache de dados privativa. Como os verificadores devem ser amplamente independentes da organização da memória, o diagrama abstrai os níveis mais baixos da hierarquia de caches, a rede de interconexão e os mecanismos de coerência.

Na Figura 4, HENSCHEL indica os pontos relevantes onde os eventos de memória podem ser observados por meio dos símbolos  $\circledast$ ,  $\oplus$  e  $\ominus$ . Cada um desses pontos é denominado de monitor.

A observabilidade dos diversos verificadores presentes na literatura pode ser esclarecida por meio deste esquemático. Os verificadores pós-silício (MANOVIT; HANGAL, 2006; HU et al., 2012) são limitados pela observa-

bilidade *intra-chip*, logo eles capturam um único *trace* por elemento de processamento, amostrando eventos como se eles fossem observados em cada monitor ⊕. Enquanto que os verificadores pré-silício podem se beneficiar da maior observabilidade de representações de projeto para resolver instâncias mais simples do problema de verificação (como será mostrado na seção 3.2). Repare que isto significa na possibilidade de utilizar mais pontos de amostragem. Por exemplo, dois verificadores pré-silício (RAMBO; HENSCHEL; SANTOS, 2012; FREITAS; RAMBO; SANTOS, 2013) amostram duas sequências de eventos por elemento de processamento, pelos monitores ⊕ e ⊕. Em Freitas, Rambo e Santos (2013) o ROB é também observado, pelo terceiro monitor ⊛. (HENSCHEL, 2014, p. 31-33)

A seguir será mostrada a formulação de HENSCHEL para as instâncias do problema de verificação alvo relevantes para esta monografia.

# 3.2 FORMULAÇÃO DO PROBLEMA

Daqui em diante, *p* e *n* denotarão, respectivamente, o número de processadores e o número total de operações de memória.

Primeiramente, HENSCHEL formaliza o principal conceito na verificação de modelos de memória baseados em simulação: o *trace*.

**Definição 6** *Um trace*  $\acute{e}$  *uma sequência*  $(e_1, \ldots, e_i, \ldots, e_m)$ , *onde*  $e_i = (op, a, value)$   $\acute{e}$  *um evento de memória tal que*  $op \in \{R, W\}$ ,  $a \acute{e}$  *um endereço e value*  $\acute{e}$  *um valor* (HENSCHEL, 2014, p. 33).

Como este autor afirmou, traces locais  $T_{\ominus}^1, \dots, T_{\ominus}^p$  são obtidos amostrando eventos em cada processador, conforme indicado pelos monitores  $\ominus$  na Figura 4. Eles podem ser combinados em um trace global T entrelaçando os traces locais, enquanto se mantém a ordem de amostragem local, i.e. se  $e_i$  precede  $e_j$  em algum trace  $T_{\ominus}^k$ , para  $k \in [1,p]$ , então  $e_i$  deve preceder  $e_k$  no trace global (T).

Quando a observabilidade é restringida à amostragem de traces nos monitores  $\ominus$ , o problema pode ser formulado da seguinte forma:

**Problema 1** (Verificação baseada em traces). Dada uma coleção de traces  $T_{\ominus}^1, \dots, T_{\ominus}^p$ , existe um trace global T que satisfaça todas as restrições do modelo de memória? (HENSCHEL, 2014, p. 34)

Esta formulação de HENSCHEL apresenta como a maior parte dos verificadores pós-silício (e.g. Manovit e Hangal (2006), Chen et al. (2009), Hu et al. (2012)) contornam o fato do problema geral ser NP-Completo

(GIBBONS; KORACH, 1994). Estes verificadores utilizam as instâncias do Problema 1, resultadas da inclusão de informações adicionais, tais como a ordem total de escritas (ordenamento de operações de escrita para um mesmo endereço) e o mapeamento de leituras (ligando cada operação de leitura com a operação de escrita que produziu seu valor). Este mapeamento pode ser facilmente realizado quando se atribui para cada escrita um valor único. O problema torna-se polinomial (considerando que *p* seja constante) quando ambas as informações estão disponíveis (GIBBONS; KORACH, 1994).

HENSCHEL elabora outro problema de verificação sobre o conceito de "comportamento", o qual é originado quando é possível determinar (em tempo de execução ou de simulação) o instante de tempo em que um evento é amostrado. Veremos mais tarde, que esta é a instância de problemas resolvidas pelo verificador de interesse, o XCHECK.

**Definição 7** (Comportamento). Um comportamento é uma sequência  $(\beta_1, \ldots, \beta_i, \ldots, \beta_m)$ , onde  $\beta_i = (op, a, value, t)$  é um evento de memória com marca temporal tal que  $op \in \{R, W\}$ , a é um endereço, value é um valor lido/escrito e t é o instante de tempo em que o evento foi observado. A marca temporal de algum evento  $\beta_i$  será denotada como  $\tau(\beta_i)$  (HENSCHEL, 2014, p. 34).

Assim como HENSCHEL esclareceu em seu trabalho, perceba que de forma similar aos traces, os comportamentos locais  $B_{\ominus}^1, \dots, B_{\ominus}^p$  são obtidos amostrando eventos em cada processador, conforme a Figura 4 indica pelos monitores  $\ominus$ . Eles podem ser combinados em um comportamento global B entrelaçando os comportamentos locais enquanto se mantém a ordem de marcas temporais, i.e. se  $\tau(\beta_i) < \tau(\beta_j)$ , então  $\beta_i$  deve preceder  $\beta_j$  no comportamento global B (HENSCHEL, 2014, p. 34).

Enfim, HENSCHEL formaliza este outro problema de verificação da seguinte maneira:

**Problema 2** (Verificação baseada em comportamentos). Dada uma coleção de comportamentos  $B_{\ominus}^1, \dots, B_{\ominus}^p$ , existe algum comportamento global B que satisfaça todas as restrições do modelo de memória? (HENSCHEL, 2014, p. 34)

O último problema definido pelo referido colega é o utilizado pelos verificadores pré-silício, os quais se beneficiam da observabilidade adicional de representações de projeto e ambientes de simulação. Eles podem resolver instâncias de um problema mais simples do que definidos anteriormente.

**Problema 3** (*Verificação aumentada baseada em comportamentos*). Dada uma coleção de comportamentos  $B_{\ominus}^1, \dots, B_{\ominus}^p, B_{\oplus}^1, \dots, B_{\oplus}^p$ , existe algum com-

portamento global B que satisfaça todas as restrições do modelo de memória? (HENSCHEL, 2014, p. 34)

A instância resultante do Problema 3 pode ser resolvida em tempo polinomial e com garantias totais de verificação sob forte atomicidade de escrita (RAMBO; HENSCHEL; SANTOS, 2012; FREITAS; RAMBO; SANTOS, 2013) quando comportamentos locais são amostrados por, pelo menos, dois monitores ( $\oplus$  e  $\ominus$ ). Henschel (2014, p. 71-74) mostrou que a verificação com complexidade polinominal, para modelos de memória que requerem uma ordem total de escritas, necessita de instâncias do problema com ainda mais informações adicionais.

Como qualquer modelo de memória define que a execução especulativa não pode ter efeitos observáveis, então, operações que são canceladas não precisam satisfazer o modelo adotado. Por esta razão alguns verificadores pré-silício (FREITAS; RAMBO; SANTOS, 2013; HENSCHEL, 2014) monitoram o ROB (\*\*) para remover estes eventos especulativos da sua verificação.

#### 4 TRABALHOS CORRELATOS

Com o propósito de discutir a relevância do XCHECK, este capítulo inicialmente mostra as técnicas relacionadas com a avaliação aqui pretendida: aquelas baseadas em *sotfware* e que resolvem instâncias dos Problemas 1, 2 e 3.

Estas técnicas, cujas principais características estão descritas na Tabela 2, podem ser dividas em duas categorias: verificação *post-mortem* e verificação *on-the-fly*. É com base nestas categorias que este capítulo se organiza de maneira a falar sobre elas.

# 4.0.1 Verificação post-mortem

Os verificadores desta categoria são caracterizados pela geração de todos os *traces* antes de que a sua verificação possa se iniciar.

A maioria dos verificadores dinâmicos se baseia na detecção de ciclos em grafos orientados, em que os vértices representam operações de memória (escritas e leituras) e as arestas representam uma relação de ordem. Desta forma, todo ciclo significa um paradoxo: todas as operações envolvidas devem terminar antes mesmo de terem se iniciado (e vice-versa).

Na prática, são adotadas relações parciais que, como podem "disfarçar" uma instância inválida do problema, tornam incompleto estes verificadores. Este disfarce acontece quando não há alguma relação de ordem total, estendida da original, que seja uma instância válida do problema.

Para mitigar a ocorrência de falso-negativos, estas ferramentas tentam inferir o maior número possível de arestas. TSOTool (HANGAL et al., 2004) é um exemplo de ferramenta de verificação incompleta que se utiliza desse método e que, posteriormente, foi estendida para se tornar completa (MANOVIT; HANGAL, 2006).

Para eliminar completamente os falso-negativos, é necessário ter absoluta certeza de que o resultado do verificador foi baseado em uma ordenação total. Logo, é necessário inferir todas as possibilidades de arestas que diminuam o número de componentes fortemente conexos do grafo. Isto, infelizmente, significa em seguir uma heurística e, muito eventualmente, fazer um *backtracking*. Método que torna exponecial a complexidade destes verificadores.

O XCHECK (HU et al., 2012), versão aprimorada do LCHECK (CHEN et al., 2009), contorna esta complexidade limitando, principalmente, a realização do *backtracking* em um subespaço cujo tamanho depende apenas

| Referência                      | Análise     | Idéia-chave                         | Garantias | Número de monitores | Complexidade de pior caso |

|---------------------------------|-------------|-------------------------------------|-----------|---------------------|---------------------------|

| Hangal et al. (2004)            | Post-mortem | Inferência                          | Nenhuma   | 1                   | $O(n^5)$                  |

| Manovit (2005)                  | Post-mortem | Inferência                          | Nenhuma   | 1                   | $O(pn^3)$                 |

| Manovit e Hangal (2006)         | Post-mortem | Inferência                          | Plenas    | 1                   | $O((n/p)^p pn^3)$         |

| Roy et al. (2006)               | Post-mortem | Inferência                          | Nenhuma   | 1                   | $O(n^4)$                  |

| Shacham et al. (2008)           | On-the-fly  | scoreboard                          | Nenhuma   | 1                   | $O(p^2n^2)$               |

| Chen et al. (2009)              | Post-mortem | Inferência                          | Nenhuma   | 1                   | $O(p^3n)$                 |

|                                 | Post-mortem | Inferência                          | Plenas    | 1                   | $O(C^p p^2 n^2)$          |

| Hu et al. (2012)                | Post-mortem | Inferência                          | Plenas    | 1                   | $O(C^p p^3 n)$            |

| Rambo, Henschel e Santos (2012) | Post-mortem | Emparelhamento em grafos bipartidos | Plenas    | 2                   | $O(n^6/p^5)$              |

| Freitas, Rambo e Santos (2013)  | On-the-fly  | Múltiplas scoreboard                | Plenas    | 3                   | $O(n^2/p)$                |

Tabela 2 – Principais características dos verificadores dinâmicos (HENSCHEL, 2014)

do número de processadores. Um avanço considerável, já que significa em retirar o principal limitador de desempenho dos verificadores atuais (o número de operações) da parte exponencial de sua complexidade.

No entanto, corroborando com Henschel (2014, p. 40), a crescente paralelização dos processadores através do aumento do número de núcleos faz com que esta técnica tenda a se tornar cada vez mais ineficiente.

Afora a detecção de ciclos, mas ainda baseado em grafos, há o método de Emparelhamento Estendido de Grafo Bipartidos (RAMBO; HENSCHEL; SANTOS, 2012) que foi projetado especialmente para a verificação de representações executáveis de plataformas multiprocessadas. Nesta outra abordagem, a invalidade de uma instância é dada através de um teste de equivalência entre eventos originados de *traces* diferentes:

Devem existir dois monitores em cada núcleo de processamento: um na saída da unidade de consolidação de resultados (commit unit) e outro na interface com a memória privativa. Um grafo bipartido é, então, construído a partir destes monitores; os vértices representam as operações de memória e as arestas representam a equivalência. Outro grafo, com os mesmo vértices, representa o ordenamento de operações, imposto pelo modelo de memória, através das suas arestas. Com base nestes dois grafos é possível determinar se o comportamento global, usando relógios globais de Lamport (LAMPORT, 1978), que utilizam marcas temporais geradas pelos monitores para cada operação. A partir deles é criado um registro de execução global, o qual é analisado por um algoritmo que determina se ele viola ou não as regras do modelo de memória. (HENSCHEL, 2014, p. 40)

# 4.0.2 Verificação on-the-fly

Por outro lado, se encontram os verificadores *on-the-fly*, os quais procuram invalidar uma instância antes mesmo da execução desta ter sido terminada.

Scoreboard Relaxado (SHACHAM et al., 2008) é uma técnica (genérica) de verificação que possui um princípio de funcionamento diferente do visto até o momento. Ela mantém uma tabela (a.k.a. scoreboard) de possíveis valores para cada endereço de memória, a qual valida o valor observado por cada uma das leituras. Durante a execução, esta tabela é atualizada de acordo

com cada operação observada. Quando uma escrita é feita na memória, a tabela recebe um novo valor no endereço da operação; quando é uma leitura, os possíveis valores são filtrados. Esta última alteração reduz o número de possibilidades, mas pode significar a remoção de um valor que havia validado (incorretamente) uma leitura anterior. Uma situação possível quando leituras se sobrepõem ou completam com uma quantidade variável de tempo. A fim de superar esta limitação, o *scoreboard* relaxado também necessita utilizar o *bactracking*. Isto, no entanto, não diminui a principal vantagem desta ferramenta com relação às técnicas anteriores, isto é, o fato de realizar a análise simultaneamente à execução do programa e poder, assim, detectar erros mais rapidamente (antes mesmo que a simulação termine).

A técnica proposta em Freitas, Rambo e Santos (2013) usa o mesmo mecanismo de verificação global da técnica de RAMBO; HENSCHEL; SANTOS. A sua verificação local, no entanto, pode ser realizada *on-the-fly* devido ao suporte de um terceiro monitor (em cada núcleo) responsável por distinguir as leituras consolidadas das leituras especulativas. Isto impede estas últimas de serem indicadas como erros (um diagnóstico de falso positivo) já que, enquanto as operações de leitura e escrita são monitoradas na interface com a memória, um monitor na unidade de consolidação se encarrega de observar as operações que foram consolidadas e outro no *buffer* de reordenamento observa quais operações concluídas foram canceladas. Por sua vez, a verificação global é realizada por meio de um *scoreboard* relaxado para cada processador, o qual é atualizado a cada operação monitorada, verificando se cada operação que chega à memória tem uma correspondente observada em algum dos outros monitores e se não há intervalo ilegal da ordem especificada pelo modelo de memória (HENSCHEL, 2014).

# 4.1 O INTERESSE NA COMPARAÇÃO QUANTITATIVA ENTRE AS TÉCNICAS DE VERIFICAÇÃO

Esta análise da literatura evidencia indícios de deficiências dos verificadores dinâmicos, os quais foram reportados em Henschel (2014, p. 42). Eles merecem ser confirmados por meio de uma avaliação experimental comparativa e de uma análise quantitativa de eficiência e de eficácia.

Repare que a importância de tal comparação, entre verificadores de classes diferentes não diminui, mesmo com o fato de ter sido raramente apresentada na literatura (RAMBO; HENSCHEL; SANTOS, 2012; FREITAS; RAMBO; SANTOS, 2013; HENSCHEL, 2014).

Por fim, perceba que o objetivo desta monografia está ligada em responder se um verificador para pré-silício (FREITAS; RAMBO; SANTOS,

2013) realmente consegue ser melhor que um verificador de inferências adaptado para pré-silício, mesmo quando a complexidade deste último é melhor (linear) do que o primeiro (quadrático) com relação ao principal limitador de desempenho atual (o número de operações). Os experimentos também podem ilustrar como a diferença entre eles irá se portar no futuro (i.e. conforme o número de processadores crescer).

#### 5 XCHECK

Em 2012, HU et al. publicaram o XCHECK, um verificador de memória *post-mortem* para a etapa pós-silício com complexidade de verificação linear sobre o número de operações de memória, o principal limitador de desempenho. Tal complexidade foi impactante devido ao fato deste verificador não necessitar da ajuda de nenhum *hardware* dedicado.

A ideia chave do XCHECK é de aproximar a ordem temporal (seção 2.4.5) para fazer uma verificação localizada, referente apenas aos pares de operações de memória que não são ordenados por ela. Uma herança do seu predecessor, o LCHECK, publicado em Chen et al. (2009).

Para os verificadores de inferência, a validade de uma instância (do Problema 2) é dada pela existência de uma ordenação total e válida das operações de memória. Logo, é necessário conjecturar todas as ordens inexistentes, uma tarefa que estes dois verificadores realizam com o auxílio do grafo de fronteiras (GIBBONS; KORACH, 1994), o qual será descrito na seção 5.3.

Porém, a construção dinâmica deste grafo significa a necessidade de validar os seus elementos para não haver a conjectura de ordens proibidas pelo modelo de memória. E, é neste ponto em que o XCHECK se diferencia do LCHECK: o algoritmo de checagem de ciclos deste primeiro (seção 5.6) possui uma complexidade significativamente menor que o do segundo:  $O(p^2)$  e  $O(np^3)$ , respectivamente. Esta queda de complexidade é resultado do XCHECK explorar a relação existente entre as arestas do grafo de fronteira que constituem em um caminho entre a fronteira inicial e a fronteira final (seção 5.3).

A inicialização do XCHECK consta em, principalmente, computar os intervalos de espera (seção 5.2) de todas as operações e construir o mecanismo que evidencia violações ao modelo de memória: o grafo de execução (seção 5.4). Tarefas que podem ser realizadas respectivamente em O(np), p. 59, e  $O(np^3)$ , p. 69.

O restante de sua verificação constitui em atravessar o grafo de fronteiras enquanto é realizado, para cada um de seus  $O(n\ C^p p)$  movimentos de fronteira, o seu método de inferências (seção 5.5) e o de checagem de ciclos (seção 5.6), cujas complexidades são respectivamente de  $O(p^2)$  (para cada aresta adicionada no grafo de execução), p. 69, e de  $O(p^2)$ , p. 71. Totalizando na complexidade de  $O(n\ C^p p^3)$ .

Na verdade, como o leitor descobrirá no decorrer deste capítulo, a utilização do método de inferências durante o atravessamento no grafo de fronteiras não foi explicitada pelos autores durante sua publicação (HU et al., 2012). O autor desta monografia supos esta sua utilização em conjunto com

## Olav Philipp Henschel.

As seções seguintes descrevem cada um destes elementos do XCHECK por meio de uma compilação das explicações dadas em Gibbons e Korach (1994), Chen et al. (2009), Hu et al. (2012). Portanto, em um primeiro momento, estará sendo mostrado como o XCHECK é capaz de resolver as instâncias do problema, considerando modelos que não reordenam as operações de escrita, como, por exemplo, o modelo sequencial e o *Godson-3 consistency* (CHEN et al., 2009, p. 384).

O capítulo finaliza apresentando (na seção 5.7) uma visão geral dos detalhes da implementação realizada do XCHECK, incluindo a explicação sobre como adaptá-lo para um modelo de memória bastante relaxado.

Antes de mais nada, a próxima seção ilustra o comportamento deste verificador para uma instância simples do problema. Desta forma, o leitor poderá entender melhor todos estes aspectos do verificador enunciados acima.

#### 5.1 EXEMPLO ILUSTRATIVO

Nesta seção o leitor será apresentado a um exemplo da verificação feita pelo XCHECK. Porém, para fins de simplificação, será omitida a ordem de tempo físico, responsável por otimizar sua verificação.

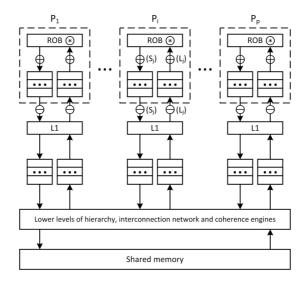

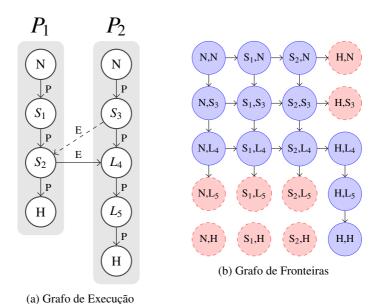

Considere que uma dada instância do problema (i.e. programas paralelos) foi submetida ao sistema de memória em inspeção (DUV), gerando o comportamento descrito nos traces da Figura 5, e que o modelo de memória adotado é o sequencial, fiel à ordem de programa.

| $P_1$          | $P_2$          |  |  |

|----------------|----------------|--|--|

| $S_1: (W,A,1)$ | $S_3: (W,B,3)$ |  |  |

| $S_2:(W,B,2)$  | $L_4:(R,B,2)$  |  |  |

| -              | $L_5: (R,A,1)$ |  |  |

Figura 5 – Um comportamento

Os *traces* esclarecem a existência de dois núcleos de processamento  $(P_1 \ e \ P_2)$  que emitiram operações ao sistema de memória. Cada linha do *trace* caracteriza uma operação emitida por um dado núcleo. Por exemplo, a primeira operação emitida por  $P_1$  é de escrita (W) ao endereço A com o valor 1. Esta operação é identificada como  $S_1$ , onde S abrevia o nome de sua instrução (store) e 1 é o seu identificador.

Observe ainda que o segundo núcleo  $(P_2)$  possui uma operação de leitura  $(L_4)$  cujo valor obtido foi escrito por  $S_2$ , uma escrita do outro

núcleo  $(P_1)$ .

A primeira tarefa realizada pelo XCHECK é de esmiuçar os *traces* revelando, assim, o máximo possível das ordens globais entre as operações executadas pelo sistema de memória. A fim de organizar tudo o que for descoberto, o XCHECK constrói um grafo, denominado por Grafo de Execução (Figura 6a), em que cada operação de memória é representada como um vértice e as ordens conhecidas são representadas por arestas. Além disso, são adicionados vértices para capturar as noções do estado inicial (operação nula, *null*, *N*) e do estado de parada (operação de parada, *halt*, *H*) do sistema de memória com relação a cada núcleo de processamento.