#### Juliano D'Ornelas Benfica

Plataforma para Testes e Qualificação de Dispositivos Reconfiguráveis e Sistemas em Chip, Submetidos aos Efeitos Combinados da Interferência Eletromagnética e da Radiação Ionizante

> Florianópolis 2015

#### Juliano D'Ornelas Benfica

# PLATAFORMA PARA TESTES E QUALIFICAÇÃO DE DISPOSITIVOS RECONFIGURÁVEIS E SISTEMAS EM CHIP, SUBMETIDOS AOS EFEITOS COMBINADOS DA INTERFERÊNCIA ELETROMAGNÉTICA E DA RADIAÇÃO IONIZANTE

Tese submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do Grau de Doutor em Engenharia Elétrica. Orientador: Prof. Dr. Eduardo Augusto Bezerra

Coorientador: Prof. Dr. Fabian Luis

Vargas

Florianópolis 2015

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Áutomática da Biblioteca Universitária da UFSC.

Benfica, Juliano D'Ornelas

Plataforma para Testes e Qualificação de Dispositivos Reconfiguráveis e Sistemas em Chip, Submetidos aos Efeitos Combinados da Interferência Eletromagnética e da Radiação Ionizante / Juliano D'Ornelas Benfica; orientador, Eduardo Augusto Bezerra; coorientador, Fabian Luis Vargas. - Florianópolis, SC, 2015.

228 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia Elétrica.

Inclui referências

1. Engenharia Elétrica. 2. Plataformas de teste. 3. Efeitos combinados da radiação e interferência eletromagnética. 4. Dispositivos reconfiguráveis. 5. Injeção de ruído. I. Bezerra, Eduardo Augusto. II. Vargas, Fabian Luis. III. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. IV. Título.

# PLATAFORMA PARA TESTES E QUALIFICAÇÃO DE DISPOSITIVOS RECONFIGURÁVEIS E SISTEMAS EM CHIP, SUBMETIDOS AOS EFEITOS COMBINADOS DA INTERFERÊNCIA ELETROMAGNÉTICA E DA RADIAÇÃO IONIZANTE

Esta Tese foi julgada adequada para obtenção do Título de Doutor em Engenharia Elétrica, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica.

Florianópolis, 24 de novembro de 2015.

Prof. Carlos Galup Montoro, Dr.

Coordenador do Programa de Pós-Graduação em Engenharia Elétrica

Prof. Eduardo Augusto Bezerra, Dr.

Orientador

Universidade Federal de Santa Catarina - UFSC

Prof. Fabian Luis Vargas, Dr.

Coorientador

Pontifícia Universidade Católica do RS - PUCRS

#### Banca Examinadora:

Prof.ª Fernanda Lima Kastensmidt, Dr.ª

Universidade Federal do Rio Grande do Sul – UFRGS

(Videoconferência)

Prof. Helano de Sousa Castro, Dr. Universidade Federal do Ceará - UFC

Prof. José Lipovetzky, Dr. Universidade de Buenos Aires- UBA (Videoconferência)

Prof. Anderson W. Spengler, Dr.

Universidade Federal de Santa Catarina – UFSC

Prof. Adroaldo Raizer, Dr. Universidade Federal de Santa Catarina - UFSC

#### AGRADECIMENTOS

A minha esposa, pela paciência, carinho e dedicação, além de ser a principal incentivadora para a realização e conclusão deste trabalho, me apoiando sempre para crescer como profissional e como pessoa. Linda, muito obrigado!!!

Aos meus orientadores, professores Eduardo Bezerra e Fabian Vargas, meus amigos acima de tudo, que sempre acreditaram e valorizaram o meu trabalho, orientando e apoiando sempre da melhor forma possível, sendo exemplo de dedicação e orientação.

A todos os integrantes do Grupo SiSC e do grupo GSE, que contribuíram para a realização deste trabalho, principalmente na realização dos ensaios em campo.

A todo o pessoal do INTI (Buenos Aires), Centro Atômico Ezeiza, do Centro Atômico Bariloche, da USP e da FEI (São Paulo), que nos possibilitaram a realização de todos os ensaios efetuados neste trabalho, fornecendo os equipamentos necessários e colaborando com suas grandes experiências no assunto.

A UFSC e ao PPGEEL pela disponibilidade dos recursos necessários para a realização deste trabalho pelo profissionalismo e competência.

A PUCRS, e principalmente aos meus colegas de trabalho do curso de Engenharia Elétrica pelo grande apoio e incentivo.

Meus sinceros agradecimentos a todos familiares e amigos, que colaboraram e apoiaram de alguma forma no decorrer desta caminhada....

#### RESUMO

Este trabalho investiga os efeitos combinados da radiação e interferência eletromagnética em sistemas embarcados críticos baseados em dispositivos reconfiguráveis (FPGAs). Os efeitos investigados podem ser resultantes de interferência eletromagnética, conduzida ou radiada, ou através de radiação ionizante, por acúmulo de dose total (*Total Ionizing Dose*, ou TID) ou por efeitos de evento único, denominados de *Single Event Effects* (SEE). Dispositivos do tipo FPGA têm sido cada vez mais utilizados em sistemas críticos, devido a sua versatilidade, desempenho e robustez. O presente estudo contribui para a caracterização e qualificação de dispositivos FPGAs quando em funcionamento em ambientes ruidosos.

O cenário descrito motivou a proposta deste trabalho, que contempla três objetivos principais: (1) O projeto, desenvolvimento e validação de uma plataforma para ensaios combinados de radiação e de interferência eletromagnética (conduzida e radiada) usando como referência o conjunto de normas IEC 62.132. (2) Desenvolver uma metodologia para qualificar sistemas em chip (SoCs) implementados em FPGA levando-se em conta os efeitos combinados da radiação (TID e SEE) e da interferência eletromagnética (EMI radiada e conduzida); (3) Demonstrar a utilização integrada da metodologia e plataforma para qualificação destes dispositivos e os sistemas em chip utilizados no que diz respeito à dose de radiação, tempo de atraso entre entrada e saída, tensão mínima de funcionamento, consumo de corrente dinâmico, nível de campo eletromagnético máximo suportado antes da falha, a faixa de frequências em que os dispositivos apresentaram falhas com outros valores de campo e a sensibilidade à Single Event Upsets (SEU) tendo seus efeitos combinados com TID e EMI.

Cabe salientar que estas plataformas de testes deste nível e para este propósito não foram encontradas na literatura nem no Brasil nem no exterior, nos motivando ainda mais a pesquisa e o desenvolvimento pela sua originalidade e grande utilidade para projetos que envolvem sistemas em chip utilizando FPGAs quando submetidos à radiação e

à EMI. Principalmente quando aplicado a sistemas embarcados para aplicações críticas.

A plataforma desenvolvida é baseada em três placas específicas e complementares em duas versões. A primeira é dedicada para ensaios com radiação ionizante, e pode ser utilizada em uma câmara aceleradora de partículas ou em uma Gamma Cell (para exposição a raios gama) ou ainda em equipamentos de raios X. A segunda placa é dedicada para o teste de imunidade à EMI radiada utilizando uma *Giga-hertz Transverse Electromagnetic Cell* (GTEM Cell) de acordo com a norma IEC 62.132-2 e a terceira é uma placa de injeção de EMI conduzido pelas linhas de alimentação do circuito, e usou como referência a norma IEC 61.000-4-29.

Com a plataforma e metodologia apresentadas neste trabalho foi possível comprovar que quanto maior a dose de radiação recebida, mais susceptível o dispositivo fica quando exposto à EMI, aumentando em pelo menos 30% a quantidade de falhas, em até 230% o tempo de atraso entre entrada e saída e em até 19% o consumo de corrente dinâmico do dispositivo. Assim como quanto maior a dose de radiação sofrida, maior será a sensibilidade à SEU. Com os limites de operação apresentados para os FPGAs em teste, o projetista pode decidir se o dispositivo está ou não qualificado para o seu uso em determinada aplicação.

Palavras-chaves: Plataformas de teste, Efeitos da radiação, Interferência Eletromagnética, Injeção de ruído, Metodologia de testes, FPGAs, SEE.

#### ABSTRACT

The combined effects of radiation and electromagnetic interference in reconfigurable devices (FPGAs) are explored in this work. The investigated effects can originate from radiated or conducted electromagnetic interference, through ionizing radiation, by accumulation of total dose (Total Ionizing Dose TID) or by Single Event Effects also known as SEE. Since FPGA devices have been increasingly used in critical systems, due to their versatility, performance and robustness, this study contributes to the characterization and qualification of FPGAs devices when operating in noisy environments.

The described scenario resulted in a proposal with three main objectives: (1) The design, development and validation of a platform for combined tests for radiation and electromagnetic interference (conducted and radiated) with reference to IEC 62.132 standards. (2) Development of a methodology to qualify systems on chip (SoC) implemented in FPGA taking into account the combined effects of radiation (TID and SEE) and electromagnetic interference (EMI radiated and conduced); (3) Demonstrate the combined use of the methodology and platform for qualifications of these devices and SoC used with respect to radiation dose, time delay between input and output, minimum operating voltage, the dynamic power consumption, electromagnetic field level supported before failure, the frequency range in which the devices had failures with other field values and sensitivity to Single Event Upsets (SEU) with TID and EMI combined effects.

It should be emphasized that these test platforms, at this level and for this purpose have not been found in the literature either in Brazil or in other countries, motivating this research and development for its originality and use in projects involving systems on chip on FPGAs when exposed to radiation and EMI. Especially when applied to embedded systems for critical applications. The developed platform is based on three specific and complementary boards in two versions. The first one is dedicated to radiation immunity test according to the IEC 62132-2 standard, and can be used in a particle accelerator chamber (e.g. protons)

Gamma Cell (for gamma rays exposure) or in X ray equipment's. The second board is dedicated to radiated noise immunity testing in a Giga-Hertz Transverse Electromagnetic Cell (GTEM Cell) referenced by the IEC 62.132-2 standard. The third one is a board for conducted EMI injection by the circuit supply lines referenced by the IEC 61.000-4-29 standard.

With the platform and methodology presented in this work it was possible to prove that the higher radiation dose received, the more susceptible when exposed to EMI the device is, increasing by at least 30 % the number of failures, up to 230 % the time delay between input and output and up to 19 % dynamic current consuming of the device. As well as the higher the radiation dose suffered, the more sensitivity to SEU is. With operating limits presented for FPGAs under test, the designer can decide if the device is qualified or not for use in a particular application.

**Key-words**: test platforms, effects of radiation, electromagnetic interference, noise injection, testing methodology, FPGAs.

# LISTA DE ILUSTRAÇÕES

| Figura 1 –    | Confiabilidade de sistemas eletrônicos ao longo do                                                                         |    |

|---------------|----------------------------------------------------------------------------------------------------------------------------|----|

|               | $tempo. \dots \dots$ | 34 |

| Figura 2 -    | Cinturões de Radiação de Van Allen                                                                                         | 46 |

| Figura 3 -    | Órbitas dos satélites                                                                                                      | 49 |

| Figura 4 -    | Órbita polar e órbita equatorial de um satélite                                                                            | 50 |

| Figura 5 -    | Classificação dos efeitos da radiação espacial em fun-                                                                     |    |

|               | ção de suas respectivas fontes                                                                                             | 53 |

| Figura 6 -    | Características típicas medidas de tensão $(V)$ e cor-                                                                     |    |

|               | rente (A) de um n<br>MOSFET de 0,4 $\mu\mathrm{m},$ onde é mos-                                                            |    |

|               | trado um aumento da corrente de fuga após a irradiação $$                                                                  | 54 |

| Figura 7 -    | Corrente de fuga do óxido de porta versus tensão de                                                                        |    |

|               | porta para um capacitor não irradiado e um capacitor                                                                       |    |

|               | irradiado a 5,3 $\rm Mrad(Si)$ por raios gama através de                                                                   |    |

|               | Co-60 com uma polarização de porta de -0,3V. $$                                                                            | 57 |

| Figura 8 -    | Curva da Banheira para tempos de falhas ( $Bathtub$                                                                        |    |

|               | <i>Curve</i> )                                                                                                             | 59 |

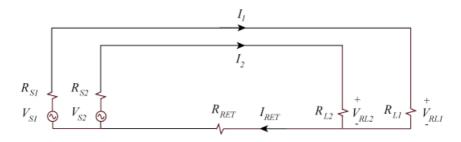

| Figura 9 –    | Dois circuitos compartilhando o caminho de retorno                                                                         |    |

|               | da corrente                                                                                                                | 62 |

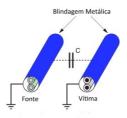

| Figura 10 -   | Campo elétrico acoplado entre dois condutores                                                                              | 63 |

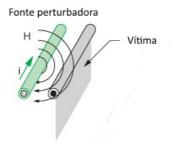

| Figura 11 –   | Campo magnético acoplado entre dois condutores                                                                             | 63 |

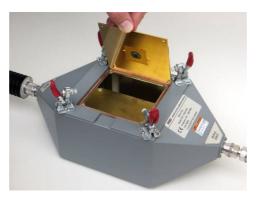

| Figura 12 -   | TEM-Cell customizada utilizada para teste de circui-                                                                       |    |

|               | tos integrados                                                                                                             | 67 |

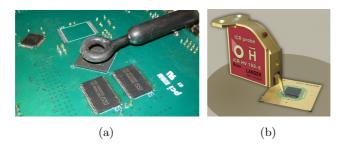

| Figura 13 -   | (a) detalhe de uma ponteira para medir campos pró-                                                                         |    |

|               | ximos provenientes de um CI como um todo. (b)                                                                              |    |

|               | detalhe de uma micro ponteira para medir campos                                                                            |    |

|               | próximos de partes do CI ou de seus pinos                                                                                  | 68 |

| Figura 14 -   | Esquema de teste por injeção de corrente                                                                                   | 69 |

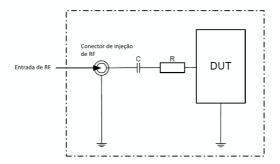

| Figura 15 $-$ | Esquema de teste por injeção direta de RF                                                                                  | 70 |

| Figura 16 –   | GTEM-Cell da Teseq                                                                                                         | 70 |

| Figura 17 –   | GTEM Cell                                                                                                                  | 82 |

| Figura 18 –   | TEM Cell utilizada para teste de PCBs com 10x10cm.                                                                         | 82 |

| Figura 19 — Câmara Gamma Cell com fonte de radiação de Co-60       |      |

|--------------------------------------------------------------------|------|

| para ensaios de radiação no Centro Atômico Ezeiza,                 |      |

| da Comissão Nacional de Energia Atômica em Buenos                  |      |

| Aires Argentina.                                                   | 83   |

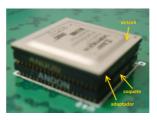

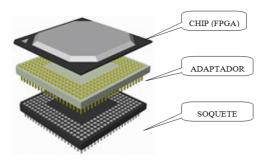

| Figura 20 – Detalhe do soquete e adaptador utilizados para os      |      |

| DUTs na plataforma.                                                | 87   |

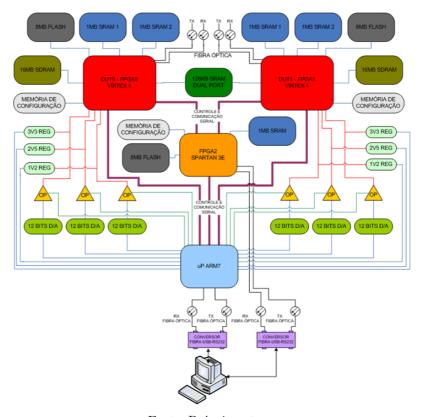

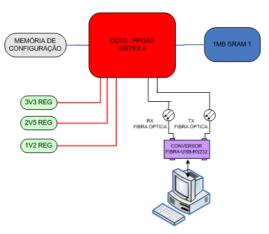

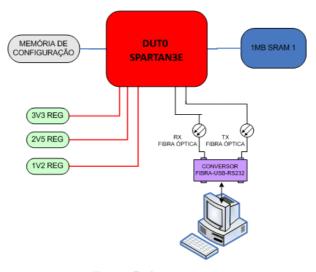

| Figura 21 – Diagrama de blocos da plataforma de testes de EMI      |      |

| radiado                                                            | 87   |

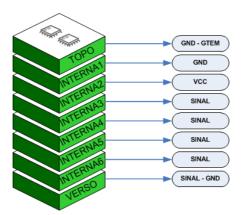

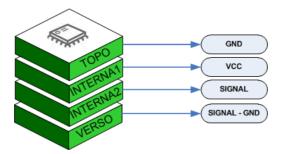

| Figura 22 — Distribuição das camadas na placa de ensaios de EMI    |      |

| radiado                                                            | 89   |

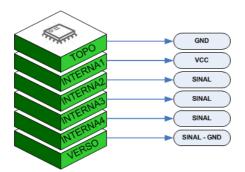

| Figura 23 – Diagrama de blocos da placa de testes de radiação      | 90   |

| Figura 24 – Distribuição das camadas na placa de ensaios de        |      |

| radiação                                                           | 92   |

| Figura 25 — Diagrama do uso do soquete e adaptador para o chip     |      |

| BGA                                                                | 93   |

| Figura 26 — Plataforma para ensaios de radiação                    | 94   |

| Figura 27 — Plataforma para Ensaios de EMI radiado visto do        |      |

| lado de cima da placa                                              | 95   |

| Figura 28 – Plataforma para Ensaios de EMI radiado visto do        |      |

| lado de baixo da placa.                                            | 96   |

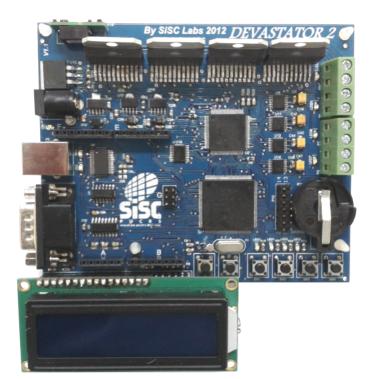

| Figura 29 – Foto da plataforma para ensaios de EMI conduzido.      | 98   |

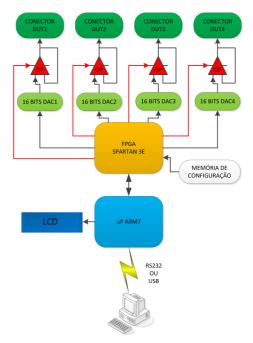

| Figura 30 – Diagrama de blocos da plataforma para ensaios de       |      |

| EMI conduzido.                                                     | 99   |

| Figura 31 – Foto da plataforma de ensaios de EMI radiado visto $$  |      |

| do lado de cima da placa                                           | 101  |

| Figura 32 — Plataforma de ensaios de EMI radiado visto do lado     |      |

| de baixo da placa                                                  | 102  |

| Figura 33 – Diagrama de blocos da plataforma de testes de EMI $$   |      |

| radiado da segunda versão                                          | 103  |

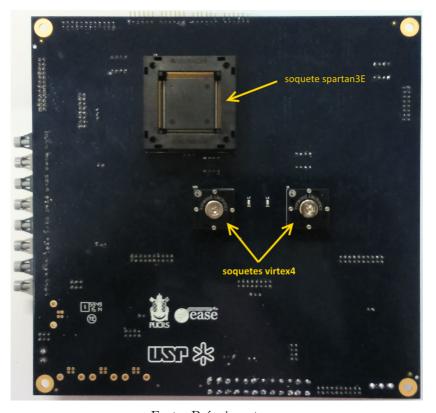

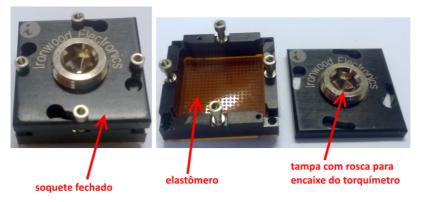

| Figura 34 – Detalhe do soquete utilizado nas Virtex 4              | 106  |

| Figura 35 — Micro torquímetro utilizado para apertar os soquetes — |      |

| da IronWood                                                        | 106  |

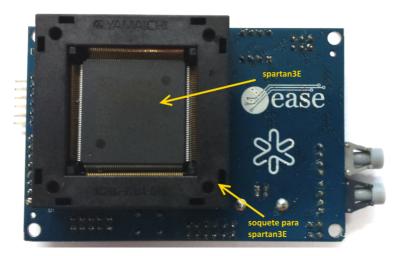

| Figura 36 – Detalhe do soquete Yamaichi utilizado na Spartan 3E    | .107 |

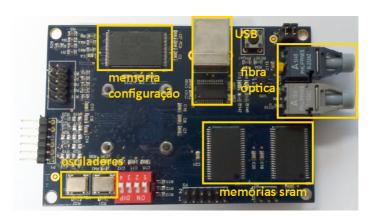

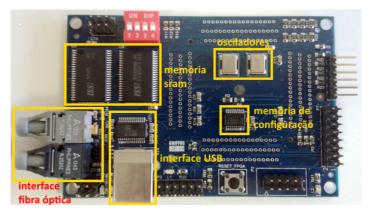

| Figura 37 – | Plataforma de ensaios de radiação para Virtex 4 visto |     |

|-------------|-------------------------------------------------------|-----|

|             | do lado de cima da placa com o detalhe do soquete     |     |

|             | IronWood                                              | 108 |

| Figura 38 – | Plataforma de ensaios de radiação para Virtex 4 visto |     |

|             | do lado de baixo da placa                             | 108 |

| Figura 39 – | Foto da plataforma de ensaios de radiação para Spar-  |     |

|             | tan3E visto do lado de cima da placa                  | 110 |

| Figura 40 – | Foto da plataforma de ensaios de radiação para Spar-  |     |

|             | tan3E visto do lado de baixo da placa                 | 111 |

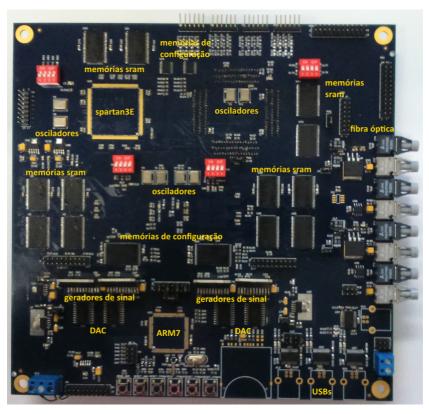

| Figura 41 – | Diagrama de blocos da placa de testes de radiação     |     |

|             | para Spartan3E                                        | 111 |

| Figura 42 – | Distribuição das camadas na placa de ensaios de       |     |

|             | radiação para Spartan3E                               | 113 |

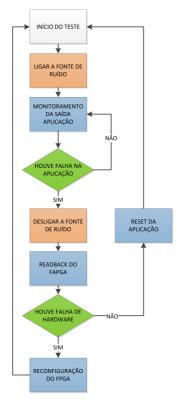

| Figura 43 – | Fluxograma de controle do ensaio                      | 114 |

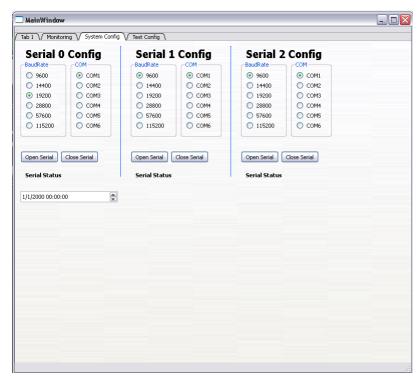

| Figura 44 – | Tela de configuração das portas seriais de comunica-  |     |

|             | ção com a plataforma                                  | 116 |

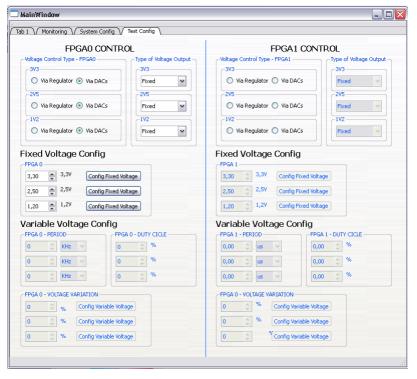

| Figura 45 – | Tela de configuração das alimentações dos FPGAs       |     |

|             | e configuração da injeção de ruído nas linhas de ali- |     |

|             | mentação                                              | 117 |

| Figura 46 – | Tela de monitoração da saída serial, configuração e   |     |

|             | $reset~\mathrm{dos}~\mathrm{FPGAs.}$                  | 119 |

| Figura 47 – | Fluxograma de controle do ensaio                      | 121 |

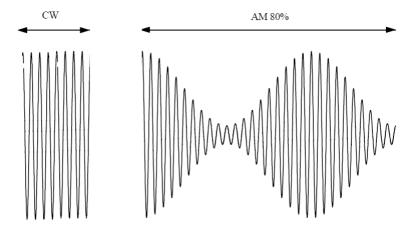

| Figura 48 – | Sinal AM com modulação 80%                            | 137 |

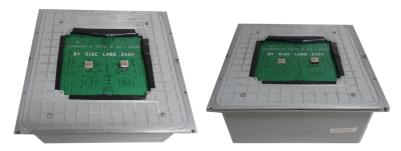

| Figura 49 – | Caixa metálica utilizada como blindagem para en-      |     |

|             | caixe da plataforma para testes de EMI radiado uti-   |     |

|             | lizando a GTEM-CELL                                   | 139 |

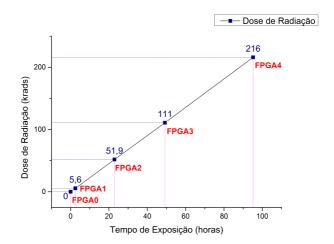

| Figura 50 – | Dose Total e Tempo de Exposição dos FPGAs             | 154 |

| Figura 51 – | Gama Cell com detalhe do suporte com as quatro        |     |

|             | placas inseridas no invólucro de testes da câmara     |     |

|             | (Benfica et al., 2011b)                               | 155 |

| Figura 52 – | Atraso entre entrada e saída do circuito de medição   |     |

|             | nos dispositivos sob teste                            | 156 |

| Figura 53 – | Desvio padrão das medidas de atraso entre entrada     |     |

|             | e saída do circuito para cada dispositivo             | 158 |

| Figura 54 – | Intervalo de confiança das medidas de atraso considerando um nível de confiança de 95%                                                                                                                       | 158 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

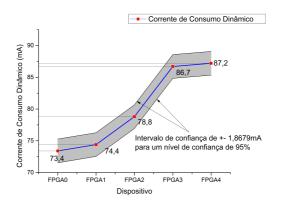

| Figura 55 – | Consumo de corrente dinâmico na alimentação do                                                                                                                                                               | 159 |

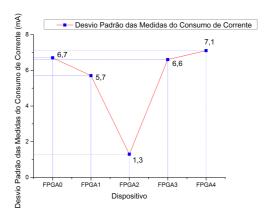

| Figura 56 – | Desvio padrão das medidas do consumo de corrente dinâmico para cada dispositivo                                                                                                                              | 160 |

| Figura 57 – | Intervalo de confiança das medidas de consumo de corrente dinâmico considerando um nível de confiança                                                                                                        |     |

| Figura 58 – | de 95%                                                                                                                                                                                                       | 161 |

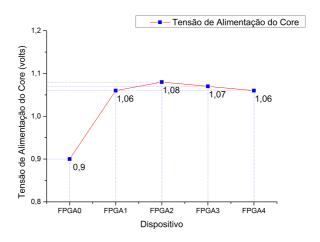

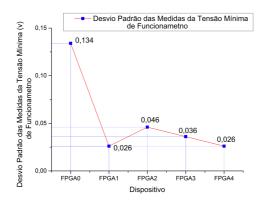

| Figura 59 – | Desvio padrão das medidas de tensão mínima de                                                                                                                                                                | 163 |

| Figura 60 – | funcionamento para cada dispositivo                                                                                                                                                                          | 164 |

|             | de funcionamento considerando um nível de confiança de 95%                                                                                                                                                   | 165 |

| Figura 61 – | GTEM-CELL com o detalhe da plataforma de testes de EMI encaixado na blindagem para os testes de                                                                                                              |     |

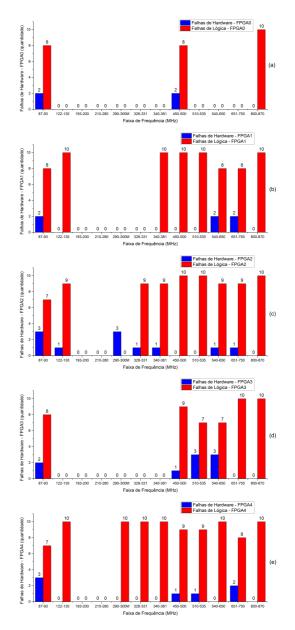

| Figura 62 – | susceptibilidade a EMI (Benfica et al., 2011a) Falhas de lógica por intervalo de frequência utili-                                                                                                           | 166 |

|             | zando tensão de alimentação do core nominal em 1,2V. (a)FPGA0, (b)FPGA1, (c)FPGA2, (d)FPGA3,                                                                                                                 |     |

| Figura 63 - | (e)FPGA4                                                                                                                                                                                                     | 169 |

| Tigara 00   | lizando tensão de alimentação do core nominal em 1,2V. (a)FPGA0, (b)FPGA1, (c)FPGA2, (d)FPGA3,                                                                                                               |     |

| Figura 64 – | (e)<br>FPGA4                                                                                                                                                                                                 | 170 |

|             | tensão de core reduzido. (a) $FPGA0 (1,06V)$ , (b) $FPGA1 (1,06V)$ , (c) $FPGA2 (1,08V)$ , (d) $FPGA3 (1,07V)$ , (e) | 244 |

|             |                                                                                                                                                                                                              | 173 |

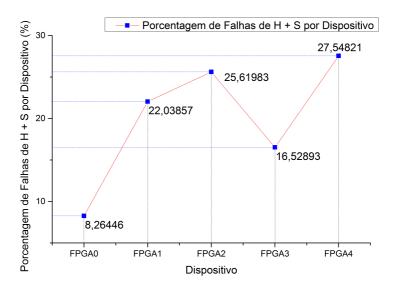

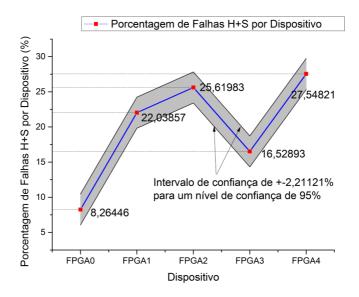

| Figura 65 – | Porcentagem de falhas de Hardware e de Lógica (S) para os testes de EMI                                                                                                                                      | 174 |

| Figura 66 – | Porcentagem de falhas de Hardware e de Lógica (S)       |     |

|-------------|---------------------------------------------------------|-----|

|             | para os testes de EMI com intervalo de confiança de     |     |

|             | 95%                                                     | 175 |

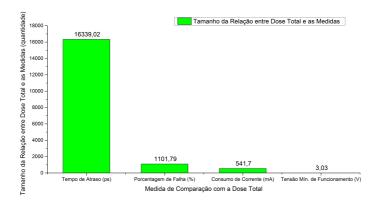

| Figura 67 – | Relação (covariância) entre as medidas utilizadas no    |     |

|             | teste e a dose total                                    | 176 |

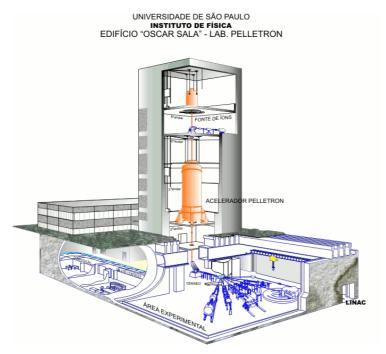

| Figura 68 – | Acelerador Pelletron do LAFN-USP construído pela        |     |

|             | NEC (National Electrostatic Corporation) no Edifício    |     |

|             | Oscar Sala.                                             | 178 |

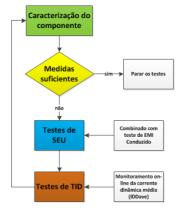

| Figura 69 – | Fluxograma de teste utilizado para os testes nos        |     |

|             | FPGAs Spartan3E.                                        | 180 |

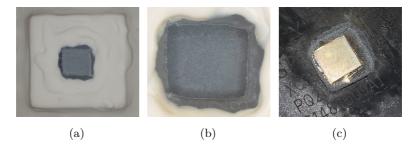

| Figura 70 – | Processo de decapagem dos FPGAs utilizados no teste.    | 181 |

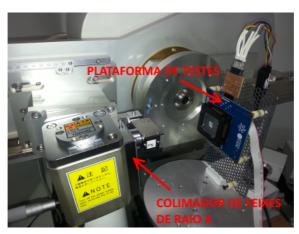

| Figura 71 – | Difractômetro de raio X Shimadzu XRD-7000 utili-        |     |

|             | zado nos testes                                         | 182 |

| Figura 72 – | Detalhe da plataforma de testes sob o feixe de raios X. | 182 |

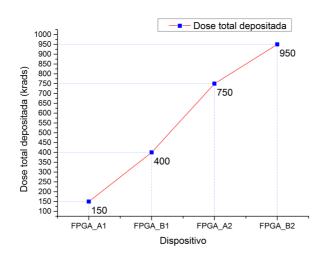

| Figura 73 – | Dose total depositada no FPGA_A e no FPGA_B.            | 184 |

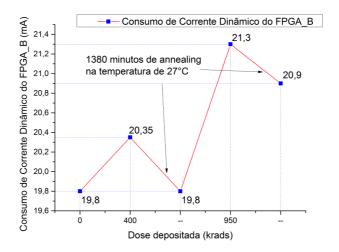

| Figura 74 – | Corrente dinâmica medida para o FPGA_B                  | 185 |

| Figura 75 – | Configuração e disposição dos equipamentos de teste     |     |

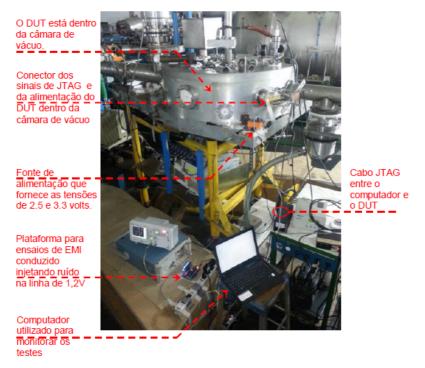

|             | utilizados para os ensaios nos FPGAs Spartan<br>3E      | 186 |

| Figura 76 – | Detalhe da plataforma dentro da câmara de vácuo         |     |

|             | do Pelletron                                            | 187 |

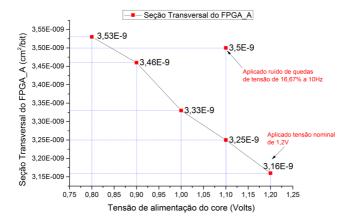

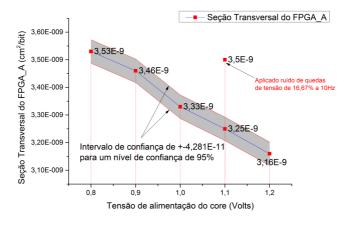

| Figura 77 – | Seção transversal de SEU do FPGA_A em função            |     |

|             | da redução de tensão                                    | 188 |

| Figura 78 – | Seção transversal de SEU do FPGA_A em função da $$      |     |

|             | redução de tensão com intervalo de confiança para       |     |

|             | um nível de confiança de 95%                            | 188 |

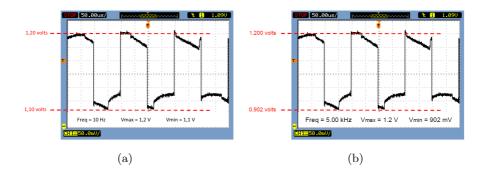

| Figura 79 – | Captura da tela do osciloscópio que mostra a forma      |     |

|             | de ondo injetada nos testes com (a) para o FPGA_A       |     |

|             | e (b) para o FPGA_B                                     | 190 |

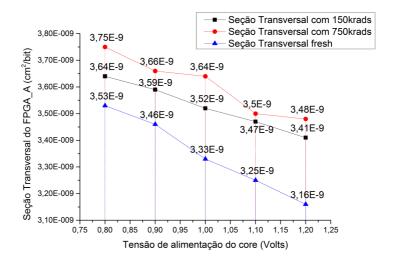

| Figura 80 – | Seção transversal de SEU do FPGA_A em função            |     |

|             | da redução de tensão nas três doses de radiação         | 191 |

| Figura 81 – | Seção transversal de SEU do FPGA_A em função            |     |

|             | da redução de tensão nas três doses de radiação         | 192 |

| Figura 82 –   | Comparação da seção transversal de SEU do FPGA_A $$   |     |

|---------------|-------------------------------------------------------|-----|

|               | em função da redução de tensão e ruído de quedas de   |     |

|               | tensão com frequência de 10Hz com dose de radiação    |     |

|               | de 150 krad                                           | 193 |

| Figura 83 -   | S<br>Comparação da seção transversal de SEU do FPGA_A |     |

|               | em função da redução de tensão e ruído de quedas de   |     |

|               | tensão com frequência de 10Hz com dose de radiação    |     |

|               | de 750 krad                                           | 194 |

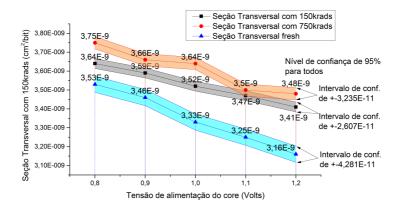

| Figura 84 –   | Seção transversal de SEU do FPGA_A em função          |     |

|               | da redução de tensão nas três doses de radiação       | 195 |

| Figura $85$ – | Seção transversal de SEU do FPGA_A em função          |     |

|               | da redução de tensão nas três doses de radiação com   |     |

|               | o intervalo de confiança                              | 196 |

| Figura 86 $-$ | Seção transversal de SEU do FPGA_B em função          |     |

|               | da redução de tensão sem radiação e com 950 krad. $$  | 198 |

| Figura 87 $-$ | Seção transversal de SEU do FPGA_B em função da       |     |

|               | redução de tensão com intervalo de confiança para     |     |

|               | um nível de confiança de 95%                          | 199 |

### LISTA DE TABELAS

| Tabela 1 –  | Tabela resumo da revisão do estado da arte quanto   |     |

|-------------|-----------------------------------------------------|-----|

|             | as plataformas de testes                            | 78  |

| Tabela 2 –  | Tamanho do passo da frequência versus faixa de      |     |

|             | frequência                                          | 136 |

| Tabela 3 -  | Níveis de tensão e duração utilizados no teste de   |     |

|             | quedas de tensão (Voltage Dips)                     | 144 |

| Tabela 4 –  | Níveis de tensão e duração utilizados no teste de   |     |

|             | curtas interrupções (Short Interruptions)           | 145 |

| Tabela 5 –  | Níveis de tensão e duração utilizados no teste de   |     |

|             | variação de tensão (Voltage Variation)              | 145 |

| Tabela 6 –  | Qualificação dos FPGAs utilizados nos testes para   |     |

|             | tensão nominal de alimentação do core e campo apli- |     |

|             | cado de $100V/m$                                    | 202 |

| Tabela 7 –  | Qualificação dos FPGAs utilizados nos testes para   |     |

|             | tensão de alimentação do core mínima para funcio-   |     |

|             | namento e campo aplicado de $125 \text{V/m}$        | 203 |

| Tabela 8 –  | Qualificação dos FPGAs para as faixas de frequência |     |

|             | utilizadas para o campo de 125V/m e tensão mínima   |     |

|             | de funcionamento                                    | 204 |

| Tabela 9 –  | Qualificação do FPGA_A em função da tensão de       |     |

|             | funcionamento e da dose de radiação com a seção     |     |

|             | transversal de SEU                                  | 206 |

| Tabela 10 – | Qualificação do FPGA_B em função da tensão de       |     |

|             | funcionamento e da dose de radiação com a seção     |     |

|             | transversal de SEU                                  | 207 |

#### LISTA DE ABREVIATURAS E SIGLAS

ABS - Anti-Blocking System

BGA -Ball Grid Array

CGS - centímetro, grama, segundo

CI - Circuito Integrado

CLB -Combinational Logic Blocks

CMOS - Complementary Metal Oxide Semiconductor.

COTS - Commercial Off-The-Shelf

DCM - Digital Clock Manager

DD - Displacement Damage

EMC - Electromagnetic Compatibility.

$\operatorname{EMI}$  -  $\operatorname{Electromagnetic}$  Interference.

EOT - Equivalent Oxide Thickness

EPRI - Electric Power Research Institute

FPGA – Field Programmable Gate Array.

GEO - Geostationary Earth Orbit

$\label{eq:GTEM-GigaHertz} GTEM-GigaHertz\ Transverse\ EletroMagnetic.$

I/O – Input / Output.

${\bf IEC\ -\ International\ Electrotechnical\ Commission}.$

INTI – Instituto Nacional de Tecnologia Industrial.

LEO - Low Earth Orbit

LOCOS - Local Oxidation of Silicon

LUT - Look Up Table

MEO - Medium Earth Orbit

MeV - Megaelétron-volts

MKS - Metro, Kilo e segundo

MOS - Metal Oxide Semiconductor.

MOSFET - Metal Oxide Silicon Field Effect Transistor.

MTBF - Mean Time Between Failures

NBTI - Negative bias temperature instability

NMOS - Negative Metal Oxide Semiconductor

P&D – Projeto e Desenvolvimento.

PCB - Printed Circuit Board.

PMOS - Positive Metal Oxide Semiconductor

POF - Physics of Failure

Qc - Carga crítica

RAM - Random Access Memory.

RF - Radiofrequência

RILC - Radiation-Induced Leakage Current

SEB - Single Event Burnout

SEE - Single Event Effects

SEGR - Single Event Gate Rupture

SEL - Single Event Latchup

SET - Single Event Transient

SEU - Single Event Upset

SHE - Single Hard Error

SiSC – Sistemas Sinais e Computação – Laboratório da PUCRS.

SNM - Static Noise Margin

SoC – System on Chip.

SRAM - Static Random Access Memory.

TID - Total Ionizing Dose

VHDL - Very High Speed Integrated Circuit Hardware Description Language.

## SUMÁRIO

| 1       | REFERENCIAIS TEURICUS                                | 31        |

|---------|------------------------------------------------------|-----------|

| 1       | INTRODUÇÃO                                           | 33        |

| 1.1     | MOTIVAÇÃO                                            | 35        |

| 1.2     | OBJETIVOS                                            | 39        |

| 1.3     | CONTRIBUIÇÕES                                        | 41        |

| 2       | ESTADO DA ARTE                                       | 45        |

| 2.1     | ANÁLISE DOS EFEITOS DA RADIAÇÃO .                    | <b>45</b> |

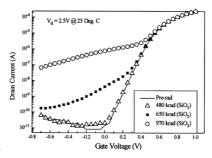

| 2.1.1   | Efeitos da Dose Total                                | 54        |

| 2.1.1.1 | Desvios na Tensão de Limiar de Transistores          | 55        |

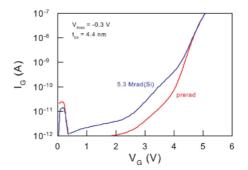

| 2.1.1.2 | Fuga de Corrente Induzida por Radiação               | 56        |

| 2.1.1.3 | Degradação da Mobilidade de Portadores               | 57        |

| 2.1.1.4 | Análise dos Efeitos do Envelhecimento (Aging) causa- |           |

|         | dos pela Radiação                                    | 58        |

| 2.1.1.5 | NBTI                                                 | 60        |

| 2.2     | ANÁLISE DOS EFEITOS DE EMI                           | 60        |

| 2.2.1   | EMC Interno ao Chip                                  | 61        |

| 2.2.1.1 | Crosstalk                                            | 61        |

| 2.2.1.2 | Acoplamento por Impedância Comum                     | 61        |

| 2.2.1.3 | Acoplamento por Campo Elétrico                       | 62        |

| 2.2.1.4 | Acoplamento por Campo Magnético                      | 63        |

| 2.2.1.5 | Ruído de Chaveamento Simultâneo                      | 64        |

| 2.2.2   | Acoplamento Externo de EMC                           | 64        |

| 2.2.2.1 | Acoplamento Conduzido                                | 65        |

| 2.2.2.2 | Acoplamento por Campo Elétrico                       | 65        |

| 2.2.2.3 | Acoplamento por Campo Magnético                      | 65        |

| 2.2.2.4 | Acoplamento por Campo Radiado                        | 66        |

| 2.2.3   | Técnicas Básicas para Medir EMC em Circui-           |           |

|         | tos Integrados                                       | 66        |

| 2.2.3.1 | Medição de Emissão de EMC                            | 66        |

| 2.2.3.2 | Medição de Susceptibilidade à EMC                    | 69        |

| 2.3     | PLATAFORMAS DE TESTE 71                          |

|---------|--------------------------------------------------|

| II      | MATERIAIS E MÉTODOS 79                           |

| 3       | PLATAFORMA DE TESTES 81                          |

| 3.1     | PRIMEIRA VERSÃO DA PLATAFORMA 81                 |

| 3.1.1   | Placa para Ensaios de EMI Radiado 83             |

| 3.1.2   | Placa para Ensaios de Radiação 89                |

| 3.1.3   | Funcionamento da Plataforma 92                   |

| 3.1.4   | Placa para Ensaios de EMI Conduzido 96           |

| 3.1.4.1 | Funcionamento da Plataforma                      |

| 3.2     | SEGUNDA VERSÃO DA PLATAFORMA 100                 |

| 3.2.1   | Placa para Ensaios de EMI Radiado 101            |

| 3.2.2   | Placa para Ensaios de Radiação para Virtex 4 107 |

| 3.2.3   | Placa para Ensaios de Radiação para Spartan      |

|         | 3E                                               |

| 3.2.4   | Conversor Fibra Óptica para USB 114              |

| 3.3     | SOFTWARE DE CONTROLE                             |

| 3.3.1   | Automação do Ensaio                              |

| 4       | METODOLOGIA PARA ENSAIOS COMBI-                  |

|         | NADOS DE RADIAÇÃO E EMI 123                      |

| 4.1     | METODOLOGIA PARA ENSAIOS DE RA-                  |

|         | DIAÇÃO POR DOSE TOTAL 124                        |

| 4.1.1   | Finalidade                                       |

| 4.1.2   | <b>Definições</b>                                |

| 4.1.3   | Plano de Teste                                   |

| 4.1.4   | Equipamentos                                     |

| 4.1.4.1 | Fontes de Radiação                               |

| 4.1.4.2 | Sistema de Dosimetria                            |

| 4.1.4.3 | Equipamentos para Testes Elétricos 127           |

| 4.1.4.4 | Placa de Circuito para Teste                     |

| 4.1.4.5 | Cabeamento                                       |

| 4.1.5   | Caracterização                                   |

| 4.1.6    | Seleção da Amostra e Manuseio 130              |

|----------|------------------------------------------------|

| 4.1.7    | Medições de Dosimetria                         |

| 4.1.8    | Níveis de Radiação                             |

| 4.1.9    | Taxa de Dose de Radiação 131                   |

| 4.1.10   | Requisitos de Temperatura 131                  |

| 4.1.11   | Condições de Teste                             |

| 4.1.11.1 | Procedimento Pós-Irradiação                    |

| 4.2      | METODOLOGIA PARA ENSAIOS DE EMI                |

|          | RADIADO                                        |

| 4.2.1    | Finalidade                                     |

| 4.2.2    | Definições                                     |

| 4.2.3    | Plano de Teste                                 |

| 4.2.4    | Caracterização                                 |

| 4.2.5    | Condições do Teste                             |

| 4.2.5.1  | Temperatura Ambiente                           |

| 4.2.5.2  | Ambiente RF 135                                |

| 4.2.5.3  | Gerador de Teste                               |

| 4.2.5.4  | Faixa de Frequência e Passos de Frequência 136 |

| 4.2.5.5  | Modulação em Amplitude                         |

| 4.2.5.6  | Tempo de Permanência da Fonte de Ruído 137     |

| 4.2.6    | Equipamentos                                   |

| 4.2.6.1  | Gerador de Ruídos RF                           |

| 4.2.6.2  | TEM Cell                                       |

| 4.2.6.3  | GTEM Cell de Banda Larga                       |

| 4.2.6.4  | Amplificador de RF                             |

| 4.2.6.5  | Analisador de Campo Elétrico                   |

| 4.2.6.6  | Classificação de Falhas                        |

| 4.3      | METODOLOGIA PARA ENSAIOS DE EMI                |

|          | CONDUZIDO                                      |

| 4.3.1    | Finalidade                                     |

| 4.3.2    | <b>Definições</b>                              |

| 4.3.3    | Plano de Teste                                 |

| 4.3.4    | Equipamentos                                   |

| 4.3.5    | Condições do Teste                             |

| 4.3.5.1    | Temperatura Ambiente                          | 3 |

|------------|-----------------------------------------------|---|

| 4.3.5.2    | Ambiente de RF                                | 3 |

| 4.3.5.3    | Níveis de Teste                               | 3 |

| III        | ETAPA DE VALIDAÇÃO 14'                        | 7 |

| 5          | EXPERIMENTOS E RESULTADOS 149                 | 9 |

| 5.1        | ANÁLISE ESTATÍSTICA DOS RESULTADOS14          | 9 |

| 5.1.1      | Variância                                     | 0 |

| 5.1.2      | Desvio Padrão                                 | 0 |

| 5.1.3      | Margem de Erro                                | 1 |

| 5.1.4      | Intervalo de Confiança                        | 1 |

| 5.1.5      | Covariância                                   | 1 |

| <b>5.2</b> | EXPERIMENTOS DE RADIAÇÃO IONIZANTE            |   |

|            | POR TID UTILIZANDO CO-60 15                   | 2 |

| 5.2.1      | Medição do Atraso                             | 6 |

| 5.2.2      | Medição do consumo de corrente dinâmico 159   | 9 |

| 5.2.3      | Cálculo da covariância entre a dose total e o |   |

|            | tempo de atraso                               | 1 |

| 5.2.4      | Cálculo da covariância entre a dose total e o |   |

|            | consumo de corrente                           | 1 |

| 5.3        | EXPERIMENTOS DE EMI RADIADO 16                | 2 |

| 5.3.1      | Medição da tensão mínima de funcionamento     |   |

|            | do FPGA                                       | 2 |

| 5.3.2      | Cálculo da covariância entre a dose total e a |   |

|            | tensão mínima de funcionamento 16             | 5 |

| 5.3.3      | Realização dos testes de EMI na câmara GTEM16 | 5 |

| 5.3.4      | Cálculo da covariância entre a dose total e a |   |

|            | porcentagem de falhas                         | 5 |

| 5.3.5      | Análise da Covariância dos Resultados 17      | 5 |

| <b>5.4</b> | EXPERIMENTOS DE SEU COMBINADOS                |   |

|            | COM EMI CONDUZIDO E TID 17                    | 7 |

| 5.4.1      | Análise de Covariância dos Resultados 199     | 9 |

| <b>5.5</b> | EXPERIMENTOS DE EMI CONDUZIDO 200            |

|------------|----------------------------------------------|

| 5.6        | QUALIFICAÇÃO DE DISPOSITIVOS RE-             |

|            | CONFIGURÁVEIS 201                            |

| 5.6.1      | Qualificação para os testes de EMI e TID 201 |

| 5.6.2      | Qualificação para os testes de SEU, TID e    |

|            | EMI Conduzido                                |

| 6          | CONCLUSÃO                                    |

|            | Referências                                  |

# Parte I REFERENCIAIS TEÓRICOS

### 1 INTRODUÇÃO

O trabalho aqui apresentado envolve o projeto, desenvolvimento e validação de uma plataforma e metodologia para a análise da robustez de sistemas embarcados mapeados em dispositivos reconfiguráveis (FPGAs SRAM (Static Random Access Memory) do tipo COTS (commercial off-the-shelf)) quando submetidos à radiação e à interferência eletromagnética (do inglês, Electromagnetic Interference ou EMI) conduzida e radiada, bem como a qualificação destes dispositivos quanto ao seu funcionamento mediante a dose de radiação e a exposição ao ruído de EMI.

Os efeitos da EMI sobre componentes que foram submetidos à radiação, é um estudo recente e de cada vez mais importância para aplicações aeroespaciais, pois tal efeito leva os sistemas a se comportarem de maneira diferente da especificação e consequentemente provoque uma falha.

Nos dias de hoje é muito importante saber como os circuitos eletrônicos operam em ambientes ruidosos e sob interferência intensa e contínua, principalmente no meio industrial, militar e espacial, onde esses circuitos operam em velocidades cada vez maiores e com tensões de alimentação cada vez menores. Estes dispositivos estão cada vez mais suscetíveis à ruídos do ambiente e também provenientes de outros dispositivos. Os circuitos eletrônicos por operarem em altas velocidades e manipularem cargas de alta potência, são também grandes fontes de ruído.

Dado que os dispositivos lógicos programáveis, neste caso os FPGAs, são cada vez mais utilizados em sistemas eletrônicos críticos, onde sua operação dentro das especificações é imprescindível para a segurança do sistema como um todo, mesmo quando operando em ambientes expostos aos efeitos da radiação e da interferência eletromagnética. Então, um estudo de caso da análise dos efeitos da radiação e de EMI em FPGAs será apresentado neste trabalho. Os sistemas integrados em um único circuito integrado (do inglês, *Systems-on-Chip* ou SoC) avançam na sua utilização e aplicação. Com isto, reforçamos a importância do

trabalho aqui apresentado.

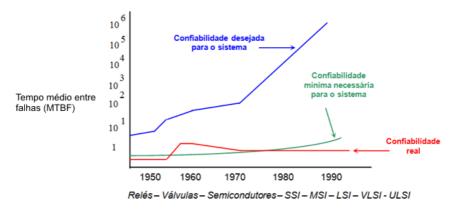

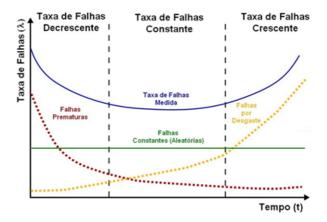

Embora se possa observar um grande aumento na quantidade e na qualidade de pesquisas visando o aumento do nível de confiabilidade de sistemas de hardware/software, a Figura 1, extraída de um dos livros clássicos da literatura envolvendo o projeto de sistemas tolerantes a falhas (Pradhan, 1996), ilustra o dramático aumento da diferenca entre a confiabilidade desejada para sistemas eletrônicos e a confiabilidade real verificada destes sistemas. Isto se deve basicamente devido ao fato destes sistemas serem cada vez mais complexos, baseando seu desempenho em tecnologias do tipo SoC (Crouch, 1999) de dezenas de milhões de transistores, de diferentes fabricantes, que por muitas vezes estão implementados em vários nós de uma rede em um sistema distribuído, com sistema operacional multitarefa, e multiusuário. Ainda em muitos casos, tipicamente naqueles sistemas destinados para eletrônica embarcada alimentada por baterias, o baixo consumo é outro fator agravante (Girard, 2002). Nestes casos, técnicas que aumentam a confiabilidade do sistema sem aumentar consumo são fortemente desejadas, e em muitos casos, a única solução possível.

Figura 1 – Confiabilidade de sistemas eletrônicos ao longo do tempo.

Fonte: (Pradhan, 1996).

Com base nestes estudos estamos propondo uma plataforma de testes combinados para ensaios de radiação onde se possa efetuar testes com Single Event Upsets (SEU) e Total Ionizing Dose (TID), EMI irradiado e conduzido (através das linhas de alimentação) em FPGAs para verificação da confiabilidade e robustez do sistema.

# 1.1 MOTIVAÇÃO

A área de Projeto e Desenvolvimento (P&D) envolvendo o projeto de sistemas robustos tem crescido consideravelmente nos últimos anos tanto no Brasil quanto no exterior. Porém, tem-se verificado ao mesmo tempo uma lacuna crescente nas pesquisas integrando o coprojeto de Hardware-Software com critérios de confiabilidade (detecção e diagnóstico de falhas) em ambientes de interferência eletromagnética. Neste sentido, especial atenção deve ser dedicada aos sistemas embarcados baseando seu funcionamento e desempenho em tecnologias do tipo SoCs complexos que necessitam, além de confiabilidade o alto desempenho para atender aplicações em tempo real (Kathail et al., 2002), (Wolf, 2012). O ambiente ruidoso em que os sistemas eletrônicos têm que operar, está tornando-se cada vez mais hostil devido as altas emissões de ruídos por circuitos que operam em altas velocidades e manipulam cargas de alta potência. Por outro lado estes circuitos estão se tornando cada vez mais suscetíveis a ruídos devido à sua tecnologia de fabricação que é cada vez menor bem como sua tensão de alimentação. A necessidade da garantia de que os circuitos eletrônicos operem em ambientes ruidosos é fundamental para a aceitação e segurança de sistemas eletrônicos para este fim. Podemos citar alguns exemplos de sistemas eletrônicos que necessitam uma garantia de funcionamento em ambientes ruidosos:

Aplicações aeronáuticas onde a tolerância ao funcionamento de telefones celulares que emitem ondas de rádio frequência no interior da aeronave, mesmo que recomendado o não uso, podem afetar os equipamentos de controle de voo, é obrigatória;

- 2. Indústria automotiva, que possui equipamentos eletrônicos de grande importância para o funcionamento e segurança do automóvel e de seus condutores tais como controle de freios ABS (do inglês Anti-Blocking System), injeção eletrônica, controle de tração ativa dentre outros equipamentos que tem de tolerar altos níveis de ruídos;

- 3. Equipamentos médico-hospitalares, que caracterizam uma aplicação extremamente crítica podendo-se perder vidas caso falhas ocorram no equipamento devido a distúrbios oriundos da rede elétrica e de interferência eletromagnética, por exemplo.

Associado a aplicações críticas, temos ainda a dificuldade de obtenção de componentes qualificados para utilização em aplicações aeroespaciais. Essa dificuldade inicialmente se devia ao alto valor dessa categoria de componente. O Brasil ainda não possui iniciativas de grande impacto na área de análise dos efeitos da radiação e de EMI em circuitos integrados e sua operação em ambientes ruidosos que é uma área estratégica para a soberania nacional.

Assim é importante compreender como as tecnologias atuais impactam na nova geração de projetos de SoCs. Nota-se que, embora a redução das tensões de alimentação (pelo menos para o core) aumente a esperança de que ocorrerá uma menor emissão de interferência eletromagnética tanto conduzida quanto radiada devido a corrente de modo comum, este benefício é compensado imediatamente por: (a) o drástico aumento de transistores comutando ao mesmo tempo por circuito integrado (CI), combinado com a alta velocidade destas comutações devido às crescentes frequências de *clock*. Todas estas características geram a interferência eletromagnética que aumenta o ruído total, e que pode afetar blocos de funções dentro do CI assim como outros CIs colocados nas suas proximidades e que podem estar gerando algum tipo de ruído; (b) a reduzida tensão de alimentação que minimiza as margens de ruído sob os quais o CI foi projetado para operar. Isto torna os blocos funcionais internos ao CI mais sensíveis à EMI devido a relação sinal/ruído ser muito baixa, ou seja, a tensão de alimentação está muito próxima

dos níveis de ruído. Estes efeitos podem ser ainda mais danosos quando o circuito integrado é submetido a radiação, devido a degradação do circuito e ao acúmulo de cargas nas camadas isolantes, propiciando aumentar a corrente de fuga do circuito.

FPGAs ainda não são amplamente utilizados como o elemento de processamento central de computadores de bordo, mas recentemente FPGAs da Microsemi, por exemplo, foram utilizados em subsistemas tais como gerência de comandos e dados (command and data handling), controle de atitude e instrumentos científicos (Foundation, 2013). Xilinx e Altera, os principais fabricantes de FPGAs, também possuem componentes para uso militar e aeroespacial. Algumas das vantagens dos FPGAs em relação a lógica discreta nessas aplicações, incluem o tamanho e peso reduzidos da placa, melhoria nos níveis de confiabilidade com a redução na quantidade de pinos de entrada e saída (pontos de solda), e a possibilidade de realizar alterações em partes do hardware do sistema, após o lançamento da missão. Essas alterações podem ser realizadas pelo envio de novas configurações (bitstreams) para o FPGA por canais de telecomando. Essa é uma importante vantagem no uso de FPGAs, pois permite que este dispositivo possua funcionalidades diferentes, de acordo com os requisitos da missão.

De acordo com o plano diretor 2011-2015 divulgado pelo Instituto Nacional de Pesquisas Espaciais (INPE) (www.inpe.br/noticias), e a partir de informações obtidas em um edital também do INPE disponibilizado em 2012, sabe-se que o computador de bordo utilizará um microprocessador da forma convencional (não embarcado em FPGAs ou ASICs), mas que o interesse para missões futuras é no uso de lógica reconfigurável, mais exatamente, microprocessadores embarcados em FPGAs. Apesar da necessidade de seguir uma linha conservadora na área espacial, devido ao alto custo associado à possível perda de uma missão pelo uso de tecnologia ainda não estabelecida nesse tipo de aplicação. Os atrativos do uso de tecnologia reconfigurável são uma importante motivação para investimentos nessa linha de pesquisa. Até a presente data, FPGAs reconfiguráveis foram utilizados por agências espaciais em outros países como elementos de processamento (e não apenas como

lógica de "cola", glue logic) apenas em satélites de aplicações científicas e, objetivamente, como uma forma de estudar os efeitos da radiação nesses componentes. Porém, devido às inúmeras vantagens associadas ao uso de lógica reconfigurável, tais como reconfiguração de todo o hardware por exemplo, existe uma tendência nos diversos programas espaciais em incentivar pesquisas no desenvolvimento de aplicações e utilização efetiva de lógica reconfigurável em computadores de bordo. Com isso fica a evidência da extrema importância da análise dos efeitos da radiação e de EMI em FPGAs, bem como uma plataforma completa para analisar estes efeitos.

A utilização de plataformas de teste e desenvolvimento de SoCs comerciais para fins de avaliação da imunidade à EMI, neste caso, não são uma boa opção, já que seu projeto não foi concebido para testes à EMI e para a analise dos efeitos da radiação e qualificação de dispositivos. Dispositivos da linha comercial "COTS" (do inglês, commercial off-theshelf) usualmente não são utilizados em aplicações espaciais já que não foram projetados para operar neste tipo de ambiente. Entretanto o desejo de se utilizar dispositivos "COTS" em aplicações espaciais é muito grande, já que o custo pode ser cerca de 20 vezes menor com relação à um dispositivo de grade espacial (Radiation-Hardened) que é projetado para suportar maiores doses de radiação. Este fato torna o custo de um projeto para aplicações espaciais extremamente elevado, dado que um satélite as vezes é lançado para operar por apenas três anos. Todo este custo em determinados casos poderia ser reduzido drasticamente se fossem utilizados componentes COTS. Porém para a utilização de componentes da linha comercial em aplicações espaciais, se faz necessário excessivos testes para sua qualificação com o objetivo de levantar os níveis de radiação e de EMI que o dispositivo suporta para a aplicação desejada. Com estes testes é possível conhecer os limites de operação do dispositivo, quando operados sob os efeitos da radiação ionizante combinados com EMI. De posse destes dados, o projetista pode realizar um projeto específico para uma aplicação espacial, ou outra, pois os limites de operação são conhecidos para a utilização destes dispositivos.

1.2. OBJETIVOS 39

Para efetuar todos estes testes de qualificação de dispositivos da linha comercial se faz necessário uma metodologia e uma plataforma de testes, que é objetivo principal dessa tese. Diante das informações, ficou claro que existe uma lacuna de projeto, pesquisa e desenvolvimento neste assunto, e isto levou a proposta de uma plataforma de prototipagem reconfigurável para avaliar, qualificar e aprimorar projetos de SoCs em FPGAs levando em conta sua imunidade à EMI juntamente com a análise dos efeitos da radiação por dose total e por "SEU"baseados em padrões, procedimentos e regras de projeto de normas internacionais.

O conjunto de normas comerciais IEC 62.132 (Commission, 2003) que é dedicado à medição da imunidade de circuitos integrados à interferência eletromagnética conduzida e radiada, foi escolhido como referência para a proposta de projeto da plataforma e da metodologia de testes, ambos propostos neste trabalho.

#### 1.2 OBJETIVOS

Este trabalho possui três principais objetivos, que são:

1. O projeto, desenvolvimento e validação de uma plataforma para ensaios combinados de radiação e de interferência eletromagnética conduzida e radiada. Esta plataforma é composta por três placas distintas, sendo a primeira para ensaios de imunidade a interferência eletromagnética radiada e conduzida, a segunda para testes com radiação, e a terceira para geração de EMI conduzido através das linhas de alimentação. O desenvolvimento da plataforma usa como referência o conjunto de normas comerciais IEC 62.132-1 e IEC 62.132-2 que é dedicado para teste de circuitos integrados. Cabe salientar que estas plataformas de testes deste nível e para este propósito não foram encontradas na literatura nem no Brasil nem no exterior, até o presente momento, nos motivando ainda mais a pesquisa e o desenvolvimento pela sua originalidade e grande utilidade para projetos que envolvem sistemas em chip utilizando FPGAs quando submetidos à radiação e à EMI;

- 2. Desenvolver uma metodologia para qualificar sistemas em chip (SoCs) implementados em lógica reconfigurável (FPGA) levandose em conta os efeitos combinados da radiação (TID e SEE) e da interferência eletromagnética (EMI radiada e conduzida), o qual afeta drasticamente circuitos integrados fabricados em nanotecnologia. A metodologia de testes proposta usou como referência e embasamento as normas IEC 62.132-2 e MIL-STD-883E;

- 3. Demonstrar a utilização integrada da metodologia e plataforma para qualificação destes dispositivos e os sistemas em chip utilizados no que diz respeito à dose de radiação, tempo de atraso entre entrada e saída, tensão mínima de funcionamento, consumo de corrente dinâmico, nível de campo eletromagnético máximo suportado antes da falha e faixa de frequências em que os dispositivos apresentaram falhas com outros valores de campo. Será analisado também a sensibilidade à "SEU"tendo seus efeitos combinados com TID e EMI.

Além do objetivo principal, este trabalho tem como objetivos secundários os seguintes:

- Análise do comportamento de FPGAs do tipo SRAM quando expostos à EMI após terem sido expostos a radiação ionizante, já que foi comprovado que um FPGA que foi exposto à radiação ficou mais susceptível à EMI;

- Demonstrar a aplicabilidade da plataforma desenvolvida para validar SoCs;

- Verificar a robustez da plataforma em função de ensaios de EMI de acordo com o conjunto de normas IEC 62.132, dado que a norma define que os componentes que não fazem parte do teste não devem ser afetados pela EMI;

- Validar o funcionamento da plataforma de injeção de EMI conduzido pelas linhas de alimentação do circuito referenciado pela

norma IEC 61.000-4-29, que descreve os procedimentos para a variação de tensão de alimentação, tais como pequenas interrupções e quedas de tensão.

Com a utilização desta plataforma e metodologia podemos formar mão de obra adequada e qualificada nestes laboratórios para a realização de tais procedimentos de testes e qualificação de sistemas em chip nas principais instalações laboratoriais do Brasil e Argentina dedicados para ensaios de radiação e EMI utilizados neste trabalho.

Cabe salientar que esta plataforma possibilitará efetuar uma ampla gama de estudos em dispositivos lógicos reconfiguráveis no que diz respeito a sua robustez à EMI e aos efeitos da radiação por dose total e por "SEU". Também é importante ressaltar que o projeto e desenvolvimento da plataforma aqui proposta trata-se de um projeto 100% nacional.

# 1.3 CONTRIBUIÇÕES

O projeto de sistemas embarcados para aplicações espaciais depende de uma série de fatores para os quais este trabalho contribui diretamente. Podemos citar as principais:

- Recursos humanos de alto nível de conhecimento em projeto de software, projeto de hardware, projeto de sistemas embarcados, técnicas de tolerância a falhas, normas internacionais para ensaios de interferência eletromagnética conduzida e radiada e efeitos da radiação em dispositivos eletrônicos, bem como a combinação dos mesmos;

- A segunda versão desta plataforma foi utilizada como base de validação dos **primeiros testes de "SEU"realizados no Brasil utilizando dispositivos reconfiguráveis** sob o projeto de título "Desenvolvimento de Metodologia de Ensaios de Radiação em Componentes Eletrônicos"que foi financiado pela Fundação de

Amparo a Pesquisa do Estado de São Paulo (FAPESP), cujo o número do processo é 2012/03383-5. Os participantes deste projeto são a Pontifícia Universidade Católica do Rio Grande do Sul (PUCRS), Universidade Federal de Santa Catarina (UFSC), Instituto de Física da Universidade de São Paulo (IFUSP) e Centro Universitário da Fundação Educacional Inaciana (FEI);

- Demanda do programa espacial brasileiro através do projeto CI-TAR do Instituto Nacional de Pesquisas Espaciais (INPE), no qual colaboramos na pesquisa e desenvolvimento de plataformas de testes para qualificação de FPGAs quanto aos níveis de radiação e de EMI à serem utilizadas, em satélites brasileiros. Essa colaboração contempla o projeto e desenvolvimento da terceira versão da plataforma que está em desenvolvimento;

- Investimentos por parte dos órgãos de fomento, tais como o Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) e a Financiadora de Estudos e Projetos (FINEP);

- Laboratórios equipados com plataformas de prototipação e equipamentos de testes e medidas para a análise destes efeitos em dispositivos eletrônicos.

Os resultados dessa pesquisa representam um grande impacto não só no Brasil, mas também a nível mundial, uma vez que passamos a dominar uma área de altíssimo valor agregado e de extrema importância estratégica e até de soberania nacional. Com relação à investigação visando a qualificação dos dispositivos e o aumento de confiabilidade, foi dada uma atenção especial no que se refere aos efeitos de EMI em componentes expostos a radiação. Essa investigação realizada durante o doutorado representou uma inovação a nível mundial. Essa pesquisa se justificou, devido a maior sensibilidade dos componentes eletrônicos, resultante da miniaturização dos mesmos, e aumento da emissão de interferência eletromagnética devido a fontes wireless, sinais de clock mais elevados, entre outros. Considera-se como contribuições originais obtidas com este trabalho as seguintes:

- Uma plataforma completa com tecnologia nacional para testes combinados de radiação e interferência eletromagnética em dispositivos reconfiguráveis visando lógica reconfigurável (FPGAs) da linha comercial (COTS) para uso na indústria aeroespacial;

- 2. A validação desta plataforma cujos testes foram realizados nos laboratórios do Instituto de Física da Universidade de São Paulo (USP), no Instituto Nacional de Tecnologia Industrial da Argentina (INTI em Buenos Aires), Centro Atômico de Buenos Aires e Bariloche, também na Argentina. Estes laboratórios são equipados para testes de radiação e EMI, o que garante todo o ambiente de validação necessário;

- A validação de uma plataforma de injeção de ruídos conduzidos pelas linhas de alimentação que possibilita efetuar a variação da tensão em tempo real com o sistema em operação;

- 4. Uma proposta de metodologia de testes combinados de radiação

+ EMI referenciados em normas internacionais;

- 5. Um relato dos resultados fazendo uma análise da susceptibilidade à EMI dos FPGAs utilizados neste trabalho que sofreram exposição à radiação por dose total ou por "SEU", tendo como principal objetivo mostrar os seus limites de operação para efetuar a qualificação destes dispositivos.

- 6. Como contribuição científica, os resultados deste trabalho foram publicados até o momento em dois artigos completos em revista ((Benfica et al., 2012c) e (Benfica et al., 2012b)) e em sete conferências internacionais ((Benfica et al., 2015) (Seclen et al., 2014) (Oliveira et al., 2013) (Benfica et al., 2012a) (Benfica et al., 2011a) (Benfica et al., 2011b) (Vargas et al., 2008)).

#### 2 ESTADO DA ARTE

# 2.1 ANÁLISE DOS EFEITOS DA RADIAÇÃO

Problemas importantes relacionados ao uso de FPGAs no ambiente espacial estão relacionados às falhas transientes e permanentes nas células de memória RAM estática do dispositivo, causados pela radiação (Gosheblagh and Mohammadi, 2014a) (Siozios and Soudris, 2013). Entretanto, as vantagens e facilidades do uso dos FPGAs do tipo SRAM justificam os estudos.

Estudos realizados, mostram que o componente energético dos prótons dos raios cósmicos galácticos poderia ser responsável por erros de bits observados nos chips de memória do tipo MOS (Metal Oxide Semiconductor) onde perturbam a informação armazenada em uma célula de memória, mesmo que no nível do mar (Węgrzyn and Sosnowski, 2014) (O'Gorman, 1994).

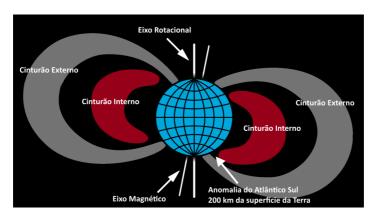

O ambiente natural de radiação da atmosfera terrestre consiste de elétrons, prótons e íons pesados que podem estar presos pelo campo magnético da Terra ou que transitam através dos domínios dos satélites artificiais (Stassinopoulos and Raymond, 1988). E é este ambiente de radiação que causa danos ou ocasiona o mau funcionamento de dispositivos eletrônicos. Este ambiente de radiação pode ser caracterizado pelo Cinturão de Van Allen <sup>1</sup>, explosões solares (que provocam labaredas

O Cinturão de Van Allen é uma região onde ocorrem vários fenômenos atmosféricos devido a concentrações de partículas no campo magnético terrestre, descobertas em 1958 por James Van Allen. As radiações de Van Allen não ocorrem, salvo em raras exceções, nos polos, e sim na região equatorial. Estas formam dois cinturões em forma de anéis, com centro no equador. O mais interno se estende entre as altitudes de mil e cinco mil quilômetros, sua intensidade máxima ocorrendo em média aos três mil quilômetros. Consiste de prótons altamente energéticos, que se originam pelo decaimento de nêutrons produzidos quando raios cósmicos vindos do espaço exterior colidem com átomos e moléculas da atmosfera terrestre. Parte dos nêutrons é ejetada para fora da atmosfera e se desintegra em prótons e elétrons ao atravessar esta região do cinturão. Essas partículas se movem em trajetórias espirais ao longo de linhas de força do campo magnético terrestre. O segundo cinturão, que fica situado entre 15.000 e 25.000 km, contém partículas eletricamente carregadas de origem tanto atmosférica quanto solar. São principalmente íons hélio trazidos pelo vento solar. As partículas mais energéticas deste são elétrons cuja energia atinge várias centenas de milhares de elétrons-volt. Os prótons são muito menos energéticos do que os do

solares), ventos solares e raios cósmicos (Reeves et al., 2013).

Cinturão de Van Allen: Os cinturões de radiação contém elétrons e prótons presos e podem ser observados na Figura 2. Esta radiação presa possui dois cinturões de elétrons. O cinturão mais interno contém elétrons cuja energia é menos que 5 MeV <sup>2</sup>. O cinturão de fora possui elétrons que podem atingir energia de até 7 MeV. Um terceiro cinturão de elétrons foi descoberto após a tempestade magnética de 24 de março de 1991. Este cinturão está na metade do caminho entre o cinturão externo e o interno e pode atingir energias muito superiores a 30 MeV (Boudenot, 2007).

Figura 2 – Cinturões de Radiação de Van Allen.

Fonte: Modificado de

http://aetherforce.com/van-allen-radiation-an-unpenetrable-barrier/

Explosões solares: As explosões solares tem um ciclo de 11 anos e podem ser subdivididos em quatro anos de baixa atividade e sete anos de alta atividade. Existem dois eventos que devem ser considerados nas explosões solares. O primeiro é a ejeção de massa coronal que dura vários dias e que emite a maior quantidade de prótons de alta

primeiro cinturão, porém seu fluxo é mais intenso (Williams et al., 1963).

O elétron-volt é uma unidade de medida de energia. Equivale a  $1,60217657 \times 10^{-19}$  joules onde 1 MeV é igual a  $1 \times 10^6 eV$ . Por definição, um elétron-volt é a quantidade de energia cinética ganha por um único elétron quando acelerado por uma diferença de potencial elétrico de um volt, no vácuo (Mohr et al., 2012).

energia (até centenas de MeV). O segundo tipo é o evento que ocorre ocasionalmente e é chamado de evento impulsivo (*Impulsive Events*) e é responsável pela grande emissão de íons pesados (*heavy ions*) que podem ir a dezenas de MeV até centenas de Gev por nucleon (Boudenot, 2007).

Ventos solares: A altíssima temperatura da corona do sol, em torno de dois milhões de graus Kelvin, produz energia suficiente para permitir que elétrons escapem da atração gravitacional do sol. O efeito da ejeção dos elétrons é um desequilíbrio de carga que resulta em uma ejeção de prótons e íons pesados da corona. O gás ejetado é tão quente que as partículas são homogeneizadas em um plasma diluído. A energia das partículas está em torno de 0,5 a 2keV por nucleon. A composição do vento solar é aproximadamente 95% de prótons, 4% de partículas de Hélio e menos de 1% de íons pesados (Boudenot, 2007).

Efeitos dos Ventos Solares: Diferenças nas características de emissão e de absorção, diferenças na exposição a luz do sol e efeitos localizados resultam em uma população de elétrons desigual que produzem voltagens diferentes entre as superfícies isoladas do satélite. Além disso, elétrons tem energia suficiente para passar através da manta térmica resultando em uma carga das superfícies e da montagens internas. Tipicamente objetos encapsulados incluindo revestimentos de cabos, malhas de dissipação térmica não aterradas, pintura térmica, encapsulamentos dos componentes eletrônicos etc. Elétrons de alta energia penetram nestes encapsulamentos e podem depositar carga na placa do circuito, fios isolados, conectores, capacitores etc. Neste processo, chamado de carga profunda do dielétrico, elétrons de alta energia penetram nos elementos do circuito e dos dispositivos, levando a prisão desta carga que vai se acumulando no material dielétrico (Boudenot, 2007).

Efeitos dos Raios Cósmicos: Os raios cósmicos são núcleos de íons pesados de alta energia. A origem desta radiação ainda não foi muito bem identificada, entretanto sabe-se que parte dela vem de fora da Via Láctea e o resto de dentro dela. A energia dos íons é muito alta (podendo chegar a 1GeV por nucleon) e correspondem aos mecanismos de aceleração que fazem com que a radiação se acople no campo magnético

da Terra, justamente na camada onde ficam os satélites nas três órbitas possíveis.

Dispositivos eletrônicos em aplicações aeroespaciais têm grande probabilidade de sofrer efeitos indesejados ocasionados por raios cósmicos e radiação. Além das aplicações em missões de exploração, a principal aplicação dos circuitos eletrônicos no espaço consiste nos satélites artificiais (comunicação, sensoriamento remoto, posicionamento global, meteorologia, pesquisa e finalidades militares).

Como exemplo de sistema eletrônico embarcado nos satélites, é o módulo de telecomando e telemetria, cujo o uso de FPGAs é comum devido a sua facilidade de implementação em hardware, aumentando assim o desempenho do sistema. O subsistema de telemetria e comando fornece a interface funcional entre o satélite e o comando e controle do solo. Os parâmetros de telemetria descrevem o status das configurações e dos equipamentos à bordo do satélites e são enviados para o centro de controle de operações do satélite em solo, na Terra. Os comandos são recebidos pelo satélite para controlar operações de missão e gestão dos recursos do equipamento. Para executar essas funções, o subsistema de telecomando e telemetria é composto de uma única antena bicone montada no painel do satélite, dois receptores de radiofrequência (RF), quatro transmissores, unidades de telemetria e comando digitais redundantes e de um triplexer que permite a operação simultânea dos transmissores e receptores para a antena sem interferência (Keesee, 2003).

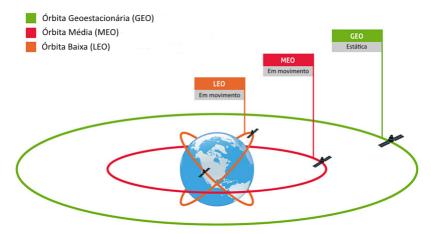

Os satélites podem ser classificados quanto à altitude de sua órbita o que define também os níveis e as fontes de radiação às quais o satélite estará exposto e pode ser observado na Figura 3.

Figura 3 – Órbitas dos satélites.

Fonte: Modificado de http://www.harriscaprock.com/blog/wp-content/uploads/2014/10/Medium-Earth-Orbit-Latency.jpg

- A primeira e mais comum delas é a geoestacionária, também conhecidas como GEO (Geostationary Earth Orbit) e são utilizadas para fins de comunicação. Posicionados a uma altitude entre 35800 km e 36000 km, os satélites gastam 23h 56 min e 04s. para dar uma volta em torno da Terra que, não por coincidência , é o mesmo período de rotação de nosso planeta (Boudenot, 2007).

- A segunda é a baixa órbita, também conhecidos como LEO(Low Earth Orbit), que estão entre 300-5000km, raramente eram usados em comunicações devido ao fato que as antenas não mantinham a visada por muito tempo. Geralmente eram utilizados com propósitos de sensoriamento científico ou militar durante todos estes anos (Davidoff et al., 1984).

- A terceira é a órbita elíptica e excêntrica, também conhecidos como MEO (*Medium Earth Orbit*) colocados entre 5000-36000 km, utilizado no início da exploração deste segmento pela União Soviética, com uma órbita de 12 horas (Davidoff et al., 1984).

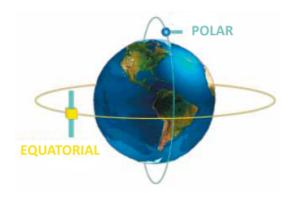

A inclinação de um satélite é o ângulo formado entre a órbita do satélite e a linha do equador terrestre. Satélites com inclinação de 0° seguem a linha do equador e são chamados de satélites de órbita equatorial. Quando sua inclinação é de 90° sua órbita cruza os polos terrestres e são chamados de satélite de órbita polar e é ilustrado na Figura 4. Quando um satélite tem inclinação igual ou menor que a latitude do local de observação, este pode ser visto diretamente se as condições permitirem (Montenbruck and Gill, 2012).

Figura 4 – Órbita polar e órbita equatorial de um satélite.

Fonte: Modificado de

http://fisicamoderna.blog.uol.com.br/images/sat\_orbitas.jpg.

Um satélite colocado em uma órbita geoestacionária sofre várias perturbações orbitais; destas, a influência do Sol e da Lua fazem com que o plano orbital desvie do plano do equador a uma razão aproximada de  $0.8^{\circ}$  por ano.

Para evitar o aumento da inclinação orbital, é preciso utilizar combustível a bordo do satélite para, periodicamente, corrigir sua órbita. Estas correções são feitas quando o satélite passa próximo do nodo ascendente ou o nodo descendente da órbita, e aplicam um  $\Delta V$  na direção norte-sul para inverter a inclinação orbital, de forma que as perturbações orbitais das próximas semanas retornem a inclinação orbital a valores próximos de zero para, em seguida, aumentar, até o

momento da manobra corretiva seguinte. A maior parte do combustível alocado para correções orbitais em um satélite geoestacionário é gasta com estas correções da inclinação orbital. Assim, uma estratégia para prolongar a vida útil de um satélite é, ao final de sua vida, deixar de corrigir a inclinação (Montenbruck and Gill, 2012).

Tanto órbitas MEO como GEO estão mais expostas ao cinturão de Van Allen externo, onde a maior fonte de radiação são elétrons. A radiação do cinturão externo pode ser mitigada com blindagens de alumínio relativamente finas, pois o poder de penetração dos elétrons do cinturão externo é moderado (Williams et al., 1963).

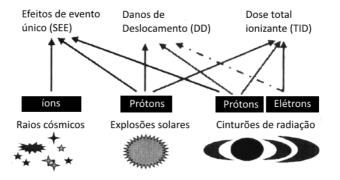

No contexto da radiação espacial, existem basicamente três tipos de efeitos que afetam os circuitos eletrônicos em aplicações espaciais (Boudenot, 2007):

## 1. Dose Total Ionizante (do inglês, Total Ionizing Dose ou TID)

– Dose total ionizante em um componente indica a dose de radiação recebida através de sua blindagem. De acordo com a exata localização do componente considerado no satélite, e suas várias blindagens que o protegem (blindagem externa do satélite, placas de circuito impresso, encapsulamento do componente etc.) a TID é computada (Zhang et al., 2014b) (Schwank et al., 2008) (Boudenot, 2007).

Influência da órbita: Nos satélites LEO, a média de distribuição da radiação não é homogênea. O cinturão mais externo de elétrons fica mais perto da Terra nas regiões polares e na região central do atlântico sul que tem um alto nível de partículas presas (prótons e elétrons). Isso quer dizer que satélites colocados em uma órbita equatorial baixa (300 km) sustenta pouca radiação. Satélites em uma órbita baixa com inclinação menor que 45° e maior que 55° estão sujeitos a Anomalia do Atlântico Sul (do inglês, South Atlantic Anomaly ou SAA) que é a região da Terra mais próxima dos cinturões de radiação de Van Allen e ficam mais expostos à radiação. Satélites colocados em órbitas acima de 1400 km recebem grandes doses de radiação e sofrem os efeitos da dose

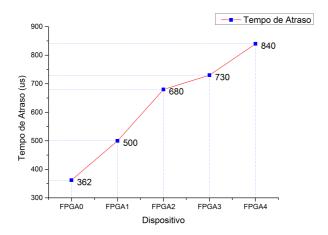

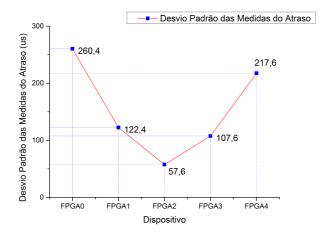

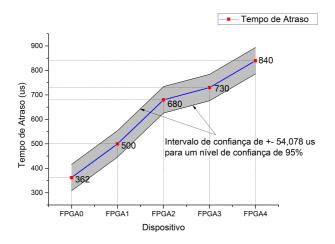

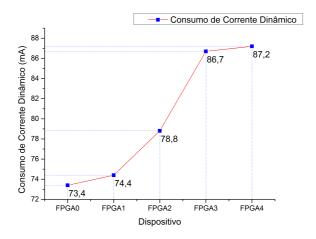

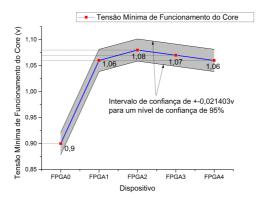

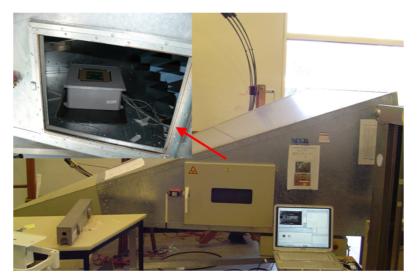

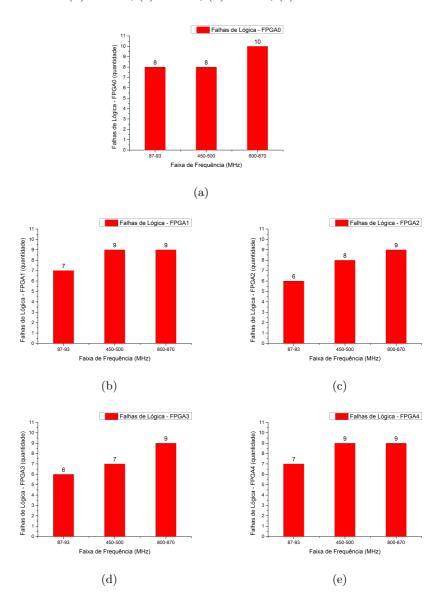

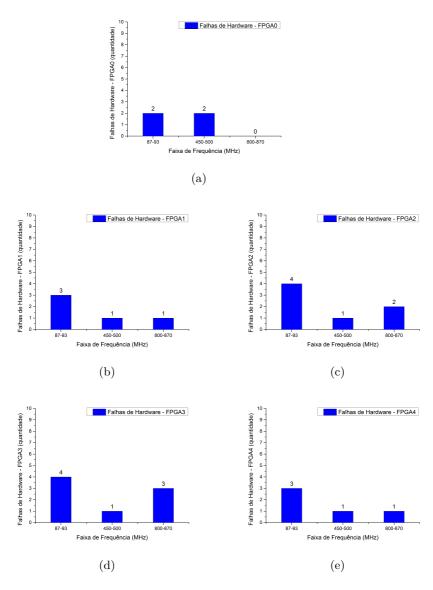

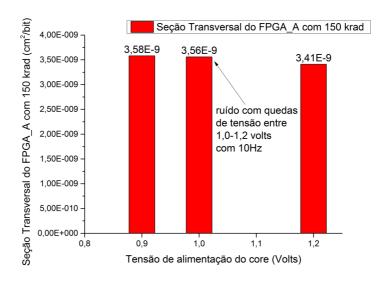

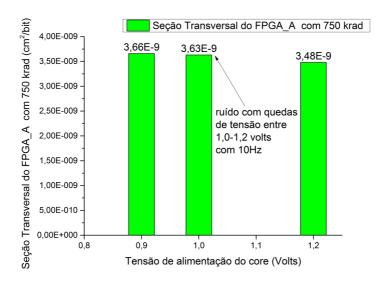

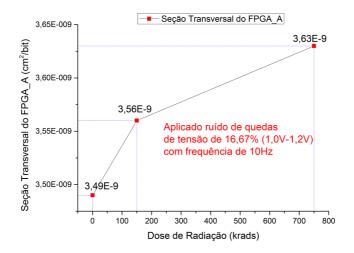

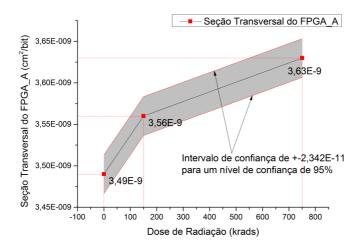

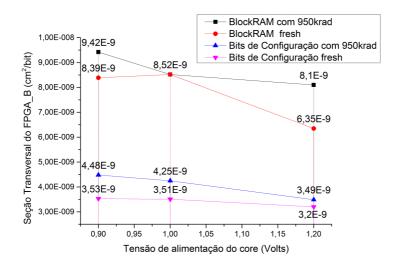

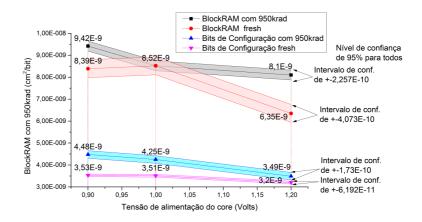

total causados pelo cinturão externo de prótons. Em satélites GEO e MEO a fonte principal da dose de radiação é devido ao cinturão externo de elétrons (como exemplo, um satélite GEO que está em órbita por 18 anos a dose total acumulada será de 100 krad protegido por uma blindagem de 5 mm de alumínio e de 10 krad protegido por 10 mm de blindagem, já em um satélite colocado em uma órbita de 2000 km durante 5 anos com blindagem de 10 mm de alumínio acumulará 300 krad) (Schwank et al., 2008) (Boudenot, 2007).