### UNIVERSIDADE FEDERAL DE SANTA CATARINA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

Pedro André Martins Bezerra

### INVERSOR TRIFÁSICO PWM FONTE DE TENSÃO COM INTEGRAÇÃO DE INTERRUPTORES EM DELTA

Florianópolis

2013

#### Pedro André Martins Bezerra

### INVERSOR TRIFÁSICO PWM FONTE DE TENSÃO COM INTEGRAÇÃO DE INTERRUPTORES EM DELTA

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para obtenção do Grau de Mestre em Engenharia Elétrica.

Orientador: Prof. Marcelo Lobo Heldwein, Dr. sc. ETH

Florianópolis, Julho de 2013

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Bezerra, Pedro André

Inversor Trifásico PWM Fonte de Tensão com Integração de Interruptores em Delta / Pedro André Bezerra ; orientador, Marcelo Lobo Heldwein - Florianópolis, SC, 2013. 253 p.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia Elétrica.

#### Inclui referências

1. Engenharia Elétrica. 2. Inversor de Tensão PWM. 3. Interruptores em Delta. 4. Modo Comum. 5. Alto Rendimento. I. Lobo Heldwein, Marcelo . II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

#### Pedro André Martins Bezerra

# INVERSOR TRIFÁSICO PWM FONTE DE TENSÃO COM INTEGRAÇÃO DE INTERRUPTORES EM **DELTA**

| Esta Dissertação foi julgada adequada para obtenção do Título de Mestre, Área de Concentração em Eletrônica de Potência e Acionamento Elétrico, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Patrick Kuo Peng, Dr.                                                                                                                                                                                                                |

| Coordenador do Programa de Pós-Graduação em Engenharia Elétrica                                                                                                                                                                      |

| Banca Examinadora:                                                                                                                                                                                                                   |

| me uh.                                                                                                                                                                                                                               |

| Marcelo Lobo Heldwein, Dr. sc. ETH<br>Orientador                                                                                                                                                                                     |

| Kor -                                                                                                                                                                                                                                |

| Prof. Romeu Hausmann, Dr.                                                                                                                                                                                                            |

| 100                                                                                                                                                                                                                                  |

| 17 Glaston                                                                                                                                                                                                                           |

| Prof. Telles Brunelli Lazzarin, Dr.                                                                                                                                                                                                  |

| All                                                                                                                                                                                                                                  |

| Prof. Ivo Barbi, Dr. Ing.                                                                                                                                                                                                            |

| Jan Deel                                                                                                                                                                                                                             |

| Prof. Samir Mussa, Dr.                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                      |

"Talvez não tenha conseguido fazer o melhor, mas lutei para que o melhor fosse feito. Não sou o que deveria ser, mas Graças a Deus, não sou o que era antes." Marthin Luther King

#### **AGRADECIMENTOS**

Gostaria de expressar toda minha gratidão a todos que me apoiaram para que eu lograsse êxito em realizar meu mestrado. Vários foram os momentos que precisei de ajuda e incentivo e, nesses momentos, tive a felicidade de contar com algumas pessoas muito importantes.

Primeiramente, gostaria de agradecer ao meu orientador, Prof. Marcelo Heldwein, por todo o conhecimento transmitido e pela orientação exemplar dedicada ao desenvolvimento deste trabalho. Sou muito grato por toda sua confiança, ajuda e compreensão. Sua maneira de trabalhar é contagiante e me serve hoje como inspiração.

Aos membros da banca: Prof. Romeu Hausmann, Prof. Telles Lazzarin, Prof. Ivo Barbi e Prof. Samir Mussa por terem disponibilizado seu tempo para participar da defesa e por terem corrigido o documento escrito. Agradeço também ao Prof. Perin, pois mesmo fazendo parte da banca como suplente, contribuiu de forma bastante significativa na correção da dissertação. Gostaria de agradecer especialmente ao Prof. Ivo Barbi pelas melhores aulas que já tive até hoje. É admirável sua habilidade de transmitir conteúdos complexos de uma maneira bastante natural e agradável. Agradeço por todo o conhecimento transmitido.

Aos demais professores e ex-professores do Instituto de Eletrônica de Potência (INEP): Denizar Martins e Enio Kassick pelo ensino técnico de qualidade e pelos ensinamentos de vida passados durante as aulas.

Aos meus grandes amigos, conterrâneos, companheiros de graduação e pós-graduação, e de moradia em Florianópolis: Décio Haramura, Luis Fernando, Luis Paulo, Carlos Alberto, Gean Jacques, Levy Costa e Lincoln Moura. Agradeço pelos dias de convivência, amizade e ajuda nos momentos difíceis. A minha estadia em Florianópolis foi muito agradável por causa de vocês. Em especial ao Levy Costa, Gean Jacques e Carlos Alberto que me acompanharam até que eu concluísse o mestrado.

Aos meu amigos da turma de mestrado Luís Fernando Machado, Luís Fernando Fontenelle, Rodrigo Santos, Odair Custódio, Marcelo Maccarini, Alan Callegaro, Levy Costa e Gean Jacques. Além de ser uma turma com imenso potencial técnico, também é um grupo que sempre procurou trabalhar em equipe para obter os melhores resultados. Agradeço a todos pela amizade, debates e pelos conhecimentos compartilhados nesses anos de convivência.

Aos demais membros do INEP que tive o o prazer de conviver durante o período do mestrado: Daniel Flores, Gierri Waltrich, Adriano Ruseler, Eduardo de Souza, Walbermark dos Santos, Bruno Dupczak, Hugo Larico, Antônio Bottion, Joselito Heerdt, Nilton da Silva, Franciéli Lima, Moisés Villanueva, Ivar Ordoñez, Delvanei Bandeira, Marcos Jacoboski, Rafael Faust, Rodrigo Piontkewicz, Rômulo Schweitzer, Jefferson Zanotti, André Andreta, Lenon Schmitz, Juarez Camurça e Rafael Eckstein. Sou muito grato pela convivência, momentos de descontração e de troca de experiencias. Gostaria de agradecer especialmente ao Thiago Soeiro, Daniel Collier, Marcio Ortmann, André Fuerback, Jackson Lago, Joabel Moia, Roberto Coelho e Tiago Jappe pela ajuda técnica nos projetos que tivemos a oportunidade de trabalhar em parceria.

Aos técnicos do INEP: Antônio Pacheco, Luiz Coelho e Carina Melatto pelo suporte técnico na parte de hardware e de informática. Aos demais funcionários do INEP: Diogo Duarte, Leandro e Elisabete pelo excelente trabalho em manter o laboratório sempre organizado.

Aos estudantes de iniciação científica: Pedro Pereira, Jaqueline Clamer, Vitor e Wagner Hoffmann pela ajuda na construção dos protótipos.

Não poderia deixar de agradecer também aos amigos que fiz em Fortaleza: Julio César, Evilásio Lucena, Ronny Glauber, Eduardo Façanha, Dalton Honório e Wellington Avelino. Sempre que retorno à minha cidade natal tenho a felicidade de poder reencontrá-los e relembrar os velhos tempos.

À minha família que me recebeu de braços abertos sempre que tive a oportunidade de retornar para casa. Gostaria de fazer um agradecimento especial à minha querida avó Margarida Martins que, infelizmente, não conseguiu ver seu neto superando mais esta etapa da vida. Devo muito do que sou hoje graças aos seus cuidados e ensinamentos.

Faço um agradecimento especial à minha namorada Nayara Coriolano que, mesmo tão distante, soube transmitir-me todo seu amor e carinho. Peço perdão pelos dias que estivemos longe um do outro, pois sei que não é uma situação confortável. Agradeço por toda sua paciência e por acreditar em nosso relacionamento.

Por fim, aos meus pais Pedro Alberto e Ângela Martins que, além de terem me dado a vida e cuidado de mim durante minha infância e juventude, ainda hoje, são meus pilares de sustentação. Agradeço

também à minha querida irmã a quem tenho tanto carinho.

Peço desculpas caso tenha esquecido de alguém, pois realmente devo a muitos esta minha conquista.

Obrigado a todos e a deus pela vida!

#### RESUMO

Este trabalho apresenta o estudo de uma nova topologia de um conversor trifásico dois níveis bidirecional com integração de interruptores conectados em delta adequado para aplicações em acionamentos de máquinas elétricas e para a conexão de sistemas à rede elétrica. A inserção da malha de interruptores em delta a um inversor de tensão convencional adiciona estados redundantes na operação do conversor que, se escolhidos de maneira adequada em uma estratégia de modulação, podem otimizar o desempenho do conversor, de acordo com critérios do projetista. Dependendo da estratégia de modulação utilizada. o conversor pode ser otimizado para a redução das perdas por condução ou para a redução da geração das tensões de modo comum. Uma metodologia para a geração de técnicas de modulação PWM contínuas. descontínuas e híbridas aplicáveis ao conversor proposto e a outros convencionais é apresentada e o desempenho de algumas estratégias é analisado. Estratégias também foram propostas para concentrar as perdas de comutação em componentes específicos, diminuindo a taxa de decrescimento da eficiência do conversor com o aumento da frequência de comutação. Um protótipo de 10 kW foi construído para validar a análise teórica e para realizar a interface de sistemas geradores com a rede elétrica. São fornecidos detalhes da implementação prática bem como a metodologia adotada para o projeto do filtro de EMI e dos controladores. Resultados experimentais são mostrados validando algumas das análises apresentadas.

Palavras-chave: Inversor de Tensão, Trifásico, VSI, Interruptores em Delta , Modulação, PWM, Vetorial, Modo Comum, Alto Rendimento.

#### ABSTRACT

This work analyzes a novel three-phase two-level delta-switch active voltage source inverter for electrical drives and grid connected applications. The addition of delta connected switches to the phases of a voltage source inverter make possible new redundant operational states. The converter states, when combined in a modulation strategy, can optimize the converter performance as defined by the designer. Depending on modulation, the converter can be optimized for losses reduction or for common mode voltage reduction. A methodology for continuous, discontinuous and hybrid PWM modulation strategies generation is presented, suitable for the proposed converter and other conventional ones, and the performance of some of them is analyzed. Strategies are also proposed in order concentrate the switching losses in some components, reducing the efficiency decreasing rate when the switching frequency is increased. A 10 kW prototype was designed and implemented in order to validate the performed analyses and to connect generation systems to the grid. Some practical details and the methodology for EMI filters and controllers design are given. Experimental results are presented validating some of the performed analysis.

**Keywords:** Voltage Source Inverter, Three-Phase, Delta-Switch, Modulation, PWM, Vetorial, Common Mode, High Efficiency.

# LISTA DE SÍMBOLOS

| Símb.            | Descrição                                                     | Unid.                      |

|------------------|---------------------------------------------------------------|----------------------------|

| $\overline{A_L}$ | Fator de indutância                                           | nH/<br>espira <sup>2</sup> |

|                  | Produto entre as áreas da                                     |                            |

| $A_eA_\omega$    | seção transversal do núcleo com                               | $\mathrm{mm}^{4}$          |

|                  | a área da janela                                              |                            |

| $B_{sat}$        | Densidade de fluxo de saturação                               | Т                          |

| $D_{sat}$        | do núcleo                                                     | 1                          |

| $C_{ic}(s)$      | Controlador de Corrente                                       | -                          |

|                  | Capacitância máxima do                                        | F                          |

| $C_{f,\max}$     | filtro LCL                                                    | r                          |

| $C_f$            | Capacitância de Filtro                                        | F                          |

| $C_d$            | Capacitância de Amortecimento                                 | F                          |

| δ                | Ângulo de fator de potência                                   | rad                        |

|                  | Funções de razão cíclica dos interruptores                    |                            |

| $d_{Sij}$        | em estrela do $\Delta$ -VSI, onde $i \in \{a, b, c\}$         | _                          |

|                  | e $j \in \{p, n\}$                                            |                            |

|                  | Funções de razão cíclica dos interruptores                    |                            |

| $d_{Sijk}$       | em delta do $\Delta$ -VSI, onde $i \in \{a, b, c\}$           | -                          |

|                  | $e \ j \in \{a, b, c\} \ com \ i \neq j \ e \ k \in \{1, 2\}$ |                            |

|                  | Funções de razão cíclica dos                                  |                            |

| $d_i$            | tempos de aplicação dos vetores,                              |                            |

| $a_i$            | referenciados ao primeiro sextante                            | _                          |

|                  | onde $i \in \{1, 2, \text{null}\}$                            |                            |

|                  | Funções de razão cíclica dos tempos em                        |                            |

| $d_{j}$          | que o vetor nulo é aplicado durante                           | -                          |

|                  | um período de comutação, onde $j=0,7$                         |                            |

| $d_{iso}$        | Diâmetro do condutor com isolação                             | m                          |

| Símb.                       | Descrição                                                                                                         | Unid. |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------|-------|

| $d_a^*, d_b^*, d_c^*$       | Funções de razão cíclica de referência em coordenadas $abc$                                                       | -     |

| $d_{\alpha}^*, d_{\beta}^*$ | Funções de razão cíclica de referência em coordenadas $\alpha\beta$                                               | -     |

| $ec{d_s}$                   | Vetor contendo as funções de razão cíclica dos interruptores superiores em estrela do $\Delta$ -VSI               | -     |

| $ec{d}_d$                   | Vetor contendo as funções de razão cíclica dos interruptores em delta do $\Delta$ -VSI                            | -     |

| $ec{d_t}$                   | Vetor contendo as funções de razão cíclica dos tempos de aplicação dos vetores do $\Delta$ -VSI                   | -     |

| $ec{d}_s^*$                 | Vetor contendo as funções de razão cíclica de referência dos interruptores superiores em estrela do $\Delta$ -VSI | -     |

| $d_z$                       | função de razão cíclica de eixo zero do $\Delta	ext{-VSI}$                                                        | -     |

| $\vec{d}^*_{abc}$           | Vetor contendo as funções de razão cíclica de referência do $\Delta\text{-VSI}$                                   | -     |

| $d_b$                       | Diâmetro de cobre do condutor                                                                                     | m     |

| $\Delta i_{max}$            | Ondulação máxima de corrente<br>em torno do valor médio                                                           | A     |

| $\Delta T_{Lc}$             | Elevação de temperatura indutor<br>do lado do conversor                                                           | °C    |

| $\delta_{\omega}$           | Profundidade de penetração da<br>corrente no cobre na temperatura<br>máxima de operação                           | m     |

| $e_{lpha},e_{eta}$          | erro de corrente em coordenadas $\alpha\beta$                                                                     | A     |

| $\eta_{\omega}$             | Fator de porosidade                                                                                               | -     |

| $\eta$                      | Rendimento                                                                                                        | -     |

| Símb.                   | Descrição                                         | Unid. |  |

|-------------------------|---------------------------------------------------|-------|--|

| $F_r$                   | Fator de resistência                              | -     |  |

| $f_{int}$               | Frequência de interesse                           | Hz    |  |

| $f_f$                   | Frequência fundamental                            | Hz    |  |

| $f_s$                   | Frequência de Comutação                           | Hz    |  |

| r                       | Frequência de ressonância do                      | TT    |  |

| $f_{ m ress,LCL}$       | filtro LCL                                        | Hz    |  |

|                         | Sinais de Gatilho dos Interruptores               |       |  |

| $G_{Sij}$               | do $\Delta$ -VSI, onde $i \in \{a, b, c\}$        | V     |  |

|                         | $e j \in \{a, b, c, p, n\} \text{ com } i \neq j$ |       |  |

| C (a)                   | Função de transferência da planta                 |       |  |

| $G_{ic}(s)$             | das correntes no lado do conversor                | -     |  |

| $H_{pk}$                | Intensidade de campo de pico                      | A/m   |  |

| II (a)                  | Função de transferência do                        |       |  |

| $H_{ic}(s)$             | condicionamento de sinal de corrente              | -     |  |

| $H_{int}$               | Intensidade de campo de interesse                 | A/m   |  |

| →<br>:*                 | Vetor contendo as as correntes                    | A     |  |

| $\vec{i}^*_{abc}$       | de referência do $\Delta$ -VSI                    | A     |  |

| $i_a, i_b, i_c$         | Correntes de fase em coordenadas $abc$            | A     |  |

| $\hat{I}_{pk}$          | Corrente de pico das correntes de                 | A     |  |

| $^{1}pk$                | referência do lado CA                             | l A   |  |

| <i>i</i> ~ .            | Valor médio da corrente no interruptor            | A     |  |

| $i_{Sap,med}$           | $S_{ap}$                                          | 11    |  |

| $i_{Sap,rms}$           | Valor eficaz da corrente no interruptor           | A     |  |

| *Sap,rms                | $S_{ap}$                                          | 11    |  |

| $i_{Sbc,med}$           | Valor médio da corrente no interruptor            | A     |  |

| *Soc,mea                | $S_{bc}$                                          | 11    |  |

| $i_{Sbc,rms}$           | Valor eficaz da corrente no interruptor           | A     |  |

| $v_{\mathcal{S}0C,Tms}$ | $S_{bc}$                                          | 11    |  |

| $I_{n,\text{ef}}$       | Valor eficaz da corrente harmônica n              | A     |  |

| ID                      | Diâmetro interno do núcleo                        | m     |  |

| Símb.                 | Descrição                                             | Unid. |  |

|-----------------------|-------------------------------------------------------|-------|--|

| $K_{u,\max}$          | Fator de utilização máximo                            | -     |  |

| L                     | Indutância do indutor boost                           | Н     |  |

| $L_c$                 | Indutância do lado do conversor                       | Н     |  |

| $L_r$                 | Indutância do lado da rede                            | Н     |  |

| т                     | Somatório da indutância do conversor                  | тт    |  |

| $L_{tot}$             | com a indutância da do lado da rede                   | H     |  |

| т                     | Indutância mínima do indutor do                       | тт    |  |

| $L_{c,\min}$          | lado do conversor                                     | H     |  |

| $l_c$                 | Comprimento do caminho magnético                      | m     |  |

| $L_{ob}$              | Indutância de projeto                                 | Н     |  |

| $l_{\omega}$          | Comprimento total do condutor                         | m     |  |

| M                     | Índice de modulação                                   | -     |  |

| $\mu_0$               | Permeabilidade absoluta do vácuo                      | H/m   |  |

| $\mu_i$               | Permeabilidade inicial do material                    | -     |  |

|                       | Permeabilidade normalizada em                         |       |  |

| $\mu_{pu}$            | relação a permeabilidade inicial                      | -     |  |

| **                    | Funções de razão modulação de                         |       |  |

| $m_a^*, m_b^*, m_c^*$ | referência em coordenadas $abc$                       | -     |  |

| 1.4                   | Máximo índice de modulação para não                   |       |  |

| $M_{ m max}$          | haver sobremodulação                                  | -     |  |

| $m_z$                 | Sinal de Modulação de Eixo Zero                       | -     |  |

|                       | Funções de modulação dos interruptores                |       |  |

| $m_{Sij}$             | em estrela do $\Delta$ -VSI, onde $i \in \{a, b, c\}$ | -     |  |

|                       | $e j \in \{p, n\}$                                    |       |  |

|                       | Funções de razão cíclica dos                          |       |  |

| m                     | interruptores em delta do $\Delta$ -VSI, onde         |       |  |

| $m_{Sijk}$            | $i \in \{a, b, c\} \in j \in \{a, b, c\}$             | _     |  |

|                       | $com i \neq j e k \in \{1, 2\}$                       |       |  |

| N -                   | Número máximo de espiras para                         |       |  |

| $N_{ m max,B}$        | não haver saturação do núcleo                         |       |  |

| Símb.                  | Descrição                               | Unid. |

|------------------------|-----------------------------------------|-------|

| N                      | Número de Espiras                       | -     |

| NΤ                     | Número máximo de espiras para           |       |

| $N_{	ext{max},\omega}$ | fisicamente possível de implementar     | _     |

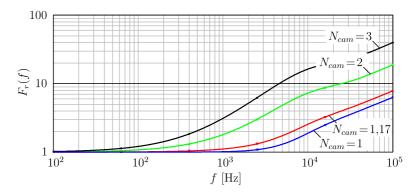

| $N_{cam}$              | Número de camadas de condutores         | -     |

|                        | Espiras que podem ser acomodadas        |       |

| $N_{ m max,cam}^n$     | por camada, onde n é o número           | -     |

|                        | da camada                               |       |

| $N_p$                  | Quantidade de núcleos em paralelo       | -     |

|                        | Quantidade de camadas inteiras          |       |

| nec                    | necessárias para acomodar               | -     |

|                        | todas as espiras do indutor             |       |

|                        | vetores que são aplicados após o        |       |

| $Ond_{\max}$           | primeiro vetor nulo da janela           | A     |

|                        | de comutação                            |       |

| $P_o$                  | Potência de Saída                       | W     |

| $P_{in}$               | Potência de Entrada                     | W     |

| $P_{\rm Mosfet,cond}$  | Perdas por Condução em um Mosfet        | W     |

| $P_{ m Mosfet,cond}$   | Perdas por Condução em um Mosfet        | W     |

| $P_{ m Mosfet,tot}$    | Perdas por condução totais              | W     |

| $P_{\mathrm{Com}}$     | Perdas por comutação                    | W     |

| $P_{\mathrm{Com,tot}}$ | Perdas por comutação totais             | W     |

| $P_{ m tot}$           | Perdas totais                           | W     |

| $P_{\omega}$           | Potência total dissipada nos condutores | W     |

| $\Gamma_{\omega}$      | do indutor                              | l vv  |

| $P_c$                  | Potência total dissipada no núcleo      | W     |

| 1 C                    | do indutor                              | **    |

|                        | Potência dissipada no cobre             |       |

| $P_{\omega,_{lf}}$     | pela componente fundamental             | W     |

|                        | de corrente                             |       |

| ímb.                            | Descrição                                                       | Unid.    |  |

|---------------------------------|-----------------------------------------------------------------|----------|--|

|                                 | Potência dissipada no cobre                                     |          |  |

| $\omega_{,hf}$                  | pelas componentes harmônicas                                    | W        |  |

|                                 | de corrente                                                     |          |  |

| $P_{Lc}$                        | Potência total dissipada no indutor                             |          |  |

| Lc                              | do lado do conversor                                            | W        |  |

| e <sub>1</sub> e p <sub>2</sub> | Derivadas de corrente                                           | A/s      |  |

|                                 | Relação entre as indutâncias do                                 |          |  |

|                                 | filtro LCL                                                      | _        |  |

|                                 | Resistividade do cobre na                                       | 0        |  |

| T                               | temperatura máxima de operação                                  | 7 5 1111 |  |

| $R_d$                           | Resistência de amortecimento                                    | Ω        |  |

|                                 | Resistência série do capacitor                                  | 0        |  |

| $R_f$                           | de filtro                                                       | 2.2      |  |

|                                 | Resistência de condução do interruptor                          |          |  |

| $R_{Sij}$                       | controlado $S_{ij}$ , onde $i \in \{a, b, c\}$ e                | Ω        |  |

|                                 | $j \in \{a, b, c, p, n\} \text{ com } i \neq j$                 |          |  |

|                                 | Resistência de condução do                                      |          |  |

| )                               | interruptor $D_{ij}$ não controlado,                            |          |  |

| $R_{Dij}$                       | onde $i \in \{a, b, c\}$ e $j \in \{a, b, c, p, n\}$            | 7.2      |  |

|                                 | $com i \neq j$                                                  |          |  |

|                                 | Resistência do cobre para corrente                              | 0        |  |

| $R_{cc}$                        | contínua                                                        | 7.2      |  |

| $c_{ca}$                        | Resistência do cobre para corrente                              | 0        |  |

| $\iota_{ca}$                    | alternada                                                       | 2.2      |  |

| γ                               | Interruptores do $\Delta$ -VSI, onde                            |          |  |

| $S_{ij}$                        | $i \in \{a, b, c\} \in \{a, b, c, p, n\} \text{ com } i \neq j$ | -        |  |

|                                 | Função de comutação do interruptor                              |          |  |

| ij                              | $S_{ij}$ , onde $i \in \{a, b, c\}$ e                           | -        |  |

|                                 | $j \in \{a, b, c, p, n\} \text{ com } i \neq j$                 |          |  |

| 'i                              | Sextantes do mapa de vetores do $\Delta$ -VSI,                  |          |  |

| i                               | onde $i \in \{0, 16\}$                                          | _        |  |

| Símb.                               | Descrição                                          | Unid.     |

|-------------------------------------|----------------------------------------------------|-----------|

| $T_{amb}$                           | Temperatura ambiente                               | °C        |

|                                     | Tempo de aplicação dos vetores,                    |           |

| $T_i$                               | referenciados ao primeiro sextante                 | s         |

|                                     | onde $i \in \{1, 2, \text{null}\}$                 |           |

| $T_s$                               | Período de comutação                               | s         |

|                                     | Intervalos de tempo em que o vetor                 |           |

| $T_j$                               | nulo é aplicado em um período de                   | s         |

|                                     | comutação, onde $j = 0, 7$                         |           |

| $T_{oper}$                          | Temperatura de operação                            | °C        |

| $T_j$                               | Temperatura na Junção                              | °C        |

| $t_j$                               | Tempo de aplicação do vetor $\vec{V}_j$            | V         |

| $\theta$                            | Ângulo das tensões de fase                         | rad       |

| $\overline{	heta^{'}}$              | Ângulo das tensões de fase referido                |           |

| O                                   | ao primeiro sextante                               | rad       |

| T/                                  | Tensão média sobre capacitores do                  | rad rad V |

| $V_{dc}$                            | barramento CC                                      | V         |

| $v_a, v_b, v_c$                     | Tensões de fase em coordenadas $abc$               | V         |

| $v_{\alpha}, v_{\beta}, v_{\gamma}$ | Tensões de fase em coordenadas $\alpha\beta\gamma$ | V         |

| $ec{V}_i$                           | Vetores espaciais de tensão do $\Delta$ -VSI,      | V         |

| $V_i$                               | onde $i \in \{0, 16\}$                             | V         |

|                                     | Vetores espaciais ativos de tensão do              |           |

| $ec{V}_{i,	ext{VSI}}$               | $\Delta$ -VSI utilizando apenas os                 | $ _{V}$   |

| $v_{i, \text{VSI}}$                 | interruptores em estrela,                          | V         |

|                                     | onde $i \in \{0, 16\}$                             |           |

|                                     | Vetores espaciais ativos de tensão do              |           |

| <i>V</i>                            | $\Delta$ -VSI utilizando dois interruptores em     | V         |

| $ec{V}_{i,	ext{SDj}}$               | estrela e um interruptor em delta,                 | V         |

|                                     | onde $i \in \{0, 16\}$ e $j \in \{1, 2\}$          |           |

| Símb.                  | Descrição                                                      | Unid. |

|------------------------|----------------------------------------------------------------|-------|

| $ec{V}_{i,	ext{RCL}}$  | Vetores espaciais ativos de tensão do                          |       |

|                        | $\Delta$ -VSI, utilizando três interruptores                   | V     |

| $v_{i, \text{RCL}}$    | em estrela e um interruptor em                                 | v     |

|                        | delta, onde $i \in \{0, 16\}$                                  |       |

|                        | Vetor nulo de tensão do $\Delta$ -VSI                          |       |

| $ec{V}_{0,	ext{VSIj}}$ | utilizando apenas os interruptores                             | V     |

|                        | em estrela, onde $j \in \{1, 2\}$                              |       |

|                        | Vetor nulo de tensão do $\Delta$ -VSI                          |       |

| $ec{V}_{0,	ext{RCLi}}$ | utilizando os interruptores                                    | V     |

| V0,RCLj                | em estrela e em delta simultaneamente,                         | V     |

|                        | onde $j \in \{1, 2\}$                                          |       |

|                        | Vetor nulo de tensão do $\Delta$ -VSI                          |       |

| $ec{V}_{0,	ext{RCMV}}$ | utilizando apenas os interruptores                             | V     |

|                        | em delta, onde $j \in \{1, 2\}$                                |       |

|                        | Tensão de polarização do interruptor                           |       |

| $V_{Sij}$              | controlado $S_{ij}$ , onde $i \in \{a, b, c\}$                 | V     |

|                        | $e j \in \{a, b, c, p, n\} \text{ com } i \neq j$              |       |

| $V_{Dij}$              | Tensão de polarização do interruptor                           |       |

|                        | $V_{Dij}$ não controlado, onde                                 | V     |

|                        | $i \in \{a, b, c\}$ e $j \in \{a, b, c, p, n\}$ com $i \neq j$ |       |

| <del>/</del> *         | Vetor de referência em coordenadas $\alpha\beta$               | V     |

| $\hat{V}_{pk}$         | Valor de pico das tensões de fase                              | V     |

| Vpk                    | de referência                                                  | V     |

| $V_{dc}$               | Tensão Média do Barramento CC                                  | V     |

|                        | Tensão máxima de pico de fase                                  |       |

| $\vec{V}_{max}^*$      | para que não haja sobremodulação na                            | V     |

|                        | modulação senoidal                                             |       |

|                        | Portadora triangular dos moduladores                           | V     |

| $v_{tri}$              | do $\Delta$ -VSI                                               | v     |

| /                      | Valor Médio Quase Instantâneo                                  |       |

| $\langle var \rangle$  | das Variáveis do $\Delta$ -VSI                                 | _     |

| Símb.                 | Descrição                              | Unid. |

|-----------------------|----------------------------------------|-------|

| ***                   | Funções de razão cíclica de referência | V     |

| $v_a^*, v_b^*, v_c^*$ | em coordenadas $abc$                   | V     |

|                       | Valor de pico da componente            |       |

| $\hat{V}_{f1}$        | fundamental das tensões de             | V     |

|                       | referência                             |       |

| $v_{cm}$              | Tensão de modo comum                   | V     |

| $V_{o,\mathrm{rms}}$  | Tensão eficaz de linha no lado CA      | V     |

| $ec{V}_y$             | vetores que são aplicados após o       |       |

|                       | primeiro vetor nulo da janela          | V     |

|                       | de comutação                           |       |

### LISTA DE ABREVIATURAS E SIGLAS

| ANPC           | Grampeamento Ativo no Ponto Central         |  |  |

|----------------|---------------------------------------------|--|--|

|                | (Active Neutral Point Clamped)              |  |  |

| AD             | Analógico Digital                           |  |  |

| ADC            | Conversor Analógico Digital                 |  |  |

| BT             | Baixa Tensão                                |  |  |

| CA             | Corrente Alternada                          |  |  |

| CC             | Corrente Contínua                           |  |  |

| CBPWM          | PWM Baseada em Portadoras                   |  |  |

| CBPWM          | (Carrier Based PWM)                         |  |  |

| CPWM           | PWM contínua                                |  |  |

| CP W M         | (Continuous PWM)                            |  |  |

| CSVM           | SVM Contínua                                |  |  |

| CSVM           | (Continuous SVM)                            |  |  |

|                | Inversor Trifásico de Tensão                |  |  |

| Δ-VSI          | Dois Níveis com Interruptores em Delta      |  |  |

| Δ- V 51        | (Two-Level Three-Phase Delta-Switch Voltage |  |  |

|                | Source Inverter)                            |  |  |

|                | Retificador Trifásico de Tensão             |  |  |

| Λ-VSR          | Dois Níveis com Interruptores em Delta      |  |  |

| Δ- ν διτ       | (Two-Level Three-Phase Delta-Switch         |  |  |

|                | Voltage Source Rectifier)                   |  |  |

|                | Ponto Neutro Grampeado com                  |  |  |

| $\Delta$ -NPC  | Interruptores em Delta                      |  |  |

|                | (Delta-Switch Neutral Point Clamped)        |  |  |

| Δ-Tipo T       | Tipo T com Interruptores em Delta           |  |  |

| Δ-11p0 1       | (Delta-Switch T-Type)                       |  |  |

|                | Capacitor flutuante com                     |  |  |

| $\Delta$ -FCap | Interruptores em Delta                      |  |  |

|                | (Delta-Switch FCap)                         |  |  |

| •              |                                             |  |  |

| DPWM    | PWM Descontínua                          |  |

|---------|------------------------------------------|--|

| DPWM1   | PWM Descontínua 1                        |  |

|         | com ângulo $\varphi = 0^{\circ}$         |  |

| DPWM0   | PWM Descontínua 0                        |  |

| DI WWO  | com ângulo $\varphi = -60$               |  |

| DPWM2   | PWM Descontínua 2                        |  |

| DI WWZ  | com ângulo $\varphi = 60$                |  |

| DPWM3   | PWM Descontínua 3                        |  |

| DPWMMAX | PWM Descontínua Máxima                   |  |

| DPWMMIN | PWM Descontínua Mínima                   |  |

|         | PWM Descontínua que utiliza os           |  |

| DPWM13  | padrões de pulsos da DPWM1 e da DPWM3    |  |

|         | (DPWM1 nos picos de $\vec{m}_{abc}^*$ )  |  |

|         | PWM Descontínua que utiliza os           |  |

| DPWM31  | padrões de pulsos da DPWM3 e da DPWM1    |  |

|         | (DPWM3 nos picos de $\vec{m}_{abc}^*$ )  |  |

| DSC     | Controlador Digital de Sinais            |  |

| DSC     | (Digital Signal Controller)              |  |

| DSVM    | SVM Descontínua                          |  |

| DOVM    | (Discontinuous SVM)                      |  |

| EMI     | Interferência Eletromagnética            |  |

| 151011  | $(Eletromagnetic\ Interference)$         |  |

| FPGA    | Arranjo de Portas Programável em Campo   |  |

| TT GH   | (Field Programmable Gate Array)          |  |

| GD      | Geração Distribuída                      |  |

| GDPWM   | PWM Descontínua Generalizada             |  |

|         | Modulação PWM Descontínua que utiliza os |  |

| GDSVPWM | padrões de pulsos da GDPWM e da SVPWM    |  |

|         | (GDPWM nos picos de $\vec{m}_{abc}^*$ )  |  |

|        | Conceito de Inversor Altamente          |  |

|--------|-----------------------------------------|--|

| HERIC  | Eficiente e Confiável                   |  |

|        | (Highly Efficient and Reliable          |  |

|        | Inverter Concept)                       |  |

|        | Instituto de Engenheiros Eletricistas   |  |

| IEEE   | e Eletrônicos                           |  |

| IEEE   | Institute of Electrical and Electronics |  |

|        | Engineers                               |  |

| IGBT   | Transistor Bipolar com Gatilho Isolado  |  |

| IGDI   | (Isolated Gate Bipolar Transistor)      |  |

|        | Equação de Steimetz Generalizada        |  |

| iGSE   | e Melhorada                             |  |

| IGSE   | (Improved Generalized Steimetz          |  |

|        | Equation)                               |  |

| MCD    | Modo de Condução Descontínuo            |  |

|        | Transistor de Efeito de                 |  |

| MOSFET | Campo Metal Oxido Semicondutor          |  |

| MOSFEI | (Metal Oxide Semiconductor              |  |

|        | Field Effect Transistor)                |  |

| NPC    | Grampeamento no Ponto Central           |  |

| NEC    | (Neutral Point Clamped)                 |  |

| ONS    | Operador Nacional do Sistema            |  |

| PWM    | Modulação por Largura da Pulso          |  |

| PWM    | (Pulse Width Modulation)                |  |

| PI     | Proporcional Integral                   |  |

| PR     | Proporcional Ressonante                 |  |

| DCI    | Perdas por Condução Reduzidas           |  |

| RCL    | (Reduced Conduction Losses)             |  |

| DCMV   | Reduzido Valor da Tensão de Modo Comum  |  |

| RCMV   | (Reduced Common Mode Voltage)           |  |

|        | 1 '                                     |  |

| RL       | Perdas Reduzidas                             |  |

|----------|----------------------------------------------|--|

|          | (Reduced Losses)                             |  |

| RB-IGBT  | IGBT com Capacidade de Bloqueio Reverso      |  |

| IID-IGD1 | (Reversing Block IGBT)                       |  |

| SEP      | Sistema Elétrico de Potência                 |  |

| SPWM     | Modulação PWM Senoidal                       |  |

| SVM      | Modulação Vetorial (Space Vector Modulation) |  |

|          | Modulação PWM Descontínua que utiliza os     |  |

| SVGDPWM  | padrões de pulsos da SVPWM e da GDPWM        |  |

|          | (SVPWM nos picos de $\vec{m}_{abc}^*$ )      |  |

| SVPWM    | Modulação Vetorial PWM                       |  |

| TDH      | Taxa de Distorção Harmônica                  |  |

| 2L-VSI   | Inversor Trifásico de Tensão Dois Níveis     |  |

| VMQI     | Valor Médio Quase Instantâneo                |  |

| ZVS      | Comutação sob Tensão Nula                    |  |

| ZVD      | (Zero Voltage Switching)                     |  |

|          | <u> </u>                                     |  |

# **SUMÁRIO**

| 1 | INT | RODU   | ÇÃO                                             | 1  |

|---|-----|--------|-------------------------------------------------|----|

|   | 1.1 | Conte  | xtualização do Trabalho                         | 1  |

|   | 1.2 | Princi | pais Contribuições do Trabalho                  | 4  |

|   |     | 1.2.1  |                                                 | 4  |

|   | 1.3 | Estrut | tura da Dissertação                             | 5  |

| 2 | INV | ERSOI  | RES TRIFÁSICOS DE ALTO DESEMPENHO               |    |

|   | PAF | RA API | LICAÇÕES EM BT                                  | 7  |

|   | 2.1 | Introd | lução                                           | 7  |

|   | 2.2 | Invers | or Trifásico de Tensão Dois Níveis Convencional |    |

|   |     |        | SI)                                             | 7  |

|   | 2.3 |        | ores Dois Níveis com Comutação Suave            | 9  |

|   | 2.4 |        | ores Dois Níveis Operando em Máquinas com Bo-   |    |

|   |     |        | Acessíveis (Dual VSI)                           | 10 |

|   | 2.5 |        | ores Três Níveis                                | 11 |

|   | 2.6 |        | ogia Proposta                                   | 13 |

|   |     | 2.6.1  |                                                 | 14 |

|   | 2.7 | Interr | uptores Conectados em Delta para Topologias     |    |

|   |     | Multin | níveis                                          | 15 |

|   | 2.8 | Concl  | usão                                            | 16 |

| 3 | OPI | ERAÇÃ  | O E PRINCÍPIOS DE MODULAÇÃO VETORIAL            |    |

|   |     |        |                                                 | 19 |

|   | 3.1 | Introd | lução                                           | 19 |

|   | 3.2 | Restri | ções de Operação do $\Delta$ -VSI               | 19 |

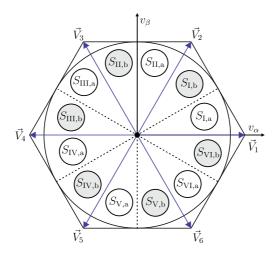

|   | 3.3 | Anális | se Vetorial do $\Delta$ -VSI                    | 21 |

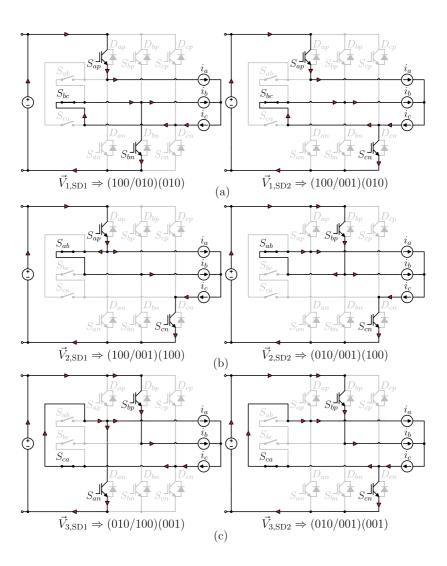

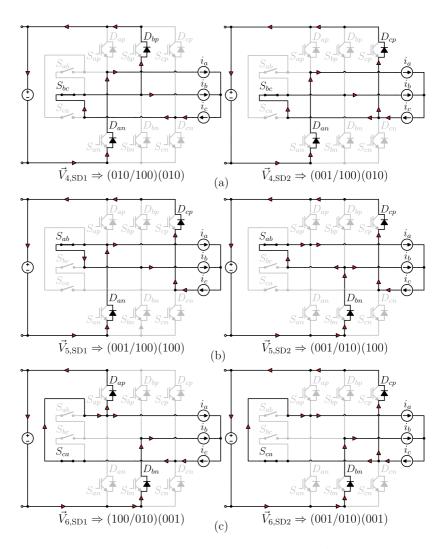

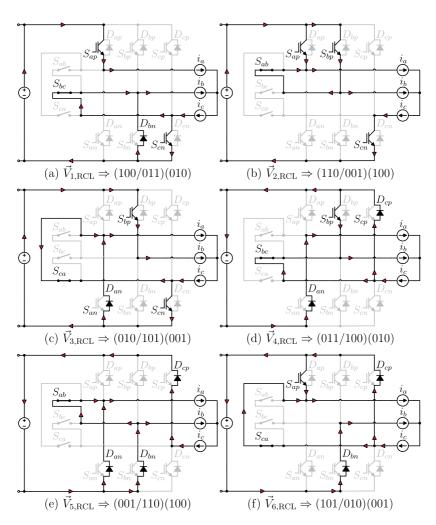

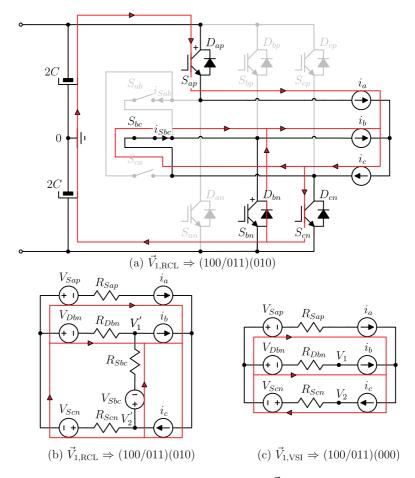

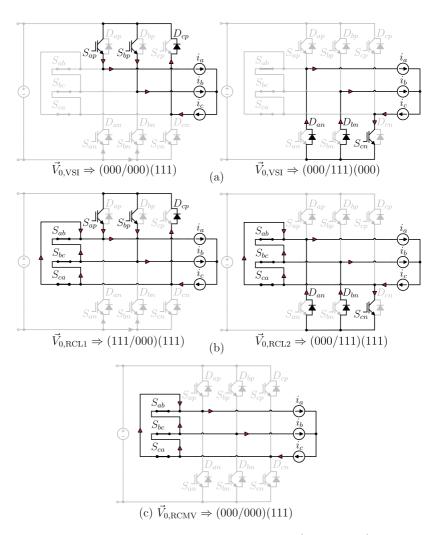

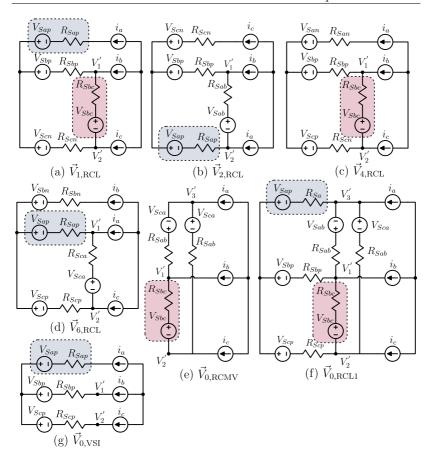

|   | 3.4 | Estado | os Topológicos do $\Delta$ -VSI                 | 25 |

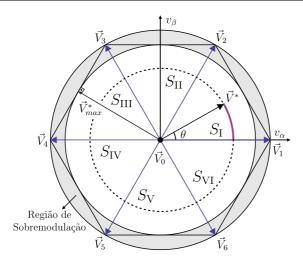

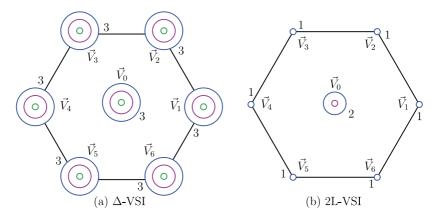

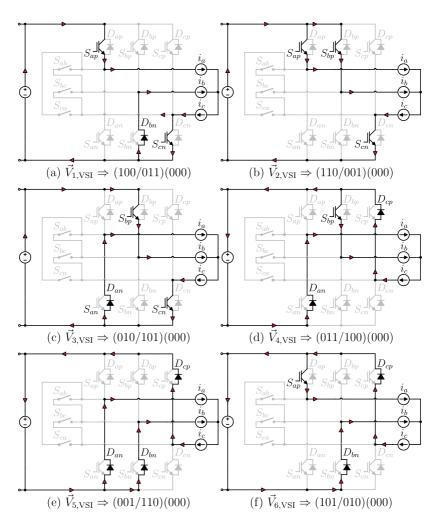

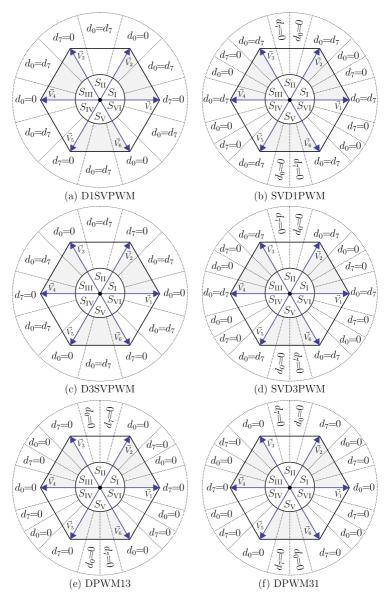

|   | 3.5 | Modu   | lação Vetorial do $\Delta$ -VSI                 | 32 |

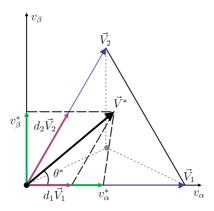

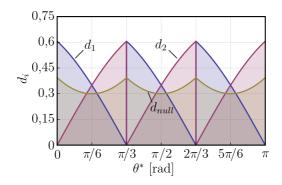

|   |     | 3.5.1  | Cálculo dos Tempos de Aplicação dos Vetores     | 34 |

|   |     | 3.5.2  | Restrições para o Vetor de Referência           | 36 |

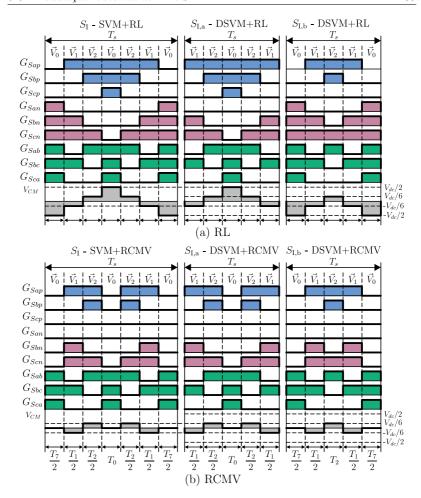

|   |     | 3.5.3  | Sequência de Vetores                            | 38 |

|   | 3.6 | Escoll | na dos Estados Redundantes e dos Semicondutores | 40 |

|   |     | 3.6.1  | Interruptores com Reduzidas Perdas por Condu-   |    |

|   |     |        | ção Conectados em Delta                         | 41 |

|   |     | 3.6.2  | Interruptores com Reduzidas Perdas por Condu-   |    |

|   |     |        | ção Conectados em Estrela                       | 43 |

|   |      | 3.6.3 Seleção dos Semicondutores                             | 44  |  |  |

|---|------|--------------------------------------------------------------|-----|--|--|

|   | 3.7  | Conclusão                                                    | 46  |  |  |

| 4 | MO   | DULAÇÃO PWM BASEADA EM PORTADORAS                            | 47  |  |  |

|   | 4.1  | Introdução                                                   | 47  |  |  |

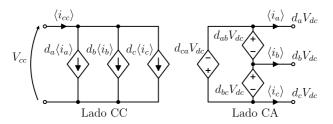

|   | 4.2  | Modelo Médio do $\Delta$ -VSI                                | 48  |  |  |

|   | 4.3  | Relação Entre a CBPWM e a SVM para os Interruptores          |     |  |  |

|   |      | em Estrela                                                   | 52  |  |  |

|   | 4.4  | Relação Entre a CBSVM e a SVM para os Interruptores          |     |  |  |

|   |      | em Delta                                                     | 55  |  |  |

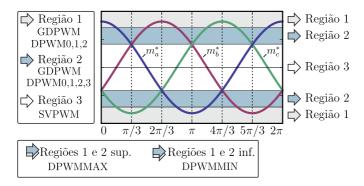

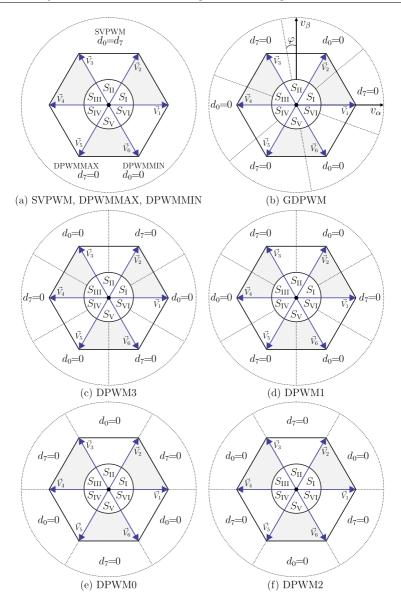

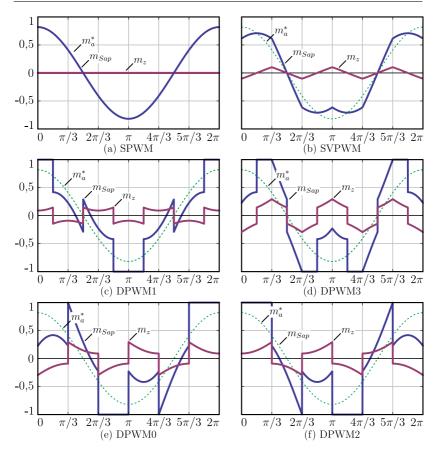

|   | 4.5  | - 1 3 · · · · · · · · · · · · · · · · · ·                    |     |  |  |

|   |      | em Estrela                                                   | 56  |  |  |

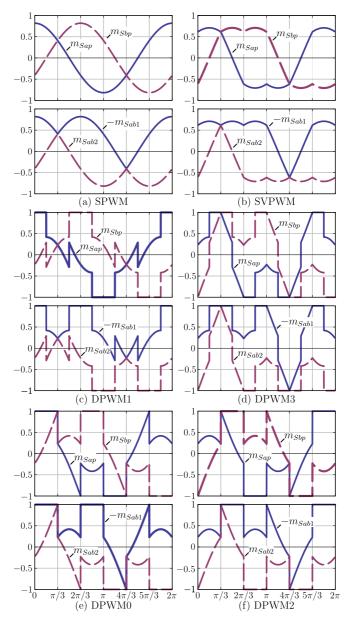

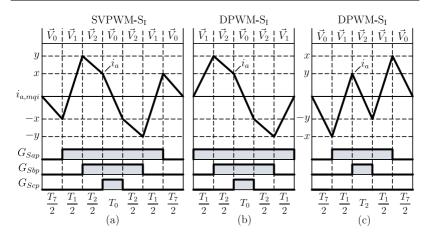

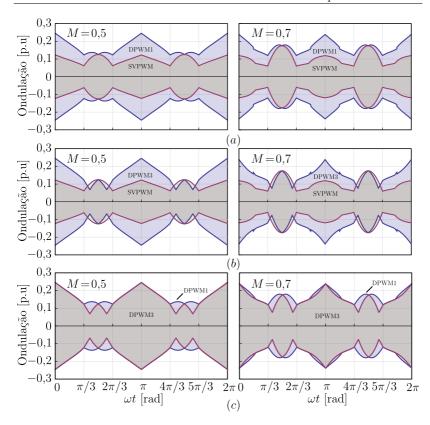

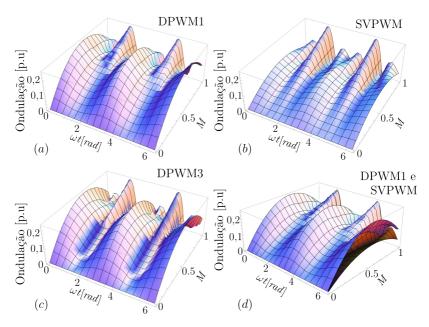

|   |      | 4.5.1 SVPWM                                                  | 58  |  |  |

|   |      | 4.5.2 DPWM                                                   | 60  |  |  |

|   |      | 4.5.2.1 Tipos de DPWMs                                       | 64  |  |  |

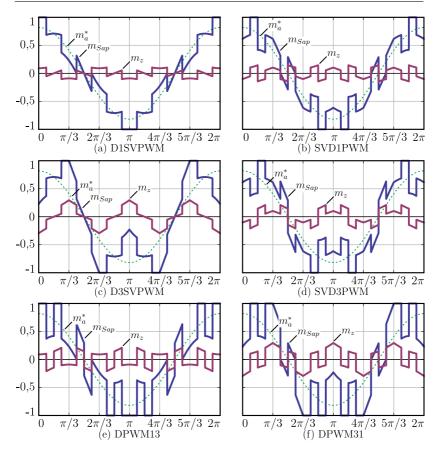

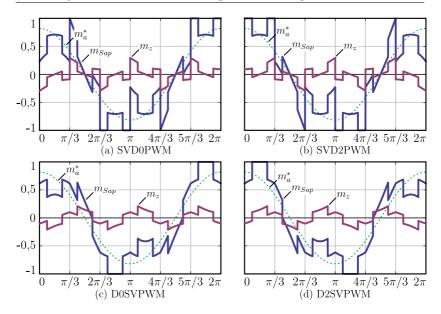

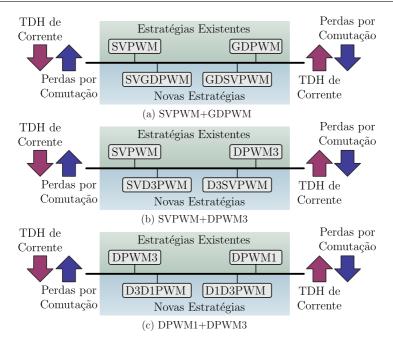

|   |      | 4.5.3 Novas Estratégias de Modulação                         | 68  |  |  |

|   |      | 4.5.4 Alternância entre Estratégias de Modulação             | 72  |  |  |

|   | 4.6  | Geração dos Sinais Moduladores para os Interruptores         |     |  |  |

|   |      | em Delta                                                     | 74  |  |  |

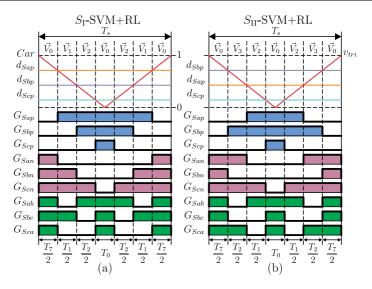

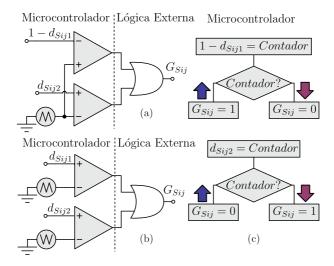

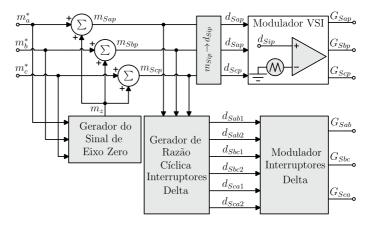

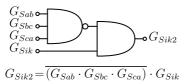

|   | 4.7  | Moduladores                                                  | 76  |  |  |

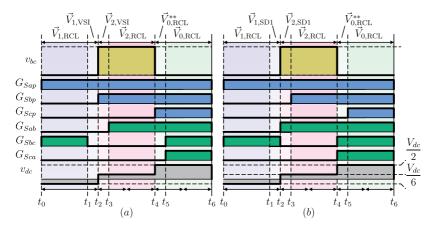

|   | 4.8  | Estratégia de Transição entre Vetores                        |     |  |  |

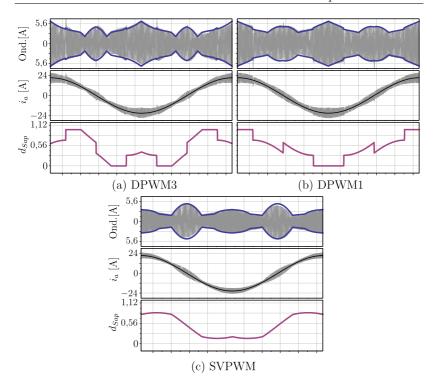

|   | 4.9  | Resultados do $\Delta$ -VSI Operando em Malha Aberta    .  . | 78  |  |  |

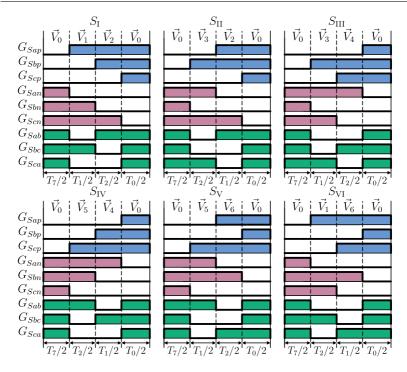

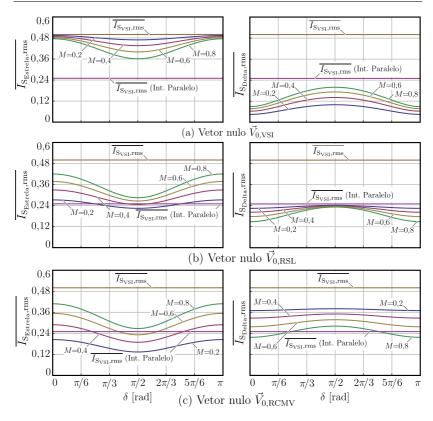

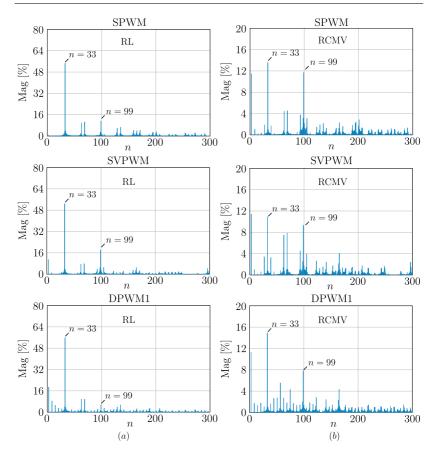

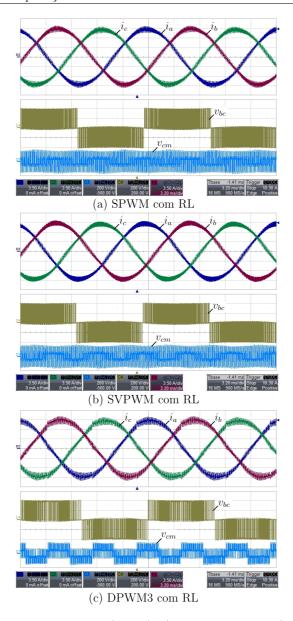

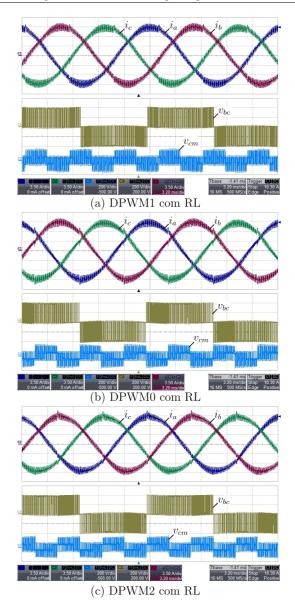

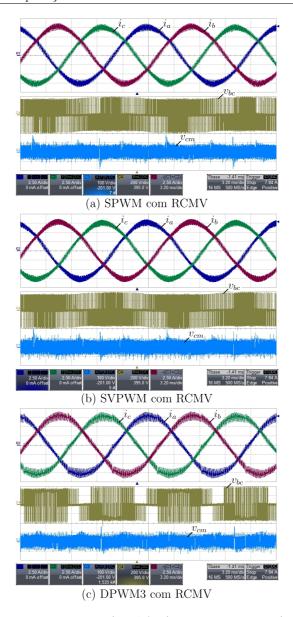

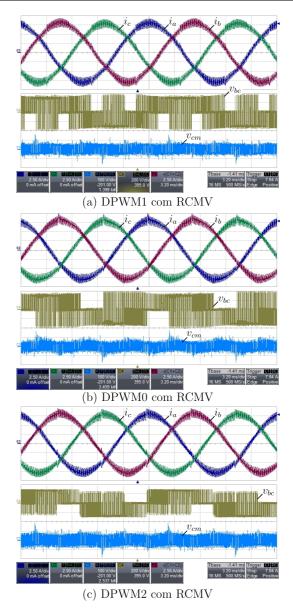

|   |      | 4.9.1 Resultado para as Modulações Tradicionais              | 80  |  |  |

|   |      | 4.9.2 Resultados para as Modulações Híbridas                 | 80  |  |  |

|   |      | 4.9.3 Problema da Distorção na Entrada e na Saída da         |     |  |  |

|   |      | Região de Descontinuidade                                    | 80  |  |  |

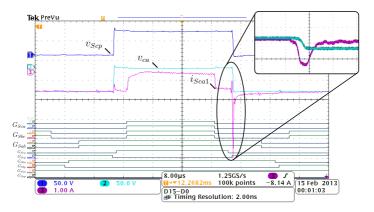

|   |      | 4.9.4 Detalhe da Transição Entre Vetores                     | 80  |  |  |

|   | 4.10 | Conclusão                                                    | 86  |  |  |

| 5 | ANA  | ÁLISE DO DESEMPENHO DO $\Delta$ -VSI                         | 89  |  |  |

|   | 5.1  | Descrição do Estudo de Caso                                  | 89  |  |  |

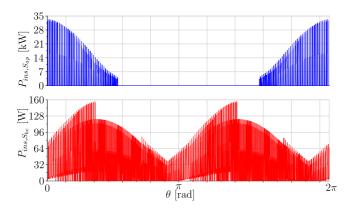

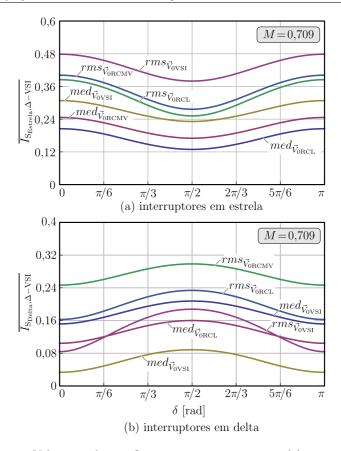

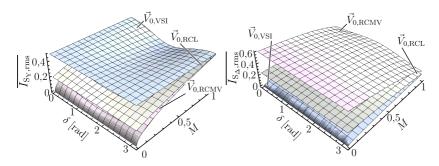

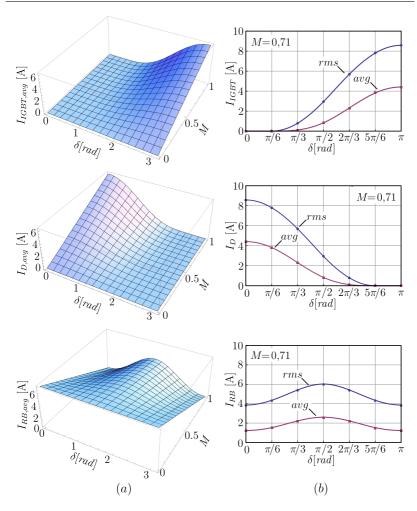

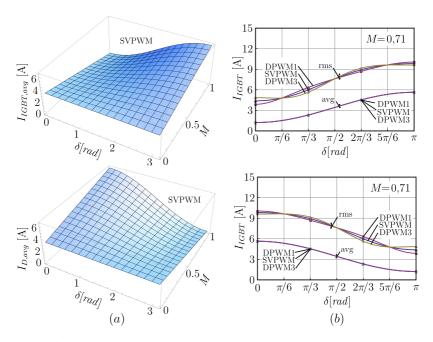

|   | 5.2  | Esforços de Corrente nos Interruptores                       | 90  |  |  |

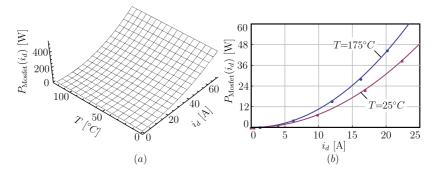

|   | 5.3  | Perdas nos Semicondutores                                    | 102 |  |  |

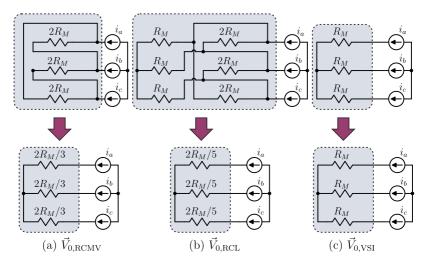

|   |      | 5.3.1 Perdas por Condução                                    | 104 |  |  |

|   |      | 5.3.2 Perdas por Comutação                                   | 108 |  |  |

|   |      | <u> </u>                                                     | 110 |  |  |

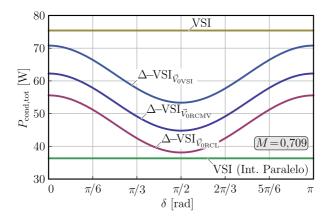

|   | 5.4  | •                                                            | 114 |  |  |

|   | 5.5  | -                                                            | 121 |  |  |

|   | 5.6  | Conclusão                                                    | 122 |  |  |

|                                   | LICAÇÃO DO CONVERSOR $\Delta$ -VSI CONECTADO À DE ELÉTRICA                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

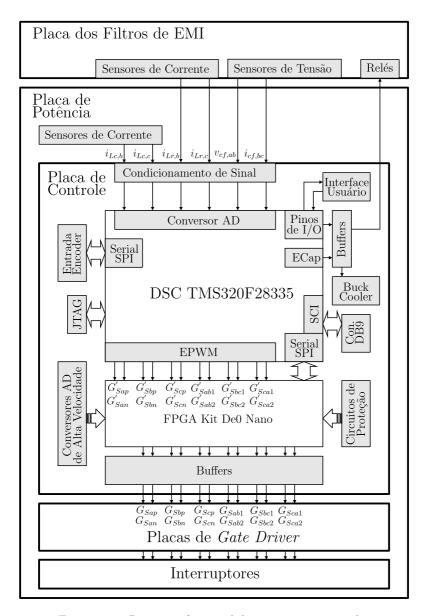

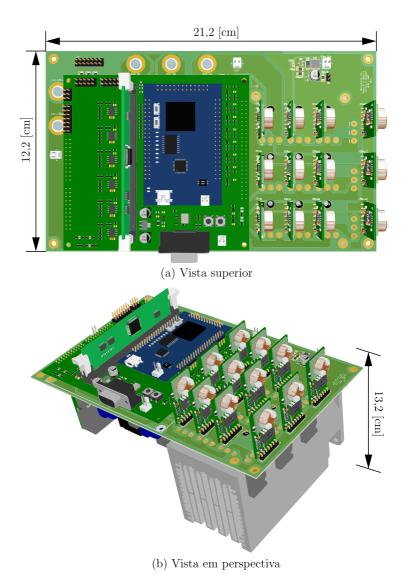

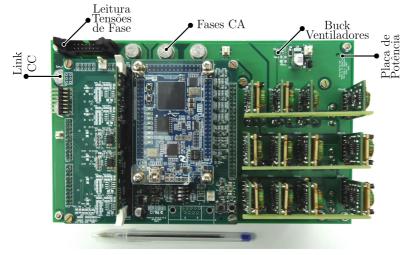

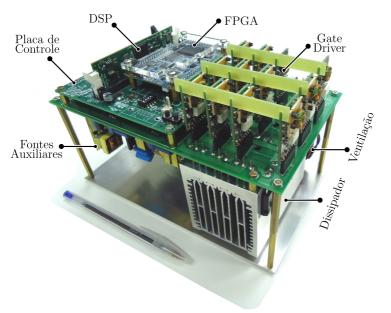

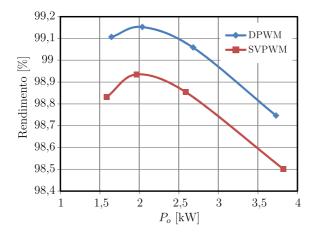

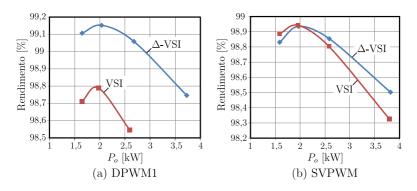

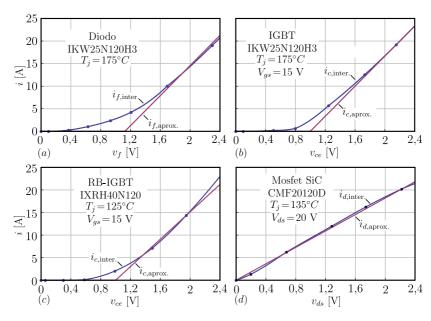

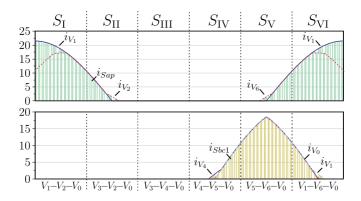

| 6.7<br>6.8<br>6.9<br>7 CON<br>7.1 | Final       150         Placa do Filtro de EMI       151         Resultados Experimentais do Protótipo Implementado       151         6.8.1 Validação das Estratégias de Modulação       155         6.8.2 Curvas de Rendimento       155         Conclusão       161         NCLUSÃO GERAL       163         Trabalhos Futuros       166                                                                             |

| A.1<br>A.2<br>A.3<br>A.4          | ce A – Algorítmo para cálculo de Esforços do $\Delta$ -VSI                                                                                                                                                                                                                                                                                                                                                            |

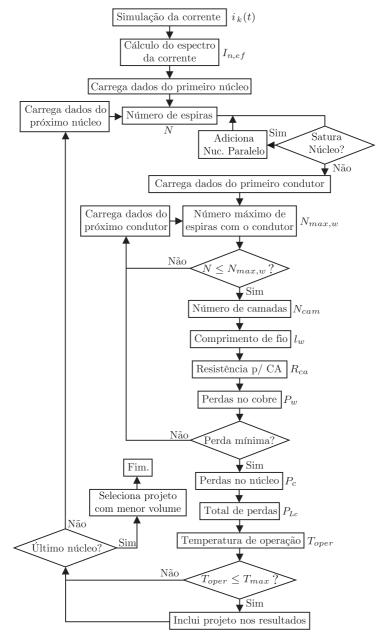

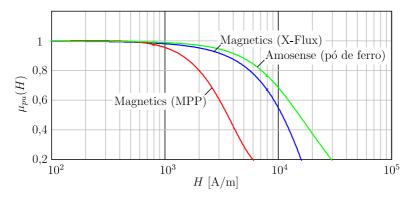

|                                   | ce B - Projeto Físico dos Indutores do Filtro LCL       193         Introdução       193         Procedimento de Projeto       193         B.2.1 Determinação do Número de Espiras e do Número de Núcleos em Paralelo       195         B.2.2 Escolha do Condutor       197         B.2.3 Perdas nos Condutores       198         B.2.4 Perdas no Magnético       200         B.2.5 Elevação de Temperatura       200 |

| B.3    |     | Re  | su  | lt | ad  | os  | О  | bt | ic | los |    |     |   |    |    |    |  |      |  |      |      |      |      | 200     |

|--------|-----|-----|-----|----|-----|-----|----|----|----|-----|----|-----|---|----|----|----|--|------|--|------|------|------|------|---------|

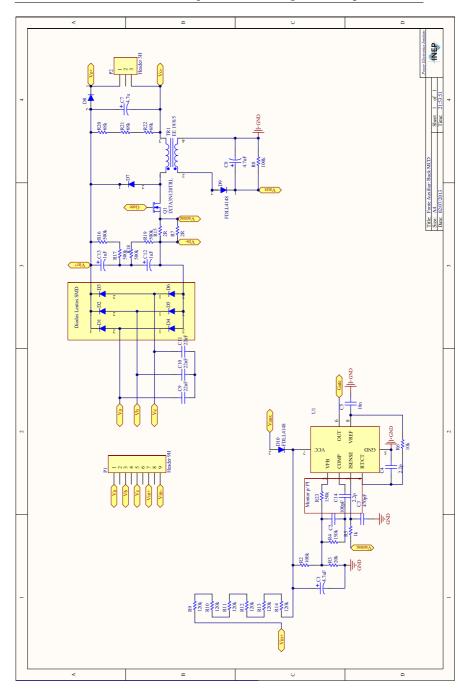

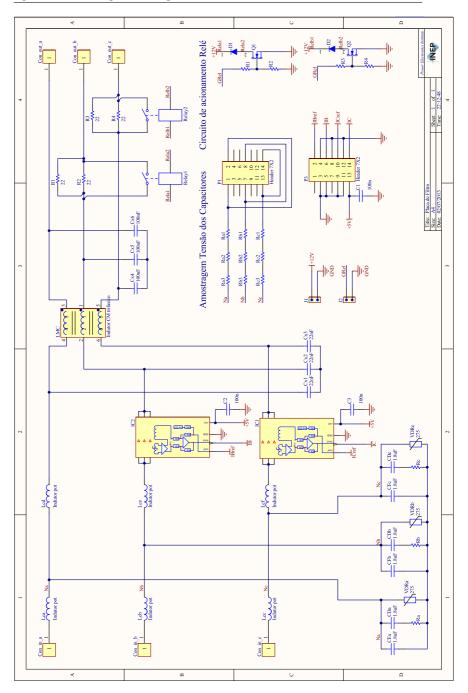

| Apêndi | .ce | e C | ; – | Ι  | )ia | ıgr | ar | na | s  | Es  | qι | ıeı | m | át | ic | os |  | <br> |  | <br> | <br> | <br> | <br> | <br>203 |

## 1 INTRODUÇÃO

## 1.1 Contextualização do Trabalho

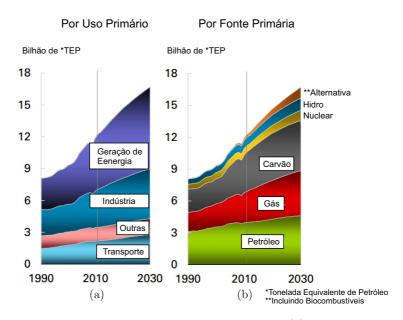

O século XXI trouxe consigo diversas propostas de mudanças na maneira como geramos, transmitimos e consumimos a energia elétrica. É mostrado na Figura 1.1 que, no início do século, houve um aumento significativo na taxa de crescimento do consumo de energia, principalmente para geração de energia elétrica. Analisando a previsão para 2030, verifica-se também que o consumo só tende a aumentar. Como a maior parte da energia consumida provém de fontes não renováveis de energia e que geram gases causadores do efeito estufa, conclui-se que panorama para o futuro é insustentável.

Figura 1.1: Consumo global de energia separado por: (a) por uso primário; (b) por fonte primária [1].

O aumento do consumo energético presenciado nos últimos anos, aliado à volatilidade do petróleo, a ineficiência das usinas térmicas, a segurança questionável das usinas nucleares, e questões ambientais

2 1 Introdução

envolvendo emissão de gases causadores do efeito estufa, radiação e destruição de ecossistemas fizeram surgir propostas de restruturação, a começar, pelo Sistema Elétrico de Potência (SEP).

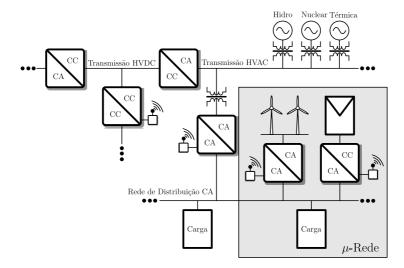

Durante muito tempo, a geração de energia no sistema elétrico de potência foi concentrada em locais isolados próximos às grandes fontes de energia, ou seja, próximo às mineradoras, poços de petróleo, grandes reservas hídricas. A energia gerada por essas fontes é então transmitida por extensas redes de alta tensão em Corrente Alternada (CA) e distribuída para os consumidores domésticos em uma rede de Baixa Tensão (BT) em CA. Os consumidores dessa rede convencional são passivos no que diz respeito à geração de energia, sendo o Operador Nacional do Sistema (ONS) o responsável pelo despacho de toda a geração do sistema. Hoje se propõe que a geração de energia ocorra em forma de Geração Distribuída (GD), conforme mostrado na Figura 1.2.

Figura 1.2: Diagrama unifilar simplificado de uma rede inteligente.

Nesse novo sistema, os consumidores de energia passam também a gerar, o que aproxima o ponto de consumo do ponto de produção. A incorporação das unidades de GD trazem diversos benefícios ao SEP como o aumento da confiabilidade e qualidade de energia, maior facilidade de instalação de novas fontes de geração, e a incorporação das fontes renováveis não convencionais de energia como a solar fotovoltaica

e a eólica.

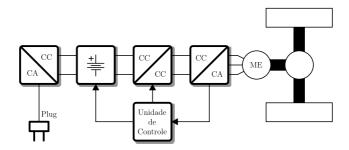

Os veículos elétricos também passam a ser elementos importantes nessa nova estrutura que, além de reduzir a quantidade de emissão de carbono na atmosfera, por não utilizarem combustíveis fósseis, também podem servir como elementos armazenadores de energia para o SEP no contexto de redes inteligentes (*Smart Grids*). Na Figura 1.3 é mostrado que a energia utilizada no carro elétrio provém de baterias. Dado que a energia armazenada é derivada de fontes renováveis, a substituição do carro a combustão pelo carro elétrico contribui para a redução de gases causadores do efeito estufa.

Figura 1.3: Esquemático de blocos de um veículo elétrico.

Entretanto, para que seja feito o controle da energia gerada e consumida nas redes ativas inteligentes, é necessário à criação de um sistema robusto de comunicação entre as fontes geradoras e consumidoras e a incorporação da eletrônica de potência ao sistema elétrico. O controle do fluxo de energia entre as fontes de geração e os consumidores finais será feito por inversores, retificadores, conversores CC-CC e CA-CA, elementos já bastante difundidos no setor industrial. Além disso, os veículos elétricos também necessitam dos conversores de potência para o acionamento dos motores elétricos e de seus periféricos, ressaltando ainda mais a importância da energia eletronicamente processada.

Os conversores mais utilizados no SEP, no acionamento de veículos elétricos e na indústria são os Inversores Fonte de Tensão (VSI) para aplicações em baixa tensão (<1000 V) e médias potências (<100 kW). Devido aos apelos citados anteriormente, esses inversores devem processar energia de forma eficiente e apresentar reduzidos peso e volume. Tais conversores também são utilizados em estações de telecomunica-

4 1 Introdução

ções, em satélites e em aplicações aeroespaciais e navais. Outro aspecto importante, principalmente para conversores conectados à rede elétrica e em acionamento de máquinas, é a interferência eletromagnética (EMI) proveniente da energia de comutação em alta frequência dos interruptores de potência que é radiada ou transmitida via cabos para a rede ou equipamentos nas proximidades.

Vários esforços têm sido feitos, ao longo dos anos, com o intuito de melhorar o desempenho dos inversores de tensão e, é neste sentido, que este trabalho busca contribuir. Uma busca recente, realizada no banco de dados do Instituto de Engenheiros Eletricistas e Eletrônicos (IEEE), por high efficiency inverter, resulta em mais de 2300 trabalhos, o que demostra grande empenho por parte dos pesquisadores para melhorar o rendimento das topologias já existentes ou propor novas alternativas de topologias.

### 1.2 Principais Contribuições do Trabalho

O trabalho em questão contribuiu no estudo de uma nova topologia de inversor trifásico com modulação por largura de pulsos (PWM) fonte de tensão dois níveis com com potencial para ser otimizado em relação a densidade de potência, rendimento e emissões eletromagnéticas. Novas topologias multiníveis foram derivadas de maneira semelhante à estudada na dissertação.

Ao longo do trabalho, foram propostas várias estratégias de modulação vetorial e baseadas em portadora para este conversor e o desempenho de cada uma delas foi avaliado. Foi proposto um método para estimação de esforços em conversores que apresentam divisão de corrente entre dispositivos semicondutores durante um dado estado de comutação. Um protótipo foi construído com o intuito de validar as as análises realizadas. A aplicação desse conversor conectado à rede elétrica foi estudada onde os detalhes da implementação são fornecidos.

## 1.2.1 Artigos Publicados

No decorrer do ano destinado ao desenvolvimento do trabalho de mestrado, foram publicados três artigos em conferências internacionais relacionados com o tema desta dissertação [2]–[4].

### 1.3 Estrutura da Dissertação

Esta dissertação está dividida em seis capítulos destinados ao estudo de uma nova topologia de inversor de tensão trifásico dois níveis. Neste foi realizada uma contextualização do trabalho e suas contribuições foram expostas.

No Capítulo 2, é feita uma revisão bibliográfica sobre topologias de inversores fonte de tensão utilizados em aplicações onde, em baixa tensão e com média potência, um alto desempenho do conversor é exigido. Ao final deste tópico, a topologia proposta é apresentada juntamente com a metodologia seguida para a sua obtenção.

Os princípios de operação do conversor, bem como duas estratégias de modulação vetorial, são apresentados no Capítulo 3. São mostrados todos os estados e vetores possíveis que o conversor pode implementar.

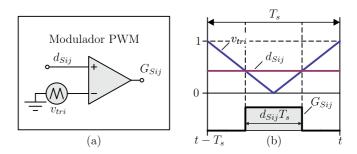

No Capítulo 4, são apresentadas algumas estratégias de modulação PWM baseadas em portadoras para o conversor proposto. Aqui, é apresentada uma metodologia para a geração de técnicas de modulação PWM baseadas em portadora a partir dos padrões de pulsos desejados para os interruptores. O procedimento desenvolvido pode ser estendido para outros conversores trifásicos. Seguindo a mesma metodologia, técnicas de modulação híbridas também são propostas para o conversor. O procedimento para calcular as funções de modulação bem como a estrutura dos moduladores são detalhados.

No Capítulo 5, o conversor proposto é comparado com um Inversor Trifásico Fonte de Tensão dois Níveis (2L-VSI) para as modulações propostas no Capítulo 4. As comparações foram feitas analiticamente e verificadas por simulações e alguns resultados experimentais.

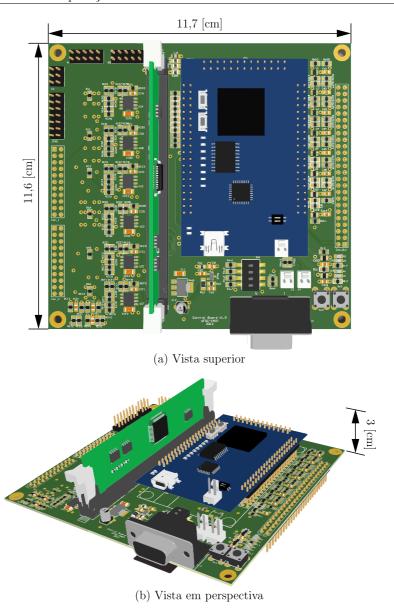

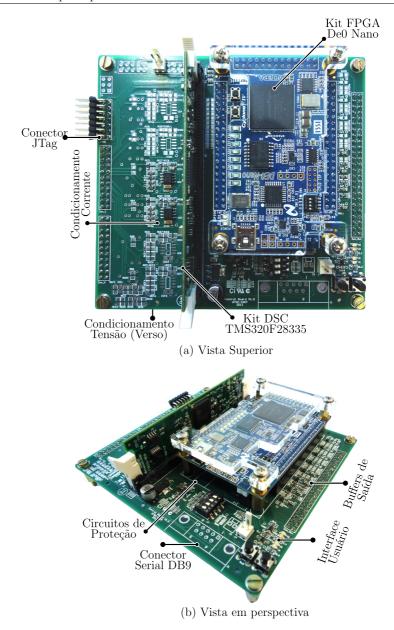

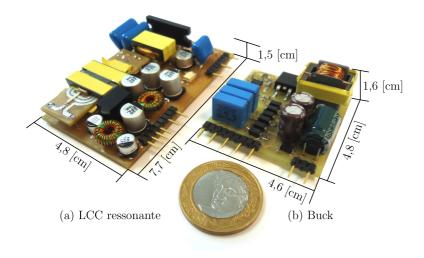

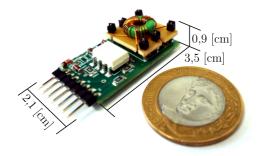

O estudo da aplicação do conversor proposto em sistemas conectados à rede elétrica foi realizado no Capítulo 6. Nesse capítulo são apresentadas especificações para o projeto de um inversor de 10 kW. O modelo do conversor incluindo o seu filtro de saída para a realização do controle de suas correntes também foi desenvolvido. O protótipo construído é apresentado bem como resultados experimentais validando algumas das teorias propostas no trabalho.

Por fim, no Capítulo 7, uma conclusão geral do trabalho é apresentada bem como perspectivas para trabalhos futuros.

O apêndice A apresenta um algoritmo proposto para a determinação dos esforços de corrente quando se tem mais de um caminho

6 1 Introdução

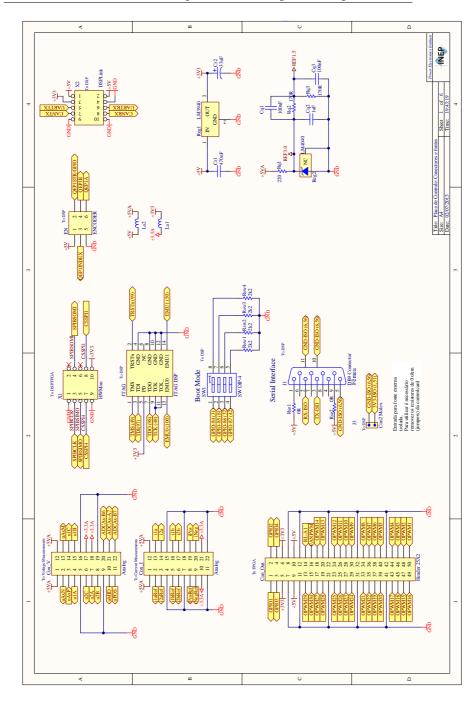

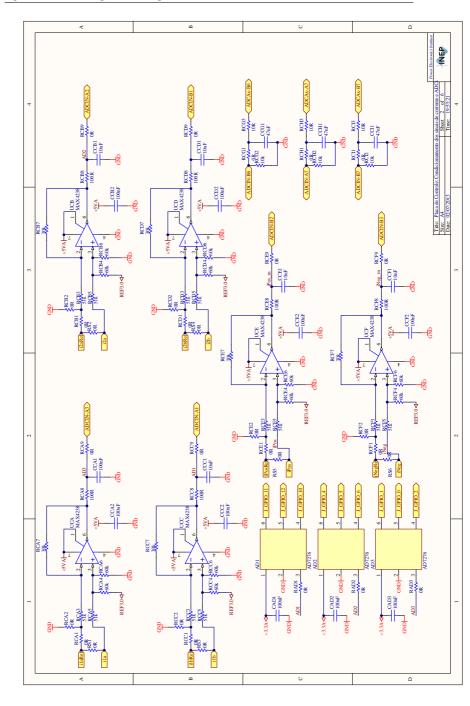

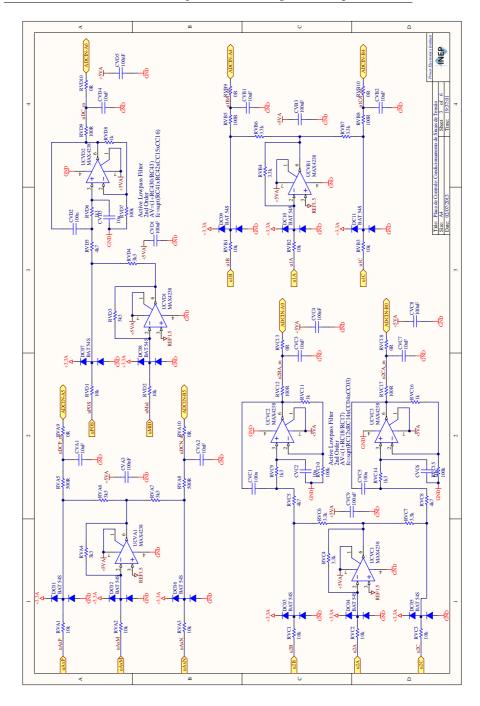

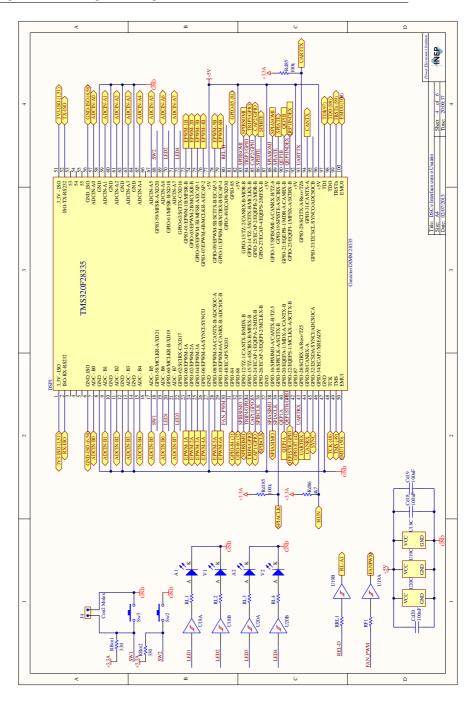

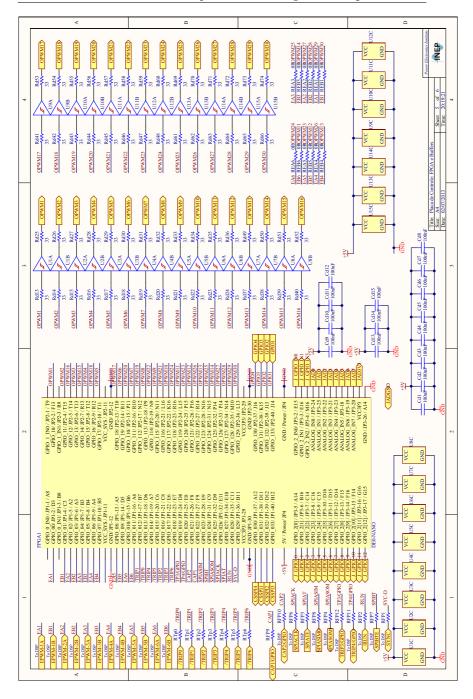

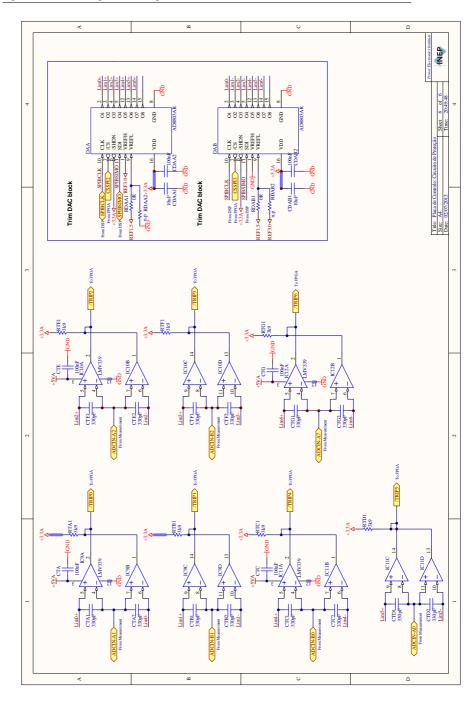

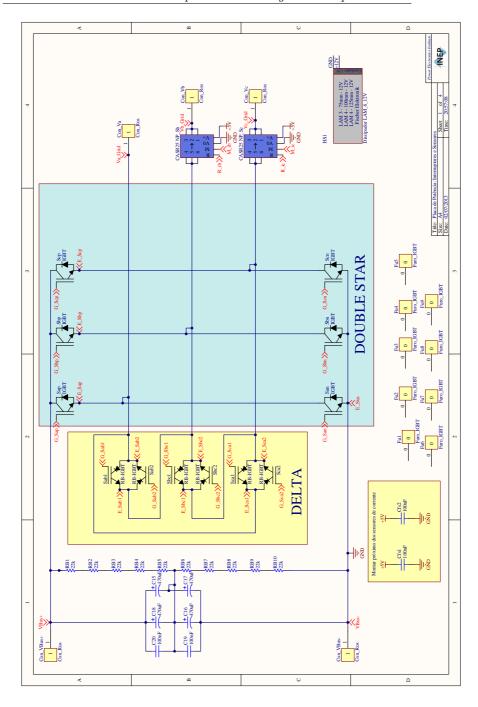

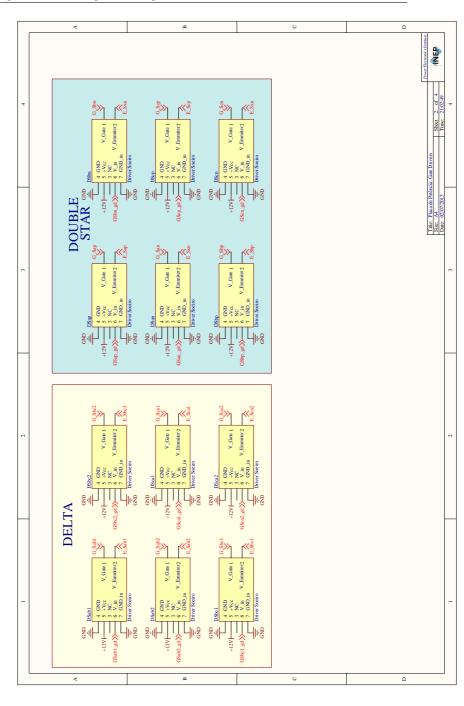

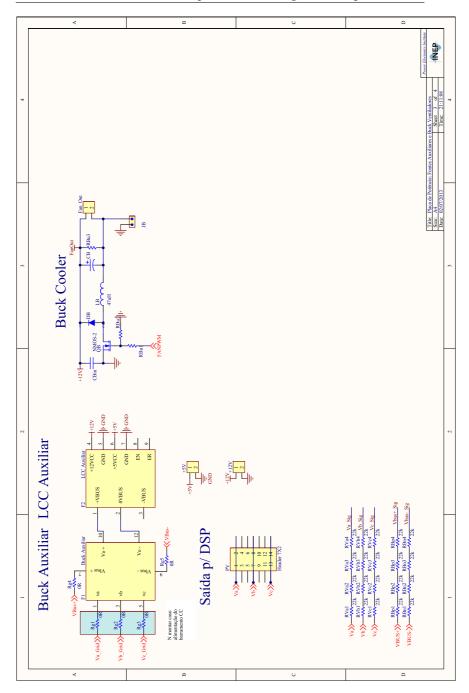

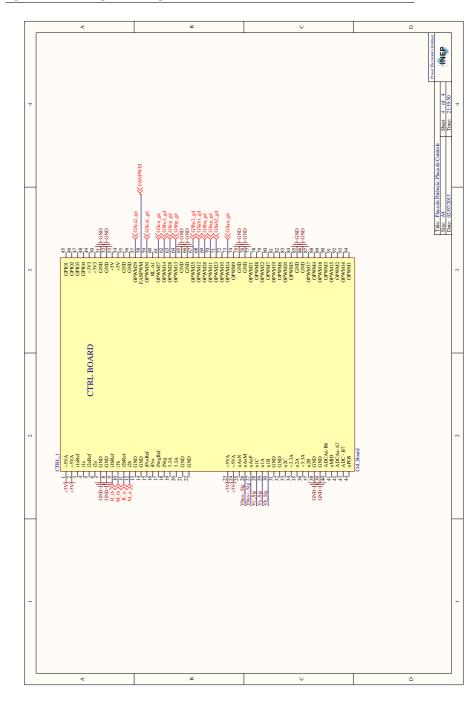

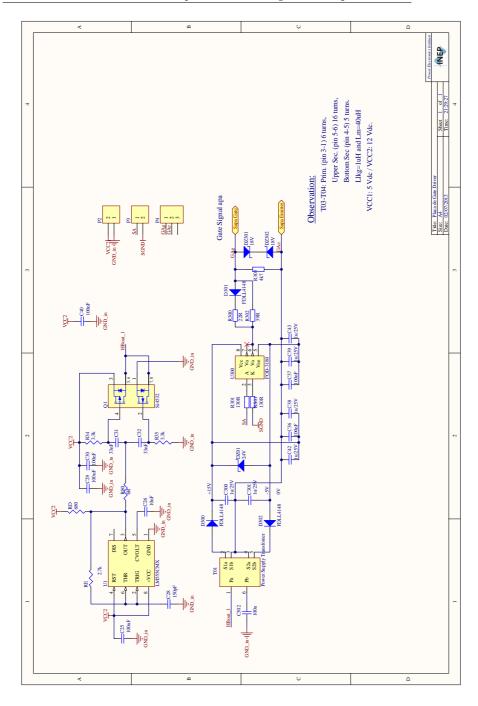

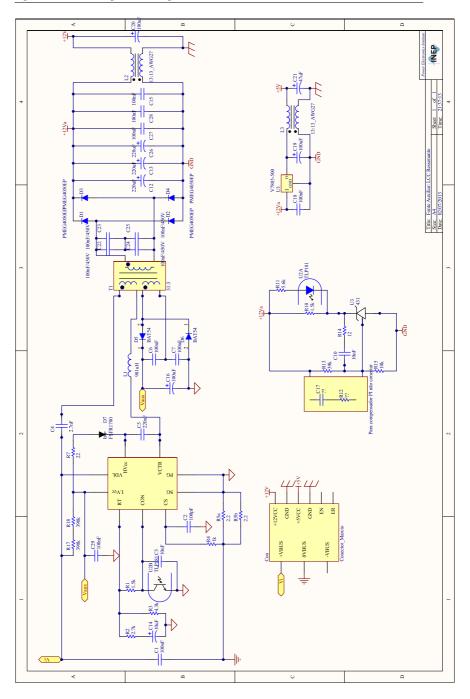

para a circulação das correntes nos interruptores em um estado de comutação. No Apêndice B é mostrado o procedimento utilizado para a realização do projeto físico dos indutores de filtro. O projeto foi realizado para que o volume do filtro fosse otimizado. O Apêndice C mostra os diagramas esquemáticos de todas as placas utilizadas no protótipo construído.

# 2 INVERSORES TRIFÁSICOS DE ALTO DESEMPENHO PARA APLICAÇÕES EM BT

## 2.1 Introdução

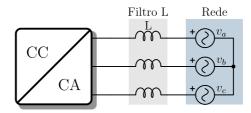

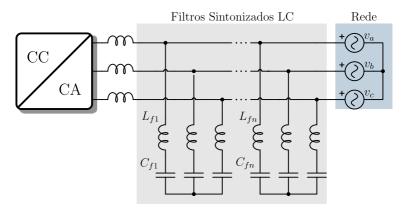

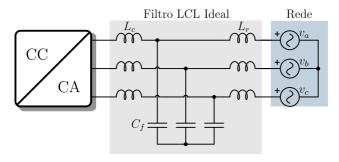

Neste capítulo, será feita uma revisão bibliográfica sobre inversores trifásicos para aplicações em baixa tensão onde são requeridos elevado rendimento e reduzidos peso e volume. Esses inversores, denominados aqui de inversores de alto desempenho, geralmente não fazem uso de transformadores de potência, pois tais elementos magnéticos apresentam peso e volume elevados. Nesses conversores estão contidos apenas capacitores, elementos semicondutores e, em alguns casos, também pequenos componentes magnéticos para o auxílio da comutação.

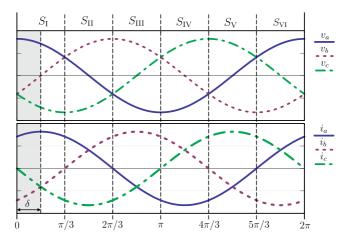

# 2.2 Inversor Trifásico de Tensão Dois Níveis Convencional (2L-VSI)

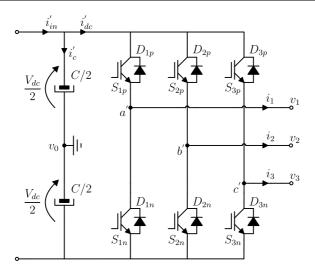

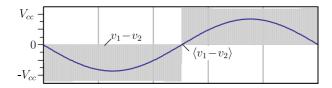

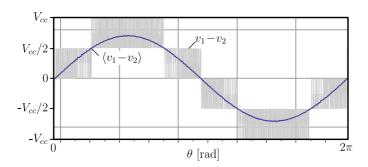

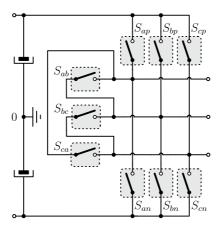

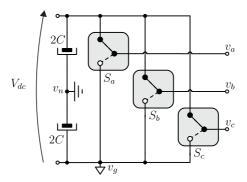

O 2L-VSI operando com Modulação por Largura de Pulso (PWM) é mostrado na Figura 2.1. Esse inversor é denominado dois níveis, pois aplica apenas dois níveis de tensão ( $-V_{dc}/2$  e  $V_{dc}/2$ ) entre as fases e o ponto neutro do barramento CC e três níveis ( $-V_{dc}$ ,  $V_{dc}$  e 0) entre as fases do lado CA conforme mostrado na Figura 2.2.

Desde a década de 1970, o 2L-VSI tem sido utilizado para o acionamento de motores na indústria e em veículos elétricos [5] e, ainda hoje, é a escolha padrão da indústria para realizar a conversão estática de corrente contínua para corrente alternada [6]. Os principais motivos para a utilização em larga escala desse conversor são a quantidade reduzida de semicondutores, apenas seis interruptores ativos e seis interruptores passivos (Diodos), a não necessidade de circuitos auxiliares de comutação, a não necessidade de controle ativo da tensão de seus capacitores, a boa distribuição de perdas, a facilidade de comando e a robustez de operação. Além disso, existem hoje na literatura inúmeros trabalhos reunidos em forma de artigos e livros [7], [8] sobre modelagem e modulação desse conversor.

Como desvantagens, o 2L-VSI necessita de um filtro volumoso de EMI devido a tensão com apenas três níveis entre seus terminais, aumenta consideravelmente as perdas por comutação com o aumento da frequência de comutação em relação a um conversor três níveis [6],

Figura 2.1: Inversor trifásico fonte de tensão dois níveis convencional.

Figura 2.2: Tensão entre os terminais CA de um inversor trifásico dois níveis.

[9]–[11] e produz elevados níveis de emissões de modo comum <sup>1</sup>.

As vantagens, os desafios e melhorias para esse conversor vêm sendo estudados desde a década de 1970 até hoje. Esse fato pode ser constatado realizando uma busca no banco de dados do IEEE [12] por *Three-phase PWM inverter* que retorna mais de 2.000 resultados.

Para tentar melhorar o desempenho desse inversor no que diz respeito a perdas nos semicondutores, uma estratégia utilizada é o paralelismo de semicondutores. Esta técnica multiplica a quantidade de interruptores utilizados com o intuito de reduzir as perdas por condução

$<sup>^1{\</sup>rm A}$ tensão de modo comum  $(v_{cm})$ foi definida neste trabalho como a média das tensões nos terminais AC do conversor em relação ao centro do barramento capacitivo  $(v_{10}+v_{20}+v_{30})/3$

do conversor [13]. Isso é obtido com o aumento nas perdas por comutação e com a necessidade de estratégias de controle para balancear os esforços de corrente entre os interruptores em paralelo.

### 2.3 Inversores Dois Níveis com Comutação Suave

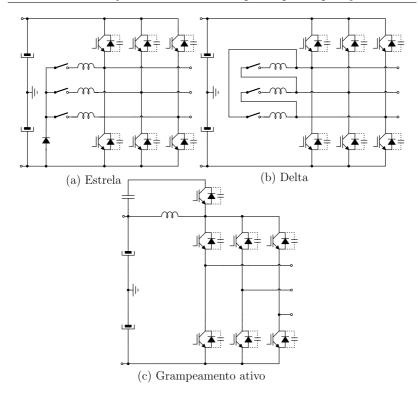

Na década de 1990, para reduzir os esforços nos semicondutores devido às perdas por comutação, diversos circuitos auxiliares foram propostos para realizar a comutação sem perdas (suave) dos interruptores. Três desses circuitos são mostrados na Figura 2.3. Por apresentarem maior rendimento e um volume reduzido, os 2L-VSIs operando com comutação suave são utilizados em aplicações como a tração automotiva [14].

A Figura 2.3(a) [15] mostra o circuito auxiliar conectado em delta às fases do inversor e a Figura 2.3(b) [16] mostra o circuito auxiliar conectado em estrela. Nos dois circuitos, os interruptores auxiliares são ligados momentos antes e desligados momentos depois dos interruptores principais para que ocorra Comutação sob Tensão Nula (ZVS) dos interruptores principais. O 2L-VSI com o circuito auxiliar conectado em delta é mais vantajoso em relação 2L-VSI com o circuito auxiliar conectado em estrela, pois não apresenta tensão flutuante nem sobretensão nos interruptores auxiliares, não apresenta corrente de circulação nas fases desligadas, e não necessita que os diodos auxiliares sejam rápidos.

A eficiência dos conversores dois níveis operando com comutação suave é aumentada, porém para isso tiveram que ser acrescentados três interruptores bidirecionais em tensão e em corrente, seus respectivos circuitos de comando e três indutores em relação ao 2L-VSI. Além disso, há uma maior complexidade na geração dos sinais de comando do inversor, pois existem três sinais a mais para serem gerados e sincronizados.

Pensando em reduzir a quantidade de circuitos auxiliares para obter comutação suave, topologias como a apresentada em [17] e mostrada na Figura 2.3 (c) foram propostas. Esse circuito é capaz de operar com comutação suave em todos os interruptores, inclusive no auxiliar, para toda a faixa de variação de carga. Como desvantagem, o interruptor auxiliar é submetido à elevados esforços de corrente no circuito com grampeamento ativo.

Figura 2.3: Inversores trifásicos de tensão dois níveis operando com comutação suave utilizando circuito auxiliar em: (a) estrela; (b) delta; (c) grampeamento ativo.

# 2.4 Inversores Dois Níveis Operando em Máquinas com Bobinas Acessíveis (Dual VSI)

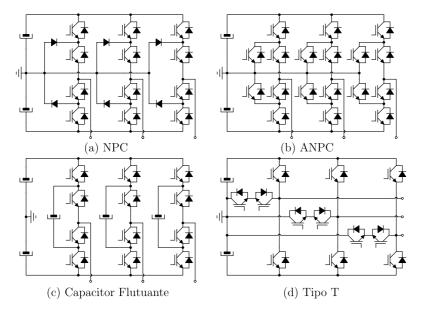

Para tentar reduzir a tensão de modo comum e a ondulação de corrente geradas pelos conversores dois níveis em aplicações para acionamento de máquinas, uma estratégia encontrada na literatura consiste na utilização de dois 2L-VSI conectados aos terminais das bobinas, conforme ilustra a Figura 2.4.

Esse conversor é capaz de aplicar sete vetores, entre eles vetores ativos e nulos, com tensão de modo comum nula. Utilizando a estratégia de modulação adequada, é possível zerar a tensão de modo comum que

Figura 2.4: Inversor trifásico de tensão dual.

a máquina é submetida [18], [19]. As desvantagens desse conversor são o uso restrito de aplicações (máquinas com acesso aos dois terminais das bobinas), a maior complexidade da modulação e a quantidade de interruptores necessários.

#### 2.5 Inversores Três Níveis

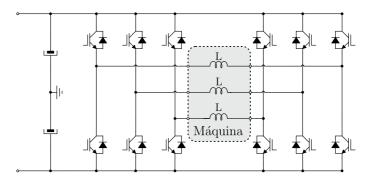

Os inversores trifásicos de tensão multiníveis [20] são a principal solução para conversão de energia em tensões mais elevadas. Entretanto, na década de 2000, os inversores multiníveis, em especial os inversores três níveis, vêm se tornando uma alternativa interessante também para a conversão de energia em baixa tensão. Os inversores de tensão três níveis mais estudados na literatura para esse tipo de aplicação são o com Ponto Neutro Grampeado (NPC) [21], [22], o com Ponto Neutro Grampeado Ativamente (ANPC) [23], o Tipo T [6], [24] e o com Capacitores Flutuantes [25], [26] . Esses inversores são mostrados na Figura 2.5.

Os inversores três níveis têm como principais vantagens em relação a um 2L-VSI, o maior número de níveis da tensão de fase, como mostrado na Figura 2.6, menor geração de tensão de modo comum, melhor distribuição das perdas entre os semicondutores e o decréscimo menos acentuado da eficiência com o aumento da frequência de comutação [6], [9]–[11].

Entretanto, esses conversores possuem maior quantidade de semicondutores e  $gate\ drivers$  isolados, a necessidade de balanço das ten-

Figura 2.5: Topologias de inversores trifásicos de tensão três níveis: (a) NPC; (b) ANPC; (c) Capacitor Flutuante; (d) Tipo T.

Figura 2.6: Tensão entre os terminais CA de um inversor trifásico três níveis.

sões nos capacitores, maior quantidade de elementos passivos, e maior complexidade na geração dos sinais de comando. Todas as desvantagens apontadas reduzem a robustez desses conversores quando comparados com as topologias dois níveis.

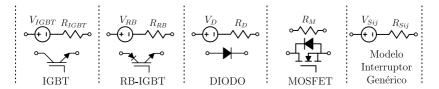

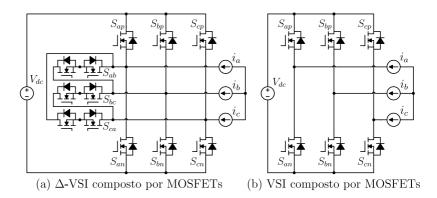

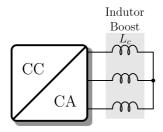

#### 2.6 Topologia Proposta

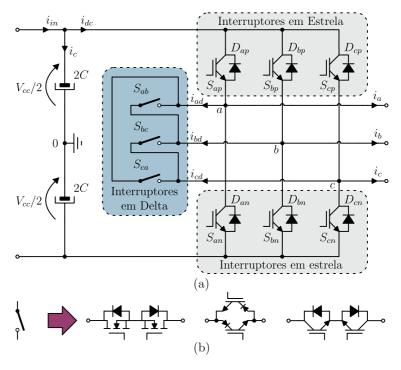

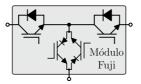

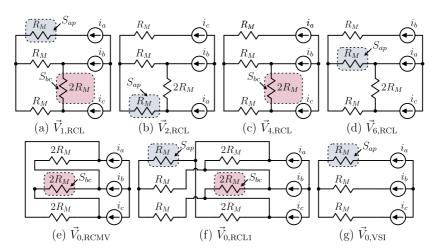

O Inversor Trifásico PWM Fonte de Tensão com Integração de Interruptores Conectados em Delta ( $\Delta$ -VSI), mostrado na Figura 2.7 (a), possui dois grupos de interruptores em estrela e um grupo de interruptores em delta. Transistores Bipolares com Gatilho Isolado (IGBTs) em antiparalelo com diodos foram utilizados para representar os interruptores conectados em estrela , podendo ser substituídos por outros dispositivos semicondutores dependendo da aplicação do conversor. Da mesma forma, os interruptores bidirecionais em tensão e em corrente podem ser implementado de diferentes maneiras, conforme mostrado na 2.7 (b).

Esse conversor aplica dois níveis de tensão, um positivo e um ne-

Figura 2.7: Inversor trifásico proposto: (a) topologia do conversor; (b) topologia de possíveis interruptores bidirecionais em tensão e em corrente.

gativo entre as fases e o ponto central aos capacitores, sendo, portanto, um inversor de dois níveis. Por ser um conversor dois níveis, muitas de suas características são semelhantes as do 2L-VSI, como será visto nos capítulos posteriores. Como nos inversores multiníveis, a adição dos interruptores bidirecionais conectados em delta cria estados de comutação redundantes que podem ser utilizados para distribuir esforços de corrente entre os semicondutores, reduzir perdas por condução e tensão de modo comum. Desta forma, o conversor proposto possui potencial para ser otimizado e atingir valores elevados de rendimento e valores reduzidos de tensão de modo comum.

## 2.6.1 Geração da Topologia

A topologia do  $\Delta$ -VSI pode ser concebida de pelo menos quatro maneiras distintas. A maneira mais intuitiva é adicionando interruptores bidirecionais em tensão e em corrente em uma configuração delta às fases de um 2L-VSI.

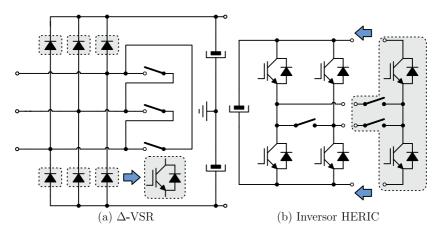

O conversor proposto também pode ser visto como a versão bidirecional do Retificador PWM Fonte de Tensão com Integração de Interruptores Conectados em Delta ( $\Delta$ -VSR)(Figura 2.8(a)) proposto em [27] e implementado pela primeira vez em [28]. Em [27] também é proposto um retificador similar, porém os interruptores bidirecionais são conectados em estrela. Estratégias de modulação foram propostas

Figura 2.8: Derivação do  $\Delta$ -VSI a partir do: (a)  $\Delta$ -VSR; (b) HERIC.

ao longo dos anos para o  $\Delta$ -VSR [29], [30] e, recentemente, a utilização desse conversor vem sendo estudada em sistemas eólicos de pequeno porte [31], [32] e em aplicações aeroespaciais [33]. O  $\Delta$ -VSR é mais robusto que um 2L-VSI operando no modo retificador, pois não é possível a realização de um curto circuito no lado CC. Para a implementação do  $\Delta$ -VSI a partir do  $\Delta$ -VSR, os interruptores passivos são trocados por interruptores ativos, como IGBTs ou MOSFETs.

O  $\Delta$ -VSI pode também ser interpretado como a versão trifásica do Conceito de Inversor Eficiente e Confiável (HERIC), mostrado na Figura 2.8(b) [34]. O HERIC difere do tradicional ponte completa monofásico pela adição do interruptor bidirecional em tensão e em corrente de forma paralela com a carga. O funcionamento deste inversor é mostrado em [35]–[39] para aplicação em sistemas fotovoltaicos, onde também são mostradas algumas variações desse conversor.

Tanto o Δ-VSR quanto o HERIC desconectam o lado CC do conversor do lado CA nas suas respectivas etapas de roda livre. Esse procedimento reduz a tensão de modo comum produzida pelas comutações dos interruptores além de reduzir a troca de reativos entre os lados CC e CA durante a aplicação do vetor nulo [40], o que aumenta o rendimento desses conversores em comparação com o VSI tradicional.

Outra maneira de conceber o  $\Delta$ -VSI é desfazendo a conexão existente com o centro dos capacitores do lado CC no circuito do inversor trifásico do Tipo T (Figura 2.5 (d)) e conectando os interruptores bidirecionais em uma configuração delta.

## 2.7 Interruptores Conectados em Delta para Topologias Multiníveis

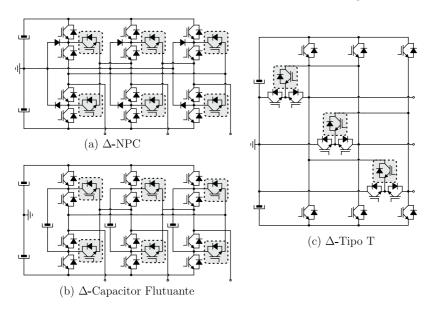

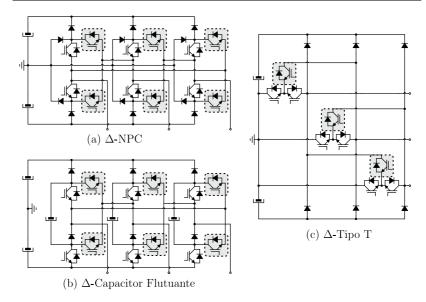

As vantagens conseguidas com a adição dos interruptores em delta ao 2L-VSI podem também ser obtidas com a implementação do interruptor bidirecional em corrente e em tensão conectado em delta às fases de conversores três níveis. Nos conversores NPC e Capacitor Flutuante mostrados na Figura 2.5 (a) e (c), são necessários a adição de seis interruptores bidirecionais em corrente (IGBT+Diodo) aos circuitos originais, conforme mostra a Figura 2.9 (a) e (b). Para realizar o interruptor bidirecional em tensão em corrente no inversor do Tipo T, apenas três interruptores precisam ser adicionados ao circuito original da Figura 2.5 (d). Com a substituição de alguns interruptores bidirecionais por interruptores bidirecionais [41], obtém-se as versões

unidirecionais desses conversores conforme mostrado em Figura 2.10.

Figura 2.9: Novas topologias com interruptores conectados em delta derivadas de conversores três níveis existentes: (a)  $\Delta$ -NPC; (b)  $\Delta$ -Capacitor Flutuante; (c)  $\Delta$ -Tipo T.

A principal vantagem do interruptor em delta aos conversores multiníveis é a possibilidade de redução das perdas por condução em relação às topologias originais.

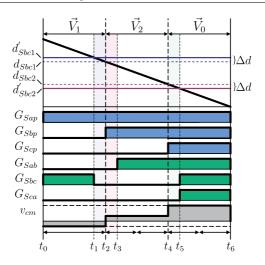

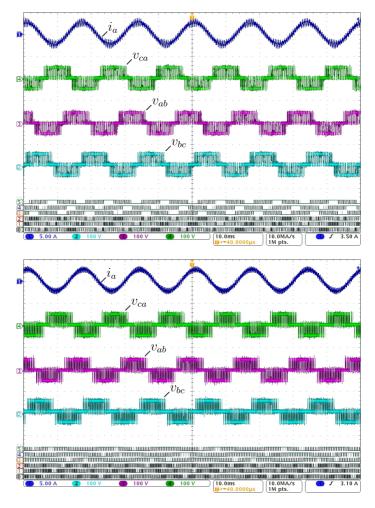

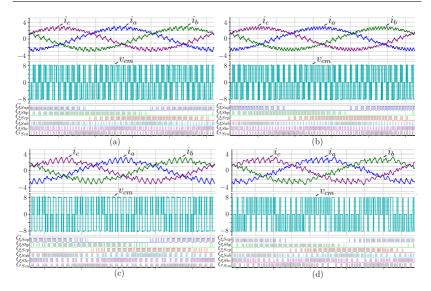

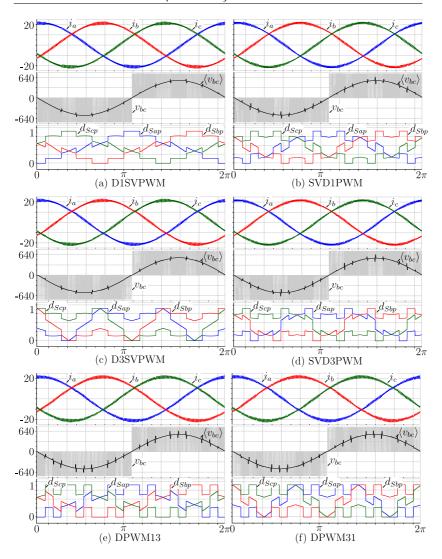

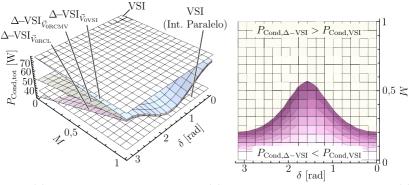

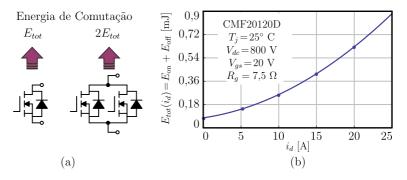

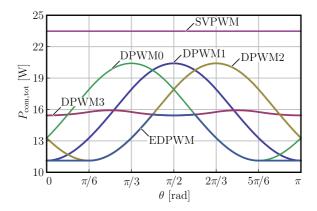

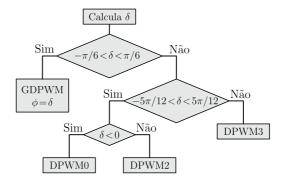

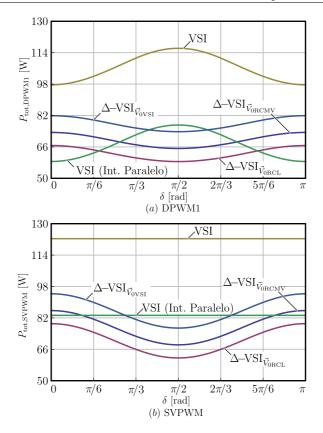

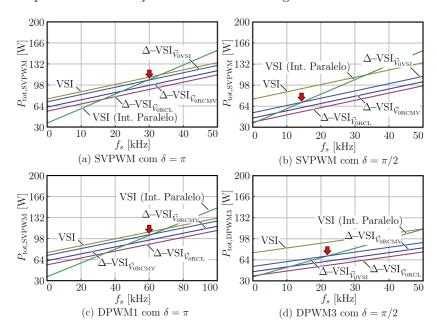

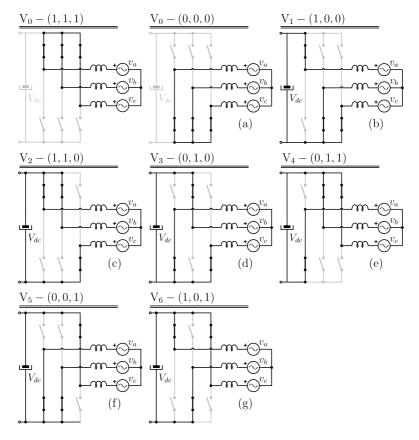

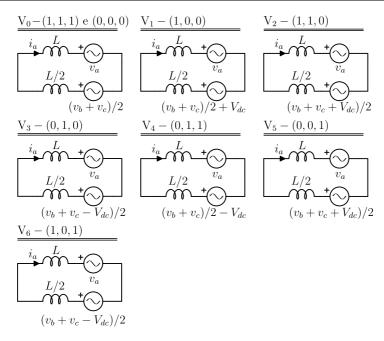

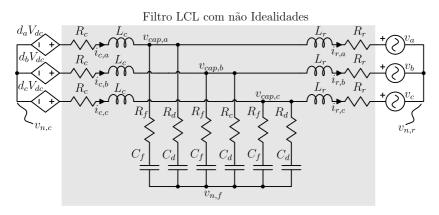

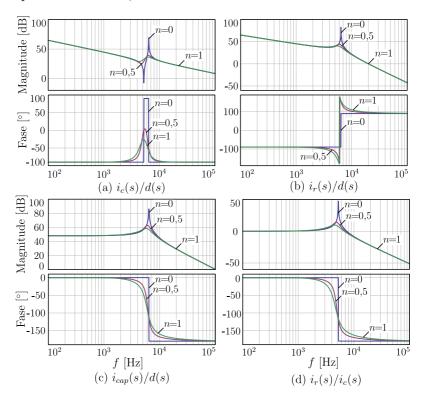

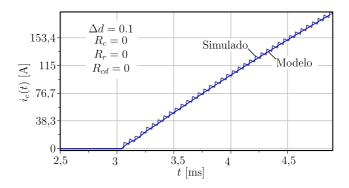

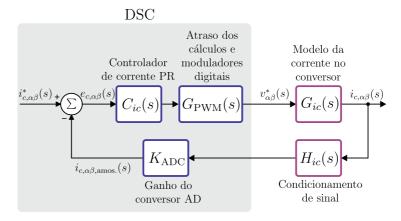

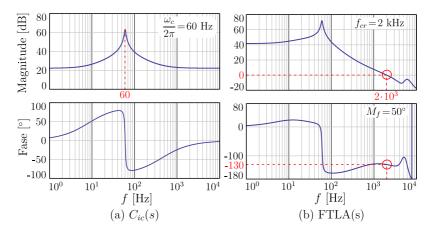

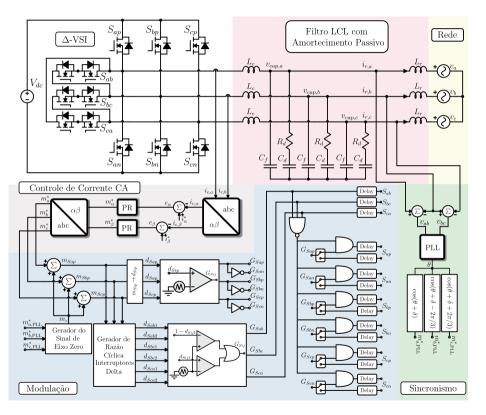

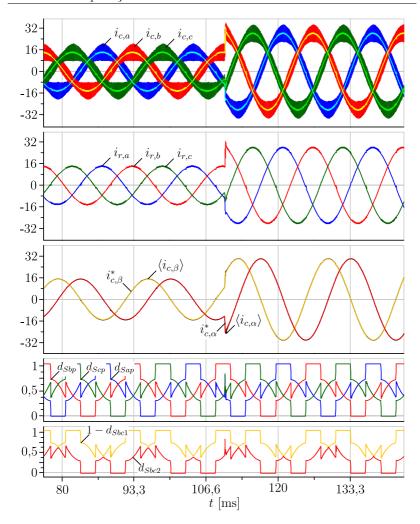

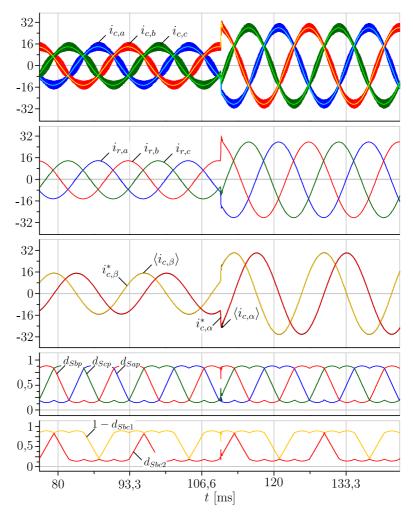

#### 2.8 Conclusão